### SY69753AL

# 3.3V, 125Mbps, 155Mbps Clock and Data Recovery

### **General Description**

The SY69753AL is a complete Clock Recovery and Data Retiming integrated circuit for OC-3/STS-3 applications at 155Mbps NRZ. The device is ideally suited for SONET/SDH/ATM applications and other high-speed data transmission systems.

Clock recovery and data retiming is performed by synchronizing the on-chip VCO directly to the incoming data stream. The VCO center frequency is controlled by the reference clock frequency and the selected divide ratio. On-chip clock generation is performed through the use of a frequency multiplier PLL with a byte rate source as reference.

The SY69753AL also includes a link fault detection circuit.

Datasheets and support documentation can be found on Micrel's web site at: <a href="https://www.micrel.com">www.micrel.com</a>.

#### **Features**

- 3.3V power supply

- SONET/SDH/ATM compatible

- Clock and data recovery for 125Mbps/155Mbps NRZ data stream

- Two on-chip PLLs: one for clock generation and another for clock recovery

- Selectable reference frequencies

- Differential PECL high-speed serial I/O

- Line receiver input: no external buffering needed

- · Link fault indication

- 100k ECL compatible I/O

- Industrial temperature range (-40°C to +85°C)

- Lower power: fully compatible with Micrel's SY87701V, but with 30% less power

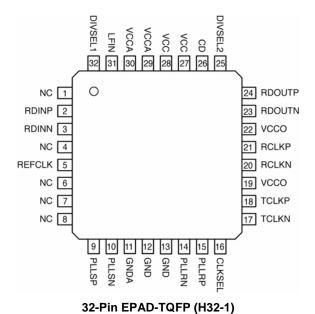

- Available in 32-pin EPAD-TQFP

### **Applications**

- Ethernet media converter(m)

- SONET/SDH/ATM OC-3

- Proprietary architecture at 120Mbps to 180Mbps

# Ordering Information<sup>(1)</sup>

| Part Number                  | Package<br>Type | Operating<br>Range | Package<br>Marking                             | Lead<br>Finish    |

|------------------------------|-----------------|--------------------|------------------------------------------------|-------------------|

| SY69753ALHG                  | H32-1           | Industrial         | SY69753ALHG with<br>Pb-Free bar-line indicator | NiPdAu<br>Pb-Free |

| SY69753ALHGTR <sup>(2)</sup> | H32-1           | Industrial         | SY69753ALHG with<br>Pb-Free bar-line indicator | NiPdAu<br>Pb-Free |

#### Notes:

- 1. Contact factory for die availability. Dice are guaranteed at T<sub>A</sub> = 25°C, DC Electricals only.

- 2. Tape and Reel.

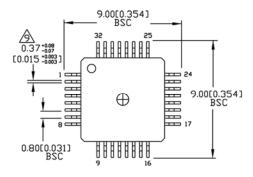

# **Pin Configuration**

# **Pin Description**

### Inputs

| Pin Number | Pin Name           | Type                 | Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|------------|--------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2 3        | RDINP<br>RDINN     | Differential<br>PECL | Serial Data Input: These built-in line receiver inputs are connected to the differential receive serial data stream. An internal receive PLL recovers the embedded clock (RCLK) and data (RDOUT) information.                                                                                                                                                                                                                                                                                                                                                                     |  |

| 5          | REFCLK             | TTL Input            | Reference Clock: This input is used as the reference for the internal frequency synthesizer and the "training" frequency for the receiver PLL to keep it centered in the absence of data coming in on the RDIN inputs.                                                                                                                                                                                                                                                                                                                                                            |  |

| 26         | CD                 | PECL Input           | Carrier Detect: This input controls the recovery function of the Receive PLL and can be driven by the carrier detect output of optical modules or from external transition detection circuitry. When this input is HIGH, the input data stream (RDIN) is recovered normally by the Receive PLL. When this input is LOW the data on the inputs RDIN will be internally forced to a constant LOW, the data outputs RDOUT will remain LOW, the Link Fault Indicator output LFIN forced LOW and the clock recovery PLL forced to look onto the clock frequency generated from REFCLK. |  |

| 32<br>25   | DIVSEL1<br>DIVSEL2 | TTL Input            | Divider Select: These inputs select the ratio between the output clock frequency (RCLK/TCLK) and the REFCLK input frequency as shown in the "Reference Frequency Selection" table.                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 16         | CLKSEL             | TTL Input            | Clock Select: This input is used to select either the recovered clock of the receiver PLL (CLKSEL = HIGH) or the clock of the frequency synthesizer (CLKSEL = LOW) to the TCLK outputs.                                                                                                                                                                                                                                                                                                                                                                                           |  |

### Outputs

| Pin Number | Pin Name         | Туре                 | Pin Name                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31         | LFIN             | TTL Output           | Link Fault Indicator: This output indicates the status of the input data stream RDIN. Active HIGH signal is indicating when the internal clock recovery PLL has locked onto the incoming data stream. LFIN will go HIGH if CD is HIGH and RDIN is within the frequency range of the Receive PLL (1000ppm) and will be alternating if not. LFIN is an asynchronous output. |

| 23<br>24   | RDOUTN<br>RDOUTP | Differential<br>PECL | Receive Data Output: These ECL 100K outputs represent the recovered data from the input data stream (RDIN). This recovered data is specified against the rising edge of RCLK.                                                                                                                                                                                             |

| 20<br>21   | RCLKN<br>RCLKP   | Differential<br>PECL | Clock Output: These ECL 100K outputs represent the recovered clock used to sample the recovered data (RDOUT).                                                                                                                                                                                                                                                             |

| 18<br>17   | TCLKP<br>TCLKN   | Differential<br>PECL | Clock Output: These ECL 100K outputs represent either the recovered clock (CLKSEL = HIGH) used to sample the recovered data (RDOUT) or the transmit clock of the frequency synthesizer (CLKSEL = LOW).                                                                                                                                                                    |

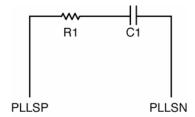

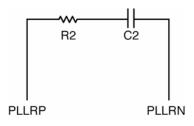

| 9<br>10    | PLLSP<br>PLLSN   |                      | Clock Synthesis PLL Loop Filter: External loop filter pins for the clock synthesis PLL.                                                                                                                                                                                                                                                                                   |

| 14<br>15   | PLLRN<br>PLLRP   |                      | Clock Recovery PLL Loop Filter: External loop filter pins for the receiver PLL.                                                                                                                                                                                                                                                                                           |

#### **Power and Ground**

| Pin Number    | Pin Name | Туре | Pin Name                                    |

|---------------|----------|------|---------------------------------------------|

| 27, 28        | VCC      |      | Power Supply. <sup>(1)</sup>                |

| 29<br>30      | VCCA     |      | Analog Power Supply Voltage. <sup>(1)</sup> |

| 19, 22        | VCCO     |      | Output Supply Voltage. (1)                  |

| 12, 13        | GND      |      | Ground.                                     |

| 1, 4, 6, 7, 8 | NC       |      | No connect.                                 |

| 11            | GNDA     |      | Analog Ground.                              |

#### Note:

1. VCC, VCCA, VCCO must be the same value.

# **Absolute Maximum Ratings**(1)

| Supply Voltage (V <sub>CC</sub> )     | 0.5V to +5.0V           |

|---------------------------------------|-------------------------|

| Input Voltage (V <sub>IN</sub> )      | 0.5V to V <sub>CC</sub> |

| Output Current (I <sub>OUT</sub> )    |                         |

| Continuous                            | ±50mA                   |

| Surge                                 | ±100mA                  |

| Lead Temperature (soldering, 20sec.)  | +260°C                  |

| Storage Temperature (T <sub>s</sub> ) | 65°C to +150°C          |

# Operating Ratings<sup>(2)</sup>

| Input Voltage (V <sub>CC</sub> )                         | +3.15V to +3.45V |

|----------------------------------------------------------|------------------|

| Ambient Temperature (T <sub>A</sub> )                    | 40°C to +85°C    |

| Junction Temperature (T <sub>J</sub> )                   | +125°C           |

| Package Thermal Resistance <sup>(3)</sup>                |                  |

| EPAD-TQFP (θ <sub>JA</sub> )<br>Still-air <sup>(4)</sup> |                  |

| Still-air <sup>(4)</sup>                                 | 28°C/W           |

| 500lfpm <sup>(4)</sup>                                   | 20°C/W           |

| EPAD-TOEP (A.s.)                                         |                  |

### **DC Electrical Characteristics**

$T_A = -40$ °C to +85°C, unless otherwise noted.

| Symbol          | Parameter            | Condition | Min  | Тур | Max  | Units |

|-----------------|----------------------|-----------|------|-----|------|-------|

| V <sub>CC</sub> | Power Supply Voltage |           | 3.15 | 3.3 | 3.45 | V     |

| Icc             | Power Supply Current |           |      | 120 | 160  | mA    |

#### **PECL 100K DC Electrical Characteristics**

$V_{CC} = V_{CCO} = V_{CCA} = 3.3V \pm 5\%$ ;  $T_A = -40^{\circ}C$  to +85°C, unless otherwise noted.

| Symbol          | Parameter           | Condition                               | Min                    | Тур | Max                    | Units |

|-----------------|---------------------|-----------------------------------------|------------------------|-----|------------------------|-------|

| V <sub>IH</sub> | Input HIGH Voltage  |                                         | V <sub>CC</sub> -1.165 |     | V <sub>CC</sub> -0.880 | V     |

| V <sub>IL</sub> | Input LOW Voltage   |                                         | V <sub>CC</sub> -1.810 |     | V <sub>CC</sub> -1.475 | V     |

| V <sub>OH</sub> | Output HIGH Voltage | 50Ω to V <sub>CC</sub> -2V              | V <sub>CC</sub> -1.075 |     | V <sub>CC</sub> -0.830 | V     |

| V <sub>OL</sub> | Output LOW Voltage  | 50Ω to V <sub>CC</sub> -2V              | V <sub>CC</sub> -1.860 |     | V <sub>CC</sub> -1.570 | V     |

| I <sub>IL</sub> | Input LOW Current   | V <sub>IN</sub> = V <sub>IL</sub> (Min) | 0.5                    |     |                        | μA    |

#### **TTL DC Electrical Characteristics**

$V_{CC} = V_{CCO} = V_{CCA} = 3.3V \pm 5\%$ ;  $T_A = -40$ °C to +85°C, unless otherwise noted.

| Symbol          | Parameter                    | Condition                                                                 | Min  | Тур | Max             | Units    |

|-----------------|------------------------------|---------------------------------------------------------------------------|------|-----|-----------------|----------|

| V <sub>IH</sub> | Input HIGH Voltage           |                                                                           | 2.0  |     | V <sub>CC</sub> | V        |

| V <sub>IL</sub> | Input LOW Voltage            |                                                                           |      |     | 0.8             | V        |

| V <sub>OH</sub> | Output HIGH Voltage          | I <sub>OH</sub> = -0.4mA                                                  | 2.0  |     |                 | V        |

| V <sub>OL</sub> | Output LOW Voltage           | I <sub>OL</sub> = 4mA                                                     |      |     | 0.5             | V        |

| I <sub>IH</sub> | Input HIGH Current           | $V_{IN}$ = 2.7V, $V_{CC}$ = Max.<br>$V_{IN}$ = $V_{CC}$ , $V_{CC}$ = Max. | -125 |     | +100            | μA<br>μA |

| I <sub>IL</sub> | Input LOW Voltage            | V <sub>IN</sub> = 0.5V, V <sub>CC</sub> = Max.                            | -300 |     |                 | μA       |

| Ios             | Output Short Circuit Current | V <sub>OUT</sub> = 0V, (max., 1 sec.)                                     | -15  |     | -100            | mA       |

#### Notes:

- 1. Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

- 3. Airflow of 500lfpm recommended for 28-pin SOIC.

- 4. Using JEDEC standard test boards with die attach pad soldered to PCB. See www.amkor.com for additional package details.

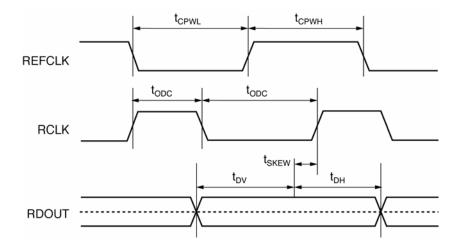

### **AC Electrical Characteristics**

$V_{CC}$  =  $V_{CCO}$  =  $V_{CCA}$  = 3.3V ±5%;  $T_A$  = -40°C to +85°C, unless otherwise noted.

| Symbol                          | Parameter                              | Condition                               | Min                           | Тур | Max  | Units      |

|---------------------------------|----------------------------------------|-----------------------------------------|-------------------------------|-----|------|------------|

| f <sub>VCO</sub>                | VCO Center Frequency                   | f <sub>REFCLK</sub> x Byte Rate         | 720                           |     | 1250 | MHz        |

| $\Delta f_{VCO}$                | VCO Center Frequency<br>Tolerance      | Nominal                                 |                               | 5   |      | %          |

| t <sub>ACQ</sub>                | Acquisition Lock Time                  | 50Ω to V <sub>CC</sub> -2V              |                               |     | 15   | μs         |

| t <sub>CPWH</sub>               | REFCLK Pulse Width HIGH                | 50Ω to V <sub>CC</sub> -2V              | 4                             |     |      | ns         |

| t <sub>CPWL</sub>               | REFCLK Pulse Width LOW                 | V <sub>IN</sub> = V <sub>IL</sub> (Min) | 4                             |     |      | ns         |

| t <sub>ir</sub>                 | REFCLK Input Rise Time                 |                                         |                               | 0.5 | 2    | ns         |

| t <sub>ODC</sub>                | Output Duty Cycle (RCLK/TCLK)          |                                         | 45                            |     | 55   | % of<br>UI |

| t <sub>r</sub> , t <sub>f</sub> | ECL Output Rise/Fall Time (20% to 80%) | $50\Omega$ to V <sub>CC</sub> -2        | 100                           |     | 400  | ps         |

| t <sub>SKEW</sub>               | Recovered Clock Skew                   |                                         | -200                          |     | +200 | ps         |

| t <sub>DV</sub>                 | Data Valid                             |                                         | 1/(2xf <sub>RCLK</sub> ) -200 |     |      | ps         |

| t <sub>DH</sub>                 | Data Hold                              |                                         | 1/(2xf <sub>RCLK</sub> ) -200 |     |      | ps         |

# **Timing Waveforms**

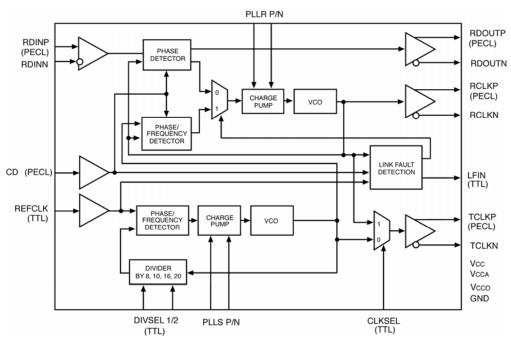

#### **Functional Block**

### **Functional Description**

#### **Clock Recovery**

Clock Recovery, as shown in the block diagram, generates a clock that is at the same frequency as the incoming data bit rate at the Serial Data input. The clock is phase aligned by a PLL so that it samples the data in the center of the data eye pattern.

The phase relationship between the edge transitions of the data and those of the generated clock are compared by a phase/frequency detector. Output pulses from the detector indicate the required direction of phase correction. These pulses are smoothed by an integral loop filter. The output of the loop filter controls the frequency of the Voltage Controlled Oscillator (VCO), which generates the recovered clock.

Frequency stability, without incoming data, is guaranteed by an alternate reference input (REFCLK) that the PLL locks onto when data is lost. If the Frequency of the incoming signal varies by greater than approximately 1000ppm with respect to the synthesizer frequency, the PLL will be declared out of lock, and the PLL will lock to the reference clock.

The loop filter transfer function is optimized to enable

the PLL to track the jitter, yet tolerate the minimum transition density expected in a received SONET data signal. This transfer function yields a 30µs data stream of continuous 1's or 0's for random incoming NRZ data.

#### **Lock Detect**

The SY69753AL contains a link fault indication circuit, which monitors the integrity of the serial data inputs. If the received serial data fails the frequency test, then the PLL will be forced to lock to the local reference clock. This will maintain the correct frequency of the recovered clock output under loss of signal or loss of lock conditions. If the recovered clock frequency deviates from the local reference clock frequency by more than approximately 1000ppm, the PLL will be declared out of lock. The lock detect circuit will poll the input data stream in an attempt to reacquire lock to data. If the recovered clock frequency is determined to be within approximately 1000ppm, the PLL will be declared in lock and the lock detect output will go active.

During the interval when the CDR is not locked onto the RDIN input, the LFIN output will not be a static LOW, but will be changing.

August 2007 6 M9999-082107-E

# Loop Filter Components<sup>(1)</sup>

R1 =  $350\Omega$ C1 =  $1.0\mu$ F (X7R Dielectric)

R2 =  $680\Omega$ C2 =  $1.0\mu$ F (X7R Dielectric)

#### Note:

1. Suggested values. Values may vary for different applications.

# **Reference Frequency Selection**

| DIVSEL1 | DIVSEL2 | f <sub>RCLK</sub> /f <sub>REFCLK</sub> |

|---------|---------|----------------------------------------|

| 0       | 0       | 8                                      |

| 0       | 1       | 10                                     |

| 1       | 0       | 16                                     |

| 1       | 1       | 20                                     |

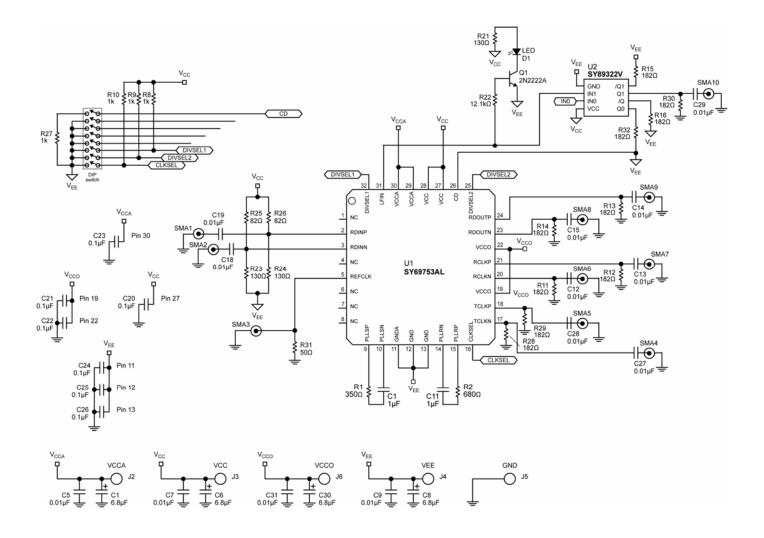

# **Application Example AC-Coupled I/O**

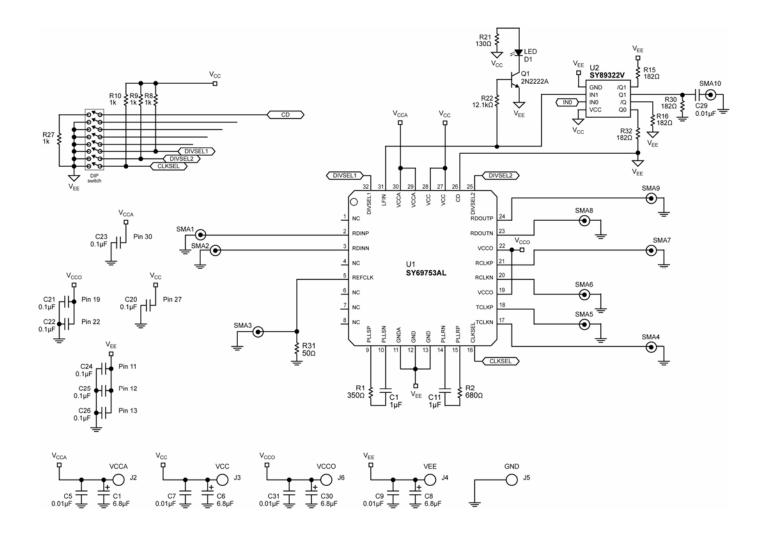

# Application Example DC-Coupled I/O

# **Related Product and Support Documentation**

| Part Number   | Function                                                                        | Data Sheet Link                                      |

|---------------|---------------------------------------------------------------------------------|------------------------------------------------------|

| SY87701AL     | Low-Power 3.3V, 28Mbps to 1300Mbps AnyRate <sup>®</sup> Clock and Data Recovery | www.micrel.com/product-info/products/sy87701al.shtml |

| HBW Solutions | New Products and Applications                                                   | www.micrel.com/product-info/products/solutions.shtml |

# **Bill of Materials (AC-Coupled)**

| Item                              | Part Number     | Manufacturer                         | Description                                                               | Qty. |

|-----------------------------------|-----------------|--------------------------------------|---------------------------------------------------------------------------|------|

| C6                                | 293D685X0025B2T | Vishay <sup>(1)</sup>                | 6.8μF, 25V, Tantalum Capacitor, Size B                                    | 1    |

| C7                                | VJ206Y103JXJAT  | Vishay <sup>(1)</sup>                | 0.01µF Ceramic Capacitor, Size 1206, X7R Dielectric                       | 1    |

| C10, C11                          | VJ0603Y105JXJAT | Vishay <sup>(1)</sup>                | 1.0µF Ceramic Capacitor, Size 0603, X7R Dielectric                        | 2    |

| C12-C15,<br>C18, C19,<br>C27, C28 | VJ0402Y104JXJAT | Vishay <sup>(1)</sup>                | 0.1μF Ceramic Capacitor, Size 0402, X7R Dielectric                        | 8    |

| C20-C26                           | VJ0402Y104JXJAT | Vishay <sup>(1)</sup>                | 0.01µF Ceramic Capacitor, Size 1206, X7R Dielectric                       | 7    |

| D1                                | P301-ND         | Panasonic <sup>(2)</sup>             | LED Diode, T-1 3/4, Red Clear                                             | 1    |

| D2                                | P300-ND/P301-ND | Vishay <sup>(1)</sup>                | T-1 3/4, Red LED                                                          | 1    |

| J2, J3, J4,<br>J6                 | 111-0702-001    | Johnson<br>Components <sup>(3)</sup> | Red, Insulated Thumb Nut Binding Post (Jumped Together)                   | 4    |

| J5                                | BLM21A102F      | Murata <sup>(4)</sup>                | Black, Insulated Thumb Nut Binding Post, GND (Jumped to V <sub>EE</sub> ) | 1    |

| Q1                                | 459-2598-5-ND   | NTE <sup>(5)</sup>                   | 2N2222A Buffer/Driver Transistor, NPN                                     | 1    |

| R1                                | CRCW04023500F   | Vishay <sup>(1)</sup>                | 350Ω Resistor, 2%, Size 0402                                              | 1    |

| R2                                | CRCW04026800F   | Vishay <sup>(1)</sup>                | 680Ω Resistor, 2%, Size 0402                                              | 1    |

| R3, R8,<br>R9, R10                | CRCW04021001F   | Vishay <sup>(1)</sup>                | 1kΩ Pull-up Resistor, 2%, Size 1206                                       | 4    |

| R11-R16,<br>R28-R30,<br>R32       | CRCW04021820F   | Vishay <sup>(1)</sup>                | 182Ω Resistor, 2%, Size 0402                                              | 10   |

| R21                               | CRCW06031300F   | Vishay <sup>(1)</sup>                | 130Ω Resistor, 2%, Size 0603                                              | 1    |

| R22                               | CRCW04021820F   | Vishay <sup>(1)</sup>                | 12.1kΩ Resistor, 2%, Size 1206                                            | 1    |

| R23, R24                          | CRCW04022825F   | Vishay <sup>(1)</sup>                | 82Ω Resistor, 2%, Size 0402                                               | 2    |

| R25, R26                          | CRCW04021300F   | Vishay <sup>(1)</sup>                | 130Ω Resistor, 2%, Size 0402                                              | 2    |

| R27                               | CRCW0402OOR0F   | Vishay <sup>(1)</sup>                | 0Ω Resistor, 2%, Size 0402                                                | 1    |

| R31                               | CRCW04025000F   | Vishay <sup>(1)</sup>                | 50Ω Resistor, 2%, Size 0402                                               | 1    |

| SMA1-<br>SMA10                    | 142-0701-851    | Johnson<br>Components <sup>(3)</sup> | End Launch SMA Jack                                                       | 10   |

| SP1-SP6                           |                 |                                      | Solder Jump Option                                                        | 6    |

| SW1                               | CT2068-ND       | CTS <sup>(6)</sup>                   | 8-Position, Top Actuated Slide Dip Switch                                 | 1    |

| U1                                | SY69753AL       | Micrel, Inc. <sup>(7)</sup>          | Low-Power 3.3V 125Mbps to 155Mbps Clock and Data Recovery                 | 1    |

| U2                                | SY89322V        | Micrel, Inc. <sup>(7)</sup>          | 3.3/5V Dual LVTTL/LVCMOS-to-Differential LVPECL Translator                | 1    |

### Notes:

1. Vishay: www.vishay.com.

Panasonic: <u>www.panasonic.com</u>.

Johnson Components: <u>www.johnson-components.com</u>. 3.

4. Murata: www.murata.com. NTE: www.nte.com. CTS: www.cts.com 6.

Micrel, Inc: www.micrel.com.

# **Bill of Materials (DC-Coupled)**

| Item                              | Part Number     | Manufacturer                         | Description                                                               | Qty. |

|-----------------------------------|-----------------|--------------------------------------|---------------------------------------------------------------------------|------|

| C6                                | 293D685X0025B2T | Vishay <sup>(1)</sup>                | 6.8μF, 25V, Tantalum Capacitor, Size B                                    | 1    |

| C7                                | VJ206Y103JXJAT  | Vishay <sup>(1)</sup>                | 0.01µF Ceramic Capacitor, Size 1206, X7R Dielectric                       | 1    |

| C10, C11                          | VJ0603Y105JXJAT | Vishay <sup>(1)</sup>                | 1.0µF Ceramic Capacitor, Size 0603, X7R Dielectric                        | 2    |

| C12-C15,<br>C18, C19,<br>C27, C28 | VJ0402Y104JXJAT | Vishay <sup>(1)</sup>                | 0.1μF Ceramic Capacitor, Size 0402, X7R Dielectric                        | 8    |

| C20-C26                           | VJ0402Y104JXJAT | Vishay <sup>(1)</sup>                | 0.01µF Ceramic Capacitor, Size 1206, X7R Dielectric                       | 7    |

| D1                                | P301-ND         | Panasonic <sup>(2)</sup>             | LED Diode, T-1 3/4, Red Clear                                             | 1    |

| D2                                | P300-ND/P301-ND | Vishay <sup>(1)</sup>                | T-1 3/4, Red LED                                                          | 1    |

| J2, J3, J4,<br>J6                 | 111-0702-001    | Johnson<br>Components <sup>(3)</sup> | Red, Insulated Thumb Nut Binding Post (Jumped Together)                   | 4    |

| J5                                | BLM21A102F      | Johnson<br>Components <sup>(3)</sup> | Black, Insulated Thumb Nut Binding Post, GND (Jumped to V <sub>EE</sub> ) | 1    |

| Q1                                | 459-2598-5-ND   | NTE <sup>(5)</sup>                   | 2N2222A Buffer/Driver Transistor, NPN                                     | 1    |

| R1                                | CRCW04023500F   | Vishay <sup>(1)</sup>                | 350Ω Resistor, 2%, Size 0402                                              | 1    |

| R2                                | CRCW04026800F   | Vishay <sup>(1)</sup>                | 680Ω Resistor, 2%, Size 0402                                              | 1    |

| R3, R8,<br>R9, R10                | CRCW04021001F   | Vishay <sup>(1)</sup>                | 1kΩ Pull-up Resistor, 2%, Size 1206                                       | 4    |

| R15, R16,<br>R30, R32             | CRCW04021820F   | Vishay <sup>(1)</sup>                | 182Ω Resistor, 2%, Size 0402                                              | 10   |

| R21                               | CRCW06031300F   | Vishay <sup>(1)</sup>                | 130Ω Resistor, 2%, Size 0603                                              | 1    |

| R22                               | CRCW04021820F   | Vishay <sup>(1)</sup>                | 12.1kΩ Resistor, 2%, Size 1206                                            | 1    |

| R23, R24                          | CRCW04022825F   | Vishay <sup>(1)</sup>                | 82Ω Resistor, 2%, Size 0402                                               | 2    |

| R27                               | CRCW0402OOR0F   | Vishay <sup>(1)</sup>                | 0Ω Resistor, 2%, Size 0402                                                | 1    |

| R31                               | CRCW04025000F   | Vishay <sup>(1)</sup>                | 50Ω Resistor, 2%, Size 0402                                               | 1    |

| SMA1-<br>SMA10                    | 142-0701-851    | Johnson<br>Components <sup>(3)</sup> | End Launch SMA Jack                                                       | 10   |

| SP1-SP6                           |                 |                                      | Solder Jump Option                                                        | 6    |

| SW1                               | CT2068-ND       | CTS <sup>(6)</sup>                   | 8-Position, Top Actuated Slide Dip Switch                                 | 1    |

| U1                                | SY69753AL       | Micrel, Inc. <sup>(7)</sup>          | Low-Power 3.3V 125Mbps to 155Mbps Clock and Data Recovery                 | 1    |

| U2                                | SY89322V        | Micrel, Inc. <sup>(7)</sup>          | 3.3/5V Dual LVTTL/LVCMOS-to-Differential LVPECL Translator                | 1    |

#### Notes:

Vishay: <a href="https://www.vishay.com">www.vishay.com</a>.

Panasonic: <a href="https://www.panasonic.com">www.panasonic.com</a>.

3. Johnson Components: www.johnson-components.com.

4. Murata: <a href="www.murata.com">www.murata.com</a>.5. NTE: <a href="www.nte.com">www.nte.com</a>.6. CTS: <a href="www.uts.com">www.uts.com</a>.

7. Micrel, Inc: www.micrel.com.

SY69753AL Micrel, Inc.

### **Appendix A**

#### **Layout and General Suggestions**

- 1. Establish controlled impedance stripline, microstrip, or coplanar construction techniques.

- Signal paths should have approximately the same width as the device pads.

- All differential paths are critical timing paths, where skew should be matched to within ±10ps.

- Signal trace impedance should not vary more than ±5%. If in doubt, perform TDR analysis of all high-speed signal traces.

- Maintain compact filter networks as close to filter pins as possible. Provide ground plane relief under filter path

- to reduce stray capacitance. Be careful of crosstalk coupling into the filter network.

- Maintain low jitter on the REFCLK input. Isolate the XTAL oscillator from power supply noise by adequately decoupling. Keep XTAL oscillator close to device, and minimize capacitive coupling from adjacent signals.

- Higher speed operation may require use of fundamental-tone (third-overtone typically has more jitter) crystal-based oscillator for optimum performance. Evaluate and compare candidates by measuring TXCLK jitter.

- All unused outputs require termination. To conserve power, unused PECL outputs can be terminated with a 1kΩ resistor to VEE.

SY69753AL Micrel, Inc.

### **Package Information**

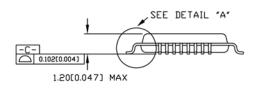

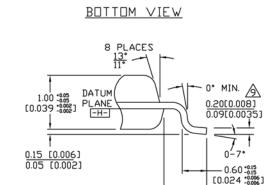

TOP VIEW

SIDE VIEW

.00[0.276] BSC

3.5 ÷0.30 = (0.138 ±0.012)

DETAIL "A"

1.00[0.039] REF.-

DIMENSIONS ARE IN MM(INCHES).

CONTROLLING DIMENSION: MM.

DIMENSION DOES NOT INCLUDE MOLD FLASH OR PROTRUSIONS, EITHER OF WHICH SHALL NOT EXCEED 0.254 (0.010). LEAD DIMENSION DOES NOT INCLUDE DAMBAR

PACKAGE TOP DIMENSIONS ARE SMALLER THAN BOTTOM DIMENSIONS AND TOP OF PACKAGE WILL NOT OVERHANG BOTTOM OF PACKAGE.

8. EXPOSED PAD SHALL BE COPLANAR WITH PACKAGE BOTTOM WITHIN 0.05mm

EXPOSED PAD: Cu WITH Sn/Pb PLATING

DIMENSION INCLUDES LEAD FINISH.

32-Pin Package Type (H32-1)

### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2006 Micrel, Incorporated.