# **Signetics**

# 74199 Shift Register

8-Bit Parallel-Access Shift Register Product Specification

### **Logic Products**

### **FEATURES**

- Buffered clock and control inputs

- Shift right and parallel load capability

- Fully synchronous data transfers

- J-K (D) inputs to first stage

- Clock enable for hold (do nothing) mode

- Asynchronous Master Reset DESCRIPTION

The functional characteristics of the '199 8-Bit Parallel-Access Shift Register are indicated in the Logic Diagram and Function Table. The device is useful in a wide variety of shifting, counting and storage applications. It performs serial, parallel, serial to parallel, or parallel to serial data transfers at very high speeds.

| TYPE  | TYPICAL fMAX | TYPICAL SUPPLY CURRENT |  |  |

|-------|--------------|------------------------|--|--|

| 74199 | 35MHz        | 90mA                   |  |  |

#### ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V ±5%; T <sub>A</sub> = 0°C to +70°C |

|-------------|-----------------------------------------------------------------------------|

| Plastic DIP | N74199N                                                                     |

#### NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

# INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS                            | DESCRIPTION      | 74   |

|---------------------------------|------------------|------|

| All                             | Inputs           | 1ul  |

| Q <sub>0</sub> – Q <sub>7</sub> | Parallel outputs | 10ul |

#### NOTE:

A 74 unit load (uI) is understood to be  $40\mu A~I_{IH}$  AND -1.6mA  $I_{IL}$

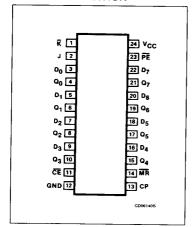

### PIN CONFIGURATION

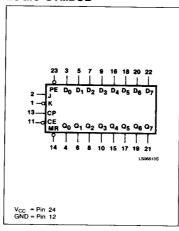

LOGIC SYMBOL

LOGIC SYMBOL (IEEE/IEC)

December 4, 1985 5-395

853-0545 81500

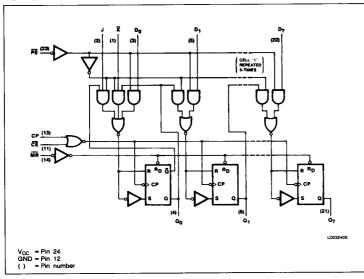

#### LOGIC DIAGRAM

## MODE SELECT - FUNCTION TABLE

| OPERATING<br>MODE           |    |    | IN               | IPUTS |   |   |                |                | OUTPUTS                                                           |

|-----------------------------|----|----|------------------|-------|---|---|----------------|----------------|-------------------------------------------------------------------|

|                             | MR | СР | CE               | PĒ    | J | ĸ | Dn             | Q <sub>0</sub> | Q <sub>1</sub> Q <sub>6</sub> Q <sub>7</sub>                      |

| Reset (clear)               | L  | х  | х                | ×     | Х | х | Х              | L              | L L L                                                             |

| Shift, set<br>first stage   | н  | 1  | ı                | h     | h | h | х              | Н              | q <sub>0</sub> q <sub>5</sub> q <sub>6</sub>                      |

| Shift, reset<br>first stage | н  | 1  | 1                | h     | ı | ı | х              | L              | <b>q</b> <sub>0</sub> <b>q</b> <sub>5</sub> <b>q</b> <sub>6</sub> |

| Shift, toggle first stage   | н  | 1  | 1                | h     | h | i | х              | q <sub>o</sub> | q <sub>0</sub> q <sub>5</sub> q <sub>6</sub>                      |

| Shift, retain first stage   | Н  | 1  | ,                | h     | ı | h | х              | q <sub>0</sub> | q <sub>0</sub> q <sub>5</sub> Q <sub>6</sub>                      |

| Parallel load               | Н  | 1  | 1                | ı     | х | х | d <sub>n</sub> | d <sub>0</sub> | d <sub>1</sub> d <sub>6</sub> d <sub>7</sub>                      |

| Hold<br>(do nothing)        | Н  | 1  | h <sup>(a)</sup> | х     | × | х | х              | qo             | q <sub>1</sub> q <sub>6</sub> q <sub>7</sub>                      |

H = HIGH voltage level steady state.

h = HIGH voltage level one set-up time prior to the LOW-to-HIGH clock transition.

L = LOW voltage level steady state.

I = LOW voltage level one set-up time prior to the LOW-to-HIGH clock transition.

X = Don't care

$d_n(q_n)$  = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the LOW-to-HIGH clock transition.

1 = LOW-to-HIGH clock transition.

NOTE:

a. The LOW-to-HIGH transition of  $\overline{\text{CE}}$  should only occur while CP is HIGH for conventional operation.

The '199 operates in two primary modes: shift right (Q0 -> Q1) and parallel load, which are controlled by the state of the Parallel Enable (PE) input. Serial data enters the first flip-flop  $(Q_0)$  via the J and  $\overline{K}$  inputs when the  $\overline{PE}$  input is HIGH, and is shifted one bit in the direction  $Q_0 \rightarrow Q_1 \rightarrow Q_3$  following each LOW-to-HIGH clock transition. The J and  $\overline{\mathsf{K}}$  inputs provide the flexibility of the J-K type input for special applications and, by tying the two pins together, the simple D-type input for general applications. The device appears as eight common clocked D flip-flops when the PE input is LOW. After the LOW-to-HIGH clock transition, data on the parallel inputs  $(D_0 - D_7)$ is transferred to the respective Q0-Q7 out-

All parallel and serial data transfers are synchronous, occuring after each LOW-to-HIGH clock transition. The '199 utilizes edge-triggering, therefore, there is no restriction on the activity of the J, K,  $D_{\rm n}$ , and  $\overline{\rm PE}$  inputs for logic operation, other than the set-up and release time requirements.

The clock input is a gated OR structure which allows one input to be used as an active-LOW Clock Enable ( $\overline{CE}$ ) input. The pin assignment for the CP and  $\overline{CE}$  inputs is arbitrary and can be reversed for layout convenience. The LOW-to-HIGH transition of  $\overline{CE}$  input should only take place while the CP is HIGH for conventional operation.

A LOW on the Master Reset (MR) input overrides all other inputs and clears the register asynchronously, forcing all bit positions to a LOW state.

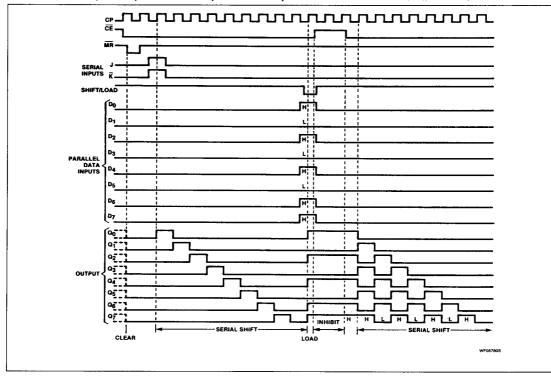

# TYPICAL CLEAR, LOAD, RIGHT-SHIFT, LEFT-SHIFT, INHIBIT AND CLEAR SEQUENCES

# ABSOLUTE MAXIMUM RATINGS (Over operating free-air temperature range unless otherwise noted.)

|                  | PARAMETER                                      | 74                       | UNIT |

|------------------|------------------------------------------------|--------------------------|------|

| V <sub>CC</sub>  | Supply voltage                                 | 7.0                      | ٧    |

| V <sub>IN</sub>  | Input voltage                                  | -0.5 to +5.5             | V    |

| I <sub>IN</sub>  | Input current                                  | -30 to +5                | mA   |

| V <sub>OUT</sub> | Voltage applied to output in HIGH output state | -0.5 to +V <sub>CC</sub> | V    |

| TA               | Operating free-air temperature range           | 0 to 70                  | °C   |

### RECOMMENDED OPERATING CONDITIONS

|                 | DADAMETED                      |      |     |      |      |

|-----------------|--------------------------------|------|-----|------|------|

|                 | PARAMETER                      | Min  | Nom | Max  | UNIT |

| V <sub>CC</sub> | Supply voltage                 | 4.75 | 5.0 | 5.25 | V    |

| V <sub>IH</sub> | HIGH-level input voltage       | 2.0  |     |      | V    |

| V <sub>IL</sub> | LOW-level input voltage        |      |     | +0.8 | V    |

| l <sub>IK</sub> | Input clamp current            |      |     | -12  | mA   |

| loн             | HIGH-level output current      |      |     | -800 | v    |

| loL             | LOW-level output current       |      |     | 16   | mA   |

| T <sub>A</sub>  | Operating free-air temperature | 0    |     | 70   | °C   |

December 4, 1985

# DC ELECTRICAL CHARACTERISTICS (Over recommended operating free-air temperature range unless otherwise noted.)

| PARAMETER       |                                           |                                                                   |     |                  |      |      |

|-----------------|-------------------------------------------|-------------------------------------------------------------------|-----|------------------|------|------|

|                 |                                           | TEST CONDITIONS <sup>1</sup>                                      | Min | Typ <sup>2</sup> | Max  | UNIT |

| V <sub>OH</sub> | HIGH-level output voltage                 | $V_{CC} = MIN$ , $V_{IH} = MIN$ , $V_{IL} = MAX$ , $I_{OH} = MAX$ | 2.4 | 3.4              |      | ٧    |

| V <sub>OL</sub> | LOW-level output voltage                  | $V_{CC} = MIN$ , $V_{IH} = MIN$ , $V_{IL} = MAX$ , $I_{OL} = MAX$ |     | 0.2              | 0.4  | ٧    |

| V <sub>IK</sub> | Input clamp voltage                       | $V_{CC} = MIN$ , $I_I = I_{IK}$                                   |     |                  | -1.5 | ٧    |

| կ               | Input current at maximum input voltage    | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5V                      |     |                  | 1.0  | mA   |

| l <sub>iH</sub> | HIGH-level input current                  | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.4V                      |     |                  | 40   | μΑ   |

| I <sub>IL</sub> | LOW-level input current                   | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.4V                      |     |                  | -1.6 | mA   |

| los             | Short-circuit output current <sup>3</sup> | V <sub>CC</sub> = MAX                                             | -18 |                  | -57  | mA   |

| Icc             | Supply current <sup>4</sup> (total)       | V <sub>CC</sub> = MAX                                             |     | 90               | 127  | mA   |

#### NOTES:

### AC ELECTRICAL CHARACTERISTICS TA = 25°C, VCC = 5.0V

|                                      |                                      | TEST CONDITIONS | C <sub>L</sub> = 15pF, | UNIT     |     |

|--------------------------------------|--------------------------------------|-----------------|------------------------|----------|-----|

|                                      |                                      |                 | Min                    | Max      |     |

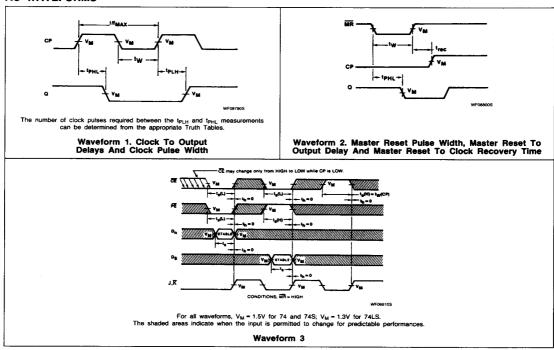

| f <sub>MAX</sub>                     | Maximum clock frequency              | Waveform 1      | 25                     |          | MHz |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Clock to output | Waveform 1      |                        | 26<br>30 | ns  |

| t <sub>PHL</sub>                     | Propagation delay                    | Waveform 2      |                        | 35       | ns  |

Per industry convention,  $f_{\text{MAX}}$  is the worst case of the maximum device operating frequency with no constraints on  $t_{\text{f}}$ ,  $t_{\text{f}}$ , pulse width or duty cycle.

### AC SET-UP REQUIREMENTS TA = 25°C, VCC = 5.0V

|                  | PARAMETER                           | TEST CONDITIONS | 7   | UNIT |     |

|------------------|-------------------------------------|-----------------|-----|------|-----|

| PARAMEICH        |                                     | 1251 CONDITIONS | Min |      | Max |

| tw               | Clock pulse width                   | Waveform 1      | 20  |      | ns  |

| tw               | MR pulse width                      | Waveform 2      | 20  |      | ns  |

| ts               | Set-up time, J, K and data to clock | Waveform 3      | 20  |      | ns  |

| th               | Hold time, J, K and data to clock   | Waveform 3      | 0   |      | ns  |

| ts               | Set-up time, CE to clock            | Waveform 3      | 30  |      | ns  |

| t <sub>h</sub>   | Hold time, CE to clock              | Waveform 3      | 0   |      | ns  |

| t <sub>s</sub>   | Set-up time, PE to clock            | Waveform 3      | 30  |      | ns  |

| t <sub>h</sub>   | Hold time, PE to clock              | Waveform 3      | 0   |      | ns  |

| t <sub>rec</sub> | Recovery time, MR to clock          | Waveform 2      | 30  |      | ns  |

December 4, 1985

<sup>1.</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

<sup>2.</sup> All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C.

<sup>3.</sup> I<sub>OS</sub> is tested with V<sub>OUT</sub> = +0.5V and V<sub>CC</sub> = V<sub>CC</sub> MAX + 0.5V. Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second.

<sup>4.</sup> Measure I<sub>CC</sub> with  $\overline{K}$ , J and D inputs at 4.5V, momentary ground clock, then apply 4.5V, ground  $\overline{CE}$ ,  $\overline{MR}$  and  $\overline{PE}$ .

#### **AC WAVEFORMS**

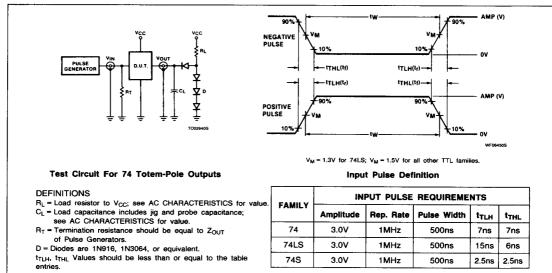

### TEST CIRCUITS AND WAVEFORMS

December 4, 1985