# DS34RT5110 DVI, HDMI Retimer with Input Equalization and Output De-Emphasis

Check for Samples: DS34RT5110

## **FEATURES**

- Optimized for HDMI/DVI Repeater Applications

- TMDS compatible Inputs with Configurable Receive Equalization Supporting Data Rates up to 3.4 Gbps

- TMDS compatible Outputs with Configurable Transmit De-Emphasis

- Dedicated CDR on Each Data Channel Reduces Jitter Transfer, Enabling Multiple Devices to be Cascaded without Impairing Signal Fidelity

- Capable of Multi-Hop Extension of HDMI/DVI Applications at Data Rates between 250 Mbps and 3.4 Gbps

- Resistor Adjustable Differential Output Voltage for AC Coupled Cat5e and Cat6 Extension Applications

- 2 Equalizer Settings for a Wide Range of Cable Reaches at Different Data Rates

- Total Output Jitter of 0.09 UI at 2.25 Gbps

- Total Output Jitter of 0.10 UI at 3.4 Gbps

- DVI 1.0 and HDMI v1.3a Compatible TMDS Source and Sink Interface

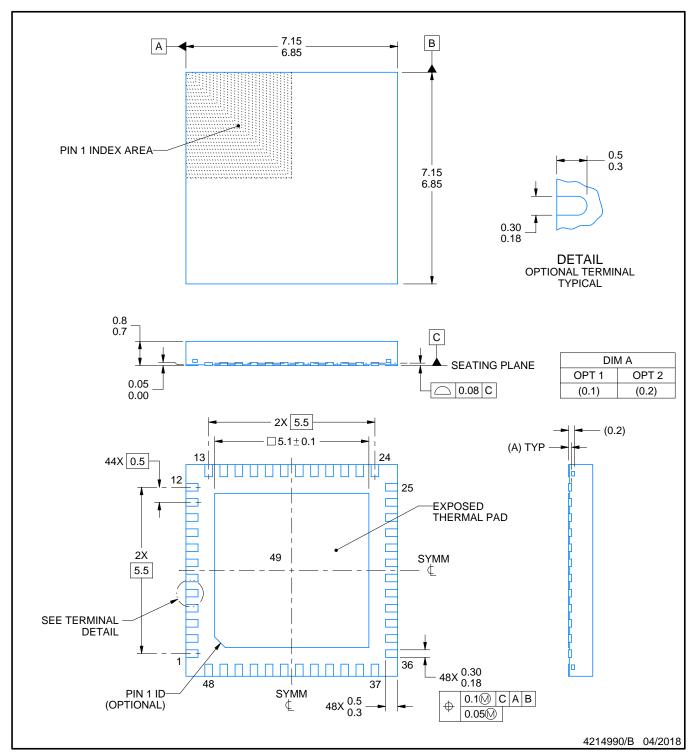

- 7 mm x 7 mm 48 Pin WQFN Package

- >8 kV HBM ESD Protection

- 0 °C to +70 °C Operating Temperature

# **APPLICATIONS**

- Repeater Applications

- Digital Routers

- HDMI / DVI Extender Multi-Hops

- Source Applications

- Video Cards

- Blu-ray DVD Players

- Game Consoles

- Sink Applications

- High Definition Displays

- Projectors

### DESCRIPTION

The DS34RT5110 is a 10.2 Gbps (3 x 3.4 Gbps) high performance re-clocking device that supports 3 Transition Minimized Differential Signaling (TMDS) data channels and a single clock channel over DVI™ v1.0, and HDMI™ v1.3a data rates up to 3.4 Gbps for each data channel. The device incorporates a configurable receive equalizer, a clock and data recovery (CDR) circuit and a de-emphasis driver on each data channel. The clock channel feeds a high-performance phase-locked loop (PLL) that regenerates a low jitter output clock for data recovery.

The DS34RT5110 equalizes and retimes greater than 25 meters 28 AWG of HDMI cable for 1080p resolution with 12 bit deep color depth (2.25 Gbps), to a low jitter version of the clock and data signal outputs, reducing both deterministic and random jitter. Several devices can be cascaded for long links without degrading signal fidelity. Obtaining total jitter is 0.09 UI or less over the supported data rates. This low level of output jitter provides system designers with extra margin and flexibility when working with stringent timing budgets.

The transmitter supports configurable transmit deemphasis so the output can be optimized for driving additional lengths of cables or FR4 traces.

₩.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

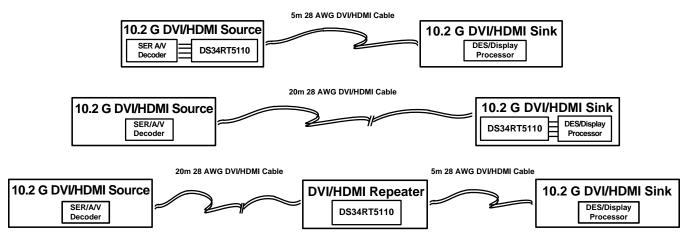

## **Application Diagram**

### **PIN DESCRIPTIONS**

| Pin Name           | Pin Number       | I/O, Type    | Description                                                                                                                                                                   |

|--------------------|------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Speed D       | Differential I/O |              |                                                                                                                                                                               |

| C_IN-<br>C_IN+     | 1<br>2           | I, CML       | Inverting and non-inverting TMDS Clock inputs to the equalizer. An on-chip 50 $\Omega$ terminating resistor connects C_IN+ to V <sub>DD</sub> and C_IN- to V <sub>DD</sub> .  |

| D_IN0+             | 4<br>5           | I, CML       | Inverting and non-inverting TMDS Data inputs to the equalizer. An on-chip 50 $\Omega$ terminating resistor connects D_IN0+ to V <sub>DD</sub> and D_IN0- to V <sub>DD</sub> . |

| D_IN1-<br>D_IN1+   | 8<br>9           | I, CML       | Inverting and non-inverting TMDS Data inputs to the equalizer. An on-chip 50 $\Omega$ terminating resistor connects D_IN1+ to V <sub>DD</sub> and D_IN1- to V <sub>DD</sub> . |

| D_IN2-<br>D_IN2+   | 11<br>12         | I, CML       | Inverting and non-inverting TMDS Data inputs to the equalizer. An on-chip 50 $\Omega$ terminating resistor connects D_IN2+ to V <sub>DD</sub> and D_IN2- to V <sub>DD</sub> . |

| C_OUT-<br>C_OUT+   | 36<br>35         | O, CML       | Inverting and non-inverting TMDS outputs from the equalizer. Open collector.                                                                                                  |

| D_OUT0-<br>D_OUT0+ | 33<br>32         | O, CML       | Inverting and non-inverting TMDS outputs from the equalizer. Open collector.                                                                                                  |

| D_OUT1-<br>D_OUT1+ | 29<br>28         | O, CML       | Inverting and non-inverting TMDS outputs from the equalizer. Open collector.                                                                                                  |

| D_OUT2-<br>D_OUT2+ | 26<br>25         | O, CML       | Inverting and non-inverting TMDS outputs from the equalizer. Open collector.                                                                                                  |

| Equalization       | Control          |              |                                                                                                                                                                               |

| EQ2<br>EQ1<br>EQ0  | 37<br>38<br>39   | I, LVCMOS    | EQ2, EQ1 and EQ0 select the equalizer boost level for EQ channels. Internally pulled LOW as default. Refer to Table 1.                                                        |

| De-Emphasis        | Control          | ii.          |                                                                                                                                                                               |

| DE1<br>DE0         | 42<br>43         | I,<br>LVCMOS | DE1, DE0 select the DE-emphasis level for output drivers. Internally pulled low as default. Refer to Table 2.                                                                 |

| Device Contr       | ol               |              |                                                                                                                                                                               |

| BYPASS             | 47               | I,<br>LVCMOS | Reclocker enable control. Internally pulled low as default. H = Reclock and De-Emphasis function is bypassed. L = Normal operation.                                           |

| EN                 | 44               | I, LVCMOS    | Enable Output Drivers. Internally pulled HIGH as default. H = normal operation (enabled). L = standby mode.                                                                   |

| MODE               | 21               | I, LVCMOS    | Clock channel mode control. Internally pulled LOW as default.  H = Clock channel is bypassed.  L = Normal operation.                                                          |

| SD                 | 45               | O, LVCMOS    | Signal Detect Output pin. H = signal detected on all channels. L = no signal detected on one or more channels.                                                                |

## **PIN DESCRIPTIONS (continued)**

| Pin Name        | Pin Number                    | I/O, Type    | Description                                                                                                                                                                                                                                           |

|-----------------|-------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOCK            | 14                            | O, LVCMOS    | Lock Indicator Output pin. H = PLL is locked. L = PLL is not locked.                                                                                                                                                                                  |

| VOD_CRL         | 48                            | I,<br>Analog | VOD control pin. Refer to Table 3. See Functional Description. External resistance = $24 \text{ k}\Omega$ to GND, Output DC Coupled Application. External resistance = $12 \text{ k}\Omega$ to GND, Output AC Coupled Application.                    |

| LFp<br>LFn      | 40<br>41                      | I,<br>Analog | Loop filter capacitor pins. See Functional Description.                                                                                                                                                                                               |

| Power           | •                             |              |                                                                                                                                                                                                                                                       |

| V <sub>DD</sub> | 3, 6, 7,<br>10, 13,<br>15, 46 | Power        | $V_{DD}$ = 3.3 V ±5%. $V_{DD}$ pins should be tied to the $V_{DD}$ plane through a low inductance path. A 0.1 µF bypass capacitor should be connected between each $V_{DD}$ pin to the GND planes. See POWER SUPPLY BYPASSING for additional details. |

| GND             | 22, 24,<br>27, 30,<br>31, 34  | GND          | Ground reference. GND should be tied to a solid ground plane through a low impedance path.                                                                                                                                                            |

| Exposed<br>DAP  | DAP                           | GND          | Ground reference. The exposed pad at the center of the package must be connected to the ground plane.                                                                                                                                                 |

| Other           |                               |              |                                                                                                                                                                                                                                                       |

| Reserv          | 16, 17,<br>18, 19,<br>20, 23  |              | Reserved. Do not connect. Leave open.                                                                                                                                                                                                                 |

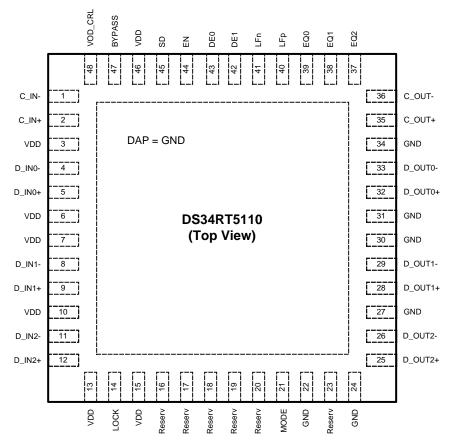

## **Connection Diagram**

TOP VIEW — Not to Scale

48 Pin WQFN Package See Package Number RHS0048A

Product Folder Links: DS34RT5110

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

**Absolute Maximum Ratings**(1)(2)

| Abootato maximam ratingo                        |                                    |  |  |  |  |

|-------------------------------------------------|------------------------------------|--|--|--|--|

| Supply Voltage (V <sub>DD</sub> )               |                                    |  |  |  |  |

|                                                 | -0.5V to (V <sub>DD</sub> + 0.5) V |  |  |  |  |

|                                                 | -0.5V to (V <sub>DD</sub> + 0.5) V |  |  |  |  |

| CML Input/Output Voltage                        |                                    |  |  |  |  |

|                                                 | +125°C                             |  |  |  |  |

| Storage Temperature                             |                                    |  |  |  |  |

| Lead Temp. (Soldering, 5 sec.)                  |                                    |  |  |  |  |

| HBM, 1.5 kΩ, 100 pF                             | >8 kV                              |  |  |  |  |

| Thermal Resistance θ <sub>JA</sub> , No Airflow |                                    |  |  |  |  |

|                                                 | HBM, 1.5 kΩ, 100 pF                |  |  |  |  |

<sup>(1) &</sup>quot;Absolute Maximum Ratings" are the ratings beyond which the safety of the device cannot be ensured. They are not meant to imply that the device should be operated at these limits.

# Recommended Operating Conditions (1)(2)

|                                                          | Min   | Тур | Max   | Units |

|----------------------------------------------------------|-------|-----|-------|-------|

| Supply Voltage (V <sub>DD</sub> to GND)                  | 3.135 | 3.3 | 3.465 | V     |

| Supply Noise Tolerance (100 Hz to 50 MHz) <sup>(3)</sup> |       | 100 |       | mVp-p |

| Ambient Temperature                                      | 0     | 25  | +70   | °C    |

<sup>(1)</sup> Typical parameters are measured at V<sub>DD</sub> = 3.3 V, T<sub>A</sub> = 25 °C. They are for reference purposes, and are not production-tested.

<sup>(2)</sup> If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

<sup>2)</sup> Parameter is ensured by statistical analysis and/or design.

<sup>(3)</sup> Allowed supply noise (mVp-p sine wave) at typical condition.

## **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. All parameters are ensured by test, statistical analysis, or design unless otherwise specified (1)

| Symbol        | Parameter                                    | Condition                                                                                                                                          | Min                   | Тур  | Max                   | Units |

|---------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| Power         | <u>.</u>                                     |                                                                                                                                                    |                       |      |                       |       |

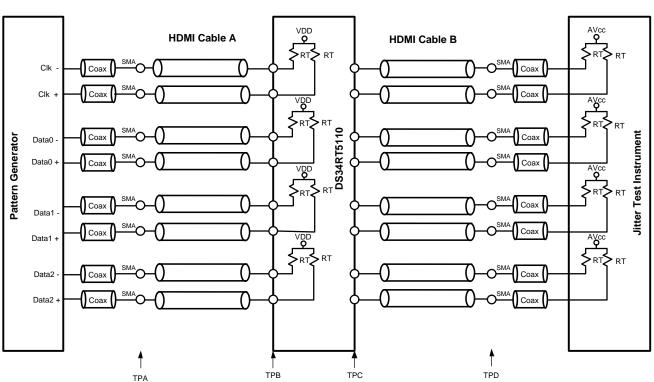

| P             | Power Supply                                 | EN = H, Device Enabled<br>PRBS15 pattern,<br>fCLK=340 MHz<br>RT= 50Ω to AV <sub>CC</sub> , Figure 2                                                |                       | 1100 | 1250                  | mW    |

| ۲             | Consumption                                  | EN = L, Standby Mode<br>PRBS15 pattern,<br>fCLK=340 MHz<br>RT= $50\Omega$ to AV <sub>CC</sub> , Figure 2                                           |                       | 850  | 1000                  | mW    |

| LVCMOS / LV   | TTL DC Specification                         | is                                                                                                                                                 |                       |      |                       |       |

| VIH           | High Level Input<br>Voltage                  |                                                                                                                                                    | 2                     |      | V <sub>DD</sub>       | V     |

| VIL           | Low Level Input<br>Voltage                   |                                                                                                                                                    | GND                   |      | 0.8                   | V     |

| VOH           | High Level Output Voltage                    | IOH = -3 mA                                                                                                                                        | 2.4                   |      |                       | V     |

| VOL           | Low Level Output<br>Voltage                  | IOL = 3 mA                                                                                                                                         |                       |      | 0.4                   | V     |

| IIH           | Input High Current                           | VIN = V <sub>DD</sub> , EQ2, EQ1, EQ0,<br>DE1, DE0, BYPASS, MODE<br>pins (pull down)                                                               |                       |      | 60                    | μΑ    |

|               |                                              | $VIN = V_{DD}$ , EN pin (pull up)                                                                                                                  | -15                   |      |                       | μA    |

| IIL           | Input Low Current                            | VIN = 0 V, EQ2, EQ1, EQ0,<br>DE1, DE0, BYPASS, MODE<br>pins (pull down)                                                                            |                       |      | 15                    | μΑ    |

|               |                                              | VIN = 0 V, EN pin (pull up)                                                                                                                        | -20                   |      |                       | μA    |

| Signal Detect |                                              |                                                                                                                                                    |                       |      |                       |       |

| SDH           | Signal Detect High                           | Default Input signal level to assert SD pin                                                                                                        |                       | 80   |                       | mVp-p |

| SDL           | Signal Detect Low                            | Default Input signal level to deassert SD                                                                                                          |                       | 20   |                       | mVp-p |

| CML Inputs    |                                              |                                                                                                                                                    |                       |      |                       |       |

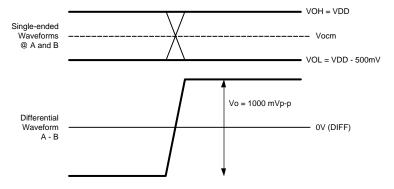

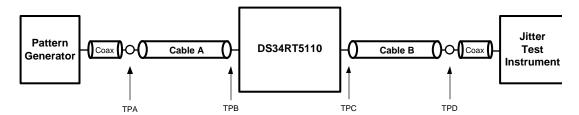

| VTX           | Input Voltage<br>Swing (Launch<br>Amplitude) | Measured differentially at TPA, Figure 1 (2)                                                                                                       | 800                   | 1000 | 1560                  | mVp-p |

| VICMDC        | Input Common-<br>Mode Voltage                | DC-Coupled requirement<br>Measured at TPB,<br>VINmin = 800mV,<br>VINmax = 1200mV, Figure 1                                                         | V <sub>DD</sub> -0.3  |      | V <sub>DD</sub> -0.2  | V     |

| VIN           | Input Voltage<br>Sensitivity                 | Measured differentially at TPB,<br>Figure 1, 3.4 Gbps, Clock<br>Pattern                                                                            | 150                   |      | 1560                  | mVp-p |

| RIN           | Input resistance                             | IN+ to V <sub>DD</sub> and IN- to V <sub>DD</sub>                                                                                                  | 40                    | 50   | 60                    | Ohms  |

| RLI           | Differential output return loss              | 100 MHz – 1125 MHz                                                                                                                                 |                       | 10   |                       | dB    |

| CML Outputs   |                                              |                                                                                                                                                    |                       |      |                       |       |

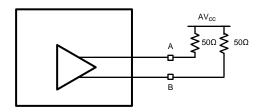

| VOFF          | Standby Output<br>Voltage                    | Measured DC outputs at TPC, RT = $50\Omega$ when DUT $V_{DD}$ is off with OUT+ and OUT-terminated by RT= $50\Omega$ to AV <sub>CC</sub> , Figure 2 | AV <sub>CC</sub> - 10 |      | AV <sub>CC</sub> + 10 | mV    |

<sup>(1)</sup> Typical parameters are measured at  $V_{DD} = 3.3 \text{ V}$ ,  $T_A = 25 \text{ °C}$ . They are for reference purposes, and are not production-tested. (2) Parameter is ensured by statistical analysis and/or design.

## **Electrical Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified. All parameters are ensured by test, statistical analysis, or design unless otherwise specified<sup>(1)</sup>.

| Symbol       | Parameter                                                               | Condition                                                                                                                                               | Min                     | Тур  | Max                     | Units |

|--------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-------------------------|-------|

| VO           | Differential Output voltage swing                                       | External resistor = 24 k $\Omega$ at VOD_CRL pin.Measured differentially with OUT+ and OUT- terminated by RT=50 $\Omega$ to AV <sub>CC</sub> , Figure 2 | 800                     |      | 1200                    | mVp-p |

| VOCM         | Output common-<br>mode Voltage                                          | Measured single-ended,<br>>1.65 Gbps, Figure 2,<br>Figure 3                                                                                             | AV <sub>CC</sub> - 0.35 |      | AV <sub>CC</sub> - 0.20 | V     |

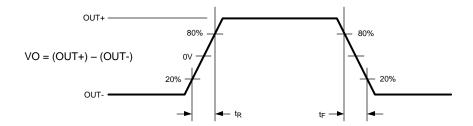

| tR, tF       | Transition time                                                         | 20% to 80% of differential<br>output voltage, measured<br>within 1" from output pins,<br>Figure 3                                                       |                         | 80   |                         | ps    |

| tCCSK        | Inter Pair Data<br>Channel-to-<br>Channel Skew (all<br>3 data channels) | Difference in 50% crossing<br>between channels<br>3.4 Gbps, Clock Pattern <sup>(2)</sup>                                                                |                         | 2    | 3                       | ps    |

| tPPSK        | Inter Pair Data<br>Channels Part-<br>toPart Skew                        | Difference in 50% crossing<br>between channels of any two<br>devices<br>3.4 Gbps, Clock Pattern                                                         |                         | 50   |                         | ps    |

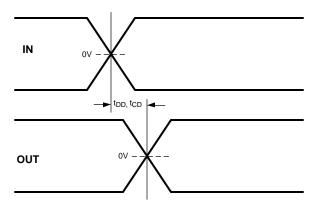

| tDD          | Data Channels<br>Latency                                                | 3.4 Gbps, Clock Pattern, Figure 4                                                                                                                       |                         | 520  |                         | ps    |

| tCD          | Clock Channel<br>Latency                                                | 3.4 Gbps, Clock Pattern, Figure 4                                                                                                                       |                         | 600  |                         | ps    |

| LVCMOS Out   | puts                                                                    |                                                                                                                                                         |                         |      |                         |       |

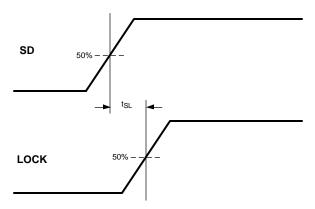

| tSL          | SD to LOCK time                                                         | Figure 4                                                                                                                                                |                         | 10   |                         | ms    |

| Bit Rate     |                                                                         |                                                                                                                                                         |                         |      |                         |       |

| fCLK         | Clock Frequency                                                         | Clock Path (3)                                                                                                                                          | 25                      |      | 340                     | MHz   |

| bR           | Bit Rate                                                                | Data Paths <sup>(3)</sup>                                                                                                                               | 0.25                    |      | 3.4                     | Gbps  |

| Data Channel | Random Jitter                                                           |                                                                                                                                                         |                         |      | 1                       |       |

| RJ           | Random Jitter                                                           | See(3)(4)(5)(6)                                                                                                                                         |                         | 3    |                         | psrms |

| Data Channel | CDR Jitter Generation                                                   | on                                                                                                                                                      |                         |      |                         | •     |

| TROJ1        | Total Output Jitter<br>0.25 Gbps                                        | Data Paths, measured at TPC PRBS7, EQ [2:0] = 000 Figure 1 (3) (4) (5)                                                                                  |                         | 0.03 | 0.05                    | Ulp-p |

| TROJ2        | Total Output Jitter<br>1.65 Gbps                                        | Data Paths, measured at TPC PRBS7, EQ [2:0] = 000 Figure 1 (3) (4) (5)                                                                                  |                         | 0.08 | 0.14                    | Ulp-p |

| TROJ3        | Total Output Jitter<br>2.25 Gbps                                        | Data Paths, measured at TPC PRBS7, EQ [2:0] = 000 Figure 1 (3) (4) (5)                                                                                  |                         | 0.09 | 0.16                    | Ulp-p |

| TROJ4        | Total Output Jitter 3.4 Gbps                                            | Data Paths, measured at TPC PRBS7, EQ [2:0] = 000 Figure 1 (3) (4) (5)                                                                                  |                         | 0.10 | 0.17                    | Ulp-p |

|              |                                                                         | 0.25 Gbps data rate                                                                                                                                     |                         | 0.25 |                         | MHz   |

| DW// OOD     | CDR Loop                                                                | 1.65 Gbps data rate                                                                                                                                     |                         | 1.65 |                         | MHz   |

| BWLOOP       | Bandwidth                                                               | 2.25 Gbps data rate                                                                                                                                     |                         | 2.25 |                         | MHz   |

|              |                                                                         | 3.4 Gbps data rate                                                                                                                                      |                         | 2.25 |                         | MHz   |

Parameter is ensured by statistical analysis and/or design.

Deterministic jitter is measured at the differential outputs (TPC of Figure 1), minus the deterministic jitter before the test channel (TPA of Figure 1). Random jitter is removed through the use of averaging or similar means.

Total Jitter is defined as peak-to-peak deterministic jitter from  $\pm$  12 times random jitter (ps). Random jitter contributed by the equalizer is defined as sq rt ( $J_{OUT}^2 - J_{IN}^2$ ).  $J_{OUT}$  is the random jitter at equalizer outputs in ps-rms, see TPC of Figure 1;  $J_{IN}$  is the random jitter at the input of the equalizer in ps-rms, see TPA of Figure 1.

## **Electrical Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified. All parameters are ensured by test, statistical analysis, or design unless otherwise specified<sup>(1)</sup>.

| Symbol                              | Parameter                      | Condition                                                 | Min | Тур  | Max   | Units |  |  |

|-------------------------------------|--------------------------------|-----------------------------------------------------------|-----|------|-------|-------|--|--|

| Clock Channel PLL Jitter Generation |                                |                                                           |     |      |       |       |  |  |

| TROJ5                               | Total Output Jitter<br>25 MHz  | Clock Path, measured at TPC Figure 1 (7)(8)(9)            |     | 0.03 | 0.045 | Ulp-p |  |  |

| TROJ6                               | Total Output Jitter<br>165 MHz | Clock Path, measured at TPC Figure 1 (7)(8)(9)            |     | 0.07 | 0.13  | Ulp-p |  |  |

| TROJ7                               | Total Output Jitter<br>225 MHz | Clock Path, measured at TPC Figure 1 <sup>(7)(8)(9)</sup> |     | 0.08 | 0.135 | Ulp-p |  |  |

| TROJ8                               | Total Output Jitter<br>340 MHz | Clock Path, measured at TPC Figure 1 (7)(8)(9)            |     | 0.09 | 0.14  | Ulp-p |  |  |

- Parameter is ensured by statistical analysis and/or design.

- Deterministic jitter is measured at the differential outputs (TPC of Figure 1), minus the deterministic jitter before the test channel (TPA of Figure 1). Random jitter is removed through the use of averaging or similar means.

Total Jitter is defined as peak-to-peak deterministic jitter from + 12 times random jitter (ps).

# **Setup and Timing Diagrams**

Figure 1. Test Setup Diagram

Figure 2. CML Output Swings at A/B (VOD\_CRL = 24 k $\Omega$ )

Figure 3. CML Output Transition Times

Figure 4. CML Latency Delay Time

Figure 5. SD - LOCK Delay Time

# **Functional Description**

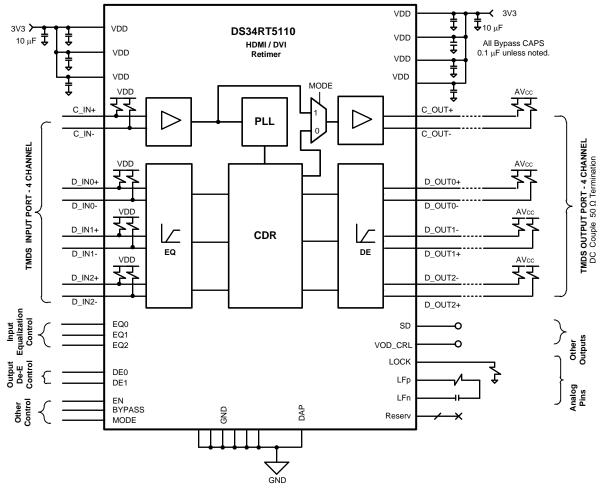

The DS34RT5110 DVI, HDMI Retimer with Input Equalization and Output De-Emphasis consists of three data channels and a clock channel. Each data channel consists of a TMDS compatible receiver with a power efficient equalizer, a dedicated clock-data recovery (CDR) unit, and a TMDS compatible transmitter.

Figure 6. Block Diagram

## PHASE-LOCKED-LOCKED LOOP (PLL)

The clock channel has a high-performance PLL that creates a low jitter sampling clock for the clock and data recovery units in the data channels. An external loop filter, composed of 2.2 nF (+ 5% tolerance) capacitor and a 3.3 k $\Omega$  (+ 5% tolerance) resistor in series, are required between the LFp and the LFn pins.

## **CLOCK-DATA RECOVERY UNIT (CDR)**

Each TMDS data channel has a CDR that operates independently from other TMDS data channels. Each CDR aligns the sampling clock edges by digitally interpolating the clock from PLL of the TMDS clock channel. The device is designed to connect to DVI/HDMI compatible transmitter and receiver at any data rate between 250 Mbps to 3.4 Gbps. The loop bandwidth of the CDR is approximately baud\_rate/1000, i.e. 2.25 MHz for 2.25 Gbps data.

## INPUT EQUALIZATION

The input data channel equalizers support eight programmable levels of equalization boost Table 1 by the EQ pins (EQ [2:0]). The range of boost settings provided enables the DS34RT5110 to address a wide range of transmission line path loss scenarios, enabling support for a variety of data rates and formats. See Application Information for recommended EQ settings.

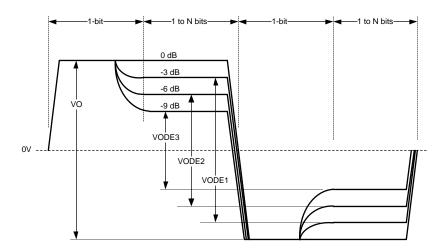

#### **OUTPUT DE-EMPHASIS**

De-emphasis is the conditioning function for use in compensating against backplane and cable transmission loss. The DS34RT5110 provides four steps of de-emphasis ranging from 0, 3, 6 and 9 dB, user-selectable dependent on the loss profile of output channels. Table 2 shows the De-emphasis control with default VO = 1000 mVp-p, and Figure 7 shows a driver de-emphasis waveform.

#### **OUTPUT VO CONTROL**

Output differential voltage (VO) is controlled through VOD\_CRL pin ties an external resistor to the ground as shown in Table 3. Users should restrict the external resistor values used to be 12 k $\Omega$  to 24 k $\Omega$ . +5% tolerance is recommended.

Table 1. Equalization Control

|     | RESULT |     |                              |

|-----|--------|-----|------------------------------|

| EQ2 | EQ1    | EQ0 | Equalization in dB (1.7 GHz) |

| 0   | 0      | 0   | 0 (default)                  |

| 0   | 0      | 1   | 10                           |

| 0   | 1      | 0   | 16                           |

| 0   | 1      | 1   | 19                           |

| 1   | 0      | 0   | 23                           |

| 1   | 0      | 1   | 25                           |

| 1   | 1      | 0   | 26                           |

| 1   | 1      | 1   | 27                           |

Table 2. De-Emphasis Control

| INP | UTS | RESULT                                                   |                      |  |

|-----|-----|----------------------------------------------------------|----------------------|--|

| DE1 | DE0 | VO De-Emphasis level in mVp-p<br>(VODE w/VOD_CRL = 24 kΩ | VO De-Emphasis in dB |  |

| 0   | 0   | 1000 (default)                                           | 0 (default)          |  |

| 0   | 1   | 710                                                      | -3                   |  |

| 1   | 0   | 500                                                      | -6                   |  |

| 1   | 1   | 355                                                      | -9                   |  |

Product Folder Links: DS34RT5110

#### **Table 3. VO Control**

| External Resistor Value (VOD_CRL pin) | Applications | VO Level (mVp-p) |

|---------------------------------------|--------------|------------------|

| 24 kΩ                                 | DC Coupled   | 1000             |

| 12 kΩ                                 | AC Coupled   | 1000             |

Figure 7. Output De-Emphasis Differential Waveform (showing all de-emphasis steps)

#### **RETIMING AND DE-EMPHASIS BYPASS**

The retiming and De-emphasis BYPASS pin provides the flexibility to configure the device to an equalizer only mode. The device is in normal operation, when holding a LOW state on the BYPASS pin. The retiming and De-emphasis features are disabled, when a HIGH state is applied.

#### **CLOCK CHANNEL MODE CONTROL**

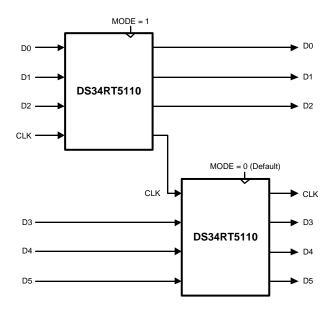

During the normal operation mode, the clock channel signal is regenerated by the PLL and the CDR. Holding a LOW state (default) on the MODE pin places the DS34RT5110 in this normal operation mode. A HIGH state on the MODE pin bypasses the clock channel. This clock channel mode feature enables the multi-hop applications. (Refer to Multiple Hop Application for detailed information)

### **DEVICE STATE AND ENABLE CONTROL**

The DS34RT5110 has an Enable feature which provides the ability to control device power consumption. This feature can be controlled via the Enable Pin (EN Pin). If Enable is activated, the data channels and clock channel are placed in the ACTIVE state and all device blocks function as described. The DS34RT5110 can also be placed in STANDBY mode to save power. In this mode, the output drivers of the device are disabled. The CML outputs are in the HIGH (AVCC) state. All LVCMOS outputs are in the HiZ state.

## **LOCK DETECT**

When the PLL of the DS34RT5110 is locked, and the generated reference phases are successfully interpolated by the CDR, this status is indicated by a logic HIGH on the LOCK pin. The LOCK pin may be connected to the Enable (EN) pin input to disable the data channels and clock channel when no data signal is being received.

## SIGNAL DETECT

The DS34RT5110 features a signal detect circuit on all channels. The status of the input signals can be determined by the state of the SD pin. A logic HIGH indicates the presence of signals that have exceeded a specified maximum threshold value (called SD\_ON) on all channels. A logic LOW means that the signals have fallen below a minimum threshold value (called SD\_OFF) on one or more channels.

Copyright © 2009–2013, Texas Instruments Incorporated

#### **AUTOMATIC ENABLE FEATURE**

During normal operation (i.e. BYPASS pin is LOW), the DS34RT5110 can be configured to automatically enter STANDBY mode, if the PLL of the DS34RT5110 is not locked. The STANDBY mode can be implemented by connecting the LOCK DETECT (LOCK) pin to the external (LVCMOS) Enable (EN) pin. If the LOCK pin is connected to the EN pin, a logic HIGH on the LOCK pin will enable the device; thus the DS34RT5110 will automatically enter the ACTIVE state. If the PLL is unlocked, then the LOCK pin will be asserted LOW, causing the aforementioned blocks to be placed in the STANDBY state.

## **APPLICATION INFORMATION**

The DS34RT5110 is a DVI/HDMI video signal reconditioning device. The device conforms to DVI v1.0 and HDMI v1.3a standards supporting up to 10.2 Gbps total throughput TMDS data for 1080p with 48 bit deep color depth.

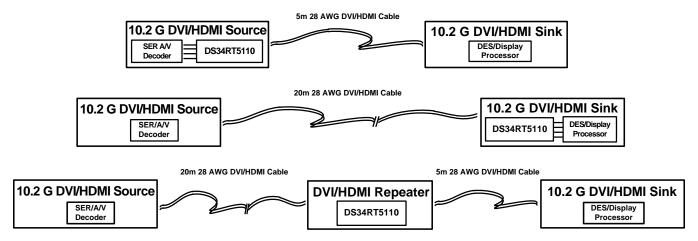

#### TYPICAL APPLICATION

In general, the DS34RT5110 in the default mode (MODE = L) is used as a DVI/HDMI source device, sink device, or a repeater device, see Figure 8. As the source device, the output de-emphasis setting should be configured based on the driving cable length. When used as the sink device, the levels of the equalization boost of the input data channels should be optimized based on the receiving cable length. The DS34RT5110 can also be used as a repeater in an external extender box with the equalization and de-emphasis level settings optimized to provide the maximum cable reach.

Figure 8. Typical Application Diagram

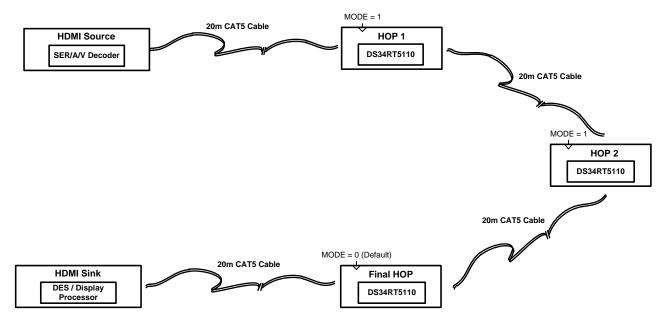

## **MULTIPLE HOP APPLICATION**

For DVI/HDMI home theater and professional studio systems with extensive lengths of cable, multi-hops with 2 or more cascaded DS34RT5110 devices can be implemented as shown in Figure 9. In order to reach the maximum cable length, the levels of the equalization and de-emphasis should be optimized for each individual hop. The MODE pin(s) of the device at the first hop (using two hop application), or at the first and the second hops (using three hop application shown in Figure 9) is recommended to be set HIGH to minimize the jitter accumulation in multiple hops. The MODE pin of the device for the final hop should be set to a LOW state to clean up the clock jitter, in order to drive the maximum cable length to the Sink.

Product Folder Links: DS34RT5110

Figure 9. Multiple Hop Systems

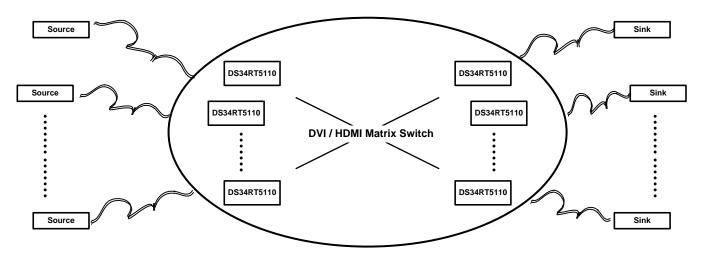

### MATRIX SWITCH APPLICATION

For the security system with matrix DVI/HDMI switches, the DS34RT5110 is ideal to equalize the long cable reach requirement from the Sources, clean the system jitter due to the complexity of PCB routings, and regenerate clean TMDS signals to the Sinks as shown in Figure 10.

Figure 10. Matrix Switch Systems

### **DUAL LINK APPLICATION**

The DS34RT5110 supports DVI dual link applications requiring ultra-high resolutions for QXGA and WQXGA. Two DS34RT5110 devices are configured as shown in Figure 11. This configuration is only recommended for a single dual link repeater application.

Copyright © 2009–2013, Texas Instruments Incorporated

Figure 11. DVI/HDMI Dual Link Application

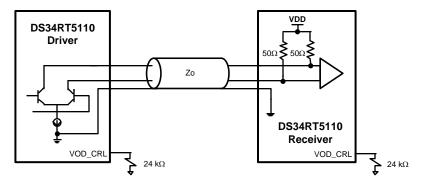

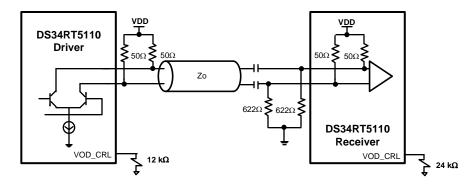

#### DC AND AC COUPLED APPLICATIONS

The DS34RT5110 is designed to support TMDS differential pairs with DC coupled transmission lines. It contains integrated termination resistors ( $50\Omega$ ), pulled up to VDD at the input stage, and open collector outputs for DVI / HDMI signaling. Figure 12 shows the DC coupled connection between the HDMI Source (ie. DS34RT5110) and HDMI Sink (ie. DS34RT5110) devices. In the DC coupled application, the external resistance of 24 k $\Omega$  at VOD\_CRL pin is used at the Source to ensure the VO level of 1000 mVp-p. The AC coupled method connecting between the Source and the Sink devices may be preferred to eliminate the impact of the ground potential difference, or to use one CAT5/6 cable between two chassis. To optimize the DS34RT5110 performance, the external resistance of 12 k $\Omega$  at the VOD\_CRL pin should be used on the Source DS34RT5110, and a pair of 50  $\Omega$  pull-up resistors should be placed close to the outputs of the Source DS34RT5110, in order to DC bias the output driver. Meanwhile,  $622\Omega$  pull-down resistors should be placed at the inputs of the Sink DS34RT5110 device, in order to set the input common mode to a 3.05 V. Note AC coupled configuration is not compliant to the HDMI specification of Source requirement (See Figure 13).

Figure 12. DC Coupled Application

Figure 13. AC Coupled Application

#### **CABLE SELECTION AND INTER-PAIR SKEW**

DVI v1.0 and HDMI v1.3a specify Inter-Pair Skew requirements for the system. The DS34RT5110 intends to extend the longer cable reach with STP (DVI / HDMI) cable, or UTP (Cat5 / Cat5e / Cat6) cable, and it does not have a de-skew function to compensate any cable Inter-Pair Skews. Long cable with Inter-Pair Skew exceeding the DVI / HDMI standard limit tolerance could cause system distortion. Therefore, TI suggests the consideration of Inter-Pair Skew budget during the system design, and recommends Low-Skew Video grade cables for cable extending applications.

## 28 AWG STP (SHIELDED TWIST PAIRS) DVI / HDMI CABLES RECOMMENDED EQ SETTINGS

Table 4 provides the recommended EQ control settings for various data rates and cable lengths for 28 AWG DVI/HDMI compliant configurations. The EQ setting is made via three EQ [2:0] pins.

Format (Data Rate) 0 ~ 10m > 10m

1080P 48-bit (3.4 Gbps) Setting 0x01 Setting 0x06

1080P 36-bit (2.25 Gbps) Setting 0x01 Setting 0x06

1080P (1.65 Gbps) Setting 0x01 Setting 0x06

1080I (750 Mbps) Setting 0x06 Setting 0x06

Table 4. EQ Control Setting for STP Cable

# 24 AWG UTP (LOW SKEW UNSHIELDED TWIST PAIRS) CABLES

The DS34RT5110 can be used to extend the length of low skew grade UTP cables, such as Cat5e and Cat6 to distances greater than 30 meters at 1.65 Gbps with < 0.20 UI of jitter. Note that for non-standard DVI/HDMI cables, the user must ensure the inter pair skew requirements are met. Table 5 shows the recommended EQ control settings for various data rates and cable lengths for UTP configurations.

**Table 5. EQ Control Setting for UTP Cable**

| Format (Data Rate)       | 0 ~ 10m      | > 10m        |

|--------------------------|--------------|--------------|

| 1080P 48-bit (3.4 Gbps)  | Setting 0x01 | Setting 0x05 |

| 1080P 36-bit (2.25 Gbps) | Setting 0x01 | Setting 0x05 |

| 1080P (1.65 Gbps)        | Setting 0x01 | Setting 0x05 |

| 1080I (750 Mbps)         | Setting 0x05 | Setting 0x05 |

#### **General Recommendations**

The DS34RT5110 is a high performance circuit capable of delivering excellent performance. To achieve optimal performance, careful attention must be paid to the details associated with high-speed design as well as providing a clean power supply. Refer to the LVDS Owner's Manual for more detailed information on high-speed design tips as well as many other available resources addressing signal integrity design issues.

Product Folder Links: DS34RT5110

#### PCB LAYOUT CONSIDERATIONS FOR DIFFERENTIAL PAIRS

The TMDS differential inputs and outputs must have a controlled differential impedance of  $100~\Omega$ . It is preferable to route TMDS lines exclusively on one layer of the board, particularly for the input traces. The use of vias should be avoided if possible. If vias must be used, they should be used sparingly and must be placed symmetrically for each side of a given differential pair. Route the TMDS signals away from other signals and noise sources on the printed circuit board. All traces of TMDS differential inputs and outputs must be equal in length to minimize intrapair skew.

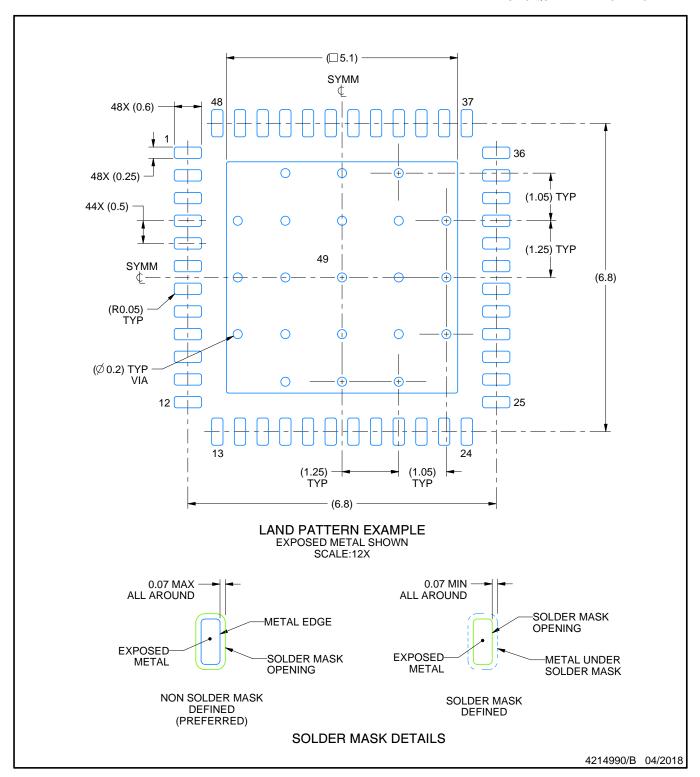

#### WQFN FOOTPRINT RECOMMENDATIONS

See TI application note: AN-1187 "Leadless Leadframe Package (LLP) Application Report" (literature number SNOA401) for additional information on WQFN packages footprint and soldering information.

#### **POWER SUPPLY BYPASSING**

Two approaches are recommended to ensure the DS34RT5110 is provided with an adequate power supply. First, the supply (VDD) and ground (GND) pins should be connected to power planes routed on adjacent layers of the printed circuit board. The layer thickness of the dielectric should be minimized so the VDD and GND planes create a low inductance supply with distributed capacitance. Second, careful attention to supply bypassing through the proper use of bypass capacitors is required. A 0.1  $\mu$ F bypass capacitor should be connected to each VDD pin such that the capacitor is placed as close as possible to the DS34RT5110. Smaller body size capacitors can help facilitate proper component placement. Additionally, two capacitors with capacitance in the range of 2.2  $\mu$ F to 10  $\mu$ F should be incorporated in the power supply bypassing design as well. These capacitors can be either tantalum or an ultra-low ESR ceramic and should be placed as close as possible to the DS34RT5110.

#### **EQUIVALENT I/O STRUCTURES**

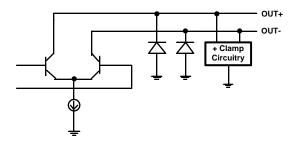

Figure 14 shows the DS34RT5110 CML output structure and ESD protection circuitry.

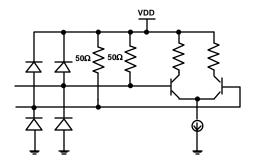

Figure 15 shows the DS34RT5110 CML input structure and ESD protection circuitry.

Figure 14. Equivalent Output Structure

Figure 15. Equivalent Input Structure

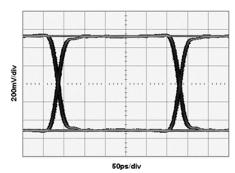

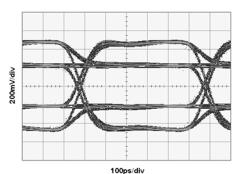

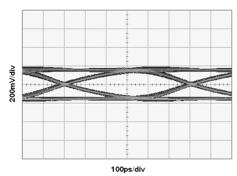

## Typical Performance Characteristics as a Repeater

Figure 16. Simplified Test Setup as a Single Repeater

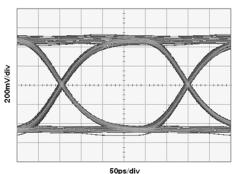

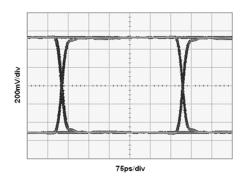

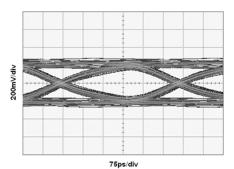

Figure 17. System Source Eye Diagram at TPA (3.4 Gbps)

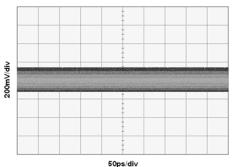

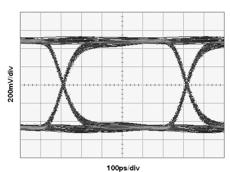

Figure 19. Device Source Eye Diagram at TPC (3.4 Gbps, Cable A = 20m 28 AWG HDMI, EQ = 0x05, BYPASS = 0, DE = 0dB)

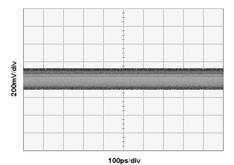

Figure 21. System Sink Eye Diagram at TPD (3.4 Gbps, Cable A = 20m 28 AWG HDMI, Cable B = 5m 28AWG HDMI, EQ = 0x05, BYPASS = 0, DE = -3dB)

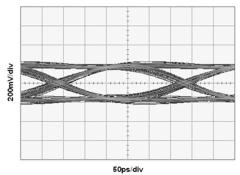

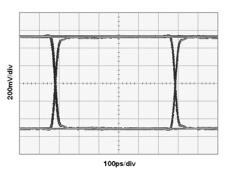

Figure 18. Device Sink Eye Diagram at TPB (3.4 Gbps, Cable A = 20m 28 AWG HDMI)

Figure 20. Device Source Eye Diagram at TPC (3.4 Gbps, Cable A = 20m 28 AWG HDMI, EQ = 0x05, BYPASS = 0, DE = -3dB)

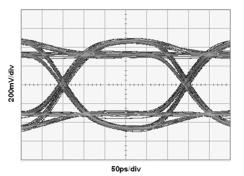

Figure 22. System Source Eye Diagram at TPA (2.25 Gbps)

## Typical Performance Characteristics as a Repeater (continued)

Figure 23. Device Sink Eye Diagram at TPB (2.25 Gbps, Cable A = 25m 28 AWG HDMI)

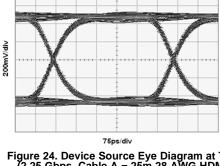

Figure 24. Device Source Eye Diagram at TPC (2.25 Gbps, Cable A = 25m 28 AWG HDMI, EQ = 0x05, BYPASS = 0, DE = 0dB)

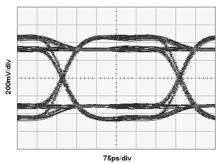

Figure 25. Device Source Eye Diagram at TPC (2.25 Gbps, Cable A = 25m 28 AWG HDMI, EQ = 0x05, BYPASS = 0, DE = -3dB)

Figure 26. System Sink Eye Diagram at TPD (2.25 Gbps, Cable A = 25m 28 AWG HDMI, Cable B = 7.5m 28AWG HDMI, EQ = 0x05, BYPASS = 0, DE = -3dB)

Figure 27. System Source Eye Diagram at TPA (1.65 Gbps)

Figure 28. Device Sink Eye Diagram at TPB (1.65 Gbps, Cable A = 35m 28 AWG HDMI)

# Typical Performance Characteristics as a Repeater (continued)

Figure 29. Device Source Eye Diagram at TPC (1.65 Gbps, Cable A = 35m 28 AWG HDMI, EQ = 0x05, BYPASS = 0, DE = 0dB)

Figure 30. Device Source Eye Diagram at TPC (1.65 Gbps, Cable A = 35m 28 AWG HDMI, EQ = 0x05, BYPASS = 0, DE = -6dB)

Figure 31. System Sink Eye Diagram at TPD (1.65 Gbps, Cable A = 35m 28 AWG HDMI, Cable B = 10m 28AWG HDMI, EQ = 0x05, BYPASS = 0, DE = -6dB)

Copyright © 2009–2013, Texas Instruments Incorporated

## SNLS310G -MARCH 2009-REVISED APRIL 2013

## **REVISION HISTORY**

| Cł | nanges from Revision F (April 2013) to Revision G  | Pa | ge |

|----|----------------------------------------------------|----|----|

| •  | Changed layout of National Data Sheet to TI format |    | 19 |

## PACKAGE OPTION ADDENDUM

6-Feb-2020

#### **PACKAGING INFORMATION**

| Orderable Device   | Status | Package Type | _       |    | _    |                            | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|--------------------|--------|--------------|---------|----|------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                    | (1)    |              | Drawing |    | Qty  | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| DS34RT5110SQ/NOPB  | NRND   | WQFN         | RHS     | 48 | 1000 | Green (RoHS<br>& no Sb/Br) | SN               | Level-3-260C-168 HR | 0 to 70      | 34RT5110       |         |

| DS34RT5110SQE/NOPB | NRND   | WQFN         | RHS     | 48 | 250  | Green (RoHS<br>& no Sb/Br) | SN               | Level-3-260C-168 HR | 0 to 70      | 34RT5110       |         |

| DS34RT5110SQX/NOPB | NRND   | WQFN         | RHS     | 48 | 2500 | Green (RoHS<br>& no Sb/Br) | SN               | Level-3-260C-168 HR | 0 to 70      | 34RT5110       |         |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# **PACKAGE OPTION ADDENDUM**

6-Feb-2020

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

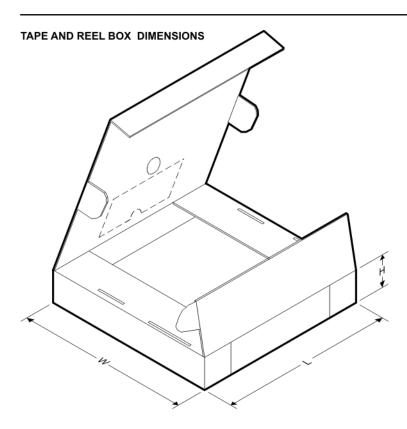

PACKAGE MATERIALS INFORMATION

www.ti.com 29-Sep-2019

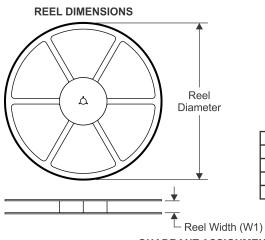

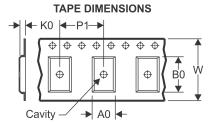

## TAPE AND REEL INFORMATION

| Α0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

|    | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

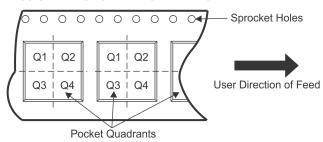

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device             | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DS34RT5110SQ/NOPB  | WQFN            | RHS                | 48 | 1000 | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.3        | 12.0       | 16.0      | Q1               |

| DS34RT5110SQE/NOPB | WQFN            | RHS                | 48 | 250  | 178.0                    | 16.4                     | 7.3        | 7.3        | 1.3        | 12.0       | 16.0      | Q1               |

| DS34RT5110SQX/NOPB | WQFN            | RHS                | 48 | 2500 | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.3        | 12.0       | 16.0      | Q1               |

www.ti.com 29-Sep-2019

\*All dimensions are nominal

| 7 III GITTIOTIOTOTIO GITO TIOTITIGI |              |                 |          |      |             |            |             |  |

|-------------------------------------|--------------|-----------------|----------|------|-------------|------------|-------------|--|

| Device                              | Package Type | Package Drawing | Pins SPQ |      | Length (mm) | Width (mm) | Height (mm) |  |

| DS34RT5110SQ/NOPB                   | WQFN         | RHS             | 48       | 1000 | 367.0       | 367.0      | 38.0        |  |

| DS34RT5110SQE/NOPB                  | WQFN         | RHS             | 48       | 250  | 210.0       | 185.0      | 35.0        |  |

| DS34RT5110SQX/NOPB                  | WQFN         | RHS             | 48       | 2500 | 367.0       | 367.0      | 38.0        |  |

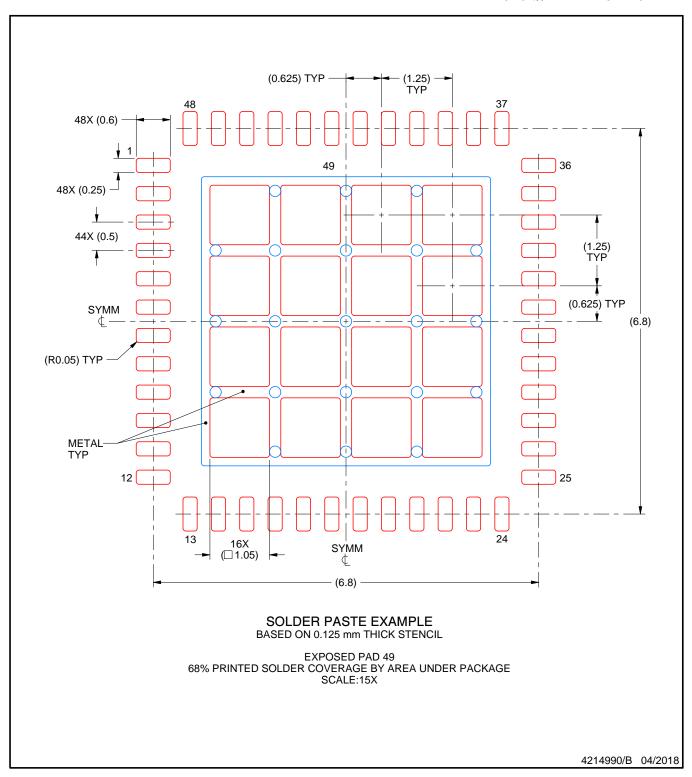

PLASTIC QUAD FLATPACK - NO LEAD

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated