# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better

and more reliable, but there is always the possibility that trouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or

(iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# Digital Camera Signal Processor

ADE-207-316 (Z) 1st Edition Sep. 1999

# **Description**

The HD49815TF is a CMOS IC that has been developed as a digital signal-processing IC for CCD-camera digital-signal-processing systems.

#### **Functions**

- CCD-sensor drive-pulse generation (TG)

- Digital AGC (automatic gain control)

- Color signal separation circuit

- RGB matrix

- RGB gain

- RGB and Y gamma

- Color-difference matrix

- Enhancer

- RGB and Y setup

- Digital I/F (4:2:2)

- Zoom control

- Mirror reversal

- Synchronization signal generator for encoding (SSG)

- AWB, AE, and AF detection

- Two-channel 8-bit D/A converter

#### **Features**

- The HD49815TF provides camera-signal processing, TG, SSG, zoom, and D/A functions and other functions in a single chip and supports high system-integration level.

- In conjunction with the HD49323AF-01 (CDS/AGC + 10-bit ADC) and the control microcomputer, the HD49815TF forms a three-chip kit that can implement an optimal CCD-camera digital-signalprocessing system.

- The HD49815TF provides the zoom function and controls the 1- to 256- times linear zoom. It also provides the half-mirror function.

### Features (cont)

- Since the HD49815TF can be made compatible with the former product, HD49811TFA, through software, a shorter development term is enabled.

- Since software controls AWB, AE, and AF, any protocol can be prepared according to the camera shooting conditions.

- Programmable TG enables use of any CCD device.

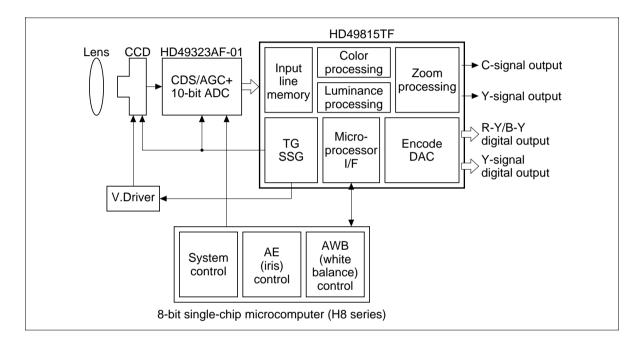

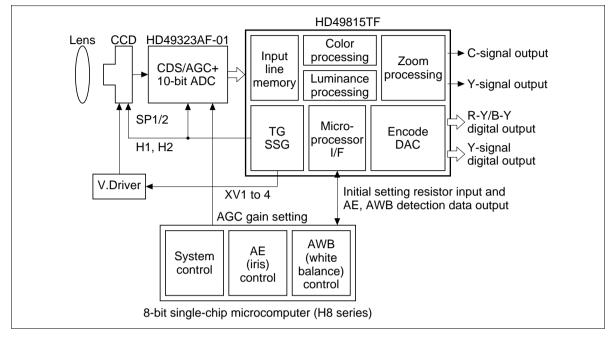

### **System Block Diagram**

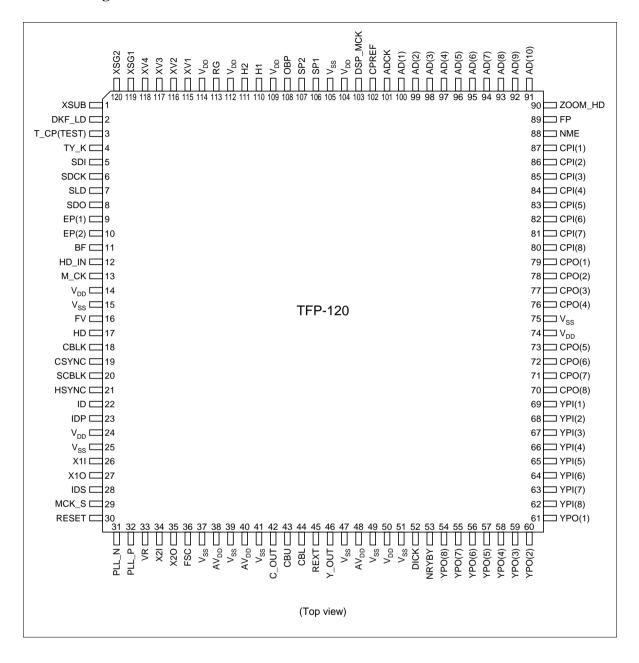

### **Pin Arrangement**

# **Pin Description**

| Pin No. | Symbol          | Pin Name              | I/O | Description                                                       | I/O<br>Format |

|---------|-----------------|-----------------------|-----|-------------------------------------------------------------------|---------------|

| 1       | XSUB            | CCD shutter pulse     | 0   | CCD control pulse                                                 | ZC2R          |

| 2       | DKF_LD          | Line input LD         | I   | Line input dedicated load                                         | ICS           |

| 3       | T_CP            | Test                  | I   | Test pin (GND input)                                              | IC            |

| 4       | TY_K            | Title SW              | I   | Title-killer SW (1 = On, 0 = Off)                                 | ICD           |

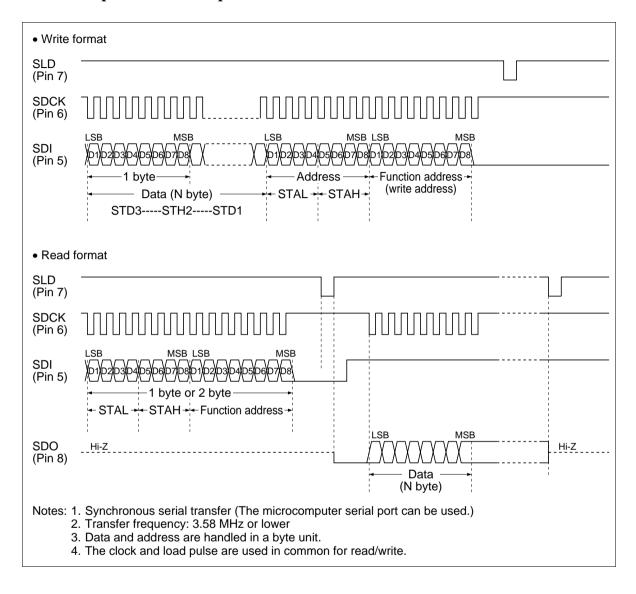

| 5       | SDI             | State data input      | I   | State data-setting data input                                     | IC            |

| 6       | SDCK            | State data clock      | I   | State data-setting clock                                          | ICS           |

| 7       | SLD             | State data load pulse | I   | State data-latch pulse                                            | ICS           |

| 8       | SDO             | AWB, AE, data output  | 0   | AWB, AE, and AF detection-data output                             | ZC2R          |

| 9       | EP (1)          | AE window pulse 1     | 0   | Iris detection-area-setting pulse:<br>SP-A7 [8] output changeover | ICZC2R        |

| 10      | EP (2)          | AE window pulse 2     | 0   | Iris detection-area-setting pulse:<br>SP-A7 [8] output changeover | ICZC2R        |

| 11      | BF              | Burst flag            | 0   | Burst flag output                                                 | ICZC2R        |

| 12      | HD_IN           | External CSYNC input  | I   | External CSYNC input                                              | ICSD          |

| 13      | M_CK            | Microprocessor clock  | 0   | Microprocessor clock output (1/2 or 1/4 dividing of X'tal 1)      | OC2R          |

| 14      | $V_{DD}$        | V <sub>cc</sub> 2     | _   | 3.3 V power supply                                                | VCCI          |

| 15      | V <sub>ss</sub> | GND                   | _   | GND                                                               | GNDI          |

| 16      | FV              | Field vertical output | 0   | Vertical synchronization pulse                                    | ICZC2R        |

| 17      | HD              | HD output             | 0   | Horizontal synchronization pulse                                  | ICZC2R        |

| 18      | CBLK            | Blanking pulse        | 0   | Blanking pulse                                                    | ICZC2R        |

| 19      | CSYNC           | SYNC output           | 0   | SYNC pulse                                                        | ICZC2R        |

| 20      | SCBLK           | SC blanking pulse     | 0   | Subcarrier blanking pulse (SECAM)                                 | ICZC2R        |

| 21      | HSYNC           | Horizontal SYNC       | 0   | Horizontal SYNC pulse (SECAM)                                     | OC2R          |

| 22      | ID              | Identity              | 0   | SECAM determination pulse                                         | OC2R          |

| 23      | IDP             | Identity pulse        | 0   | SECAM determination pulse                                         | ICZC2R        |

| 24      | V <sub>DD</sub> | V <sub>cc</sub> 2     | _   | 3.3 V power supply                                                | VCCC          |

| 25      | V <sub>ss</sub> | GND                   | _   | GND                                                               | GNDC          |

| 26      | X1I             | X'tal 1 input         | I   | 2fsc oscillator input                                             | IQ3           |

| 27      | X10             | X'tal 1 output        | 0   | 2fsc oscillator output                                            | OQ3           |

| 28      | IDS             | Line ID reset input   | I   | Line-determination-signal input                                   | ICD           |

| 29      | MCK_S           | MCK output SW         | I   | Pin 13 MCK dividing setting SW (1 = 1/2, 0 = 1/4)                 | IC            |

| 30      | RESET           | Reset                 | I   | Reset: to restore the initial data settings                       | ICS           |

# Pin Description (cont)

| Pin No. | Symbol          | Pin Name                   | I/O | Description                           | I/O<br>Format |

|---------|-----------------|----------------------------|-----|---------------------------------------|---------------|

| 31      | PLL_N           | PLL negative               | 0   | PLL signal output                     | ZC2           |

| 32      | PLL_P           | PLL positive               | 0   | PLL signal output                     | ZC2           |

| 33      | VR              | Vertical reset             | I   | Vertical synchronization signal input | ICSD          |

| 34      | X2I             | X'tal 2 input              | I   | 4fsc oscillator input                 | IQ2           |

| 35      | X2O             | X'tal 2 output             | 0   | 4fsc oscillator output                | OQ2           |

| 36      | FSC             | Sub carrier frequency      | 0   | fsc output                            | ICZC2R        |

| 37      | V <sub>ss</sub> | GND                        | _   | GND                                   | GNDA          |

| 38      | $AV_{DD}$       | Analog V <sub>cc</sub> 2   | _   | Analog system power supply: 3.3 V     | VCCA          |

| 39      | V <sub>SS</sub> | GND                        | _   | GND                                   | GNDA          |

| 40      | $AV_{DD}$       | Analog V <sub>cc</sub> 2   | _   | Analog system power supply: 3.3 V     | VCCA          |

| 41      | V <sub>SS</sub> | GND                        | _   | GND                                   | GNDA          |

| 42      | C_OUT           | C analog signal output     | 0   | Chrominance-signal analog output      | OA            |

| 43      | CBU             | Current buffer upper       | I   | D/A upper current source              | IA            |

| 44      | CBL             | Current buffer lower       | I   | D/A lower current source              | IA            |

| 45      | REXT            | Reference resister EXT     | I   | Reference voltage input               | IA            |

| 46      | Y_OUT           | Y analog signal output     | 0   | Luminance-signal analog output        | OA            |

| 47      | V <sub>ss</sub> | GND                        | _   | GND                                   | GNDA          |

| 48      | $AV_{DD}$       | Analog V <sub>cc</sub> 2   | _   | Analog system power supply: 3.3 V     | VCCA          |

| 49      | V <sub>ss</sub> | GND                        | _   | GND                                   | GNDA          |

| 50      | V <sub>DD</sub> | V <sub>cc</sub> 2          | _   | Digital system power supply: 3.3 V    | VCCI          |

| 51      | V <sub>SS</sub> | GND                        | _   | GND                                   | GNDI          |

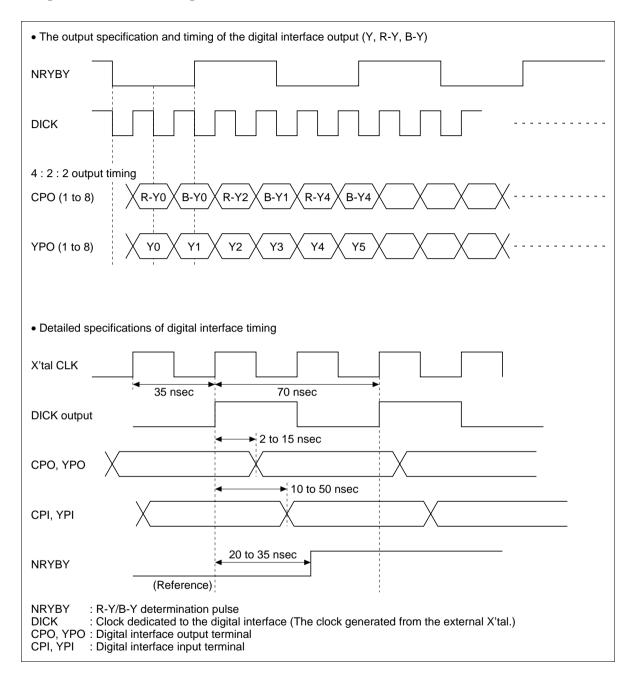

| 52      | DICK            | Digital interface clock    | 0   | Digital interface clock output        | ICZC2R        |

| 53      | NRYBY           | R-Y, B-Y phase output      | 0   | Color-difference signal phase clock   | ICZC2R        |

| 54      | YPO (8)         | Y parallel output (8); MSB | 0   | Luminance-signal digital output MSB   | OC2R          |

| 55      | YPO (7)         | Y parallel output (7)      | 0   | Luminance-signal digital output       | OC2R          |

| 56      | YPO (6)         | Y parallel output (6)      | 0   | Luminance-signal digital output       | OC2R          |

| 57      | YPO (5)         | Y parallel output (5)      | 0   | Luminance-signal digital output       | OC2R          |

| 58      | YPO (4)         | Y parallel output (4)      | 0   | Luminance-signal digital output       | OC2R          |

| 59      | YPO (3)         | Y parallel output (3)      | 0   | Luminance-signal digital output       | OC2R          |

| 60      | YPO (2)         | Y parallel output (2)      | 0   | Luminance-signal digital output       | OC2R          |

| 61      | YPO (1)         | Y parallel output (1); LSB | 0   | Luminance-signal digital output LSB   | OC2R          |

| 62      | YPI (8)         | Y parallel input (8); MSB  | I   | Luminance-signal digital input MSB    | ICD           |

| 63      | YPI (7)         | Y parallel input (7)       | I   | Luminance-signal digital input        | ICD           |

| 64      | YPI (6)         | Y parallel input (6)       | I   | Luminance-signal digital input        | ICD           |

# Pin Description (cont)

| Pin No. | Symbol          | Pin Name                   | I/O | Description                           | I/O<br>Format |

|---------|-----------------|----------------------------|-----|---------------------------------------|---------------|

| 65      | YPI (5)         | Y parallel input (5)       | I   | Luminance-signal digital input        | ICD           |

| 66      | YPI (4)         | Y parallel input (4)       | I   | Luminance-signal digital input        | ICD           |

| 67      | YPI (3)         | Y parallel input (3)       | I   | Luminance-signal digital input        | ICD           |

| 68      | YPI (2)         | Y parallel input (2)       | I   | Luminance-signal digital input        | ICD           |

| 69      | YPI (1)         | Y parallel input (1); LSB  | I   | Luminance-signal digital input LSB    | ICD           |

| 70      | CPO (8)         | C parallel output (8); MSB | 0   | Chrominance-signal digital output MSB | OC2R          |

| 71      | CPO (7)         | C parallel output (7)      | 0   | Chrominance-signal digital output     | OC2R          |

| 72      | CPO (6)         | C parallel output (6)      | 0   | Chrominance-signal digital output     | OC2R          |

| 73      | CPO (5)         | C parallel output (5)      | 0   | Chrominance-signal digital output     | OC2R          |

| 74      | $V_{DD}$        | V <sub>cc</sub> 2          | _   | 3.3 V power supply                    | VCCO          |

| 75      | V <sub>ss</sub> | GND                        | _   | GND                                   | GNDO          |

| 76      | CPO (4)         | C parallel output (4)      | 0   | Chrominance-signal digital output     | OC2R          |

| 77      | CPO (3)         | C parallel output (3)      | 0   | Chrominance-signal digital output     | OC2R          |

| 78      | CPO (2)         | C parallel output (2)      | 0   | Chrominance-signal digital output     | OC2R          |

| 79      | CPO (1)         | C parallel output (1); LSB | 0   | Chrominance-signal digital output LSB | OC2R          |

| 80      | CPI (8)         | C parallel input (8); MSB  | I   | Chrominance-signal digital input MSB  | ICD           |

| 81      | CPI (7)         | C parallel input (7)       | I   | Chrominance-signal digital input      | ICD           |

| 82      | CPI (6)         | C parallel input (6)       | I   | Chrominance-signal digital input      | ICD           |

| 83      | CPI (5)         | C parallel input (5)       | I   | Chrominance-signal digital input      | ICD           |

| 84      | CPI (4)         | C parallel input (4)       | I   | Chrominance-signal digital input      | ICD           |

| 85      | CPI (3)         | C parallel input (3)       | I   | Chrominance-signal digital input      | ICD           |

| 86      | CPI (2)         | C parallel input (2)       | I   | Chrominance-signal digital input      | ICD           |

| 87      | CPI (1)         | C parallel input (1); LSB  | I   | Chrominance-signal digital input LSB  | ICD           |

| 88      | NME             | Memory HD output           | 0   | Line memory control output            | ICZC2DR       |

| 89      | FP              | Field pulse                | 0   | Field pulse                           | ICZC2R        |

| 90      | ZOOM_HD         | Zoom HD output             | 0   | Horizontal synchronization signal     | ICZC2R        |

| 91      | AD (10)         | AD input (10); MSB         | I   | A/D data input MSB                    | IC            |

| 92      | AD (9)          | AD input (9)               | I   | A/D data input                        | IC            |

| 93      | AD (8)          | AD input (8)               | I   | A/D data input                        | IC            |

| 94      | AD (7)          | AD input (7)               | I   | A/D data input                        | IC            |

# Pin Description (cont)

| Pin No. | Symbol          | Pin Name                    | I/O | Description                                                 | I/O<br>Format |

|---------|-----------------|-----------------------------|-----|-------------------------------------------------------------|---------------|

| 95      | AD (6)          | AD input (6)                | I   | A/D data input                                              | IC            |

| 96      | AD (5)          | AD input (5)                | I   | A/D data input                                              | IC            |

| 97      | AD (4)          | AD input (4)                | I   | A/D data input                                              | IC            |

| 98      | AD (3)          | AD input (3)                | I   | A/D data input                                              | IC            |

| 99      | AD (2)          | AD input (2)                | I   | A/D data input                                              | IC            |

| 100     | AD (1)          | AD input (1); LSB           | I   | A/D data input LSB                                          | IC            |

| 101     | ADCK            | AD clock                    | 0   | A/D converter clock                                         | ICZC2R        |

| 102     | CPREF           | Clamp reference output      | 0   | Clamp reference pulse                                       | 2C3           |

| 103     | DSP_MCK         | Microprocessor clock output | 0   | Microprocessor clock output:<br>SP-A7 [8] output changeover | ICZC2R        |

| 104     | V <sub>DD</sub> | V <sub>cc</sub> 2           | _   | 3.3 V power supply                                          | VCCO          |

| 105     | V <sub>ss</sub> | GND                         | _   | GND                                                         | GNDO          |

| 106     | SP1             | Sampling pulse 1            | 0   | Sampling pulse for the AGC/CDS IC                           | ICZC2         |

| 107     | SP2             | Sampling pulse 2            | 0   | Sampling pulse for the AGC/CDS IC                           | ICZC2         |

| 108     | OBP             | OBP pulse                   | 0   | Optical black-pulse output                                  | ICZC2R        |

| 109     | $V_{DD}$        | V <sub>cc</sub> 1           | _   | 3 V or 5 V power supply<br>(H1/H2 power supply)             | VCCC35        |

| 110     | H1              | H1                          | 0   | CCD-sensor horizontal drive pulse                           | OC3R          |

| 111     | H2              | H2                          | 0   | CCD-sensor horizontal drive pulse                           | OC3R          |

| 112     | $V_{DD}$        | V <sub>cc</sub> 1           | _   | 5 V power supply<br>(RG power supply)                       | VCCC5         |

| 113     | RG              | Reset gate                  | 0   | CCD-sensor control reset gate                               | ZC3R          |

| 114     | V <sub>DD</sub> | V <sub>cc</sub> 2           | _   | 3.3 V power supply                                          | VCCO          |

| 115     | XV1             | XV1                         | 0   | CCD-sensor vertical control pulse                           | ICZC2R        |

| 116     | XV2             | XV2                         | 0   | CCD-sensor vertical control pulse                           | ICZC2R        |

| 117     | XV3             | XV3                         | 0   | CCD-sensor vertical control pulse                           | ICZC2R        |

| 118     | XV4             | XV4                         | 0   | CCD-sensor vertical control pulse                           | ICZC2R        |

| 119     | XSG1            | XSG1                        | 0   | CCD-sensor vertical control pulse                           | ZC2R          |

| 120     | XSG2            | XSG2                        | 0   | CCD-sensor vertical control pulse                           | ZC2R          |

# **Description of I/O Format**

| I/O Format | Contents                                                                     |

|------------|------------------------------------------------------------------------------|

| IC         | CMOS level input                                                             |

| ICD        | CMOS level input with pull-down resistor                                     |

| ICS        | CMOS level schmitt input                                                     |

| ICSD       | CMOS level input with pull-down resistor                                     |

| ICZC2      | CMOS level common I/O (4 mA)                                                 |

| ICZC2DR    | CMOS level common I/O with pull-down resistor and through-put control (4 mA) |

| ICZC2R     | CMOS level common I/O with through-put control (4 mA)                        |

| OC2R       | CMOS level output with through-put control (4 mA)                            |

| OC3R       | CMOS level output with through-put control (8 mA)                            |

| IQ2        | Crystal oscillator input                                                     |

| OQ2        | Crystal oscillator output                                                    |

| IQ3        | Crystal oscillator input                                                     |

| OQ3        | Crystal oscillator output                                                    |

| ZC2        | CMOS-level three-state output (4 mA)                                         |

| ZC2R       | CMOS-level three-state output with through-put control (4 mA)                |

| ZC3        | CMOS-level three-state output (8 mA)                                         |

| ZC3R       | CMOS-level three-state output with through-put control (8 mA)                |

| VCCI       | Core system power supply: 3 V                                                |

| VCCO       | Puddling system power supply: 3 V                                            |

| VCCC       | Common power supply: 3 V                                                     |

| VCCC5      | Common power supply: 5 V for pin 112                                         |

| VCCC35     | Common power supply: 3 or 5 V for pin 109                                    |

| GNDI       | Core system GND                                                              |

| GNDO       | Puddling system GND                                                          |

| GNDC       | Common GND                                                                   |

| IA         | Analog input                                                                 |

| OA         | Analog output                                                                |

| VCCA       | Analog power supply                                                          |

| GNDA       | Analog GND                                                                   |

Notes: 1. Pin 113 is used for 5 V system output.

2. Pins 110 and 111 are used for 3 V or 5 V system output. They depend on the voltage of pin 109.

# **Absolute Maximum Ratings** (Ta = 25°C)

| Item                         | Symbol                       | Ratings | Unit                           |    |

|------------------------------|------------------------------|---------|--------------------------------|----|

| Power supply voltage         | Power supply voltage         |         |                                | V  |

| Pin voltage (5 V operation b | olock)                       | Vt5V    | -0.2 to V <sub>cc</sub> 1 +0.2 | V  |

| Pin voltage (3 V operation b | olock)                       | Vt3V    | -0.2 to V <sub>cc</sub> 2 +0.2 | V  |

| Output current               | Per output                   | lo      | -32 to +32                     | mA |

|                              | Per GND-V <sub>cc</sub> pair | lot     | -72 to +72                     | mA |

| Allowable power dissipation  | 1                            | Popr    | 450                            | mW |

| Operating temperature        |                              | Topr    | -10 to +75                     | °C |

| Storage temperature          | With bias                    | Tbias   | -10 to +75                     | °C |

|                              | Without bias                 | Tstg    | -40 to +125                    | °C |

- Notes: 1. Using this LSI at values in excess of the absolute maximum ratings may permanently damage the LSI. The LSI should normally be operated under the conditions specified for the electrical characteristics. Exceeding these conditions may lead to incorrect operation and may adversely affect LSI reliability.

- 2. All voltage values are referenced to GND = 0 V.

- 3. The pin voltage ratings also apply to the NC pins.

- 4.  $V_{cc}1$  indicates the 5 V system power supply and  $V_{cc}2$  indicates the 3 V system power supply.

**Electrical Characteristics** ( $V_{CC}1 = 4.75 \text{ V}$  to 5.25 V,  $V_{CC}2 = 2.85 \text{ V}$  to 3.15 V,  $AV_{CC} = 2.85 \text{ V}$  to 3.15 V,  $Ta = 25^{\circ}\text{C}$ )

|                                    |                   |                        |      |                        |      | <b>Test Conditions</b>                                                          |      |

|------------------------------------|-------------------|------------------------|------|------------------------|------|---------------------------------------------------------------------------------|------|

| Item                               | Symbol            | Min                    | Тур  | Max                    | Unit |                                                                                 | Note |

| CMOS-level                         | $V_{\text{IHC}}$  | V <sub>cc</sub> 2×0.75 | _    | V <sub>cc</sub> 2      | V    |                                                                                 |      |

| input voltage                      | V <sub>ILC</sub>  | 0.0                    | _    | V <sub>cc</sub> 2×0.20 | V    |                                                                                 |      |

| CMOS schmitt                       | V <sub>TC</sub> + | 2.50                   | _    | V <sub>cc</sub> 2      | V    | V <sub>cc</sub> 1 = 5 V                                                         |      |

| input voltage                      | V <sub>TC</sub> - | 0.0                    | _    | 0.60                   | V    | $V_{cc}2 = 3 \text{ V}$                                                         |      |

| Output voltage                     | V <sub>OHC1</sub> | V <sub>cc</sub> 1–0.5  | _    | _                      | V    | I <sub>OH</sub> = -200 μA<br>5 V system pin                                     | 1    |

|                                    | V <sub>OLC1</sub> | _                      | _    | 0.4                    | V    | $I_{OL}$ = 200 $\mu$ A<br>5 V system pin                                        | _    |

|                                    | $V_{OHC2}$        | V <sub>cc</sub> 2–0.5  | _    | _                      | V    | $I_{OH} = -200 \mu A$<br>3 V system pin                                         | 1, 5 |

|                                    | V <sub>OLC2</sub> | _                      | _    | 0.4                    | V    | $I_{OL}$ = 200 $\mu$ A<br>3 V system pin                                        | 1, 6 |

| Input leakage current              | l <sub>LI</sub>   | _                      | _    | 1.0                    | μΑ   | $V_{IN} = 0 \text{ V to } V_{CC}$                                               | 2    |

| Output leakage current             | I <sub>LO</sub>   | _                      | _    | 1.0                    | μΑ   | Output Hi-Z conditions                                                          | 2    |

| Pull-down current                  | I <sub>PD</sub>   | 5                      | _    | 100                    | μΑ   | $V_{IN} = V_{CC}2 = 3 \text{ V}$                                                |      |

| Power dissipation                  | Popr              | _                      | _    | 450                    | mW   | $V_{cc}1 = 5 \text{ V},$<br>$V_{cc}2 = 3 \text{ V},$<br>$AV_{cc} = 3 \text{ V}$ | 3    |

| Analog output voltage (full scale) | Vfull             | 0.80                   | 1.00 | 1.20                   | V    |                                                                                 | 3, 4 |

| Analog output voltage (zero scale) | Vzero             | -0.20                  | 0.00 | 0.20                   | V    | -                                                                               |      |

| Differential linearity             | DNL               | -2.0                   | _    | 2.0                    | LSB  |                                                                                 |      |

Notes: 1. Output voltage must be measured in the steady state.

- 2. Except for pins that include a pull-down resistor.

- 3. Guaranteed at CBU = 0.1  $\mu$ F, CBL = 0.1  $\mu$ F, REXT = 3.4  $k\Omega$  analog output load resistance = 500  $\Omega$ , and Ta = 25°C.

- 4. Applied to pins indicated as OA in the I/O format column of the pin-functions table.

- 5. Because V<sub>OH</sub> of pin 31 cannot be measured logically, it was not tested.

- 6. Because  $V_{\text{OL}}$  of pin 32 cannot be measured logically, it was not tested.

- 7.  $V_{cc}1$ ,  $V_{cc}2$ , and  $AV_{cc}$  indicate the 5 V system power supply, the 3 V system power supply, and the analog system power supply, respectively.  $V_{cc}$  indicates  $V_{cc}1$ ,  $V_{cc}2$ , and  $AV_{cc}$ .

- 8. The voltage range of pin 109 (VCCC35) is  $V_{cc}$  = 2.85 V to 5.25 V.

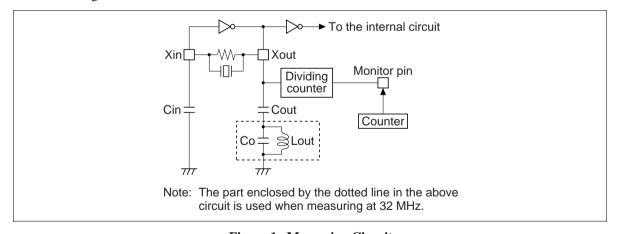

# **Crystal Oscillation Circuit**

#### 1. Measuring conditions

The oscillation frequency was measured under the following conditions.

$$\begin{split} &V_{CC}1 = 5.0 \text{ V} \\ &V_{CC}2 = 3 \text{ V} \\ &Ta = 25^{\circ}\text{C} \\ &8 \text{ MHz, } 20 \text{ MHz, } \text{and } 24 \text{ MHz:} \\ &Rf = 1 \text{ to } 10 \text{ M}\Omega \\ &\text{Cin, } \text{Cout} = 20 \text{ pF } (\pm 20 \text{ pF}) \\ &32 \text{ MHz:} \\ &Rf = 1 \text{ to } 10 \text{ M}\Omega \\ &\text{Cin} = 20 \text{ pF } (\pm 20 \text{ pF}) \\ &\text{Cout} = 100 \text{ pF } (\pm 20 \text{ pF}), \text{ Co} = 15 \text{ pF } (\pm 5 \text{ pF}), \text{ Lout} = 1 \text{ } \mu\text{H} \end{split}$$

The conditions above may be changed within the range of measuring conditions.

#### 2. Measuring method

Under the measuring conditions above, two methods were tested.

fmin. = 20 MHz, and fmax. = 32 MHz (applied to pins 26 and 27)

fmin. = 8 MHz, and fmax. = 24 MHz (applied to pins 34 and 35)

Note: The oscillation start time tosc is max = 200 ms.

#### 3. Measuring circuit

Figure 1 Measuring Circuit

# **Built-in Functions and System Configuration**

#### **System Configuration**

Figure 2 System Configuration

#### **System Description**

#### 1. CCD

The following lists the pixels of the CCD sensors that can be used with the HD49815TF. For other pixel numbers, contact our sales dept.

$512 (H) \times 492 (V) NTSC$

$512 (H) \times 582 (V) PAL$

$682 (H) \times 492 (V) NTSC$

681 (H) × 582 (V) PAL

#### 2. CDS/AGC + 10-bit ADC

The HD49323AF-01 (manufactured by Hitachi) is recommended as an optimal CDS/AGC + 10-bit ADC IC for the HD49815TF. Since the HD49323AF-01 provides a correlated double sampling circuit that realizes high S/N and an automatic gain control (AGC) circuit that implements programmable control of 0 dB to 34.7 dB, it enables a high-image-quality camera system when used in conjunction with the HD49815TF.

#### 3. 8-bit single-chip microcomputer

The 8-bit single-chip microcomputer controls the system. It receives the image detection data that the HD49815TF is gathering and implements automatic iris control (AE), automatic white balance control (AWB), and automatic focus control (AF).

When setting the power on, this microcomputer implements the initial setting to the state data of the HD49815TF.

For details on the state data, see "Hitachi Camera DSP (HD49815TF) State Data".

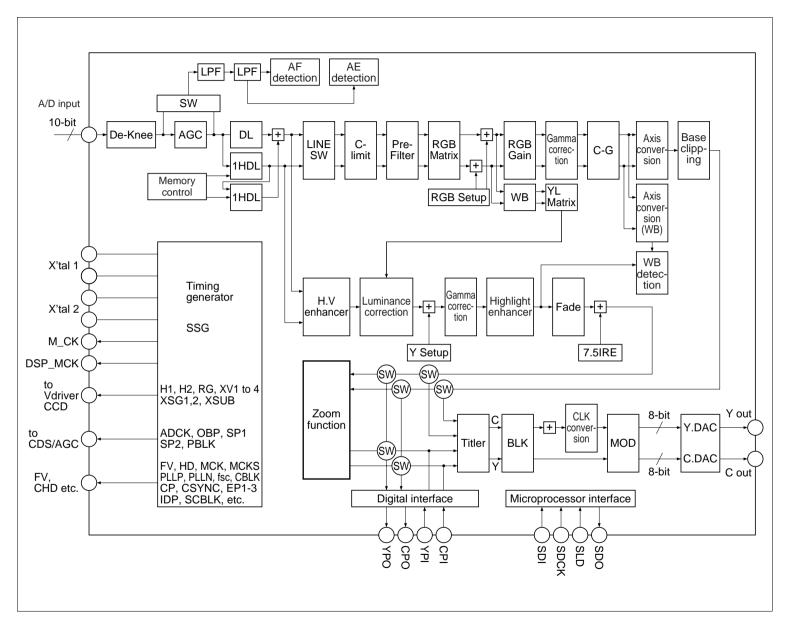

#### **Built-in Functions**

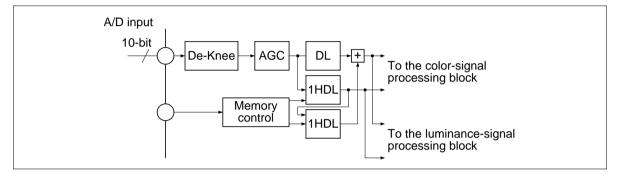

#### 1. Input line memory block

Figure 3 Input Line Memory Block

#### a. De-knee function

When the CDS/AGC IC at the pre-stage or the external circuit uses the knee circuit to expand the dynamic range of the signal, the de-knee (inverse knee) circuit returns the signal converted by the knee circuit to the original state.

The de-knee point can be set in State Data SP\_A0 [1]. The gain of the high-luminance block is 1/2.

#### b. AGC function

A digital AGC circuit is provided. The AGC gain can be set in State Data SP\_A0 [2] from 1 to 16 times.

#### c. 1H delay line (1HDL) function

This circuit obtains horizontal efficient pixels of the CCD output signal. The number of efficient pixels is set in State Data SP A0 [9, 10] and TM A0 [14] MCSET.

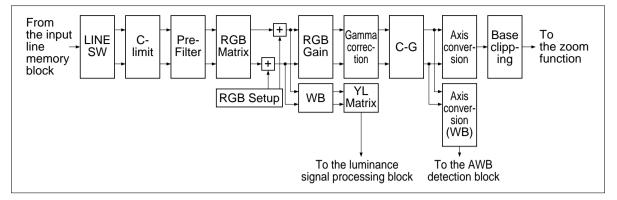

#### 2. Color-signal processing block

Figure 4 Color-Signal Processing Block

#### a. C-limit (complementary color clipping level) function

High clipping processing is performed on the complementary color signals independently. High clipping is set in State Data SP\_A2 [0 to 3].

The complementary color signal indicates Gb: (G + Cy), Wr: (Ye + Mg), Wb: (Mg + Cy), and Gr: (G + Ye).

#### b. RGB-matrix block

The three primary colors (red, green, and blue) are acquired in the RGB matrix by multiplying arbitrary coefficients by the four complementary colors (Gb, Wr, Wb, and Gr) and taking the total of those results. The RGB matrix is designed to support the minimum color moire and to enable free color reproduction. Arbitrary coefficients are set in State Data SP\_A2 [4 to 15]. The following shows the formula.

#### c. RGB-setup block

The black level of the color signals is variable according to the coefficients of the RGB matrix. The value calculated by the formula below is subtracted from the color signal to correct the black level. The subtracted value can be set externally and is set in State Data SP\_A3 [0 to 2].

Formula =

$$-[48 \times \Sigma \text{ (Matrix data)} \times 2^3]$$

#### d. RGB-gain block

The RGB gain value acquired in the AWB control is set in the RGB gain circuit to improve the white reproduction performance. As it is set prior to the gamma correction, it changes the gamma correction amount. The RGB gain can be set in State Data SP\_A3 [3 to 5] from 1 to 256 times. (The G gain is set from 1 to 128 times.)

#### e. C gamma (γ) correction block

The C gamma correction circuit performs gamma processing on the RGB signal. It is set in State Data SP\_A3 [6 to 9]. Four kinds of values can be set independently, according to the input-signal level, to acquire optimal gamma characteristics: the C gamma dark (to reduce the gain of the small signals for improving S/N), C gamma coefficient (to control the expansion of the gamma curve), C gamma knee (to decide the slope of the large signals), and C gamma limit (to perform high-clipping processing for the input signal of the C gamma circuit).

#### f. YL matrix block

The luminance level changes according to the color temperature of the imaged object. Set State Data SP\_A5 [12, 13] for the luminance correction. To correct the luminance, create YL from the three primary colors (R, G, and B) and convert it to the luminance signal level. The YL matrix circuit creates the YL level from the RGB signal.

The YL matrix is set in State Data SP\_A3 [11 to 13].

#### g. The axis-conversion (C-Y matrix) block

The C-Y (color-difference) matrix takes R-G and B-G as its input signals, and creates the R-Y and B-Y color-difference signals by setting coefficients for those inputs.

The axis-conversion (C-Y matrix) circuits are set in State Data SP A8 [0 to 5].

#### h. Base-clipping block

Since base clipping is performed on the color-difference signals, the base-clipping circuit has the characteristics of clipping the sections near axes on a vector scope.

This circuit is set in State Data SP A8 [8].

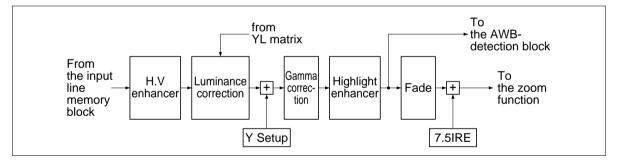

#### 3. Luminance-signal-processing block

Figure 5 Luminance-Signal-Processing Block

#### a. H-enhancer function

The H-enhancer circuit allows the core level, the enhancer gain, and the noise coefficient to be set independently to acquire optimal characteristics.

This circuit is set in State Data SP\_A4 [4 to 7].

#### b. V-enhancer function

The V-enhancer circuit allows the enhancer coefficient to be set and can control the gain for only those signal components that exceed the set core level.

This circuit is set in State Data SP A4 [8 to 10].

#### c. Luminance correction

The ratio of the red and blue levels changes according to the color temperature of the imaged object. For example, if a red object is imaged at a low color temperature, the luminance level increases and the object appears to have a lower chrominance. Therefore, the luminance correction circuit performs luminance-correction processing to implement color depth reproduction.

The luminance-correction circuit is set in State Data SP A5 [12, 13].

#### d. Y setup

Since the OB clamp processes the signal, the black level of the 10-bit signal input to the HD49815TF is fixed to 48/1024. The Y-setup circuit subtracts 48 at the black level. However, when 48 at the black level differs due to the noise mixed in the analog signal, the Y-setup circuit subtracts that value.

The Y-setup circuit is set in State Data SP A5 [6].

#### e. Gamma correction

The gamma-correction circuit implements the gamma-correction processing for the separated Y signal. Four kinds of values can be set independently, according to the input-signal level, to acquire optimal gamma characteristics: the gamma input limit, the gamma knee coefficient, the gamma coefficient, and the gamma black clipping.

The gamma correction circuit is set in State Data SP\_A5 [1 to 4].

#### f. Highlight enhancer

For input-Y signal levels in excess of 100 IRE, the highlight enhancer implements highlight enhancer processing.

This circuit is set in State Data SP\_A5 [0, 5, and 14].

#### g. Fade

The fade circuit amplifies the luminance signal by a factor of 0 to 1.

This circuit is set in State Data SP A5 [9].

#### 4. Zoom, encode block, TG, SSG, and AWB and AE detection blocks

#### a. Zoom processing

The Y, R-Y, and B-Y signals completed the color-signal processing and the luminance-signal processing can be electronically zoomed by a factor of 1 to 256.

After clipping CCD signals for V direction, zoom circuit clips these signals for H direction, and expand these signals for H and V directions.

The zooming times and the read starting position for the V and H directions are set in State Data TM\_A2 [3, 4, 5, 6, 8, and 9] and ZM\_A0 to 6.

#### b. Encode block

This circuit encodes the signals completed the color-signal processing, the luminance-signal processing, and the zoom processing as the NTSC/PAL TV-monitor method.

A DAC that converts the digital signal to an analog signal is provided. The DAC has two channels: one for R-Y signals and one for B-Y signals.

#### c. TG and SSG

The TG generates the signals required to drive the CCD sensor (H1, H2, RG, SG1/2, and the V transfer pulse), and the CDS/AGC control signals (SP1 and SP2).

In addition, the SSG generates the signals to synchronize with the TV monitor (the Sync signal). The drive timing of the generated signals differs according to the manufacturer and the specifications of the CCD sensor. Setting the state data enables setting of any timing.

The state data of TG and SSG can be set in TM A0, A1, A2, A3, and A8.

#### d. AWB- and AE-detection blocks

The HD49815TF provides automatic white-balance (AWB) and automatic-iris (AE) detection circuits that are indispensable for a camera.

The AWB-detection block takes the R-Y and B-Y color-difference signals completed the color-signal processing, and converts to the R-B and MG-G axes. The converted signals are sent to circuits for the white detection to obtain white signal components only, and the white-color difference value is detected. The 8-bit single-chip microcomputer acquires this detection data, and controls the R and B gains to produce the true white.

The State Data of the AWB detection is AWB A0 and A8.

The AE-detection block divides the CCD output signal converted to digital by the 10-bit ADC to six arbitrary areas, and performs integration processing. This function enables detection of the lighting level of the image signal.

The 8-bit single-chip microcomputer acquires this detection data, and controls the accumulation amount (the shutter) of the CCD sensor or the iris motor of the lens to maintain the proper lighting. The State Data of the AF detection is AE\_A0 to A7 and A8.

# **Microcomputer Interface Specifications**

# **Data Transfer Specification**

For data transfer between the HD49815TF and the microcomputer, two types (N and E for write, and R1 and R2 for read) are available. The following table shows the relationship between the function block and the transfer specifications. On the next page, the details of the transfer specifications are described.

| Function Block    | Transfer Mode | Transfer<br>Specifications *1 | Related Address            |

|-------------------|---------------|-------------------------------|----------------------------|

| Signal processing | W             | N                             | SP_A0, 2 to 5, 7 to 10, 15 |

| TM                | W             | N                             | TM_A3, 15                  |

|                   |               | E                             | TM_A0 to 2, 8, 10 to 12    |

|                   | R             | R1                            | TMR_A0                     |

| Iris              | W             | N                             | AE_A0 to 7                 |

|                   | R             | R2                            | AE_A8                      |

| White balance     | W             | N                             | AWB_A0                     |

|                   | R             | R1                            | AWB_A8                     |

| AF                | W             | N                             | AF_A0 to 3                 |

|                   | R             | R1                            | AF_A8 to 13                |

| ZOOM              | W             | N                             | ZM_A0 to 6                 |

Note: 1. Transfer specifications

Type N : Normal transfer from the microcomputer to the DSP

Type E : Transfer using the set pulse (synchronous with VD) or the reset signal (used as a

synchronous pulse in the DSP) sent from the microcomputer to the RS latch in the

DSP

Note: This cannot be set during the standby mode.

Type R1  $\,:\,$  Data transfer (1) from the DSP to microcomputer

Type R2 : Data transfer (2) from the DSP to microcomputer

# • Type N

| Transfer specification | Pulse Timing             | Conditions                                                     |

|------------------------|--------------------------|----------------------------------------------------------------|

| N                      | SLD (Pin 7) SDCK (Pin 6) | A = 100 ns or more<br>B = 100 ns or more<br>C = 100 ns or more |

# • Type E

| Transfer specification | Pulse Timing |             |                         | Conditi                   | ons               |                   |

|------------------------|--------------|-------------|-------------------------|---------------------------|-------------------|-------------------|

|                        | SLD          |             |                         |                           | 270,000<br>pixels | 410,000<br>pixels |

|                        | (Pin 7)      |             | Α                       | 0.5 / fs + 100 ns or more | 150 ns<br>or more | 135 ns<br>or more |

| E                      | E SDCK       | В           | 2 / fs + 100 ns or more | 300 ns<br>or more         | 240 ns<br>or more |                   |

|                        | (Pin 6) A B  |             | D                       | 5.5 / fs + 100 ns or more | 650 ns<br>or more | 485 ns<br>or more |

|                        | D            | !<br>!<br>! | fs                      | Sensor clock              | 100 ns            | 70 ns             |

# • Type R1

| Transfer specification | Pulse Timing                     | Conditions                                                                                                                                                               |

|------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R1                     | SLD (Pin 7)  SDCK (Pin 6)  A B D | A = 100 ns or more B = 100 ns or more D = 400 ns or more  Do not read the white balance data and the AF read data within the 1H period from the start of the V blanking. |

# • Type R2

| Transfer specification | Pulse Timing     | Conditions                                                                                                                             |

|------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                        | SLD (Pin 7)      | A = 100 ns or more<br>B = 100 ns or more                                                                                               |

| R2                     |                  | 270,000 410,000 pixels pixels                                                                                                          |

|                        | SDCK (Pin 6) A B | D $\{1 / \text{fs} \times (32 + 5) + 400 \text{ ns}\}$ or more $\{1 / \text{fs} \times (32 + 5) + 4.1  \mu\text{s} \}$ or more or more |

|                        | D                | fs Sensor clock 100 ns 70 ns                                                                                                           |

# RENESAS

Note: 2 to 9. Function addresses

The following table shows the function addresses for each function block (during state data transfer) and the data to be transferred from the microcomputer.

Table 2 Function Addresses for each Function Block and State Data

|                    |        |                                             |               |     |                             |             |              |             |          |           |                                                         |     | L           | .ist        | 0                                                  | f D | ata         | а Т            | rar                                     | ısfe     | erre    | ed         |              |          |                                  |      |     |           |                |       |               |      |                            |               | Remarks                        |

|--------------------|--------|---------------------------------------------|---------------|-----|-----------------------------|-------------|--------------|-------------|----------|-----------|---------------------------------------------------------|-----|-------------|-------------|----------------------------------------------------|-----|-------------|----------------|-----------------------------------------|----------|---------|------------|--------------|----------|----------------------------------|------|-----|-----------|----------------|-------|---------------|------|----------------------------|---------------|--------------------------------|

| 2                  |        | Function Address                            |               |     |                             |             |              |             | Š        | STAH STAL |                                                         |     |             |             |                                                    |     |             | STD1           |                                         |          |         |            |              |          |                                  | STD2 |     |           |                |       |               |      |                            |               | This example                   |

| Signa              | ıl<br> | D8 I                                        | )7            | D6  | D5                          | D4          | D3           | 3 D2        | D1       | D8        | D7                                                      | D6  | D5          | D4          | D3                                                 | D2  | D'          | 1 D8           | 3 D7                                    | D6       | D5      | D4         | D3           | D2       | D1                               | D8   | D7  | D6        | D:             | 5 D   | 4 E           | 03   | D2 D                       |               | is related to                  |

| process<br>(Settin |        | 0                                           | 0             | 0   | 0                           | 0           | 0            | 0           | 0        | *         | *                                                       | *   | *           | *           | *                                                  | *   | *           | *              | *                                       | *        | *       | *          | *            | *        | *                                | *    | *   | *         | *              | *     | :             | *    | * *                        | k ,           | SP-A0[9].                      |

| exampl             |        | 0                                           | 0             | 0   | 0                           | 0           | 0            | 0           | 0        | 0         | 0                                                       | 0   | 0           | 1           | 0                                                  | 0   | 1           | D8             | 3 D7                                    | D6       | D5      | D4         | D3           | D2       | D1                               |      | _   | -         | -              | - -   | _ -           | -    | — D                        | 9             |                                |

| 3                  |        | F                                           | un            | cti | on                          | Ac          | ddı          | ress        | 3        |           | ST                                                      | ΑH  |             |             | ST                                                 | ΓAL |             |                |                                         |          | ST      | D1         |              |          |                                  |      |     |           | S              | TD:   | 2             |      |                            |               | This example                   |

| TM wri             | te     | D8 D7 D6 D5 D4                              |               |     | D4                          | I D3        | 3 D2         | D1          | D8       | D7        | D6                                                      | D5  | D4          | D3          | D2                                                 | D   | 1 D8        | 3 D7           | D6                                      | D5       | D4      | D3         | D2           | D1       | D8                               | D7   | D6  | D:        | 5 D            | 4 E   | )3            | D2 D |                            | is related to |                                |

| (Settin            | a      | 0                                           | 0             | 0   | 0                           | 0           | 0            | 0           | 1        | *         | *                                                       | *   | *           | *           | *                                                  | *   | *           | *              | *                                       | *        | *       | *          | *            | *        | *                                | *    | *   | *         | *              | *     | :             | *    | * *                        | k             | TM-A0 [14].                    |

| exampl             |        |                                             | - 1           | 0   | 0                           | 0           | _            |             | 1        | 0         | 0                                                       | 0   | 0           | 1           | 1                                                  | 1   | 0           | D8             | 3 D7                                    | D6       | D5      | D4         | D3           | D2       | D1                               |      | _   |           | -              | - -   | _ -           | _    | _                          | _             |                                |

| 4                  |        | _                                           | _             | _   | _                           | _           | _            | ress        |          |           |                                                         |     |             |             |                                                    |     |             |                |                                         |          |         |            |              |          |                                  |      |     |           |                |       |               |      |                            |               |                                |

| TM rea             | ad     | D8 I                                        | $\rightarrow$ |     |                             | _           | -            | _           | -        |           | С                                                       | ata | re          | ad          | for                                                | au  | tor         | nati           | ic p                                    | has      | e a     | dju        | stm          | nen      | t fo                             | r S  | P1, | SI        | 2,             | ar    | nd            | RC   | 3                          |               |                                |

|                    |        |                                             | - 1           | 0   | 0                           | _           | 0 0 1        |             |          |           |                                                         |     |             |             |                                                    |     |             | _              |                                         |          |         |            |              |          |                                  |      |     |           |                |       |               |      |                            |               |                                |

|                    |        |                                             | _             |     |                             |             | ADATA        |             |          | _         | ST                                                      |     |             |             | _                                                  | ΓAL | _           | _              | STD1<br>D8 D7 D6 D5 D4 D3               |          |         |            |              |          |                                  |      |     | STD2      |                |       |               |      |                            | — .           | This example                   |

|                    |        |                                             | $\rightarrow$ | _   | _                           | _           | +-           | -           | D1       | _         |                                                         | _   | <u> </u>    | D4          | _                                                  | +   | +           | 1 D8           | 3 D7                                    | D6       | D5      |            | <u> </u>     | _        | D1                               | -    | -   | -         | -              | -     | -             | -    | D2 D                       | щ,            | is related to<br>the IRIS peak |

|                    |        | -                                           | -             | 0   | 1                           | 0           | *            | -           | *        | *         | *                                                       | *   | *           | *           | *                                                  | *   | *           | ┢              | ⊨                                       | _        | _       | *          | *            | *        | *                                | 0    | 0   | 0         | +-             | -     | -             | -    | 0 (                        | ᆚ             | detection area.                |

|                    | 5      |                                             | 0             |     | 1                           | 0           | 1            |             | 0        | _         | _                                                       |     | _           |             | _                                                  | D2  |             | 1 -            | _                                       | _        | —       | _          | _            | _        | _                                | 0    | 0   | 0         | _              | _     | _             | 0    | 0 0                        | ו             |                                |

|                    | W      | Fund                                        | _             | _   | _                           |             | -            | _           |          |           | ST                                                      |     |             |             |                                                    | ΓAL | _           | _              | _                                       |          | ST      |            |              |          |                                  |      |     |           | <del>, -</del> | TD:   | =,-           |      |                            | — .           | This example                   |

| AE                 |        | -                                           | $\rightarrow$ |     | _                           |             | +            | _           |          |           |                                                         | _   | _           | _           | _                                                  | _   | +           | _              | 3 D7                                    | D6       | -       |            | _            | _        | _                                |      | -   | -         | -              | -     | _             | -    | D2 D                       | щ,            | is related to<br>the window    |

|                    |        |                                             | -             | 0   | 0                           | 0           | -            | -           | 1        | *         | *                                                       | *   | *           | *           | *                                                  | *   | *           | _              | -                                       | <u> </u> | *       | *          | *            | *        | *                                | 0    | 0   | 0         | 0              | -     | _             | 0    | -   '                      | 기             | H count 3.                     |

|                    |        |                                             | _             | 0   | 0                           | _           | _            |             | 1        | 1         | 0                                                       | 1   | 0           | 0           | 0                                                  | 1   | _           | 1              |                                         | _        | D5      | D4         | D3           | D2       | D1                               | 0    | 0   | 0         | 0              | C     | )             | 0    | 0   0                      | ו             |                                |

|                    | 6      | <del></del>                                 | _             | _   | ction Address   STAH   STAL |             |              |             |          |           |                                                         |     |             |             |                                                    |     |             |                |                                         |          |         |            |              |          |                                  |      |     |           |                |       |               |      |                            |               |                                |

|                    | Ř      | -                                           | $\rightarrow$ |     | _                           |             | -            | _           | -        | D8        | D7                                                      | D6  | D5          | _           | -                                                  | _   | -           | 1              |                                         | R        | eac     | ar         | ea           | set      | tınç                             | g by | /S  | IΑ        | L (            | 4 b   | ıts           | )    |                            |               |                                |

|                    |        |                                             | _             | 0   | 1                           | 1           | -            | 0           |          | _         |                                                         |     |             |             |                                                    |     |             |                | STD1                                    |          |         |            |              |          | STD2                             |      |     |           |                |       |               |      |                            | TI:           |                                |

|                    |        |                                             |               |     |                             |             |              | ADAT        |          |           |                                                         |     |             | D.4         | _                                                  |     |             |                |                                         | - DO     |         |            | Б.           | Б0       | 1 .                              | _    |     | - I       | _              |       |               | 20   |                            |               | This example is related to     |

|                    |        |                                             |               |     |                             |             | D            | 3 D2        | וט       | שט        | יט                                                      | Dб  | _           | _           | -                                                  | _   | _           | _              | $\overline{}$                           | _        | -       | ₩<br>*     | ₩<br>*       | _        | -                                |      |     |           |                |       |               |      | _                          | щ,            | the offset R-B.                |

|                    |        | -                                           | 0             | 1   | 0                           | 0           | H            | $\vdash$    |          | _         | =                                                       |     | *           | *           | *                                                  | *   | *           | *              | *                                       | *        | *       |            | <u> </u>     | *        | *                                | 0    | 0   | 0         | 0              | -     | -             | 0    | 0 (                        | _             |                                |

|                    | 7      | 0 Fund                                      | 0             |     | 0                           | 0           | _            | D 4         |          | _         | CT                                                      |     | 0           | 0           | 0                                                  | 0   | _           | ╀              |                                         | טט       | D5      |            | D3           | D2       | וטו                              | 0    | _   | 0         |                | _     |               |      | -   -                      | -             | This avample                   |

| AWB                | VV     |                                             | -             | _   |                             |             | -            | _           |          | _         | STAH                                                    |     |             | STAL        |                                                    |     |             | 100            | STD1<br> D8  D7  D6  D5  D4  D3  D2  D1 |          |         |            |              |          | Window setting for white balance |      |     |           |                |       |               |      | This example is related to |               |                                |

| AVVD               |        | -                                           | $\rightarrow$ | 0   | 0                           | 0           | 0            | _           | *        | *         | *                                                       | *   | *           | *           | *                                                  | *   | *           | ישו            | וט כ                                    | סט       | טט      | <i>D</i> 4 | נט           | UZ       | וטו                              | -    |     | r w<br>WE |                |       |               |      |                            |               | he V count 2                   |

|                    |        | <u> </u>                                    | -             | 0   | 0                           | _           | +-           | <del></del> | 1        | 1         | 0                                                       | 1   | 1           | 0           |                                                    |     | +           |                | D7                                      |          | *<br>DE | *          | *            | ₩<br>  * | ×<br>D4                          | -    |     |           |                |       |               |      |                            |               |                                |

|                    |        | _                                           | _             | _   |                             | _           | _            |             | <u> </u> |           | U                                                       |     |             | U           | 0 0 1 1 D8 D7 D6 D5 D4 D3 D2 D1 axis phase setting |     |             |                |                                         |          |         |            |              |          |                                  |      |     | +         |                |       |               |      |                            |               |                                |

|                    | 8      | Function Address<br>D8 D7 D6 D5 D4 D3 D2 D1 |               |     |                             |             |              |             |          |           | White balance read                                      |     |             |             |                                                    |     |             |                |                                         |          |         |            |              |          |                                  |      |     |           |                |       |               |      |                            |               |                                |

|                    | R      | -                                           | 0             | 1   | 0                           |             | -            | _           | -        |           | Willie Dalatice read                                    |     |             |             |                                                    |     |             |                |                                         |          |         |            |              |          | <br> -                           |      |     |           |                |       |               |      |                            |               |                                |

|                    |        | Function Address ADATA                      |               |     |                             |             |              |             |          |           | ST                                                      | ΔН  |             |             | 91                                                 | ΓAL |             | Т              |                                         |          |         |            |              |          |                                  |      |     |           |                |       |               |      |                            | +             | This example                   |

| AF                 | 9      |                                             |               |     |                             | D4 D3 D2 D1 |              |             |          |           |                                                         |     | <del></del> |             |                                                    | 1   | HPF bandwid |                |                                         |          |         |            | th selection |          |                                  |      |     |           |                | -   i | is related to |      |                            |               |                                |

|                    |        | -                                           | 0             | 1   | 1                           | 0           | *            | _           | *        | *         | *                                                       | *   | *           | *           | *                                                  | _   | _           | -              |                                         |          | Б       |            |              | : ·      |                                  |      |     |           | •              |       |               |      |                            |               | the HRF                        |

|                    |        |                                             | *   *   *   * |     |                             |             |              |             | _        |           |                                                         |     |             | D4 D3 D2 D1 |                                                    |     | 4           | Base-ciip quai |                                         |          |         |            |              | ntit     |                                  |      |     |           |                |       |               |      | bandwidth selection.       |               |                                |

|                    |        | Function Address ADATA                      |               |     |                             |             |              |             | 1 -      |           | ST                                                      | ДΗ  | _           | Ĕ.          | _                                                  | ΓAL | _           |                |                                         |          | ST      | D1         |              |          |                                  |      |     |           |                |       |               |      |                            | $\rightarrow$ | This example                   |

|                    | 10     | D8 I                                        |               |     |                             |             | -            | -           |          | _         |                                                         |     | D5          | D4          | _                                                  |     | _           | 1 DE           | 3 D7                                    | D6       |         |            | D3           | D2       | D1                               | 5    | ett | ina       | fo             | r in  | te            | ara  | tion                       | -  i          | is related to                  |

|                    |        | -                                           | _             | 0   | 0                           | _           | <del>-</del> | -           | 1        | 1         | 1                                                       | 0   | 0           | 0           | *                                                  | *   | *           | +-             | +                                       | *        | *       | *          | *            | *        | *                                | `    |     | nd        |                |       |               |      |                            |               | the differential               |