www.ti.com

SNVS057C - NOVEMBER 1999-REVISED APRIL 2013

# LM2686 Regulated Switched Capacitor Voltage Converter

Check for Samples: LM2686

## **FEATURES**

- +5V Regulated Output

- **Doubles Input Supply Voltage**

- **TSSOP 14 Package**

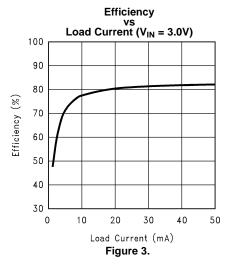

- 80% Typical Conversion Efficiency at 25mA

- Input Voltage Range of 2.85V to 6.5V

- **Independent Shutdown Control Pins**

## APPLICATIONS

- **Cellular Phones**

- **Pagers**

- **PDAs**

- Handheld Instrumentation

- 3.3V to 5V Voltage Conversion Applications

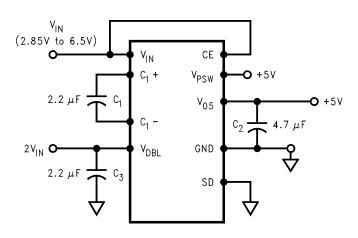

## Typical Application and Connection Diagram

## DESCRIPTION

The LM2686 CMOS charge-pump voltage converter operates as an input voltage doubler and a +5V regulator for an input voltage in the range of +2.85V to +6.5V. Three low cost capacitors are used in this circuit to provide up to 50mA of output current at +5.0V (± 5%). The LM2686 operates at a 130 kHz switching frequency to reduce output resistance and voltage ripple. With an operating current of only 450µA (operating efficiency greater than 80% with most loads) and 6.0µA typical shutdown current, the LM2686 is ideal for use in battery powered systems. The device is in a small 14-pin TSSOP package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

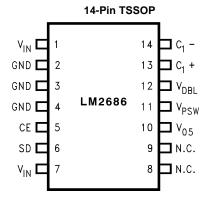

## **PIN DESCRIPTIONS**

www.ti.com

| Pin No. | Name                           | Function                                                                                                            |  |

|---------|--------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| 1       | $V_{IN^{(1)}}$                 | Power supply input voltage.                                                                                         |  |

| 2       | GND <sup>(2)</sup>             | Power supply ground.                                                                                                |  |

| 3       | GND <sup>(2)</sup>             | Power supply ground.                                                                                                |  |

| 4       | GND <sup>(2)</sup>             | Power supply ground.                                                                                                |  |

| 5       | CE                             | Chip enable input. This pin is high for normal operation and low for shutdown and V <sub>PSW</sub> load disconnect. |  |

| 6       | SD                             | Shutdown input. This pin is low for normal operation and high for shutdown and V <sub>PSW</sub> load disconnect.    |  |

| 7       | V <sub>IN</sub> <sup>(1)</sup> | Power supply input voltage.                                                                                         |  |

| 8       | NC                             | No connection.                                                                                                      |  |

| 9       | NC                             | No connection.                                                                                                      |  |

| 10      | V <sub>05</sub>                | Regulated +5V output.                                                                                               |  |

| 11      | $V_{PSW}$                      | V <sub>05</sub> output connected through a series switch, PSW.                                                      |  |

| 12      | $V_{DBL}$                      | Output of doubled input voltage.                                                                                    |  |

| 13      | C <sub>1</sub> <sup>+</sup>    | The positive terminal of doubling charge-pump capacitor, C1.                                                        |  |

| 14      | $C_1^-$                        | The negative terminal of doubling charge-pump capacitor, C1.                                                        |  |

<sup>(1)</sup> All V<sub>IN</sub> pins, pin 1 and pin 7 must be tied together for proper operation.

(2) All ground pins, pin 2, pin 3 and pin 4 must be tied together for proper operation.

www.ti.com

SNVS057C - NOVEMBER 1999-REVISED APRIL 2013

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## ABSOLUTE MAXIMUM RATINGS(1)(2)

| Supply Voltage (V <sub>IN</sub> to GND)                      | 6.8V                                   |

|--------------------------------------------------------------|----------------------------------------|

| SD, CE                                                       | (GND - $0.3V$ ) to ( $V_{In} + 0.3V$ ) |

| V <sub>05</sub> Continuous Output Current                    | 80mA                                   |

| V <sub>05</sub> Short-Circuit Duration to GND <sup>(3)</sup> | Indefinite                             |

| Continuous Power Dissipation (T <sub>A</sub> = 25°C) (4)     | 600mW                                  |

| T <sub>JMAX</sub> <sup>(4)</sup>                             | 150°C                                  |

| $\theta_{\mathrm{JA}}^{(4)}$                                 | 140°C/W                                |

| Operating Ambient Temp. Range                                | -40°C to 85°C                          |

| Operating Junction Temperature Range                         | −40°C to 125°C                         |

| Storage Temp. Range                                          | −65°C to 150°C                         |

| Lead Temp. (Soldering, 10 sec.)                              | 300°C                                  |

| ESD Rating (5)                                               | 2kV                                    |

- Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics.

- If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office / Distributors for availability and specifications.

- V<sub>05</sub> may be shorted to GND without damage. For temperature above 85°C, V<sub>05</sub> must not be shorted to GND or device may be damaged.

- The maximum allowable power dissipation is calculated by using  $P_{DMAX} = (T_{JMAX} T_A)/\theta_{JA}$ , where  $T_{JMAX}$  is the maximum junction temperature,  $T_A$  is the ambient temperature and  $\theta_{JA}$  is the junction-to-ambient thermal resistance of the specified package.

- The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin.

## **ELECTRICAL CHARACTERISTICS**

Limits with standard typeface apply for  $T_J = 25$ °C, and limits in **boldface type** apply over the full temperature range. Unless otherwise specified  $V_{IN} = 3.6V$ ,  $C_1 = C_3 = 2.2 \mu F$ .  $C_2 = 4.7 \mu F$ . (1)

| Symbol               | Parameter                                                         | Conditions                                                     | Min   | Тур  | Max   | Units |  |

|----------------------|-------------------------------------------------------------------|----------------------------------------------------------------|-------|------|-------|-------|--|

| V <sup>+</sup>       | Supply Voltage                                                    |                                                                | 2.85  |      | 6.5   | V     |  |

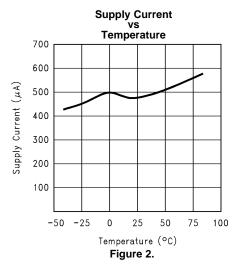

| IQ                   | Supply Current                                                    | No Load                                                        |       | 450  | 950   | μΑ    |  |

| I <sub>SD</sub>      | Shutdown Supply Current                                           | V <sub>IN</sub> = 6.5V                                         |       | 6    | 30    | μΑ    |  |

| $V_{SD}$             | Shutdown Pin Input Voltage for CE,                                | Logic Input High @ 6.5V                                        | 2.4   |      |       | V     |  |

|                      | SD                                                                | Logic Input Low @ 6.5V                                         |       |      | 0.8   |       |  |

| I <sub>L</sub> (+5V) | Output Current at V <sub>05</sub>                                 | 2.85V < V <sub>IN</sub> < 6.5V                                 |       |      | 50    | mA    |  |

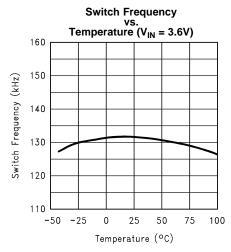

| F <sub>SW</sub>      | Switch Frequency                                                  |                                                                | 85    | 130  | 180   | kHz   |  |

| P <sub>EFF</sub>     | Average Power Efficiency at V <sub>05</sub>                       | 2.85V < V <sub>IN</sub> < 6.5V<br>I <sub>L</sub> = 25mA to GND |       | 82   |       | %     |  |

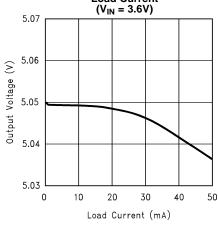

| V <sub>05</sub>      | Output Regulation                                                 | $1mA < I_L < 50mA, V_{IN} = 6.5V$                              | 4.848 | 5.05 | 5.252 | V     |  |

|                      |                                                                   | 1mA < I <sub>L</sub> < 50mA, V <sub>IN</sub> = 6.5V            | 4.797 | 5.05 | 5.303 | V     |  |

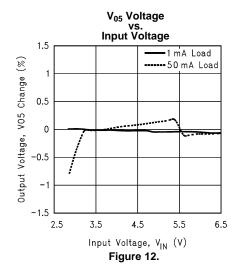

| G <sub>LINE</sub>    | Line Regulation                                                   | 2.85V < V <sub>IN</sub> < 3.6V                                 |       | 0.25 |       | 0/ 0/ |  |

|                      |                                                                   | 3.6V < V <sub>IN</sub> < 6.5V                                  |       | 0.05 |       | %/V   |  |

| G <sub>LOAD</sub>    | Load Regulation                                                   | 1mA < I <sub>L</sub> < 50mA, V <sub>IN</sub> = 6.5V            |       | 0.3  | 1.0   | %     |  |

| R <sub>SW</sub>      | Series Switch Resistance from V <sub>05</sub> to V <sub>PSW</sub> | V <sub>IN</sub> > 2.85V                                        |       | 5.0  |       | Ω     |  |

In the typical operating circuit, capacitors C<sub>1</sub> and C<sub>3</sub> are 2.2μF, 0.3Ω maximum ESR capacitors. Capacitors with higher ESR will

Product Folder Links: LM2686

increase output resistance, reduce output voltage and efficiency.

The 50mA maximum current assumes no current is drawn from V<sub>DBL</sub> pin. See Voltage Doubler section in the Detailed Device Description.

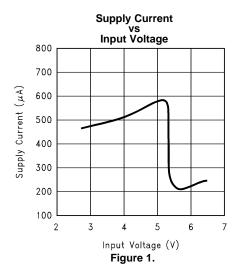

## TYPICAL PERFORMANCE CHARACTERISTICS

Unless otherwise specified,  $T_A = 25$ °C,  $V_{IN} = 3.6$ V.

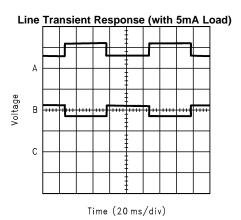

Figure 5.

A: INPUT VOLTAGE:  $V_{IN}$  = 3.2V to 6.0V, 5V/div B: OUTPUT VOLTAGE:  $V_{PSW}$ : 100mV/div Figure 6.

**NSTRUMENTS**

V<sub>PSW</sub> Response to CE (with 5mA Load)

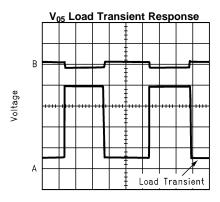

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Unless otherwise specified,  $T_A = 25$ °C,  $V_{IN} = 3.6$ V.

Time (20 ms/div)

A: LOAD CURRENT:  $I_{LOAD}$  = 5mA to 39.6mA, 10mA/div B: OUTPUT VOLTAGE: V<sub>05</sub>: 10mV/div Figure 7.

A: CE INPUT: 5V/div

Α

Voltage

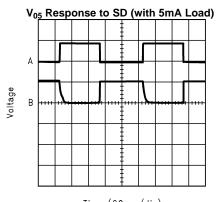

Time (20 ms/div) A: SD INPUT: 5V/div

B: OUTPUT VOLTAGE: 5V/div

Figure 9.

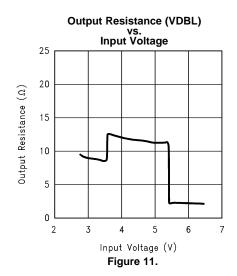

Figure 10.

#### DETAILED DEVICE DESCRIPTION

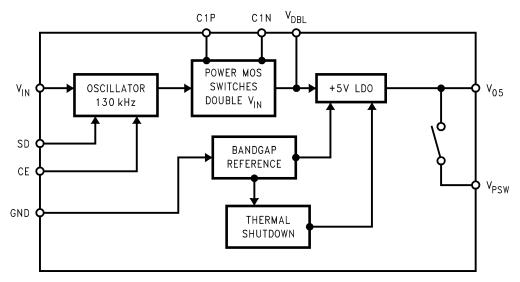

Figure 13. Functional Block Diagram

The LM2686 CMOS charge pump voltage converter operates as an input voltage doubler, +5V regulator for an input voltage in the range of +2.85V to +6.5V. It delivers maximum load currents of 50mA for the regulated +5V, with an operating current of only 450μA. It also has a typical shutdown current of 6μA. All these performance qualities make the LM2686 an ideal device for battery powered systems.

The LM2686 has two main functional blocks: a voltage doubler and a low dropout (LDO) regulator. Figure 13 shows the LM2686 functional block diagram.

## **VOLTAGE DOUBLER**

The voltage doubler ties directly to  $V_{IN}$  and doubles the input voltage in the range from +2.85V to +5.4V up to 5.7V to 10.8V at the  $V_{DBL}$  pin. For  $V_{IN}$  above 5.4V, the doubler shuts off and the input voltage is passed directly to VDBL via an internal power switch.

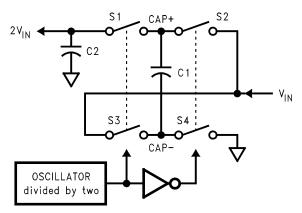

The doubler contains four large CMOS switches which are switched in a sequence to double the input supply voltage. Figure 14 illustrates the voltage conversion scheme. When S2 and S4 are closed, C1 charges to the supply voltage  $V_{IN}$ . During this time interval, switches S1 and S3 are open. In the next time interval, S2 and S4 are opened at the same time, S1 and S3 are closed, the sum of the input voltage  $V_{IN}$  and the voltage across C1 gives the  $2V_{IN}$  and the voltage across C2 gives the  $2V_{IN}$  at  $V_{DBL}$  output.  $V_{DBL}$  supplies the LDO regulator. It is recommended not to load  $V_{DBL}$  when  $V_{05}$  has a load of 50mA. For proper operation, the sum of  $V_{DBL}$  and  $V_{05}$  loads must not be more than 50mA.

Figure 14. Voltage Doubler Principle

www.ti.com

SNVS057C - NOVEMBER 1999-REVISED APRIL 2013

#### +5 LDO REGULATOR

$V_{DBL}$  is the input to an LDO regulator that regulates it to a +5 output voltage at  $V_{05}$ .  $V_{PSW}$  is tied to  $V_{05}$  through a series switch PSW. The LDO output capacitor (4.7 $\mu$ F Tantalum) may be connected to either  $V_{05}$  or  $V_{PSW}$ .

## SHUTDOWN AND LOAD DISCONNECT

In addition to the nominal charge pump and regulator functions, the LM2686 features shutdown and load disconnect circuitry. CE (chip enable) and SD (shutdown positive) perform the same task with opposite input polarities. When CE is low or SD is high, all circuit blocks are disabled and  $V_{05}$  falls to ground potential. This is the same result as when the die temperature exceeds 150°C, and the device's internal thermal shutdown is triggered.

The LM2686 incorporates a low impedance switch tied to the  $V_{05}$  output, because some special applications require load disconnect and this is achievable via the switch. Switch PSW connects  $V_{05}$  to  $V_{PSW}$ . In normal operation, this switch is closed, allowing 5V loads to be tied to either  $V_{05}$  or  $V_{PSW}$ . Forcing CE low or SD high opens the PSW.

Product Folder Links: LM2686

#### **APPLICATION INFORMATION**

## **CAPACITOR SELECTION**

The output resistance and ripple voltage are dependent on the capacitance and ESR values of the external capacitors.

## **VOLTAGE DOUBLER EXTERNAL CAPACITORS**

The selection of capacitors are based on the specifications of the dropout voltage (which equals  $I_{OUT}$   $R_{OUT}$ ), the output voltage ripple, and the converter efficiency.

$$R_{OUT} = 2 R_{SW} + \frac{2}{f_{OSC} \times C_1} + 4 ESR_{C_1} + ESR_{C_3}$$

where

R<sub>SW</sub> is the sum of the ON resistance of the internal MOSFET switches as shown in Figure 14

The peak-to-peak output voltage ripple is determined by the oscillator frequency, the capacitance and ESR of the capacitor C3.

$$V_{RIPPLE} = \frac{I_L}{f_{OSC} \times C_2} + 2 \times I_L \times ESR_{C_3}$$

High capacitance (2.2µF to higher), low ESR capacitors can reduce the output resistance and the voltage ripple.

Power efficiency of =

$$\frac{P_{OUT}}{P_{IN}} = \frac{I_L^2 R_L}{I_L^2 R_I + I_L^2 R_{OUT} + I_O (V+)}$$

where

- I<sub>O</sub>(V+) is the quiescent power loss of the IC device

- I<sup>2</sup><sub>L</sub>R is the conversion loss associated with the switch on-resistance, the two external capacitors and their ESRs (1)

Low ESR capacitors (table to be referenced) are recommended to maximize efficiency, reduce the output voltage drop and voltage ripple.

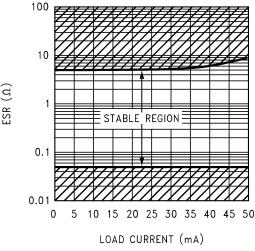

## +5 LDO REGULATOR EXTERNAL CAPACITORS

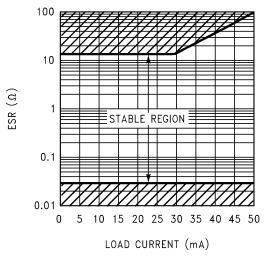

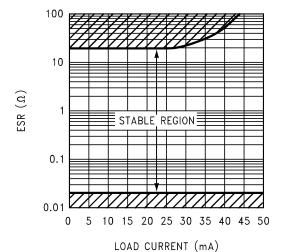

The voltage doubler output capacitor, C3, serves as the input capacitor of the 5 LDO regulator. The output capacitor C4, must meet the requirement for minimum amount of capacitance and appropriate ESR (Equivalent Serving Resistance) for proper operations. The ESR value must remain within the regions of stability as shown in Figure 15, Figure 16 and Figure 17 to ensure output's stability. A minimum capacitance of  $1\mu$ F is required at the output. This can be increased without limit, but a  $4.7\mu$ F tantalum capacitor is recommended for loads ranging upto the maximum specification. In lighter loads of less or equal to 10mA, ceramic capacitor of at least  $1\mu$ F and ESR in the milliohms can be used. This has to be connected to  $V_{PSW}$  pin instead of the  $V_{05}$  pin.

Any output capacitor used should have a good tolerance over temperature for capacitance and ESR values. The larger the capacitor, with ESR within the stable region, the better the stability and noise performance.

Figure 15. ESR Curve for C<sub>OUT</sub> = 2.2μF

Figure 16. ESR Curve for  $C_{OUT} = 4.7 \mu F$

Figure 17. ESR Curve for  $C_{OUT} = 10 \mu F$

NSTRUMENTS

| SNVS057C - | -NOVEMBER | 1999_ | REVISED | <b>APRII</b> | 201 |

|------------|-----------|-------|---------|--------------|-----|

www.ti.com

## **REVISION HISTORY**

| Changes from Revision B (April 2013) to Revision C |                                                    |   |  |  |

|----------------------------------------------------|----------------------------------------------------|---|--|--|

| •                                                  | Changed layout of National Data Sheet to TI format | 9 |  |  |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>