# STV3500

# Integrated Up-Convertor with 32-bit CPU Core with Video Enhancers and Bitmap On-Screen Display

**DATA BRIEF**

#### **FEATURES**

- Versatile integrated up-converter

- 100/120-Hz Interlaced: AABB, AA\*B\*B, AA\*BB\*, ABAB or AAAA field-repeat

- Motion driven 100-Hz up-conversion based on Median filter

- 50/60-Hz progressive with line-interpolation, field-merging with motion-adaptive deinterlacing

- Advanced still picture modes: AA\*AA\* and ABAB interlaced or AAAA non-interlaced

- Automatic movie mode detection and scanning

- Standard definition input

- ITU-R BT.656/601 video input

- Separate H/V inputs synchronous with input clock

- 3D temporal noise reduction with cometeffect correction

- Movie mode detection with motion phase recovery

- Scene-change detector for contrast enhancer and up-conversion control

- Letterbox format detection and auto-format correction

- High-quality video display

- Picture structure improvement including color transition improvement, luma peaking/coring and luma contrast enhancer

- H/V format conversion with zoom In/Out (4x to 1/8x) with H/V decimation

- Letterbox and 4:3 to 16:9 format conversion with programmable 5-segment panoramic mode

- Very flexible sync generator for master and slave modes by Vsync and Hsync signals with line-locked pixel clock

- Progressive display mode (60 Hz, 525 lines) for full-screen graphic planes

- Support for monitor mode: VGA, SVGA, XGA

- Mosaic mode with up to 16 pictures displayed

- High-Performance 8-bit Bitmap OSD Generator

- Pixel-based resolution with 10-bit RGB outputs

- Programmable Resolution up to 1920x1024, all standard displays are supported: teletext 1.5 (480x520) and 2.5 (672x520), doublepage teletext (960x520) with picture& text, teleWeb (640x480)

- 4 graphic planes with full alpha-blending capabilities: 24-bit background plane, 10-bit RGB video plane, bitmap OSD plane with color map, up to 128 x 128 pixel cursor plane

- 2D graphics accelerator

- Embedded 32-bit ST20 CPU core

- Peripherals and I/Os for TV Chassis Control

- 30 fully-programmable I/Os (5V tolerant)

- 4 external interrupts

- 8-bit programmable PWM with 4 inputs/ outputs

- Infrared digital preprocessor

- Real time clock and watchdog timer

- 4 16-bit standard timers

- 10-bit ADC with 6 inputs and wake-up capability

- 2 Master/slave I2C bus interfaces

- UART and support for IrDA interfaces

- Teletext 1.5 and 2.5, Closed-Caption, VPS and WSS VBI data decoding, TeleWeb compliant

- Embedded emulation resources with in-situ flash programming capabilities

- 1.8V and 3.3V power supplies

- Eco standby mode

- 27-MHz crystal oscillator

Rev. 1 November 2004 1/3

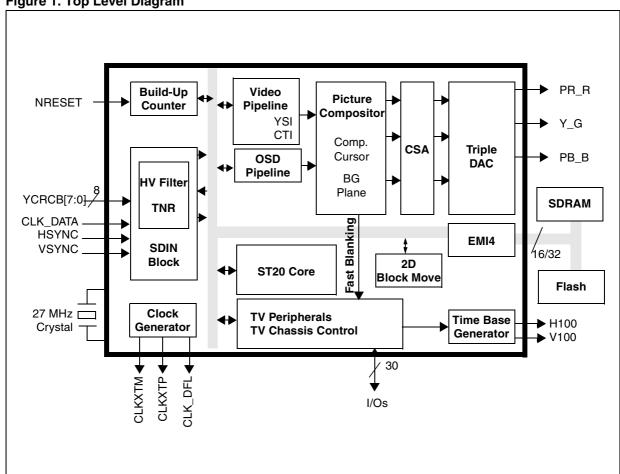

#### **DESCRIPTION**

This integrated circuit (IC) is dedicated to low-cost 100-Hz TV chassis. Combined with a digital multistandard video decoder (STV2310) delivering an ITU-R BT.601/656 video stream and a 2H video scan IC, it provides a cost-effective, high-performance solution for 2H applications. The STV3500 includes a field or line up-converter, a 32-bit ST20 CPU core with all peripherals required for controlling the TV chassis. Teletext data is extracted from the incoming stream and decoded by the CPU. An embedded On-Screen Display (OSD) generator delivers the text and graphics. The Video Display Pipeline performs feature box image processing such as picture improvement, horizontal and vertical rescaling and Temporal Noise Reduction.

The chip operates with a single external SDRAM that is used for the field-rate up-conversion and text and graphic generations. The external

SDRAM can be configured as a single bank of 16/64/128 Mb (16-bit configuration) or a dual bank of 16 to 256 Mb (32-bit configuration). Application program codes are stored in an external Flash memory and executed from the SDRAM.

The STV3500 is designed using an 0.18 micron CMOS process and delivered in a 160-pin PQFP (0.65 mm pitch) package.

The ST3500 completes the Digital IC Core family (STi5xxx, STi7xxx) which offers common CPU and software platforms based on STMicroelectronics' 32-bit ST20 CPU core.

Table 1. Order Codes

| Part Number | Description                                       |

|-------------|---------------------------------------------------|

| STV3500     | Device in low-cost 0.65 mm pitch PQFP 160 package |

Figure 1. Top Level Diagram

2/3

## **REVISION HISTORY**

### **Table 2. Revision History**

| Date          | Revision | Description of Changes |

|---------------|----------|------------------------|

| November 2004 | 1        | First Issue            |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics.

All other names are the property of their respective owners

© 2004 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com