## 8259A

## Programmable Interrupt Controller iAPX86 Family MILITARY INFORMATION

## DISTINCTIVE CHARACTERISTICS

- SMD/DESC qualified

- · Eight-level priority controller

- Expandable to 64 levels

- · Programmable interrupt modes

- Individual request mask capability

- Single +5-V supply (no clocks)

- 28-pin dual-in-line package

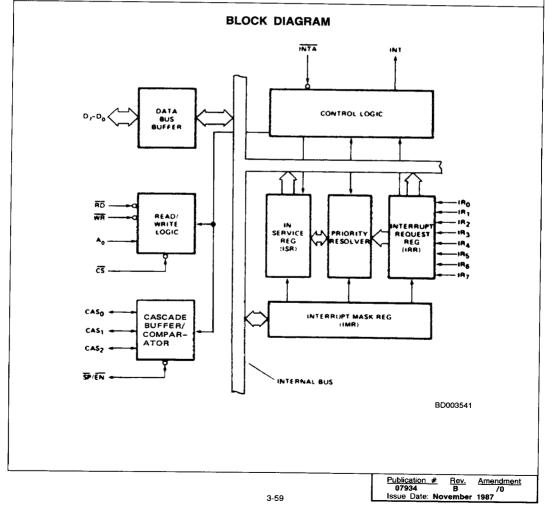

## GENERAL DESCRIPTION

The 8259A Programmable Interrupt Controller handles up to eight vectored priority interrupts for the CPU. It is cascadable for up to 64 vectored priority interrupts without additional circuitry. It is packaged in a 28-pin DIP, uses NMOS technology, and requires a single +5-V supply. Circuitry is static, requiring no clock input.

The 8259A is designed to minimize the software and realtime overhead in handling multi-level priority interrupts. It has several modes, permitting optimization for a variety of system requirements.

The 8259A is fully upward-compatible with the 8259. Software originally written for the 8259 will operate the 8259A in all 8259-equivalent modes.

## CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation.

## **MILITARY ORDERING INFORMATION**

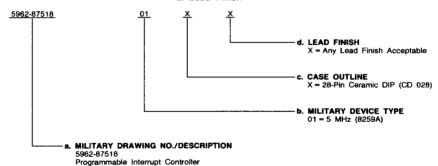

## Standard Military Drawing (SMD)/DESC Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. Standard Military Drawing (SMD)/DESC products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for SMD/DESC products is formed by a combination of: a. Military Drawing Part Number

- b. Device Type

- c. Case Outline

- d. Lead Finish

## Valid Combinations 5962-8751801 XX

## **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

## **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

## MILITARY ORDERING INFORMATION (Cont'd.)

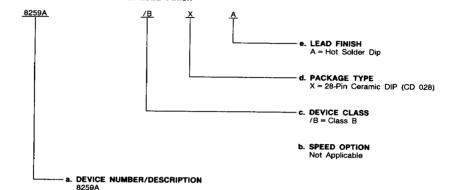

### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. **Device Number**

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type e. Lead Finish

# Valid Combinations 8259A /BXA

Programmable Interrupt Controller

### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

### Group A Tests

Group A tests consist of subgroups 1, 2, 3, 7, 8, 9 10, 11.

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65 to +15     | o°C |

|----------------------------------|-----|

| Voltage on Any Pin               |     |

| with Respect to Ground0.5 V to + | 7 V |

| Power Dissination                | 1 W |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

| Military (M) Devices              |    |     |       |

|-----------------------------------|----|-----|-------|

| Temperature (T <sub>C</sub> )     | 55 | to  | 125°C |

| Supply Voltage (V <sub>CC</sub> ) | 5  | ٠ ۲ | 10%   |

Operating ranges define those limits between which the functionality of the device is guaranteed.

**DC CHARACTERISTICS** over operating range (for SMD/DESC and APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol                    | Parameter<br>Description                        | Test Conditions                                    | Min.  | Max.                     | Unit |

|----------------------------------------|-------------------------------------------------|----------------------------------------------------|-------|--------------------------|------|

| VIL                                    | Input LOW Voltage                               | V <sub>CC</sub> = 4.5 V to 5.5 V                   | -0.5* | 0.8                      | ٧    |

| VIH                                    | Input HIGH Voltage                              | V <sub>CC</sub> = 4.5 V to 5.5 V                   | 2.3   | V <sub>CC</sub> + 0.5 V* | V    |

| VOL                                    | Output LOW Voltage                              | I <sub>OL</sub> = 2.2 mA, V <sub>CC</sub> = 4.5 V  |       | 0.45                     | ٧    |

| V <sub>OH</sub>                        | Output HIGH Voltage                             | I <sub>OH</sub> = -400 μA, V <sub>CC</sub> = 4.5 V | 2.4   |                          | ٧    |

|                                        | 1.1                                             | I <sub>OH</sub> = -100 μA, V <sub>CC</sub> = 4 V   | 3.5   |                          | ٧    |

| VOH(INT) Interrupt Output HIGH Voltage | I <sub>OH</sub> = -400 μ/ V <sub>CC</sub> 4.5 V | 2.4                                                |       | ٧                        |      |

| I <sub>EI</sub>                        | Input Load Current                              | V 5 N = 5.5 Y and 0 V                              | -10   | + 10                     | μΑ   |

| ILOL, ILOH                             | Output Leakage Current                          | V 5 V, UT = 5.5 V and 0.45 V                       | -10   | + 10                     | μA   |

| lcc                                    | V <sub>CC</sub> Supply Current                  | V <sub>C</sub> = 5.9 V (Note 1)                    |       | 125                      | mA   |

Notes: 1. I<sub>CC</sub> measured in a static condition with autput in a worst-case state, having standard I<sub>OL</sub>/I<sub>OH</sub> loads applied.

## CAPACITANCE (TARRESTON VCC = GND = 0 V)

| Parameter<br>Symbol | Parameter<br>Description | Test Conditions                 | Min. | Max. | Unit |

|---------------------|--------------------------|---------------------------------|------|------|------|

| C <sub>IN</sub> †   | Input Capacitance        | fc = 1 MHz                      |      | 10*  | pF   |

| C <sub>I/O</sub> †  | I/O Capacitance          | Unmeasured pins returned to VSS |      | 20*  | pF   |

\*Guaranteed by design; not tested. †Not included in Group A tests.

## SWITCHING TEST WAVEFORM

## Input/Output

Note: AC testing inputs are driven at 2.4 V for a logic "1" and 0.45 V for a logic "0." Timing measurements are made at 2.0 V for a logic "1" and 0.8 V for a logic "0."

See Section 6 of the MOS Microprocessors and Peripherals Data Book (Order #09067A) for Thermal Characteristics information. SWITCHING CHARACTERISTICS over operating range (for SMD/DESC and APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted).

| Parameter<br>No. Symbol | <b>D</b>           |                                                 |                 | 8259A |      |      |

|-------------------------|--------------------|-------------------------------------------------|-----------------|-------|------|------|

|                         |                    |                                                 | Test Conditions | Min.  | Max. | Unit |

| TIMING                  | REQUIREMENTS       | 5                                               |                 |       |      | -    |

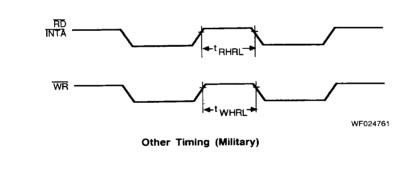

| 1                       | t <sub>AHRL</sub>  | A <sub>0</sub> /CS Setup to RD/INTA             |                 | 0     |      | ns   |

| 2                       | t <sub>RHAX</sub>  | A <sub>0</sub> /CS Hold after RD/INTA           |                 | 0     |      | ns   |

| 3                       | <sup>t</sup> RLRH  | RD Pulse Width                                  |                 | 235   |      | ns   |

| 4                       | t <sub>AHWL</sub>  | A <sub>0</sub> /CS Setup to WR↓                 |                 | 0     |      | ns   |

| 5                       | twhax              | A <sub>0</sub> /CS Hold after WR1               |                 | 0     |      | ns   |

| 6                       | twLwH              | WR Pulse Width                                  |                 | 290   |      | ns   |

| 7                       | t <sub>DVWH</sub>  | Data Setup to WR1                               | (Note 1)        | 240   |      | ns   |

| 8                       | twhox              | Data Hold after WR;                             |                 | 0     |      | ns   |

| 9                       | tJLJH              | Interrupt Request Width (LOW)                   | **              | 100   |      | ns   |

| 10                      | <sup>‡</sup> CVIAL | Cascade Setup Second or Third NTA! (Slave Only) |                 | 55    |      | ns   |

| 11                      | tahal .            | End of RD to next Command                       |                 | 300   |      | ns   |

| 12                      | twhal              | End of WR to next Com                           |                 | 370   |      | ns   |

| TIMING                  | RESPONSES          |                                                 |                 |       |      |      |

| 13                      | IRLOV              | Data Valid from ADA JA                          |                 |       | 200  | ns   |

| 14                      | <sup>t</sup> RHDZ  | Data Float after D/IN 1                         |                 | 10    | 100  | ns   |

| 15                      | Uнiн               | Interrupt tuput Deby                            |                 |       | 350  | ns   |

| 16                      | †IALCV             | Casado Va m First iNTA:                         |                 |       | 565  | ns   |

| 17                      | taler.             | that e ctive from RD1 or INTA1                  | (Notes 1 and 2) |       | 125  | ns   |

| 18                      | tanen              | Inactive from RD1 or INTA1                      |                 |       | 150  | ns   |

| 19                      | tahdv              | Data Valid from Stable Address                  |                 |       | 200  | ns   |

| 20                      | tcvpv              | Cascade Valid to Valid Data                     |                 |       | 300  | ns   |

Notes: 1. Test Conditions:  $V_{CC}$  = 4.5 V to 5.5 V  $V_{CL}$  = 0.45 V,  $V_{IH}$  = 2.4 V;  $V_{OL}$  = 0.8 V,  $V_{OH}$  = = 2.0 V  $V_{OH}$  = 2.2 mA,  $V_{OH}$  = -400  $V_{OH}$  =-400  $V_{OH}$