# 2816A/2816AH 5516A/5516AH

Timer E<sup>2</sup> 16K Electrically Erasable PROMs

August 1992

#### Features

- Military and Extended Temperature Range

- - 55°C to + 125°C, Operation (Military)

- - 40°C to +85°C, Operation (Extended)

- 0°C to +70°C, Operation (Commercial)

- End of Write Detection

- Optional DATA Polling Feature

- High Endurance Write Cycles

- · 2816A: 10,000 Cycles/Byte Minimum

- 5516A: 100K, 400K and 1 Million Cycles/Byte

- On-Chip Timer

- · Automatic Erase and Write Time Out

- M All Inputs Latched by Write or Chip Enable

- 5 V ± 10% Power Supply

- Power Up/Down Protection Circuitry

- 150 ns max. Access Time

- Low Power Operation

- · 100 mA max. Active Current

- · 40 mA max. Standby Current

- JEDEC Approved Byte-Wide Pinout

- MIL-STD-883 Class B Compliant

### Description

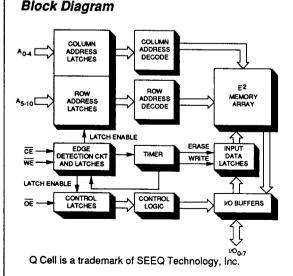

SEEQ's 2816A/5516A are 5V only, 2K x 8 electrically erasable programmable read only memories (EEPROMs). EEPROMs are ideal for applications which require nonvolatility and in-system data modification. The endurance, the minimum number of times that a byte may be written, is 10 thousand (K) for the 2816A, and 100K, 400K or 1 million cycles for the 5516A. The 5516A's high endurance was accomplished using SEEQ's proprietary oxyntride EEPROM process and its innovative Q Cell<sup>TM</sup> design. The 2816A/5516A is ideal for systems that require frequent updates.

There is an internal timer that automatically times out the write time. A separate erase cycle is not required and the minimum write enable (WE) pulse width needs to be as little as 100 ns depending on device address access time.

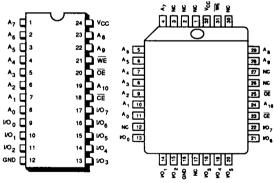

## Pin Configuration

DUAL-IN-LINE PLASTIC LEADED

TOP VIEW CHIP CARRIER TOP VIEW

NOTE: For PLCC - Ready/Busy pin option is always connected unless otherwise specified.

### Pin Names

| A <sub>0</sub> -A <sub>10</sub> | ADDRESSES                                         |

|---------------------------------|---------------------------------------------------|

| CE                              | CHIP ENABLE                                       |

| ŌĒ                              | OUTPUT ENABLE                                     |

| WE                              | WRITE ENABLE                                      |

| I/O <sub>0.7</sub>              | DATA INPUT (WRITE OR ERASE)<br>DATA OUTPUT (READ) |

The on-chip timer, along with the inputs being latched by a write or chip enable signal edge, frees the microcomputer system for other tasks during the write time. The standard 2816A/5516A's write time is 10 ms, while the 2816AH/5516AH write time is a fast 2ms. Once a byte is written, it can be read in a maximum of 150 ns. The inputs are TTL for both the byte write and read mode.

### **Device Operation**

There are five operational modes (see Table 1) and, except for the chip erase mode [1], only TTL inputs are required. To write into a particular location, a TTL low is applied to write enable (WE) pin of a selected (CE low) device. This, combined with output enable (OE) being high, initiates a write cycle. During a byte write cycle, addresses are latched on the last falling edge of CE or WE and data is latched on the first rising edge of CE or WE. An internal timer times out the required byte write time. An automatic byte erase is performed internally in the byte write mode.

## DATA Polling (Optional Feature)

DATA polling is a method of minimizing write times by determining the actual end-point of a write cycle. If a read is performed to any address while the device is still writing, it will present the ones-complement of the last byte written. When the device has completed its write cycle, a read from the last address written will result in valid data. Thus, software can simply read from the part until the last data byte written is read correctly. Timing for a DATA polling read is the same as a normal read.

### Mode Selection (Table 1)

| Mode       | CE              | ŌĒ              | WE              | 1/0                                                |

|------------|-----------------|-----------------|-----------------|----------------------------------------------------|

| Read       | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | D <sub>out</sub>                                   |

| Standby    | V <sub>IH</sub> | Х               | Х               | High Z                                             |

| Byte Write | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | D <sub>IN</sub>                                    |

| Write      | Х               | V <sub>IL</sub> | X               | High Z/D <sub>out</sub><br>High Z/D <sub>out</sub> |

| Inhibit    | X               | X -             | V <sub>IH</sub> | High Z/D <sub>out</sub>                            |

X: any TTL level

### Absolute Maximum Stress Ratings\*

| l emperature                      |                       |

|-----------------------------------|-----------------------|

| Storage                           | 65°C to +150°C        |

| Under Bias                        |                       |

| Military/Extended                 | 65° C to +135° C      |

| Commercial                        |                       |

| D.C. Voltage applied to all Input | s or Outputs          |

| with respect to ground            | +6.0 V to -0.5 V      |

| Undershoot/Overshoot pulse of     | less then 10 ns       |

| (measured at 50% point) applied   | d to all inputs or    |

| outputs with respect to ground    | i (undershoot) -1.0 V |

|                                   | (overshoot) + 7.0 V   |

|                                   |                       |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Recommended Operating Conditions**

|                              |            | 2816A/2816AH-150<br>5516A/5516AH-150 | 2816A/2816AH-200<br>5516A/5516AH-200 | 2816A/2816AH-250<br>5516A/5516AH-250 | 2816A/2816AH-300<br>5516A/5516AH-300 |

|------------------------------|------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|

| Temperature                  | Commercial | 0°C to +70°C                         | 0°C to +70°C                         | 0°C to +70°C                         | 0°C to +70°C                         |

| Range                        | Extended   | -40°C to +85°C                       | -40°C to +85°C                       | -40°C to +85°C                       | -40°C to +85°C                       |

|                              | Military   | -55°C to +125°C                      | -55°C to +125°C                      | -55°C to +125°C                      | -55°C to +125°C                      |

| V <sub>cc</sub> Supply Volta | age        | 5V±10%                               | 5V±10%                               | 5V±10%                               | 5V±10%                               |

### **Endurance and Data Retention**

| Symbol          | Parameter                  | Value                           | Units       | Condition                       |

|-----------------|----------------------------|---------------------------------|-------------|---------------------------------|

| N               | Minimum Endurance<br>2816A | 10,000                          | Cycles/Byte | MIL-STD 883 Test<br>Method 1033 |

|                 | 5516A                      | 100,000<br>400,000<br>1,000,000 | Cycles/Byte | MIL-STD 883 Test<br>Method 1033 |

| T <sub>DR</sub> | Data Retention             | >10                             | Years       | MIL-STD 883 Test<br>Method 1033 |

#### Notes:

- 1. Chip Erase is an optional mode.

- 2. Characterized. Not tested.

### Power Up/Down Considerations

The 2816A/5516A has internal circuitry to minimize a false write during system V<sub>cc</sub> power up or down. This circuitry prevents writing under any one of the following conditions.

- 1. V<sub>CC</sub> is less than 3V.<sup>[2]</sup>

2. A negative Write Enable (WE) transition has not occured when V<sub>cc</sub> is between 3 V and 5 V.

Writing will also be prevented if  $\overline{CE}$  or  $\overline{OE}$  are in a logical state other than that specified for a byte write in the Mode Selection table.

# $\ensuremath{\textit{DC Operating Characteristics}}$ (Over the operating $V_{cc}$ and temperature range)

|                 | Parameter                       | Li   | mits  |       |                                                                                               |

|-----------------|---------------------------------|------|-------|-------|-----------------------------------------------------------------------------------------------|

| Symbol          |                                 | Min. | Max.  | Units | Test Condition                                                                                |

| l <sub>cc</sub> | Active V <sub>cc</sub> Current  |      | 100   | mA    | CE = OE =V <sub>IL</sub> ; All I/O Open;<br>Other Inputs = 5.5 V                              |

|                 |                                 |      |       |       | CE = OE =V <sub>IL</sub> ; All I/O Open;<br>Other Inputs = 5.5 V                              |

| I <sub>SB</sub> | Standby V <sub>cc</sub> Current |      | 40    | mA    | $\overline{CE} = V_{IH}$ , $\overline{OE} = V_{IL}$ ; All I/O's<br>Open; Other Inputs = 5.5 V |

| l <sub>LI</sub> | Input Leakage Current           |      | 10    | μΑ    | V <sub>IN</sub> = 5.5 V                                                                       |

| I <sub>LO</sub> | Output Leakage Current          |      | ·- 10 | μА    | V <sub>OUT</sub> = 5.5 V                                                                      |

| V <sub>IL</sub> | Input Low Voltage               | -0.1 | 0.8   | ٧     |                                                                                               |

| V <sub>IH</sub> | Input High Voltage              | 2.0  | 6     | ٧     |                                                                                               |

| V <sub>oL</sub> | Output Low Voltage              |      | 0.4   | ٧     | l <sub>oL</sub> = 2.1 mA                                                                      |

| V <sub>oh</sub> | Output High Voltage             | 2.4  |       | ٧     | I <sub>OH</sub> = -400 μA                                                                     |

## Capacitance [1] T, = 25°C, f = 1 MHz

| Symbol           | Parameter              | Max   | Conditions             |

|------------------|------------------------|-------|------------------------|

| C <sub>IN</sub>  | Input Capacitance      | 6 pF  | V <sub>IN</sub> = 0 V  |

| C <sub>out</sub> | Data (I/O) Capacitance | 10 pF | V <sub>I/O</sub> = 0 V |

1. This parameter measured only for the initial qualification and after process or design changes which may affect capacitance.

## Equivalent A.C. Test Conditions

Output Load: 1 TTL gate and C, = 100 pF Input Rise and Fall Times: < 20 ns Input Pulse Levels: 0.45 V to 2.4 V Timing Measurement Reference Level: Inputs 1 V and 2 V Outputs 0.8 V and 2 V

### AC Characteristics

Read Operation (Over the operating V<sub>cc</sub> and temperature range)

| Symbol              | Parameter                    | Limits |      |                                      |      |      |      |                                      |      |       |

|---------------------|------------------------------|--------|------|--------------------------------------|------|------|------|--------------------------------------|------|-------|

|                     |                              |        |      | 2816A/2816AH-200<br>5516A/5516AH-200 |      |      |      | 2816A/2816AH-300<br>5516A/5516AH-300 |      |       |

|                     |                              | Min.   | Max. | Min.                                 | Max. | Min. | Max. | Min.                                 | Max. | Units |

| t <sub>ec</sub>     | Read Cycle Time              | 150    |      | 200                                  |      | 250  |      | 300                                  |      | ns    |

| t <sub>CE</sub>     | Chip Enable Access Time      | 1      | 150  | <u> </u>                             | 200  |      | 250  |                                      | 300  | ns    |

| t <sub>AA</sub>     | Address Access Time          | 1      | 150  |                                      | 200  |      | 250  |                                      | 300  | ns    |

| toE                 | Output Enable Access Time    |        | 70   |                                      | 90   |      | 90   | <u> </u>                             | 100  | ns    |

| t <sub>LZ</sub>     | CE to Output in Low Z        | 10     |      | 10                                   |      | 10   |      | 10                                   |      | ns    |

| t <sub>HZ</sub>     | CE to Output in High Z       |        | 100  |                                      | 100  |      | 100  |                                      | 100  | ns    |

| t <sub>oLZ</sub>    | OE to Output in Low Z        | 50     |      | 50                                   |      | 50   |      | 50                                   |      | ns    |

| tonz                | OE to Output in High Z       |        | 100  |                                      | 100  |      | 100  |                                      | 100  | ns    |

| t <sub>oH</sub> [1] | Output Hold from Addr Change | 20     |      | 20                                   |      | 20   |      | 20                                   |      | กร    |

| t <sub>PU</sub> [1] | CE to Power-up Time          | 0      |      | 0                                    |      | 0    |      | 0                                    |      | ns    |

| t <sub>PD</sub> [1] | CE to Power Down Time        |        | 50   |                                      | 50   |      | 50   | <u> </u>                             | 50   | ns    |

#### NOTES:

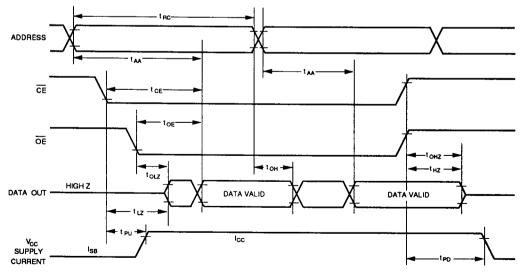

## Read Cycle Timing

1-18

<sup>1.</sup> This parameter measured only for the initial qualification and after process or design changes which may affect capacitance.

## 2816A/2816AH 5516A/5516AH

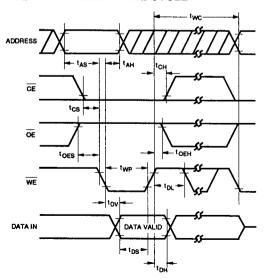

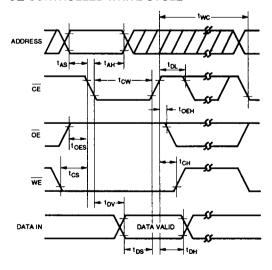

# ${\it AC\ Characteristics}\ {\it Write\ Operation}\ ({\it Over\ the\ operating\ V_{cc}}\ {\it and\ temperature\ range})$

|                                |                          | Limits                 |      |                              |      |                              |      |                              |      |       |

|--------------------------------|--------------------------|------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|-------|

|                                |                          | 2816A/AH-<br>5516A/AH- |      | 2816A/AH-200<br>5516A/AH-200 |      | 2816A/AH-250<br>5516A/AH-250 |      | 2816A/AH-300<br>5516A/AH-300 |      |       |

| Symbol                         | Parameter                | Min.                   | Max. | Min.                         | Max. | Min.                         | Max. | Min.                         | Max. | Units |

| t <sub>wc</sub>                | Write Cycle Time         |                        |      |                              |      |                              |      |                              |      |       |

|                                | 2816AH/5516AH            |                        | 2    |                              | 2    |                              | 2    |                              | 2    | ms    |

|                                | 2816A/5516A              |                        | 10   |                              | 10   |                              | 10   |                              | 10   | ms    |

| tas                            | Address Set Up Time      | 10                     |      | 10                           |      | 10                           |      | 10                           |      | ns    |

| t <sub>AH</sub>                | Address Hold Time        | 50                     |      | 50                           |      | 50                           |      | 70                           |      | ns    |

| t <sub>cs</sub>                | Write Set Up Time        | 0                      |      | 0                            |      | 0                            |      | 0                            |      | ns    |

| t <sub>cH</sub>                | Write Hold Time          | 0                      |      | 0                            |      | 0                            |      | 0                            |      | ns    |

| t <sub>cw</sub>                | CE to End of Write Input | 150                    |      | 150                          |      | 150                          |      | 150                          |      | ns    |

| t <sub>oes</sub>               | OE Set Up Time           | 10                     |      | 10                           |      | 10                           |      | 10                           |      | ns    |

| t <sub>OEH</sub>               | OE Hold Time             | 10                     |      | 10                           |      | 10                           |      | 10                           |      | กร    |

| t <sub>wp</sub> [1]            | WE Write Pulse Width     | 100                    |      | 150                          |      | 150                          |      | 150                          |      | ns    |

| t <sub>DL</sub>                | Data Latch Time          | 50                     |      | 50                           |      | 50                           |      | 50                           |      | ns    |

| t <sub>DV</sub> <sup>[2]</sup> | Data Valid Time          |                        | 1    | <u> </u>                     | 1    |                              | 1    |                              | 1    | μѕ    |

| t <sub>os</sub>                | Data Set Up Time         | 50                     |      | 50                           |      | 50                           |      | 50                           |      | ns    |

| t <sub>DH</sub>                | Data Hold Time           | 0                      |      | 0                            |      | 0                            |      | 0                            |      | ns    |

#### NOTES:

- 1. WE is noise protected. Less than a 20 ns write pulse will not activate a write cycle.

- 2. Data must be valid within 1 µs maximum after the initiation of a write cycle.

## TTL Byte Write Cycle

### WE CONTROLLED WRITE CYCLE

### **CE CONTROLLED WRITE CYCLE**

## 2816A/2816AH 5516A/5516AH

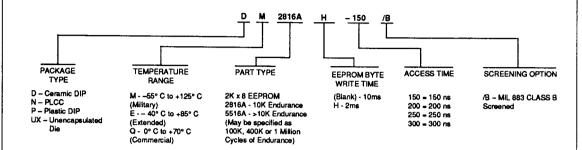

## **Ordering Information**