# REGULATING PULSE WIDTH MODULATORS

- COMPLETE PWM POWER CONTROL CIR-CUITRY

- UNCOMMITTED OUTPUTS FOR SINGLE-ENDED OR PUSH PULL APPLICATIONS

- LOW STANDBY CURRENT 8mA TYPICAL

- OPERATION UP TO 300KHz

- 1% MAXIMUM TEMPERATURE VARIATION OF REFERENCE VOLTAGE

#### DESCRIPTION

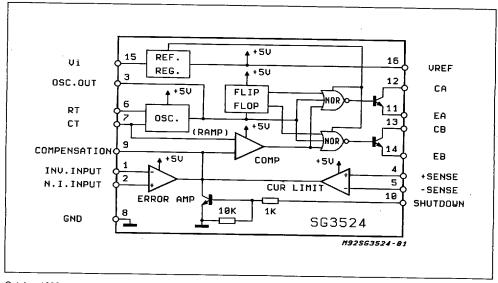

The SG2524, and SG3524 incorporate on a single monolithic chip all the function required for the construction of regulating power suppies inverters or switching regulators. They can also be used as the control element for high power-output applications. The SG3524 family was designed for switching regulators of either polarity, transformer-coupled dc-to-dc converters, transformer-less voltage doublers and polarity converter applications employing fixed-frequency, pulse-width modulation techniques. The dual alternating outputs allows either single-ended or push-pull appli-

cations. Each device includes an on-ship reference, error amplifier, programmable oscillator, pulse-steering flip flop, two uncommitted output transistors, a high-gain comparator, and current-limiting and shut-down circuitry.

## **BLOCK DIAGRAM**

October 1992

7929237 0051535 889 📟

1/6

535

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                             | Value       | Unit |

|------------------|-------------------------------------------------------|-------------|------|

|                  | Supply Voltage                                        | 40          |      |

| V <sub>IN</sub>  | Collector Output Current                              | 100         | mA   |

| <u>lc</u>        | Reference Output Current                              | 50          | mA   |

| IR               | Current Through C <sub>T</sub> Terminal               | -5          | mA   |

| <u> </u>         | Total Power Dissipation at T <sub>amb</sub> = 70°C    | 1000        | mV   |

| Ptot             |                                                       | - 65 to 150 | °C   |

| T <sub>stg</sub> | Storage Temperature Range                             | - 25 to 85  | °C   |

| Top              | Operating Ambient Temperature Range: SG2524<br>SG3524 | 0 to 70     | °C   |

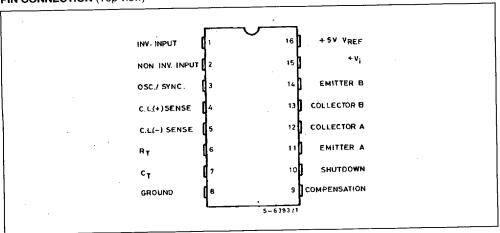

## PIN CONNECTION (Top view)

#### THERMAL DATA

| Symbol                | Parameter                                                                   |              | DIP16 | SO16   | Unit         |

|-----------------------|-----------------------------------------------------------------------------|--------------|-------|--------|--------------|

| R <sub>th j-amb</sub> | Thermal Resistance Junction-ambient Thermal Resistance Junction-alumina (*) | Max.<br>Max. | 80    | <br>50 | ∘C\M<br>∘C\M |

| Rth j-alumina         | Thermal resistance currents (7                                              |              |       |        |              |

<sup>(\*)</sup> Thermal resistance junction-alumina with the device soldered on the middle of an alumina supporting substrate measuring 15 x 20mm; 0.65mm thickness with infinite heatsink.

**ELECTRICAL CHARACTERISTICS** (unless otherwise stated, these specifications apply for Tj = -25 to +85°C for the SG2524, and 0 to 70°C for the SG3524,  $V_{IN}$  = 20V, and f = 20KHz).

| Symbol                | Parameter                      | Test Condition                                                           | SG2524   |      | SG3524 |             | I I m i a |      |       |

|-----------------------|--------------------------------|--------------------------------------------------------------------------|----------|------|--------|-------------|-----------|------|-------|

|                       |                                |                                                                          | Min.     | Тур. | Max.   | Min.        | Тур.      | Max. | Unit  |

|                       | NCE SECTION                    |                                                                          |          |      |        |             |           |      |       |

| V <sub>REF</sub>      | Output Voltage                 |                                                                          | 4.8      | 5    | 5.2    | 4.6         | 5         | 5.4  | V     |

| $\Delta V_{REF}$      | Line Regulation                | Vin = 8 to 40V                                                           | <u> </u> | 10   | 20     |             | 10        | 30   | mV    |

| $\Delta V_{REF}$      | Load Regulation                | IL = 0 to 20mA                                                           | ļ        | 20   | 50_    |             | 20        | 50   | mV    |

|                       | Ripple Rejection               | f = 120Hz, T <sub>i</sub> = 25°C                                         | L        | 66   |        |             | 66        |      | dB    |

|                       | Short Circuit Current<br>Limit | V <sub>REF</sub> = 0, T <sub>j</sub> = 25°C                              |          | 100  |        |             | 100       |      | mA    |

| ΔV <sub>REF</sub> /ΔT | Temperature Stability          | Over Operating<br>Temperature range                                      |          | 0.3  | 1      |             | 0.3       | 1    | %     |

| $\Delta V_{REF}$      | Long Term Stability            | Tj = 125°C, t = 1000Hrs                                                  |          | 20   |        |             | 20        |      | mV    |

| OSCILLA               | TOR SECTION                    |                                                                          |          |      |        |             |           |      |       |

| f <sub>MAX</sub>      | Maximum Frequency              | $C_T = 0.001 \mu F$ , $R_T = 2K\Omega$                                   |          | 300  |        |             | 300       |      | KHz   |

|                       | Initial Accuracy               | R <sub>T</sub> and C <sub>T</sub> Constant                               |          | 5    |        |             | 5         |      | %     |

|                       | Voltage Stability              | $V_{IN} = 8 \text{ to } 40V, T_j = 25^{\circ}C$                          |          |      | 1      |             |           | 1    | %     |

| Δf/ΔT                 | Temperature Stability          | Over Operating<br>Temperature Range                                      |          |      | 2      | -           |           | 2    | %     |

|                       | Output Amplitude               | Pin 3, T <sub>i</sub> = 25°C                                             |          | 3.5  |        |             | 3.5       |      | V     |

|                       | Output Pulse Width             | $C_T = 0.01 \mu F$ , $T_j = 25^{\circ}C$                                 |          | 0.5  |        |             | 0.5       |      | μѕ    |

| ERROR A               | AMPLIFIER SECTION              |                                                                          |          |      |        |             |           |      |       |

| Vos                   | Input Offset Voltage           | $V_{CM} = 2.5V$                                                          |          | 0.5  | 5      |             | 2         | 10   | mV    |

| l <sub>b</sub>        | Input Bias Current             |                                                                          |          | 2    | 10     |             | 2         | 10   | μА    |

| Gv                    | Open Loop Voltage Gain         |                                                                          | 72       | 80   |        | 60          | 80        |      | dB    |

| CMV                   | Common Mode Voltage            | T <sub>i</sub> = 25°C                                                    | 1.8      |      | 3.4    | 1.8         |           | 3.4  | V     |

| CMR                   | Common Mode Rejection          | T <sub>j</sub> = 25°C                                                    |          | 70   |        |             | 70        |      | dB    |

| B                     | Small Signal Bandwidth         | $A_V = 0$ dB, $T_j = 25$ °C                                              |          | 3    |        |             | 3         |      | MHz   |

| Vo                    | Output Voltage                 | T <sub>j</sub> = 25°C                                                    | 0.5      |      | 3.8    | 0.5         |           | 3.8  | V     |

| COMPAR                | ATOR SECTION                   |                                                                          |          |      |        |             |           |      |       |

|                       | Duty-cycle                     | % Each Output On                                                         | 0        |      | 45     | 0           |           | 45   | %     |

| VIT                   | Input Threshold                | Zero Duty-cycle                                                          |          | 1    |        |             | 1         |      | V     |

|                       |                                | Maximum Duty-cycle                                                       |          | 3.5  |        |             | 3.5       |      | V     |

| lb                    | Input Bias Current             |                                                                          |          | 1    |        |             | _ 1       |      | μА    |

| CURREN                | T LIMITING SECTION             |                                                                          |          |      |        |             |           |      |       |

|                       | Sense Voltage                  | Pin 9 = 2V with Error<br>Amp. Set for Max. Out.<br>T <sub>i</sub> = 25°C | 190      | 200  | 210    | 180         | 200       | 220  | mV    |

|                       | Sense Voltage T.C.             |                                                                          |          | 0.2  |        |             | 0.2       |      | mV/°C |

| CMV                   | Common Mode Voltage            |                                                                          | -1       |      | 1      | -1          |           | 1    | ,     |

| OUTPUT                | SECTION(each output)           |                                                                          |          |      | -      |             |           |      |       |

|                       | Collector-emitter Voltage      |                                                                          | 40       |      |        | 40          | -         |      | V     |

|                       | Collector Leackage Curr.       | V <sub>CE</sub> = 40V                                                    |          | 0.1  | 50     |             | 0.1       | 50   | μΑ    |

|                       | Saturation Voltage             | I <sub>C</sub> = 50mA                                                    |          | 1    | 2      | $\neg \neg$ | 1         | 2    | V     |

|                       | Emitter Output Voltage         | V <sub>IN</sub> = 20V                                                    | 17       | 18   |        | 17          | 18        |      | V     |

| tr                    | Rise Time                      | $R_C = 2K\Omega$ , $T_j = 25^{\circ}C$                                   |          | 0.2  |        |             | 0.2       |      | μs    |

| tf                    | Fall Time                      | $R_C = 2K\Omega$ , $T_j = 25^{\circ}C$                                   |          | 0.1  |        |             | 0.1       |      | μs    |

| l <sub>q</sub> (*)    | Total Standby Current          | V <sub>IN</sub> = 40V                                                    |          | 8    | 10     |             | 8         | 10   | mA    |

| 7929237 0051537 651 |

3/6

537

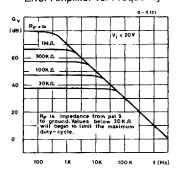

Figure 1: Open-loop Voltage Amplification of Error Amplifier vs. Frequency

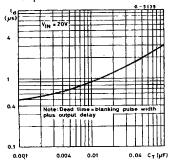

Figure 3: Output Dead Time vs. Timing Capacitance Value.

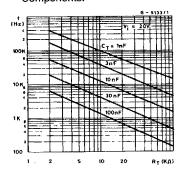

Figure 2: Oscillator Frequency vs. Timing Components.

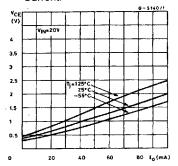

Figure 4: Output Saturation Voltage vs. load Current.

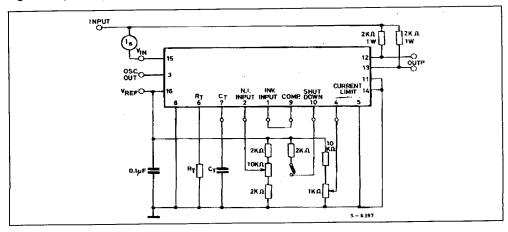

Figure 5: Open Loop Test Circuit.

0051538

598

4/6 **538**

This Material Copyrighted By Its Respective Manufacturer

7929237

#### PRINCIPLES OF OPERATION

The SG2524/3524 is a fixed frequency pulsewith-modulation voltage regulator control circuit. The regulator operates at a frequency that is programmed by one timing resistor (RT) and one timing capacitor (CT). RT established a constant charging current for CT. This results in a linear voltage ramp at CT, which is fed to the comparator providing linear control of the output pulse width by the error amplifier, the SG2524/3524 contains, an on-board 5V regulator that serves as reference as well powering as SG2524/3524's internal control circuitry and is also useful in supplying external support functions. This reference voltage is lowered externally by a resistor divider to provide a reference within the common mode range the error amplifier or an external reference may be used. The power supply output is sensed by a second resistor divider network to generale a feedback signal to error amplifier. The amplifier output voltage is then compared to the linear voltage ramp at CT. The resulting modulated pulse out of the high-gain comparator is then steered to the appropriate output pass transistors (QA or QB) by the pulsesteering flip-flop, which is synchronously toggled by the oscillator output. The oscillator output pulse also serves as a blanking pulse to assure both output are never on simultaneously during the transition times. The width of the blanking pulse is controlled by the value of CT. The outputs may be applied in a push-pull configuration in which their frequency is half that of the base oscillator, or paralleled for single-ended applications in which the frequency is equal to that of the oscillator. The output of the error amplifier shares a common input to the comparator with the current limiting at shutdown circuitry and can be overridden by signals from either of these inputs. This common point is also available externally and may be employed to control the gain of, or to compensate, the error amplifier, or to provide additional control to the regulator.

#### RECOMMENDED OPERATING CONDITIONS

| Supply voltage V <sub>IN</sub>         | 8 to 40V       |  |  |  |

|----------------------------------------|----------------|--|--|--|

| Reference Output Current               | 0 to 20mA      |  |  |  |

| Current trough C <sub>T</sub> Terminal | - 0.03 to -2mA |  |  |  |

| Timing Resistor, R <sub>T</sub>        | 1.8 to 100KΩ   |  |  |  |

| Timing Capacitor, C <sub>T</sub>       | 0.001 to 0.1μF |  |  |  |

# TYPICAL APPLICATIONS DATA

OSCILLATOR

The oscillator controls the frequency of the

SG2524 and is programmed by R<sub>T</sub> and C<sub>T</sub> according to the approximate formula:

$$f = \frac{1.18}{R_T C_T}$$

where: R<sub>T</sub> is in KΩ C<sub>T</sub> is in μF f is in KHz

Pratical values of  $C_T$  fall between 0.001 and 0.1 $\mu$ F. Pratical values of  $R_T$  fall between 1.8 and 100K $\Omega$ . This results in a frequency range typically from 120Hz to to 500KHz.

#### BLANKING

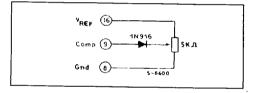

The output pulse of oscillator is used as a blanking pulse at the output. This pulse width is controlled by the value of C<sub>T</sub>.If small values of C<sub>T</sub> are required for frequency control, the oscillator output pulse width may still be increased by applying a shunt capacitance of up to 100pF from pin 3 to ground. If still greater dead-time is required, it should be accomplished by limiting the maximum duty cycle by clamping the output of the error amplifier. This can easily be done with the circuit below:

Figure 6.

## SYNCRONOUS OPERATION

When an external clock is desired, a clock pulse of approximately 3V can be applied directly to the oscillator output terminal. The impedance to ground at this point is approximately  $2K\Omega$ . In this configuration R<sub>T</sub> C<sub>T</sub> must be selected for a clock period slightly greater than that the external clock.

If two more SG2524 regulators are to be operated synchronously, all oscillator output terminals should be tied together, all CT terminals connected to a single timing capacitor, and timing resistor connected to a single RT terminal. The other RT terminals can be left open or shorted to VREF. Minimum lead lengths should be used between the CT terminals.

7929237 0051539 424

5/6

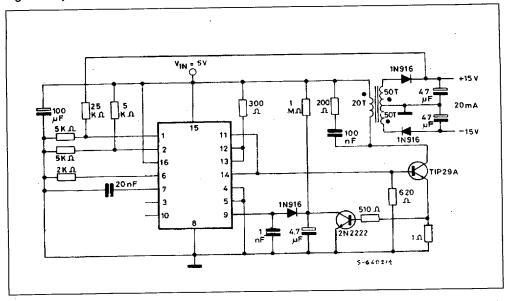

Figure 7: Flyback Converter Circuit.

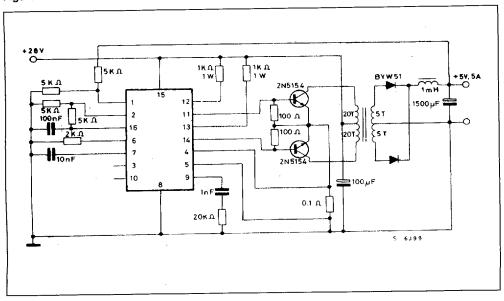

Figure 8: PUSH-PULL Transformer-coupled circuit.

6/6 7929237 0051540 146 **■**

This Material Copyrighted By Its Respective Manufacturer