| Document information |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Info                 | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>Keywords</b>      | PCB2115, Demonstration board, ADC, ADC1613D, ADC1413D, ADC1213D, ADC1113D, Altera, Xilinx, Lattice,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>Abstract</b>      | This document describes how to use the demonstration board PCB2115 ( ADC1x13D board without FPGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>Block Diagram</b> | <p>The I/Q Demodulator down converts an RF signal to IF frequency based on programmed LO synthesizer frequency. The dual ADC performs IF baseband sampling, and transmits real digital data to FPGA connector via the Jedece JESD204A interface. The Clock Generator provides clocks for entire system, including ADC and FPGA. The SPI interface provides control and status of all programmable elements. In standalone mode , the SPI bus is controlled by USB interface. In FPGA mode the SPI bus is directly controlled by FPGA.</p>                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Main features</b> | <ul style="list-style-type: none"> <li>ADC sampling rate = 125Msps max.</li> <li>The ADC clock provided by either on board clock generator or by an external clock generator</li> <li>ADC input connected to either on board RF I/Q demodulator or to external IF inputs.</li> <li>Demodulation sampling rate controlled by either on board LO synthesizer or by an external clock.</li> <li>Maximum ADC analog input bandwidth will be 600MHz.</li> <li>Standalone mode : <ul style="list-style-type: none"> <li>ADC, ADC clock generator and Demodulator clock synthesizer are controlled by PC application via SPI/USB interface</li> <li>Single 6.5Vdc external power supply</li> </ul> </li> <li>FPGA mode : <ul style="list-style-type: none"> <li>ADC, ADC clock generator and Demodulator clock synthesizer are controlled by FPGA via SPI interface</li> <li>Power supply from 12Vdc FPGA host board</li> </ul> </li> </ul> |

# 1. Quick start

## 1.1 Setup overview

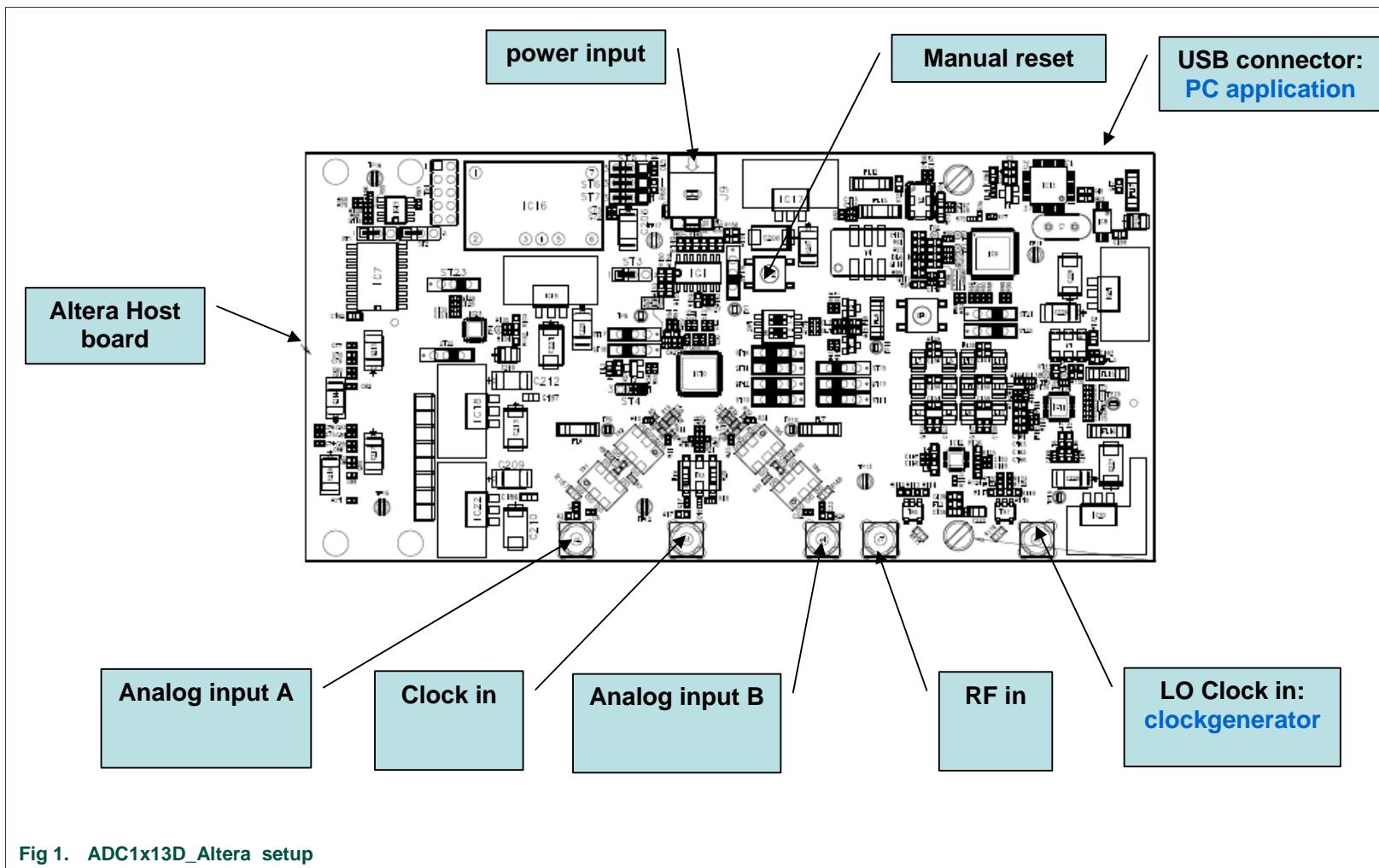

The following figure presents the connections of the ADC1x13D\_Altara board.

## 1.2 FPGA Board interface

The PCB2115 board includes an HSMC connector in order to connect it to the Altera evaluation board. In order to connect to the Xilinx evaluation board, the board adaptor reference HSDC\_ACC01/DB need to be used. In order to connect to the Lattice evaluation board, the board adaptor reference HSDC\_ACC02/DB need to be used. Both addaptator need to be ordered separately.

## 1.3 Power supply

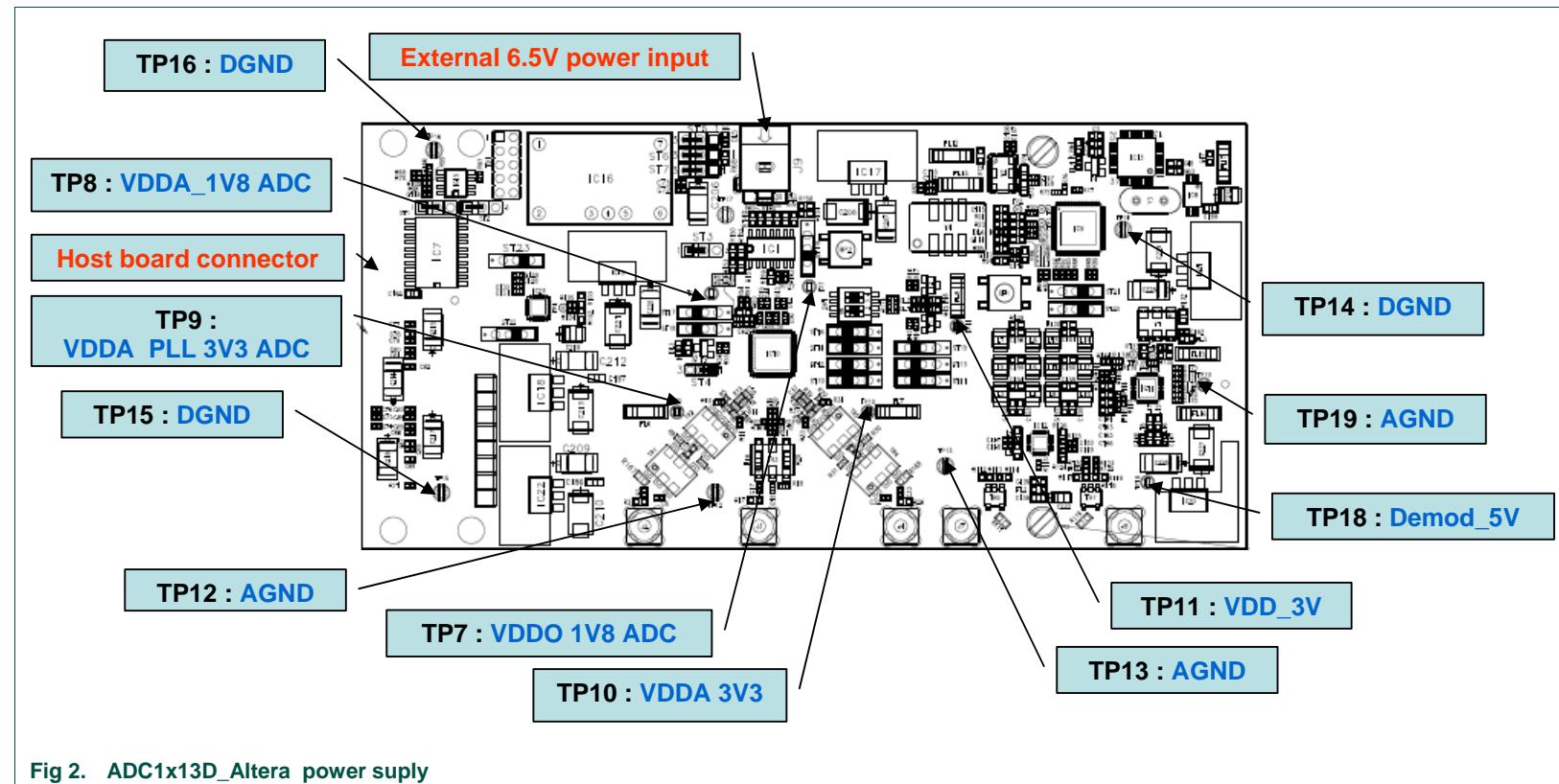

The following figure presents the power supply input / test point of the ADC1x13D\_Alttera board:

Fig 2. ADC1x13D\_Alttera power supply

## 1.4 Board configuration

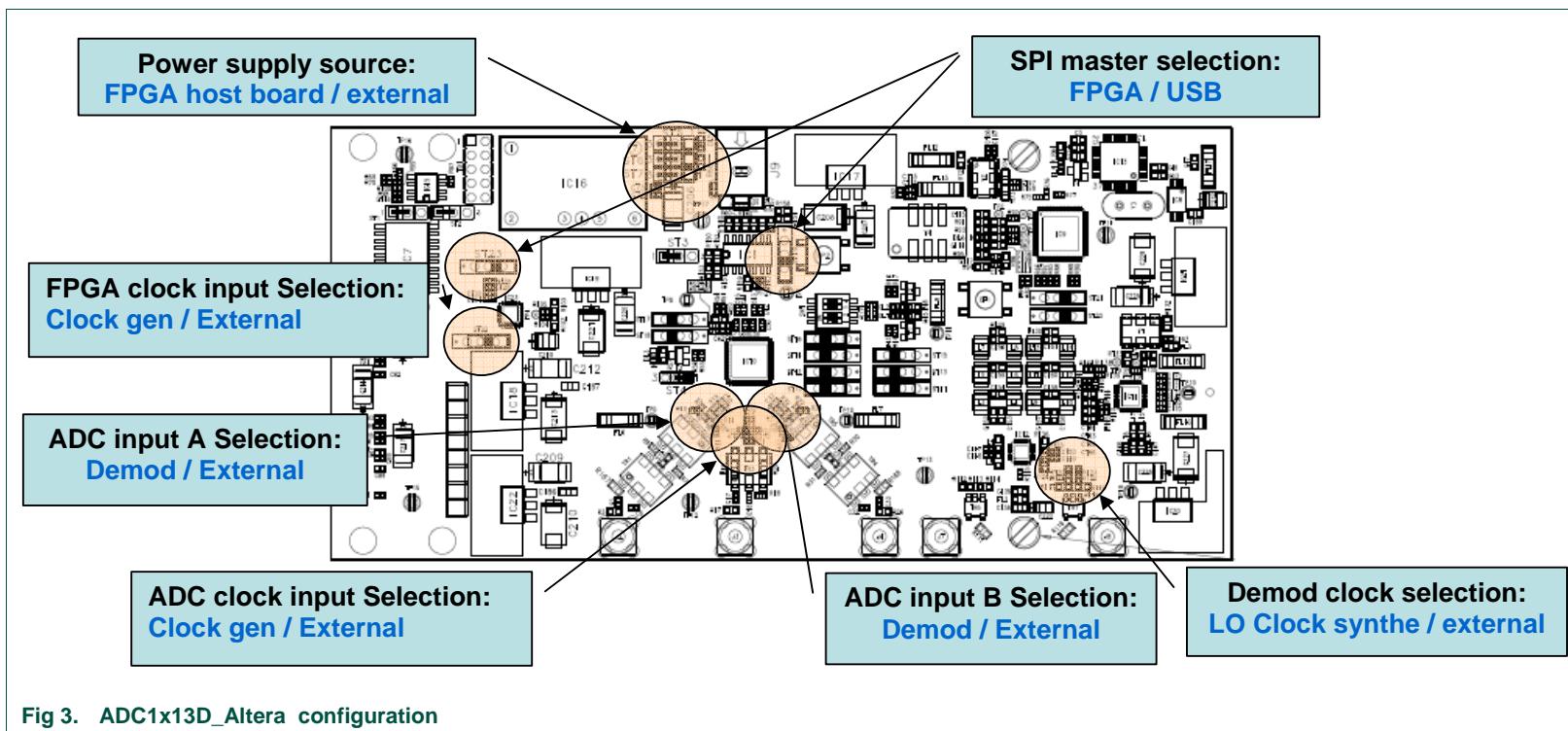

The ADC1x13D\_Altura board could be used in several configurations:

- SPI bus could be controlled by FPGA (=host board) or by USB interface (=PC application)

- The board could be power by host board or by external power supply

- FPGA clock could be provided by on board clock generator or by external clock.

- ADC clock could be provided by on board clock generator or by external clock.

- ADC inputs could be connected to on board demodulator or external source.

The selection between above configurations is done using mounting options, jumpers or switches. The following figure enables to locate the components used in these different configurations. Following chapter give detail information about all these configurations.

Fig 3. ADC1x13D\_Altura configuration

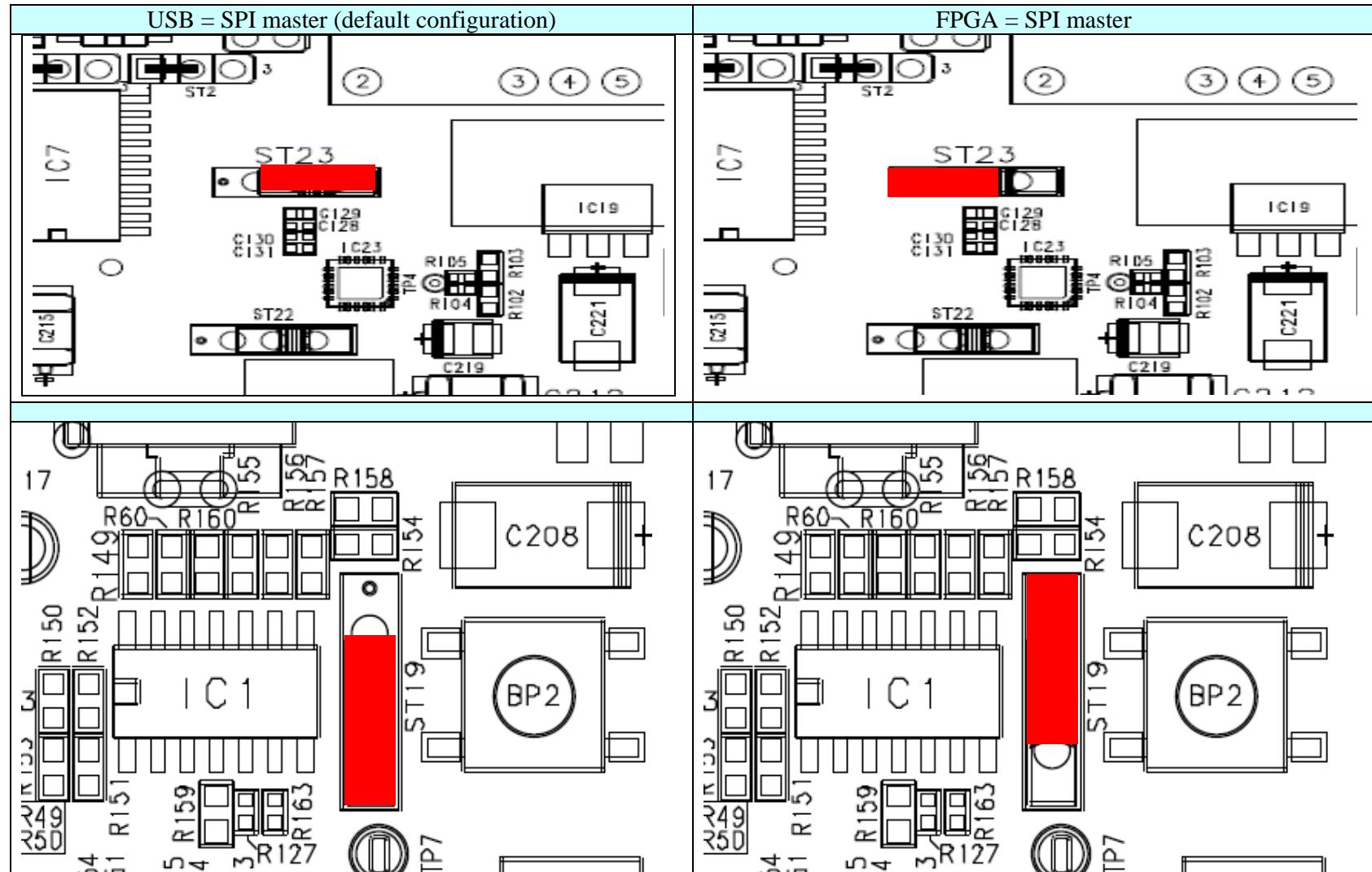

### 1.4.1 SPI bus master configuration

The ADC, the ADC clock generator and the Demodulator clock synthesizer are programmable using SPI interface. The SPI master could either be the FPGA from the host board or the PC application (USB). Selection between these 2 modes is done as indicated below:

### 1.4.2 Power supply configuration

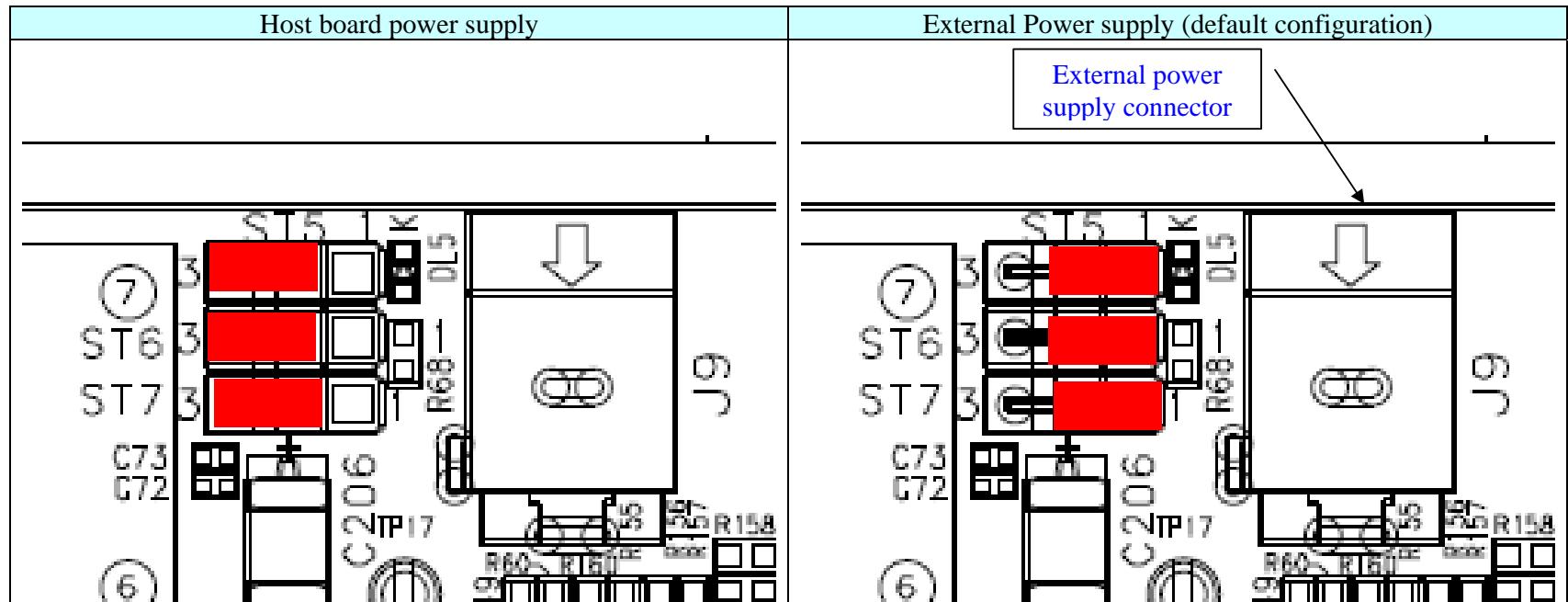

The board could be powered by either the host board or by an external power supply. Selection between these 2 modes is done as indicated below:

### 1.4.3 FPGA clock configuration

The FPGA could use the on board clock generator as reference clock or could use an external clock. Selection between these 2 modes is done as indicated below:

#### 1.4.4 ADC clock configuration

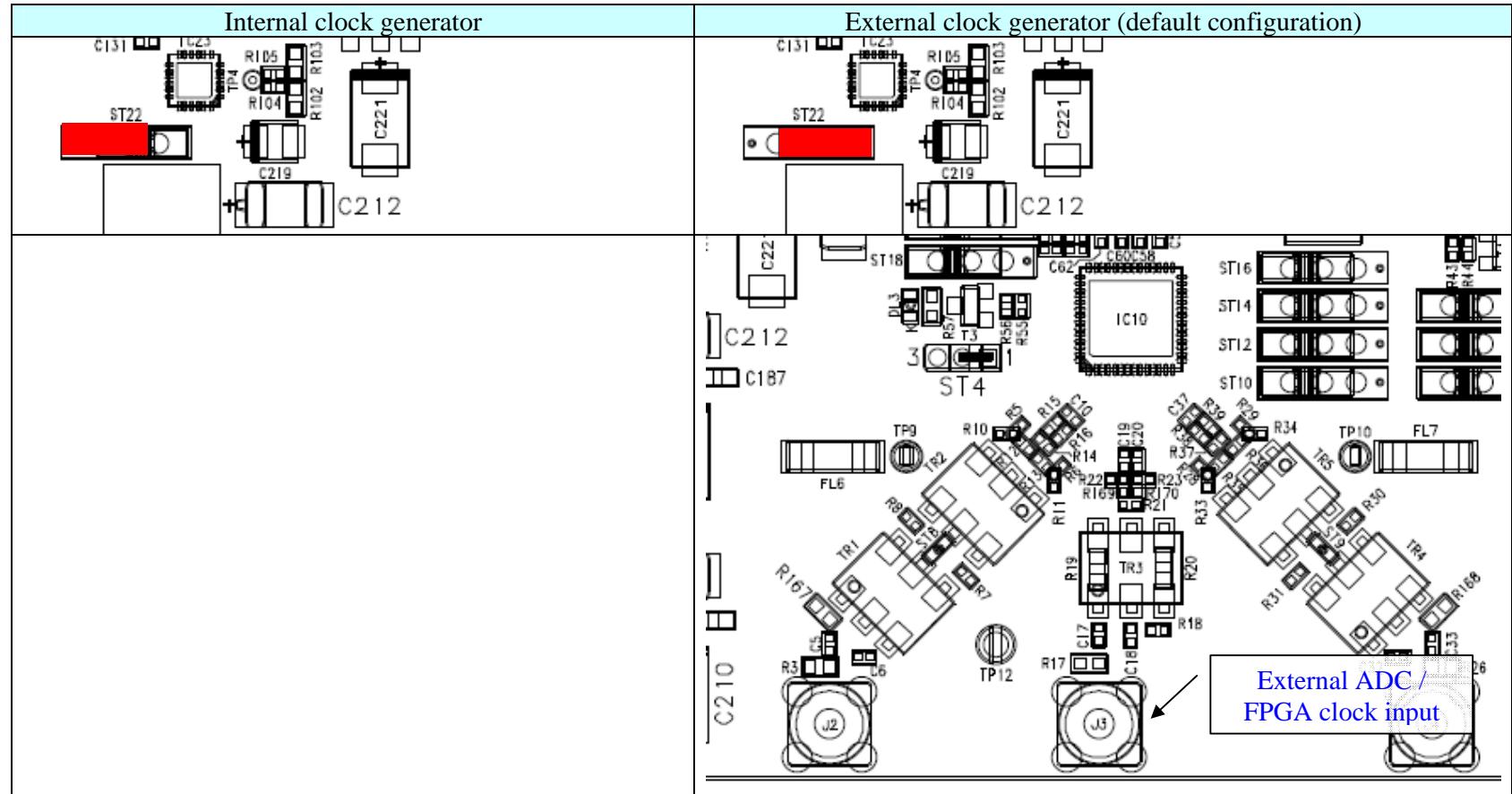

The ADC could used the on board clock generator or an external clock as sampling clock. Selection between these 2 modes is done as indicated bellow:

| Internal clock generator                                                                                                                                                                                                            | external clock generator (default configuration)                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                    |                                                                                                                                                      |

| Legend :<br>Part mounted on PCB = <br>Part not- mounted on PCB =  | Legend :<br>Part mounted on PCB = <br>Part not- mounted on PCB =  |

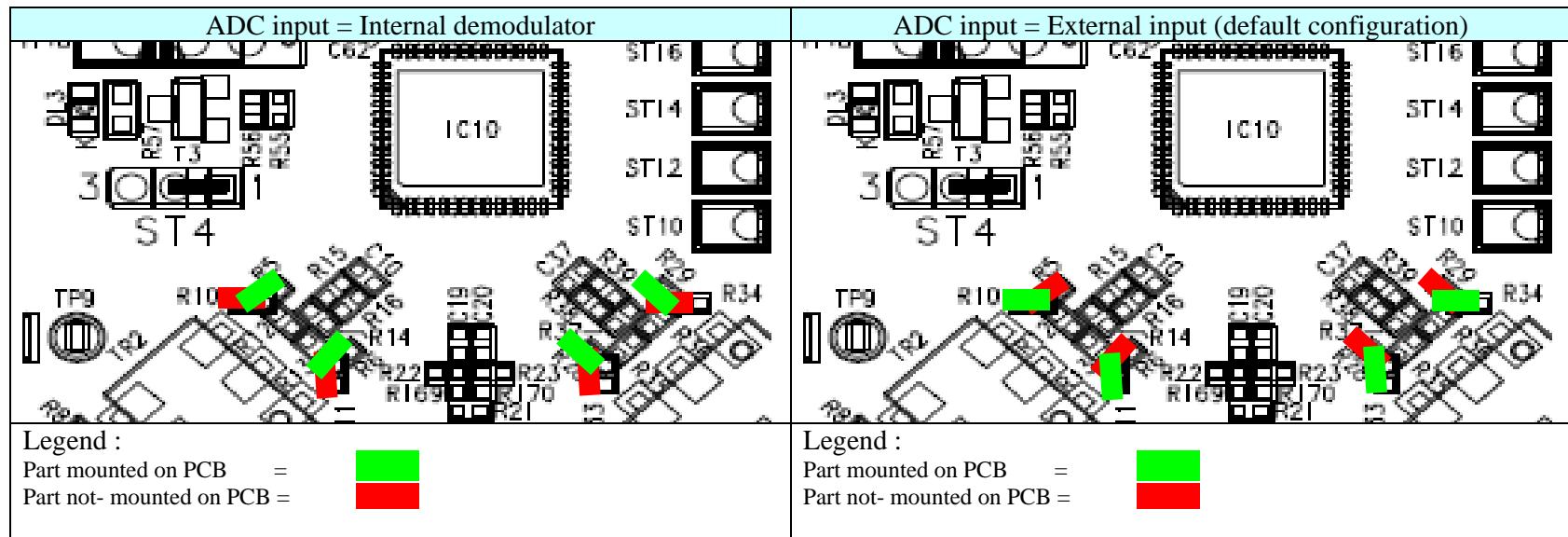

### 1.4.5 ADC input configuration

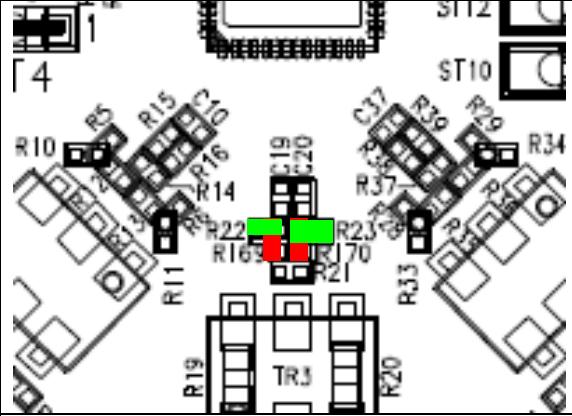

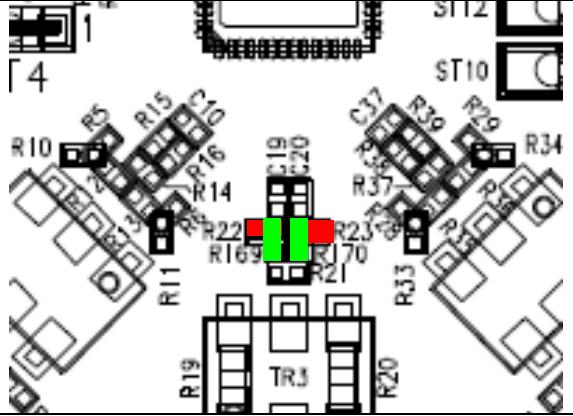

The ADC input could be connected to the on board demodulator or to an external source. Selection between these 2 modes is done as indicated below:

## 2. SPI quick start

### 2.1 Install

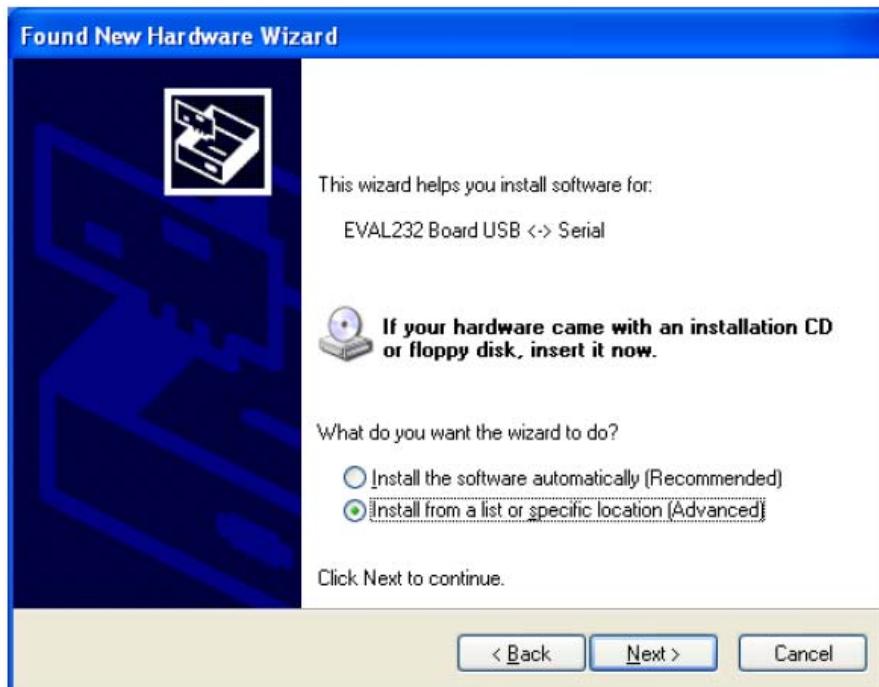

- Step 1

Connect the device to a USB port on your PC. Windows '**Found New Hardware Wizard**' will be launched. Select '**No, not this time**' from the options available and then click '**Next**' to proceed with the installation.

- Step 2

Select '**Install from a list or specific location (Advanced)**' as shown below and then click '**Next**'.

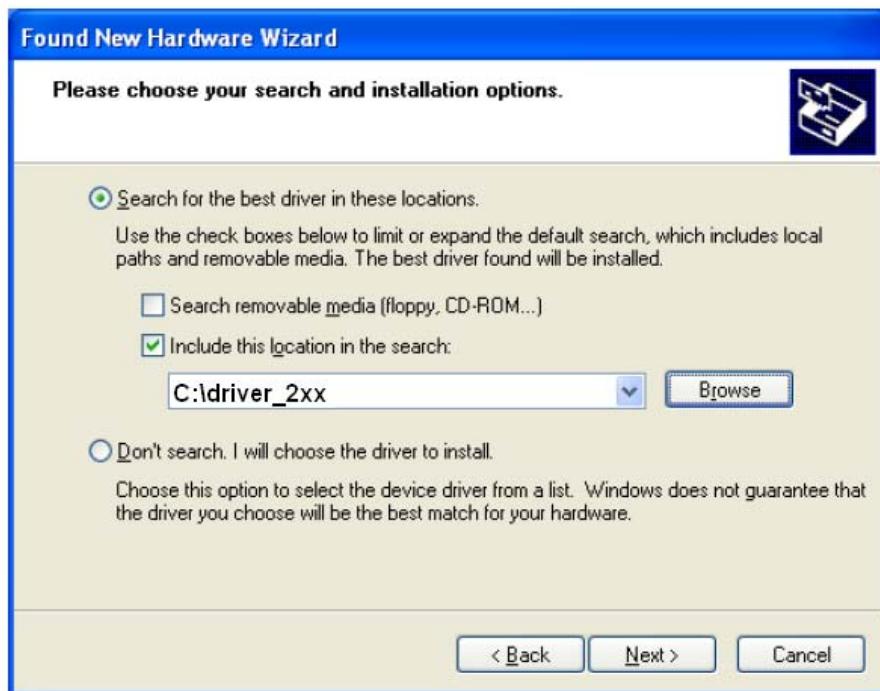

- Step 3

Select 'Search for the best driver in these locations' and enter the file path of the folder 'driver\_2xx' in the combo-box ('C:\driver\_2xx' in the example below) or browse to it by clicking the browse button. Once the file path has been entered in the box, click 'next' to proceed.

- Step 4

Windows should then display a message indicating that the installation was successful. Click 'Finish' to complete the installation for the first port of the device.

- Step 5

The Found New Hardware Wizard will continue by installing the USB Serial Converter driver for the second port of the device. The procedure for installing the second port is identical to that for installing the first port from the first screen of the Found New Hardware Wizard.

Once the second port is installed, the device should be ready to be used.

## 2.2 SPI interface

- Step 1

Install the LabVIEW Run-time Engine [LabVIEW85RuntimeEngineFull.exe](#) (if not already installed).

- Step 2

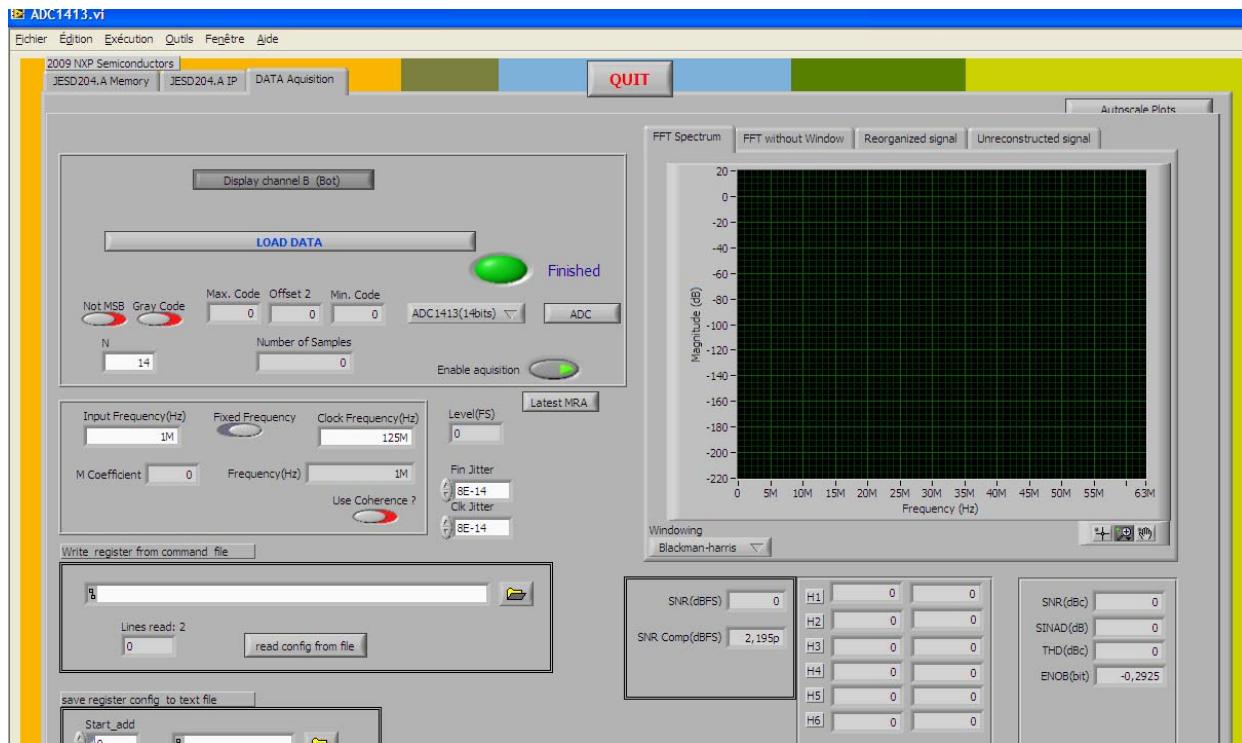

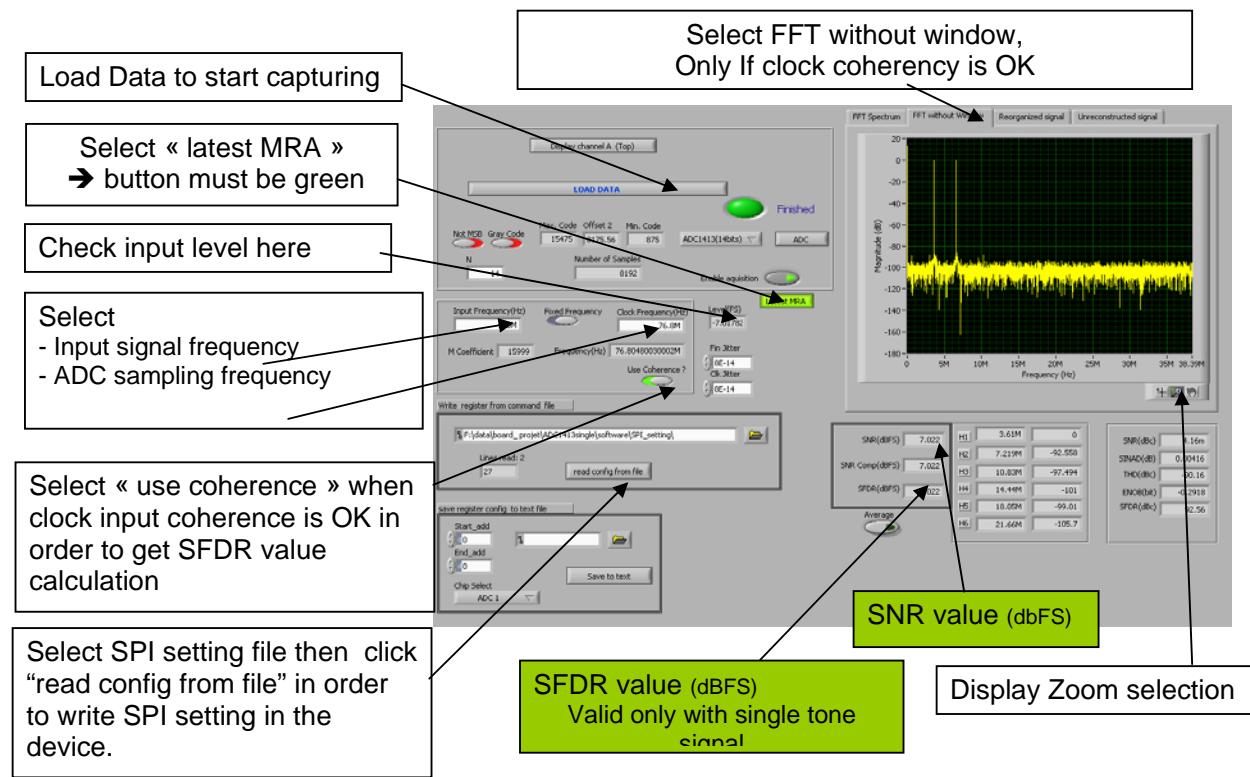

Start the LabVIEW application "ADC1x13.exe". a graphical window will pop-up

Under the "Write register from command file" field, choose the write configuration file from "ADC Command" directory depending on the used operating points.

Click on the "read from config file".

Push the Push\_A button on the board to make a manual synchronization of the JESD204A communication.

|                     |                 |                     |

|---------------------|-----------------|---------------------|

| Input Frequency(Hz) | Fixed Frequency | Clock Frequency(Hz) |

| 1M                  |                 | 125M                |

| M Coefficient       | 0               | Frequency(Hz)       |

|                     |                 | 1M                  |

| Use Coherence ?     |                 |                     |

Fill the Input Frequency and Clock Frequency fields with the wanted operating points.

|                         |                   |           |

|-------------------------|-------------------|-----------|

| Display channel B (Bot) |                   |           |

| LOAD DATA               |                   |           |

| Finished                |                   |           |

| Not MSB                 | Gray Code         |           |

| Max. Code               | Offset 2          | Min. Code |

| 0                       | 0                 | 0         |

| ADC1413(14bits)         |                   |           |

| ADC                     |                   |           |

| N                       | Number of Samples |           |

| 14                      | 0                 |           |

| Enable aquisition       |                   |           |

Click on ADC button to choose between internal ADC capture or FPGA capture

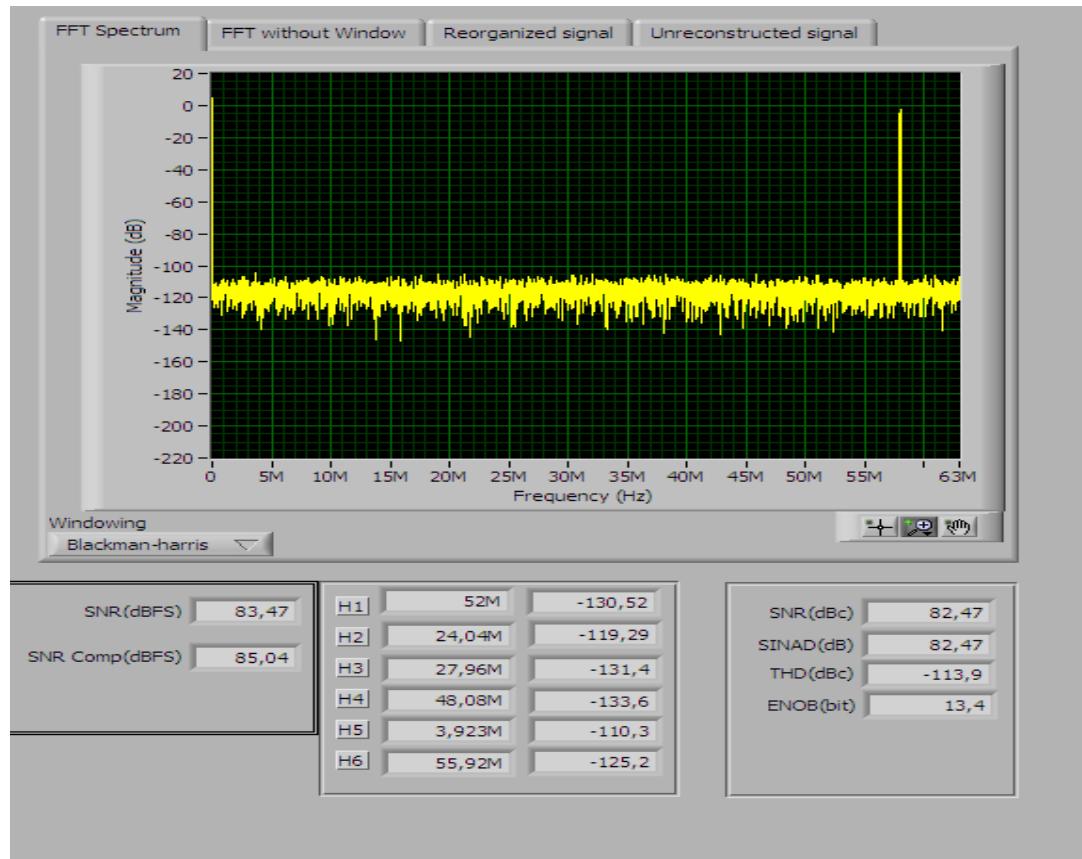

Click on Load DATA to get the FFT and the ADC performances

## Overview of the user interface :

---

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[NXP](#):

[ADC1113D125WO/DB,598](#)