## **TP3420A**

TP3420A ISDN S/T Interface Device

Literature Number: SNOSC00

## **PRELIMINARY**

July 1994

# TP3420A ISDN S/T Interface Device

## **General Description**

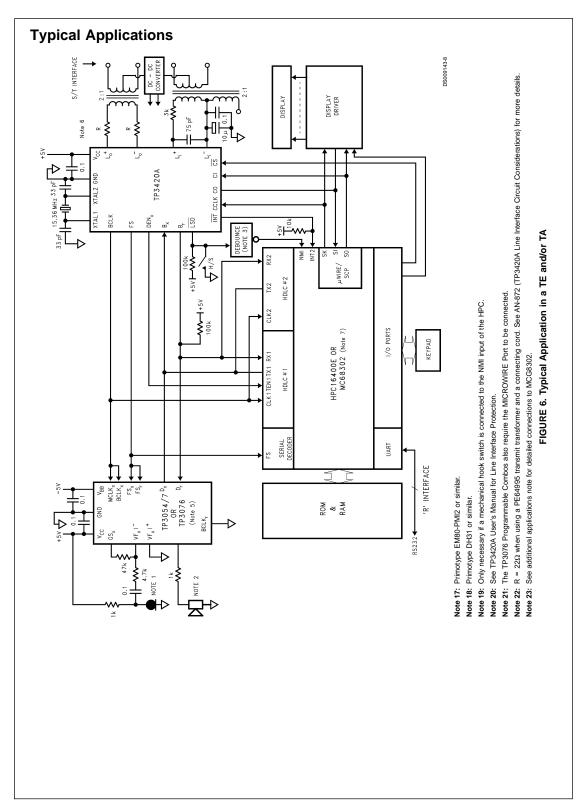

The TP3420A is an enhanced version of the TP3420, with a number of upgraded features for compliance with the new release of ANSI T1.605-1991 and CCITT I-430. At initial power-up the device is fully backwards compatible with the TP3420 device, and modifications to the firmware are only required to take advantage of the new features.

The TP3420A S Interface Device (SID™) is a complete monolithic transceiver for data transmission on twisted pair subscriber loops. It is built on National's advanced 1.0 micron double-metal CMOS process, and requires only a single +5V supply. All functions specified in CCITT recommendation I.430 (1991) and ANSI T1.605 (1991) for ISDN basic access at the "S" and "T" interfaces are provided, and the device can be configured to operate either in a TE (Terminal Equipment), in an NT-1 or NT-2 (Network Termination) or as a PABX line-card or trunk-card device.

As specified in I.430, full-duplex transmission at 192 kb/s is provided on separate transmit and receive twisted wire pairs using inverted Alternate Mark Inversion (AMI) line coding. 2 "B" channels, each of 64 kb/s, and 1 "D" channel at 16 kb/s are available for users' data. In addition, the TP3420A provides the 800 b/s "S1", "S2" & "Q" multiframe channels for Layer 1 maintenance.

All I.430 wiring configurations are supported by the TP3420A SID, including the "passive bus" for up to 8 TE's distributed within 200 meters of low capacitance cable, and point-to-point and point-to-star connections up to at least 1500 meters (24AWG). Adaptive receive signal processing ensures low bit error rates on any of the standard types of cable pairs commonly found in premise wiring installations when tested with the noise sources specified in I.430.

### **Features**

- 2 B + D 4-wire 192 kb/s transceiver

- Selectable TF or NT mode

- Exceeds I.430 range: 1.5 km point-to-point

- Adaptive receiver for high noise immunity

- Adaptive and fixed timing options for NT-1

- Clock resynchronizer and elastic buffers for NT-2/LT

- Slave-slave mode for NT-2 trunks

- Extensive hardware support for SC1, SC2 and Q channel messaging

- Bipolar violation detection and FECV messaging

- Selectable system interface formats

- MICROWIRE™ and SCP compatible serial control interface

- TP3054/7 Codec/Filter COMBO<sup>™</sup> compatibility

- Single +5V supply

- 20-pin package DIP, PLCC

## **Applications**

- Same Device for NT, TE and PBX Line Card

- Point-to-Point Range Extended to 1.5 km

- Point-to-Multipoint for all I.430 Configurations

- Easy Interface to:

LÁPD Processor MC68302, HPC16400

Terminal Adapter MC68302, HPC16400

Codec/Filter COMBO TP3054/7 and TP3076

"U" Interface Device TP3410

Line Card Backplanes - No External PLL Needed

■ Line Monitor Mode for Test Equipment

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

COMBO™, MICROWIRE™ and SID™ are trademarks of National Semiconductor Corporation

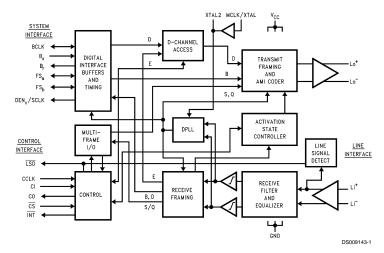

## **Block Diagram**

## **Connection Diagrams**

## TP3420A SID

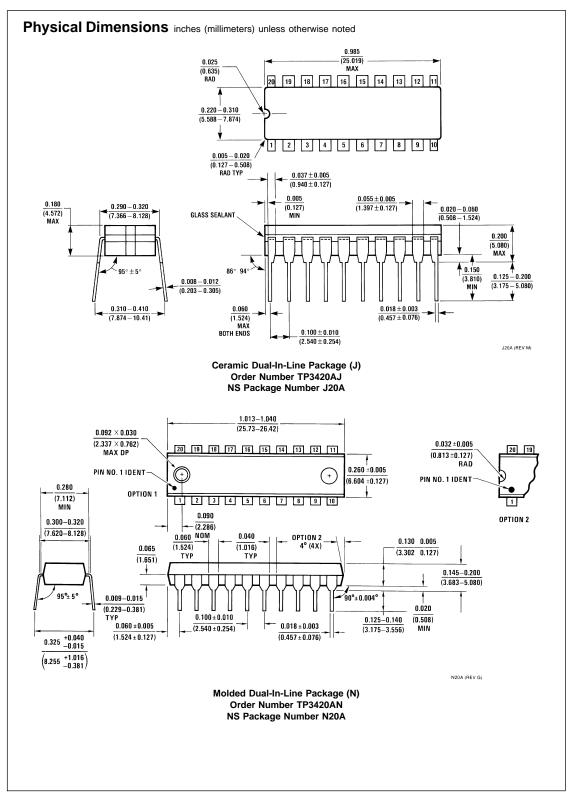

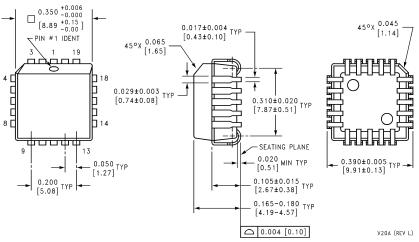

Order Number TP3420AV See NS Package Number V20A

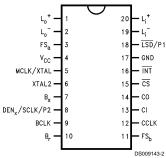

TP3420A SID

Top View Order Number TP3420AJ or TP3420AN See NS Package Number J20A or N20A

## **Pin Descriptions**

|                 | •                                                                                                                                                                                                                                                                                 |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name            | Description                                                                                                                                                                                                                                                                       |

| GND             | Negative power supply pin, normally 0V (ground). All analog and digital signals are referenced to this pin.                                                                                                                                                                       |

| V <sub>CC</sub> | Positive power supply input, which must be +5V ±5% relative to GND.                                                                                                                                                                                                               |

| MCLK/XTAL       | The 15.36 MHz Master Clock input, which requires either a crystal (Note 1) to be tied between this pin and XTAL2, or a CMOS logic level clock input from a stable source. When using a crystal, a total of 33 pF load capacitance to GND must also be connected. (Note 2)         |

| XTAL2           | The output of the crystal oscillator, which should be connected to one end of the crystal, and 33 pF of load capacitance to GND. (Note 2) If using an external master Clock via the MCLK pin, leave the XTAL2 pin unconnected.                                                    |

| BCLK            | The Bit Clock pin, which determines the data shift rate for "B" and "D" channel data at the digital interface. When NT mode or TES mode is selected, BCLK is a TTL/CMOS input which may be any multiple of 8 kHz from 256 kHz to 4.096 MHz. It need not be synchronous with MCLK. |

|                 | When TEM mode is selected, this pin is a CMOS output at frequency selected by the Digital Interface Format. This clock is phase-locked to the received line signal and is synchronous with the data on $B_{\rm x}$ and $B_{\rm r}$ .                                              |

| III Des              | criptions (Continued)                                                                            | Name                               | Description                                                                                                  |

|----------------------|--------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Name                 | Description                                                                                      | СО                                 | Control channel serial data CMOS outputer for status information. When not enabled                           |

| S <sub>a</sub>       | In NT modes and TES mode, this pin is                                                            |                                    | by CS, this output is TRI-STATE.                                                                             |

|                      | the Transmit Frame Sync pulse                                                                    | CCLK                               | TTL/CMOS clock input for the Control                                                                         |

|                      | TTL/CMOS input, requiring a positive                                                             | 002.1                              | Channel.                                                                                                     |

|                      | edge to indicate the start of the active                                                         | <del>CS</del>                      | Chip Select input which enables the                                                                          |

|                      | channel time for transmit "B" and "D"                                                            | 00                                 | control channel data to be shifted in and                                                                    |

|                      | channel data into B <sub>x</sub> . In TEM mode only,                                             |                                    | out when pulled low. When high, this pin                                                                     |

|                      | this pin is a digital output pulse whose                                                         |                                    | inhibits the Control interface.                                                                              |

|                      | positive indicates the start of the "B"                                                          | ĪNT                                | Interrupt output, a latched n-channel                                                                        |

|                      | channel data transfer at both B <sub>x</sub> and B <sub>r</sub> .                                |                                    | open-drain output signal which is                                                                            |

| S <sub>b</sub>       | In NT modes and TES mode, this pin is                                                            |                                    | normally high impedance, and goes low                                                                        |

| Pin 11)              | the Receive Frame Sync pulse                                                                     |                                    | to indicate a change of status of the loop                                                                   |

|                      | TTL/CMOS input, requiring a positive                                                             |                                    | transmission system.                                                                                         |

|                      | edge to indicate the start of the active                                                         | LSD/P1                             | In all modes, this pin by default is the                                                                     |

|                      | channel time of the device for receive "B" and "D" channel data out from B <sub>r</sub> . In TEM | (Pin 18)                           | Line Signal Detect output, an n-channel                                                                      |

|                      | mode only, when digital interface Format                                                         | ( -/                               | open-drain output which is normally                                                                          |

|                      | 1 is selected, this pin is an 8-bit wide                                                         |                                    | high-impedance, but pulls low when the                                                                       |

|                      | pulse which indicates the active slot for                                                        |                                    | device is powered down and a received                                                                        |

|                      | the B2 channel on the digital interface.                                                         |                                    | line signal is detected. It is intended to b                                                                 |

|                      | The DCKE command will alter the                                                                  |                                    | used to "wake-up" a microprocessor from                                                                      |

|                      | function of this pin. See <i>Table 2</i> for                                                     |                                    | a low-power idle mode. This output is                                                                        |

|                      | details.                                                                                         |                                    | high impedance when the device is                                                                            |

| $B_{x}$              | TTL/CMOS input for "B" and "D" channel                                                           |                                    | powered up.                                                                                                  |

| ×                    | data to be transmitted to the line; must be                                                      |                                    | This pin P1 in Table 1 can also be                                                                           |

|                      | synchronous with BCLK.                                                                           |                                    | programmed to provide alternate                                                                              |

| $B_r$                | CMOS output for "B" and "D" channel                                                              |                                    | functions. See <i>Table 1</i> for details.                                                                   |

| r                    | data received from the line, which is                                                            | L <sub>o</sub> +, L <sub>o</sub> - | Transmit AMI signal differential outputs t                                                                   |

|                      | synchronous with BCLK. When not                                                                  |                                    | the line transformer. When used with a                                                                       |

|                      | shifting data, this pin is TRI-STATE®.                                                           |                                    | 2:1 step-down transformer, the line signa                                                                    |

| DEN <sub>x</sub> /p2 | In TEM mode, this pin by default is a                                                            |                                    | conforms to the output pulse masks in                                                                        |

| Pin 8)               | CMOS output which is normally low and                                                            |                                    | 1.430.                                                                                                       |

| •                    | pulses high to indicate the active bit-times                                                     | L <sub>i</sub> +, L <sub>i</sub> – | Receive AMI signal differential inputs                                                                       |

|                      | for "D" channel Transmit data at the B <sub>x</sub>                                              |                                    | from the line transformer. The L <sub>i</sub> - pin is also the internal voltage reference pin,              |

|                      | input. It is intended to be gated with                                                           |                                    | and must be decoupled to GND with a 1                                                                        |

|                      | BCLK to control the shifting of data from                                                        |                                    | μf capacitor in parallel with a 0.1 μF                                                                       |

|                      | layer 2 device to the TP3420A transmit                                                           |                                    | ceramic capacitor.                                                                                           |

|                      | buffer.                                                                                          | Note 1: Crystal                    | specification: 15.36 MHz parallel resonant; $R_s \le 150\Omega$ ,                                            |

|                      | In NT modes, this pin by default is a                                                            | C <sub>L</sub> = 20 pF and         |                                                                                                              |

|                      | pulse output (DEN <sub>x</sub> ) which occurs in                                                 |                                    | pF includes any board capacitance.                                                                           |

|                      | every 8 KHz frame and indicates the                                                              |                                    |                                                                                                              |

|                      | location of D channel data input on the B <sub>x</sub>                                           |                                    | E PIN FUNCTIONS                                                                                              |

|                      | pin.                                                                                             |                                    | OWIRE command PINDEF (B'1110 0 x2 x1 x                                                                       |

|                      | In TES mode, this pin by default is an                                                           |                                    | If functions of these pins can be changed to p                                                               |

|                      | output synchronized clock (SCLK) at the                                                          |                                    | e functions (see <i>Table 1</i> and the MICROWII<br><i>Table 4</i> ). "*" indicates the default pin function |

|                      | frequency selected by the Digital Interface Format. This clock is                                |                                    | mode selection. Power-up default device mo                                                                   |

|                      | phase-locked to the received line signal,                                                        | is NTA.                            | aa colociidii i oli oli ap aciaalii aciico iiic                                                              |

|                      | and is intended to be used as the BCLK                                                           |                                    |                                                                                                              |

|                      | source.                                                                                          |                                    |                                                                                                              |

|                      | This pin called P2 in <i>Table 1</i> can also be                                                 |                                    |                                                                                                              |

|                      | programmed to provide alternate                                                                  |                                    |                                                                                                              |

|                      | functions. See <i>Table 1</i> for details.                                                       |                                    |                                                                                                              |

| CI                   | MICROWIRE control channel serial data                                                            |                                    |                                                                                                              |

| <b>,</b> ,           |                                                                                                  |                                    |                                                                                                              |

|                      | TTL/CMOS input.                                                                                  |                                    |                                                                                                              |

## Pin Descriptions (Continued)

**TABLE 1. Alternate Pin Function Assignment**

| Device | P2 - P   | in 8           | P1 - P   | in 18                           |

|--------|----------|----------------|----------|---------------------------------|

| Mode   | Function | X <sub>2</sub> | Function | x <sub>1</sub> , x <sub>0</sub> |

| TEM    | DENx     | 0              | LSD      | 00                              |

|        | (Note 3) | (Note 3)       |          | (Note 3)                        |

|        | SCLK     | 1              | DENr     | 01                              |

|        |          |                | SCLK     | 10                              |

|        |          |                | DENx     | 11                              |

| TES    | DENx     | 0              | LSD      | 00                              |

|        |          |                |          | (Note 3)                        |

|        | SCLK     | 1              | DENr     | 01                              |

|        | (Note 3) | (Note 3)       |          |                                 |

|        |          |                | SCLK     | 10                              |

|        |          |                | DENx     | 11                              |

| NTA    | DENx     | 0              | LSD      | 00                              |

|        | (Note 3) | (Note 3)       |          | (Note 3)                        |

| NTF    | SCLK     | 1              | DENr     | 01                              |

|        |          |                | SCLK     | 10                              |

|        |          |                | DENx     | 11                              |

| MMA    | DENx     | 0              | LSD      | 00                              |

|        | (Note 3) | (Note 3)       |          | (Note 3)                        |

|        | SCLK     | 1              | DENr     | 01                              |

|        |          |                | SCLK     | 10                              |

|        |          |                | DENx     | 11                              |

PINDEF command is coded as X'EX (i.e. 11100x<sub>2</sub>x<sub>1</sub>x<sub>0</sub>). **Note 3:** Default pin function after device mode selection.

#### SIGNAL DESCRIPTION

SCLK is an output synchronized clock at the frequency selected by the Digital Interface Format. This clock is phase-locked to the received line signal, and is intended to be used as the BCLK source.

LSD is the Line Signal Output, an n-channel open-drain output that is normally high-impedance, but pulls low when the device is powered down and a received line signal is detected. It is intended to be used to "wake-up" a microprocessor from a low-power idle mode. This output is a high impedance when the device is powered up.

DENr is a CMOS output that is normally low and pulses high to indicate the active bit times for "D" channel Receive data at the  $B_r$  output pin. It is intended to be gated with BCLK to control the shifting of data from the TP3420A receive buffer to a layer 2 device.

DENx is a CMOS output that is normally low and pulses high to indicate the active bit times for D channel Transmit data at the  $\rm B_x$  input. It is intended to be gated with BCLK to control the shifting of data from a layer 2 device to the TP3420A's transmit buffer. In NT mode, this pulse occurs every 8 kHz frame and indicates the location of D channel data input on the  $\rm B_v$  pin.

### ADDITIONAL PIN CONFIGURATION

The TP3420A in TEM mode can be configured to interface with the Motorola layer-2 devices such as the MC68302 and the MC145488. A PINDEF (X'E1) command followed by a DCKE (X'F1) command will alter the TP3420A pin functions as shown in *Table 2*. Other configurations of PINDEF are not supported.

TABLE 2.

| Pin Number | Pin Function |

|------------|--------------|

| 8          | DTCK         |

| 11         | TxD          |

| 18         | DRCK         |

#### Where:

- DCLK is a burst clock output intended to be used as a clock source for the transmitter of an HDLC device.

- TxD is an input being sampled on the rising edge of DCLK during the active D-channel timeslot.

- DRCK is a burst clock output which pulses 2 BCLK periods every 8 kHz frame. This output is intended to be used as a clock source for the receiver of an HDLC device. The D-channel data at B<sub>r</sub> is transmitted on the falling edge of the DRCK.

## **Functional Description**

#### **DEVICE MODES**

The TP3420A can be programmed into one of four possible modes. For NT applications select NT Adaptive timing (NTA) for all wiring configurations except a Short Passive Bus, for which NT Fixed Timing (NTF) should be selected. In TE applications, select TE Master mode (TEM) for the device to be the master (source) of clocks at the digital interface, or select TE Slave mode (TES) for the digital interface to accept clocks from the system.

Selection of these modes is described in the section on Control Register instructions.

### POWER-ON DEVICE CONDITIONS

Following the initial application of power, the TP3420A SID enters the power-down (de-activated) state, in which all the internal circuits including the Master oscillator are inactive and in a low power state except for the Line-Signal Detect circuit; the line outputs  $L_o + l_{-o} -$  are in a high impedance state and the Digital System Interface is inactive. All bits in the Control Register power-up as indicated in *Table 1*. In both NT and TE modes, a Line-Signal Detect circuit monitors the line while the device is powered-down, to enable loop transmission to be initiated from either end.

#### POWER-OFF DEVICE CONDITION

When power to the TP3420A is turned off, the Line outputs  $L_o + /L_o -$  go into high impedance state, hence if a TE on a passive bus lost power its transmit impedance still meets the specification without any external relay (see AN665 for external protection components). The receiver impedance also remains in specification.

#### LINE CODING AND FRAME FORMAT

For both directions of transmission, Alternate-Mark Inversion (AMI) coding with inverted binary is used, as illustrated in *Figure 1*. This coding rule requires that a binary ONE is represented by 0V high impedance output, whereas a binary ZERO is represented by a positive or negative-going 100% duty-cycle pulse. Normally, binary ZEROs alternate in polarity to maintain a d.c.-balanced line signal.

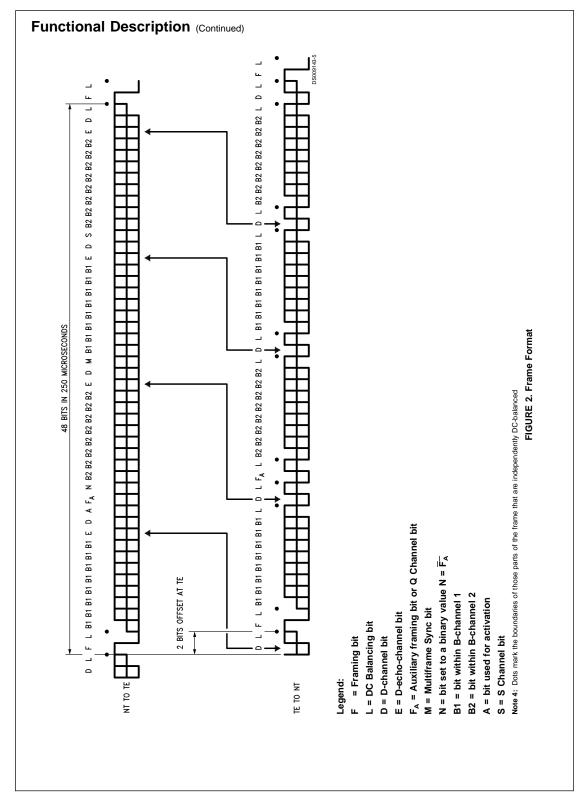

The frame format used in the TP3420A SID follows the CCITT recommendation specified in I.430 and illustrated in Figure 2. Each complete frame consists of 48 bits, with a line bit rate of 192 kb/s, giving a frame repetition rate of 4 kHz. A violation of the AMI coding rule is used to indicate a frame

boundary, by using a  $0^+$  bit followed by a  $0^-$  balance bit to indicate the start of a frame, and forcing the first binary zero following the balance bit to be of the same polarity as the balance bit.

In the Network Termination (NT) to the Terminal Equipment (TE) transmission direction the frame contains an echo channel, the E bit, which is used to retransmit the D bits that are received from the TE. The last bit of this frame is used as a frame balancing bit. In the TE to NT direction, d.c.-balancing is carried out for each channel, as illustrated in *Figure 2*.

#### LINE TRANSMIT SECTION

The differential line-driver outputs,  $L_o+$  and  $L_o-$ , are designed to drive a transformer with an external termination resistor. A suitable 2:1 transformer, terminated in  $50\Omega$ , results in a signal amplitude of nominally 750 mV pk on the line which fully complies with the 1.430 pulse mask specifications. When driving a binary 1 symbol the output presents a high impedance in accordance with 1.430. When driving a 0+ or 0- symbol a voltage-limited current source is turned on. Short-circuit protection is included in the output stage; over-voltage protection is required externally, see the Applications section.

#### LINE RECEIVE SECTION

The receive input signal should be derived via a 1:1 transformer, or a 1:2 transformer of the same type used for the transmit direction. At the front-end of the receive section is a continuous filter which limits the noise bandwidth. To correct pulse attenuation and distortion caused by the transmission line in point-to-point and extended passive bus applications, an adaptive equalizer enhances the received pulse shape,

thereby restoring a "flat" channel response with maximum eye opening over a wide spread of cable attenuation characteristics. This equalizer is always enabled when either TE mode or NT Mode Adaptive Sampling is selected, but is disabled for short passive bus applications when NT Mode Fixed Sampling is selected. An adaptive threshold circuit maximizes the Signal-to-Noise ratio in the eye at the detector for all loop conditions.

In NTF mode the receive baud sampling point is fixed relative to the transmit baud clock. This ensures accurate sampling of received pulses with differential delays on a passive bus, thus extending the short passive bus range to over 250m of low capacitive cable.

In NTA and TE modes, the receive baud sampling is adaptive. In these modes, a DPLL (Digital Phase-Locked Loop) recovers a low-jitter clock for optimum sampling of the received symbols. The MCLK input provides the reference clock for the DPLL at 15.36 MHz. Clocks for the digital interface timing may either be derived from this recovered clock, as in TE mode Digital System Interface Master, or may be slaved to an external source, as in the T-interface side of an NT-2 (TES mode). In TES and NT modes, re-timing circuitry on the TP3420A allows the MCLK frequency to be plesiochronous (i.e., free-running) with respect to the network clock, i.e. the 8 kHz FSa input. With a tolerance on the MCLK oscillator of 15.36 MHz  $\pm 100$  ppm, the lock-in range of the DPLL allows the network clock frequency to deviate up to  $\pm 50$  ppm from nominal.

When the device is powered-down (either on initial powering-on of the device or after using a PDN command), a Line-Signal Detect circuit is enabled to detect the presence of incoming data if the far-end starts to activate the loop. The LSD circuit is disabled by a Power-Up (PUP) command.

FIGURE 1. Inverted AMI Line-Coding Rule

#### **DIGITAL SYSTEM INTERFACE**

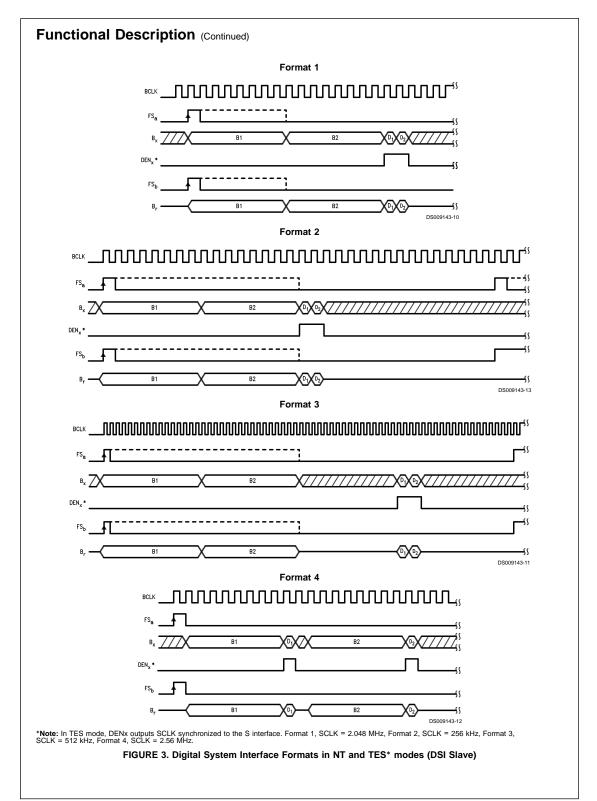

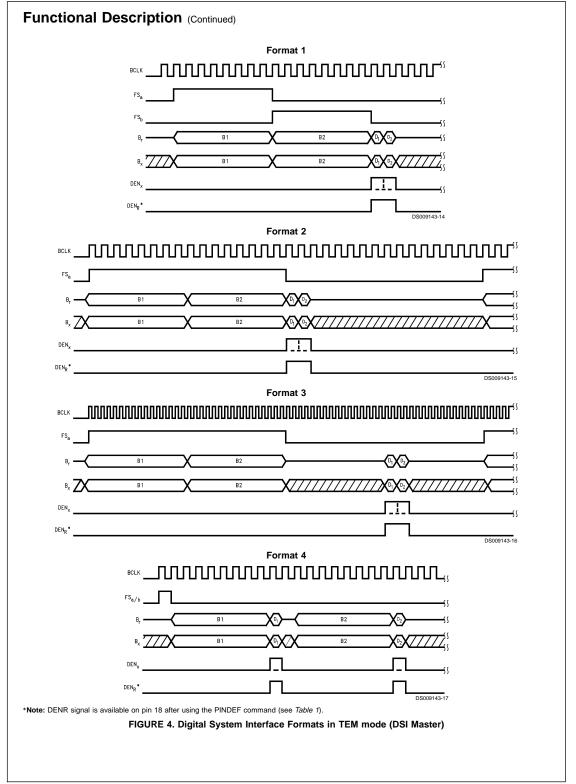

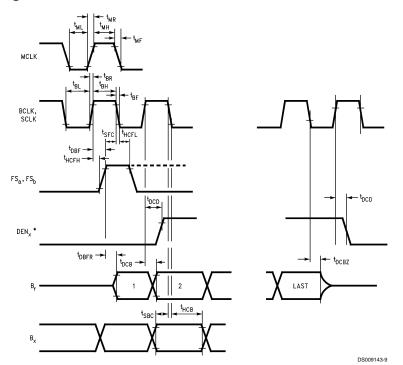

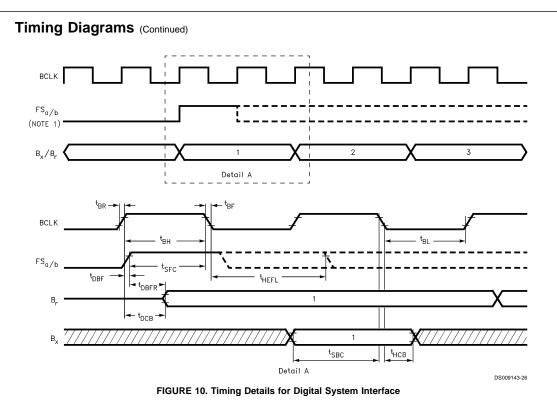

The Digital System Interface (DSI) on the TP3420A combines "B" and "D" channel data onto common pins to provide maximum flexibility with minimum pin count. Several multiplexed formats of the B and D channel data are available as shown in *Figure 3*. Selection is made via the Control Register.

NTA, NTF and TES modes: at this interface, phase skew between transmit and receive frames may be accommodated when the device is a slave at the Digital Interface (NT and TES Modes) since separate frame sync inputs (Figure 3),  $FS_a$  and  $FS_b$ , are provided. Each of these synchronizes a counter which gates the transfer of B1 and B2 channels in consecutive time-slots across the digital interface. The serial shift rate is determined by the BCLK input, and may be any multiple of 8 kHz from 256 kHz to 4.096 MHz. Thus, for applications on a PABX line-card (in NT mode), the "B" and "D" channel slots can be interfaced to a TDM bus and assigned to a time-slot.

TEM mode: in TE Master Mode (TEM), FS<sub>a</sub> is an output (*Figure 4*) indicating the start of both transmit and receive "B" channel data transfers. BCLK is also an output at the serial data shift rate, which is dependent on the format selected, see *Table 5*

TES mode: for applications such as the network side of an NT-2, e.g. a PBX trunk card, the TE Slave (TES) Mode is provided. This "slave-slave" mode allows the transmission side of the device to be a slave to the received frame timing, while the Digital System Interface is also in a slave mode i.e.  ${\sf FS}_a$ ,  ${\sf FS}_b$  and BCLK are inputs. The Digital System Interface includes elastic buffers which allow any arbitrary phase relationship between each FS input and the received I.430 frame.

#### JITTER ABSORPTION AND PHASE WANDER BUFFERS

The TP3420A has an improved serial data buffer circuit to handle larger amounts of phase wander exceeding the specification of 18 µs pk-to-pk, regardless of the phase difference between the transmit and receive frames. A SLIP indicator interrupt is generated to inform the CPU if the phase deviation between two clocks exceeds the boundary of the circuit, causing the data buffers to adjust the internal delay to accommodate this. Under some, but not all, circumstances this will result in data errors as the slip occurs. Separate interrupt status values (SLIP—TX and SLIP—RX) indicate the clock slippage in the transmit buffer or the receiver buffer. TES Mode also provides a synchronized clock output (SCLK) which is phase-locked to the received line signal; SCLK may be used as the BCLK source.

**TABLE 3. DSI Format Rates**

| Format | BLCK as<br>DSI Master | BCLK as<br>DSI Slave |  |  |  |  |

|--------|-----------------------|----------------------|--|--|--|--|

|        | (Output) (Note 5)     | (Input)              |  |  |  |  |

| 1      | 2.048 MHz             | 256 kHz-4.096 MHz    |  |  |  |  |

| 2      | 256 kHz               | 256 kHz-4.096 MHz    |  |  |  |  |

| Format | BLCK as DSI Master (Output) (Note 5) | BCLK as<br>DSI Slave<br>(Input) |

|--------|--------------------------------------|---------------------------------|

| 3      | 512 kHz                              | 512 kHz-4.096 MHz               |

| 4      | 2.56 MHz                             | 256 kHz-4.096 MHz               |

Note 5: also SCLK output in TES Mode.

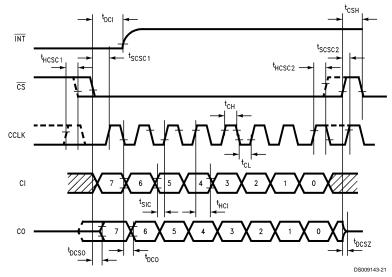

#### MICROWIRE CONTROL INTERFACE

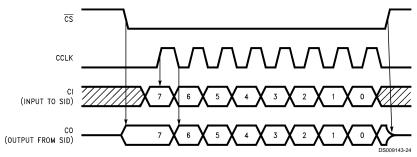

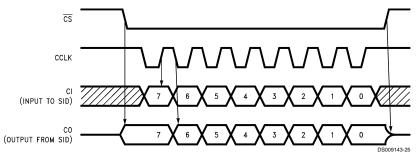

A serial interface, which can be clocked independently from the "B" and "D" channel system interface, is provided for microprocessor control of various functions in the TP3420. This port can be used when the device is powered up or powered down. All data transfers consist of a single byte shifted into the Control Register via the CI pin, simultaneous with a single byte shifted out from the Status Register via the CO pin.

Data shifts in to CI on rising edges of CCLK and out from CO on falling edges when  $\overline{CS}$  is pulled low for 8 cycles of CCLK. An Interrupt output,  $\overline{INT}$  goes low to alert the microprocessor whenever a change occurs in one or more of the conditions indicated in the Status Register. This latched output is cleared to a high impedance state by the first rising CCLK edge after  $\overline{CS}$  goes low. Interrupt Source(s) occurring while another is still pending are stored in a stack and read in sequence, by causing another interrupt at the end of the current  $\overline{CS}$  cycle ( $\overline{INT}$  can go low only when  $\overline{CS}$  is high). When reading the Status Register the CI input is also enabled, therefore a "dummy" command e.g. NOP(X'FF) must be loaded into CI as CO is read.

Each source of an Interrupt event (e.g., EI, AI, SLIP) in the device has an internal latch, such that the occurrence of that event is stored until read from the status register. Multiple events will be reported in turn by the device in a circular manner. There is no priority criteria. If multiple occurrences of the same event occur (e.g., EI, followed by AI and then EI) and if left unserviced, than the second occurrence (of EI in this example) will over-write the first. Also if a multiframe interrupt such as MFR1 interrupt is not serviced before a second occurrence of the MFR1 interrupt, then the second value in the M1-M4 bits will overwrite the first. The DI interrupt clears all pending interrupts and indicating the reset state of the device. The LSD interrupt is generated independently and is only valid while the device is in low power mode (PDN). A PUP command resets the line signal detect circuit and the LSD interrupt. A PDN command resets and re-enables the LSD circuit and interrupt

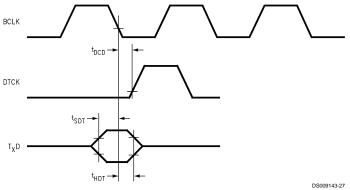

Figure 5 shows the timing for this interface, and Table 4 and Table 5 list the control functions and status indicators.

#### **FLEXIBLE MICROWIRE PORT**

The MICROWIRE port of the TP3420A has been enhanced such that it can connect to standard MICROWIRE master devices (such as National's microcontrollers of the HPC and COP families) as well as the SCP interface master from the Motorola microcontroller family. SCP is the Serial Control Port on devices such as the MC68302 or the MC145488 HDLC. See the MICROWIRE port timing diagram and the applications section.

FIGURE 5. TP3240A Enhanced MICROWIRE Control Interface Timing

TABLE 4. Control Register Functions

| Function                                              | Mnemonic | nic Bit Number |   |   |   |   |   |   |   |

|-------------------------------------------------------|----------|----------------|---|---|---|---|---|---|---|

|                                                       |          | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Activation/Deactivation                               | -        |                |   |   |   |   |   |   |   |

| No Operation                                          | NOP      | 1              | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Power-Down (Note 6)                                   | PDN      | 0              | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Power-Up                                              | PUP      | 0              | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| Deactivation Request                                  | DR       | 0              | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| Force INFO2 (NT only)                                 | FI2      | 0              | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| Monitor Mode Activation                               | MMA      | 0              | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| Activation Request                                    | AR       | 0              | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| Device Modes                                          | ·        |                |   |   |   |   |   |   |   |

| NT Mode, Adaptive Sampling (Note 6)                   | NTA      | 0              | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| NT Mode, Fixed Sampling                               | NTF      | 0              | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| TE Mode, Digital System Interface Slave (Note 7)      | TES      | 0              | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| TE Mode, Digital System Interface Master              | TEM      | 0              | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| Digital Interface Formats                             |          |                |   |   |   |   |   |   |   |

| Digital System Interface Format 1 (Note 6)            | DIF1     | 0              | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| Digital System Interface Format 2                     | DIF2     | 0              | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| Digital System Interface Format 3                     | DIF3     | 0              | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| Digital System Interface Format 4                     | DIF4     | 0              | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| BCLK Frequency Settings                               | ·        |                |   |   |   |   |   |   |   |

| Set BCLK to 2.048 MHz                                 | BCLK1    | 1              | 0 | 0 | 1 | 1 | 0 | 0 | 0 |

| Set BCLK to 256 kHz                                   | BCLK2    | 1              | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

| Set BCLK to 512 kHz                                   | BCLK3    | 1              | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| Set BCLK to 2.56 MHz                                  | BCLK4    | 1              | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| B Channel Exchange                                    |          |                |   |   |   |   |   |   |   |

| B Channels Mapped Direct, B1 to B1, B2 to B2 (Note 6) | BDIR     | 0              | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| B Channels Exchanged, B1 to B2, B2 to B1              | BEX      | 0              | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

TABLE 4. Control Register Functions (Continued)

| Function                                               | Mnemonic | nic Bit Number |   |   |          |          |    |          |          |

|--------------------------------------------------------|----------|----------------|---|---|----------|----------|----|----------|----------|

|                                                        |          | 7              | 6 | 5 | 4        | 3        | 2  | 1        | 0        |

| D Channel Access                                       |          |                |   |   |          |          |    |          |          |

| D Channel Request, Class 1 Message                     | DREQ1    | 0              | 0 | 0 | 0        | 1        | 1  | 1        | 0        |

| D Channel Request, Class 2 Message                     | DREQ2    | 0              | 0 | 0 | 0        | 1        | 1  | 1        | 1        |

| D Channel Access Control                               | 22       |                |   |   |          | <u> </u> |    | <u> </u> |          |

| Enable D-Channel Access Mechanism, TE Mode (Note 8)    | DACCE    | 1              | 0 | 0 | 1        | 0        | 0  | 0        | 0        |

| Disable D-Channel Access Mechanism, TE Mode (Note 8)   | DACCD    | 1              | 0 | 0 | 1        | 0        | 0  | 0        | 1        |

| Force Echo Bit to 0                                    | EBIT0    | 1              | 0 | 0 | 1        | 0        | 1  | 1        | 0        |

| Force Echo Bit to Inverted Received D Bit              | EBITI    | 1              | 0 | 0 | 1        | 0        | 1  | 1        | 1        |

| Reset EBITI and EBIT0 to Normal Condition (Note 6)     | EBITNRM  | 1              | 0 | 0 | 1        | 1        | 1  | 0        | 0        |

| D Channel Clock Enable                                 | DCKE     | 1              | 1 | 1 | 1        | 0        | 0  | 0        | 1        |

| End of Message Interrupt                               | DORL     | '              | ' | ' | '        |          |    |          | '        |

| <u> </u>                                               | EIE      | 0              | 0 | 0 | 1        | 0        | 0  | 0        | 0        |

| EOM Interrupt Enabled (Note 6)                         |          | -              |   |   |          | _        |    |          |          |

| EOM Interrupt Disabled                                 | EID      | 0              | 0 | 0 | 1        | 0        | 0  | 0        | 1        |

| Multiframe Circuit and Interrupt                       | MEA      |                |   |   | T .      |          |    | T .      |          |

| Enable SC1/Q Messaging and MFR1 Interrupt              | MIE1     | 0              | 0 | 0 | 1        | 0        | 0  | 1        | 0        |

| Disable SC1/Q Message and Interrupt (Note 6)           | MID1     | 0              | 0 | 0 | 1        | 0        | 0  | 1        | 1        |

| Enable 5 ms Interrupt (Every Multiframe)               | MFC1E    | 0              | 0 | 1 | 0        | 0        | 0  | 1        | 0        |

| Disable 5 ms Interrupt (Note 6)                        | MFC1D    | 0              | 0 | 1 | 0        | 0        | 0  | 1        | 1        |

| Enable 30 ms Interrupt (6 Multiframes)                 | MFC6E    | 0              | 0 | 1 | 0        | 0        | 1  | 0        | 0        |

| Disable 30 ms Interrupt (Note 6)                       | MFC6D    | 0              | 0 | 1 | 0        | 0        | 1  | 0        | 1        |

| Enable SC2 Messaging and MFR2 Interrupt                | MIE2     | 0              | 0 | 1 | 0        | 0        | 1  | 1        | 0        |

| Disable SC2 Messaging and Interrupt (Note 6)           | MID2     | 0              | 0 | 1 | 0        | 0        | 1  | 1        | 1        |

| Multiframe Receive Message Validation                  |          |                |   |   |          |          |    |          |          |

| Enable 3x and 1x Validation of Received Data           | ENV      | 0              | 0 | 1 | 0        | 1        | 0  | 0        | 0        |

| Disable 3x and 1x Validation of Received Data (Note 6) | DISV     | 0              | 0 | 1 | 0        | 1        | 0  | 0        | 1        |

| Multiframe Transmit Registers                          |          |                |   |   |          |          |    |          |          |

| Write to Multiframe Transmit Register                  | MFT1L    | 0              | 0 | 1 | 1        | M1       | M2 | М3       | M4       |

| (SC1/Q Low Priority Messages)                          |          |                |   |   |          |          |    |          |          |

| Write to Multiframe Transmit Register                  | MFT1H    | 0              | 1 | 0 | 0        | M1       | M2 | МЗ       | M4       |

| (SC1/Q High Priority Messages)                         |          |                |   |   |          |          |    |          |          |

| Write to Multiframe Transmit Register                  | MFT2     | 0              | 1 | 0 | 1        | M1       | M2 | МЗ       | M4       |

| (SC2 Messages)                                         |          |                |   |   |          |          |    |          |          |

| B1 Channel Enable/Disable                              |          |                |   |   |          |          |    |          |          |

| B1 Channel Enabled                                     | B1E      | 0              | 0 | 0 | 1        | 0        | 1  | 0        | 0        |

| B1 Channel Disabled (Note 6)                           | B1D      | 0              | 0 | 0 | 1        | 0        | 1  | 0        | 1        |

| B2 Channel Enable/Disable                              | •        |                |   |   |          |          |    |          |          |

| B2 Channel Enabled                                     | B2E      | 0              | 0 | 0 | 1        | 0        | 1  | 1        | 0        |

| B2 Channel Disabled (Note 6)                           | B2D      | 0              | 0 | 0 | 1        | 0        | 1  | 1        | 1        |

| Loopback Test Modes                                    | 1        |                |   |   |          |          |    |          |          |

| Loopback B1 Towards Line Interface                     | LBL1     | 0              | 0 | 0 | 1        | 1        | 0  | 0        | 0        |

| Loopback B2 Towards Line Interface                     | LBL2     | 0              | 0 | 0 | 1        | 1        | 0  | 0        | 1        |

| Loopback 2B+D Towards Digital Interface                | LBS      | 0              | 0 | 0 | 1        | 1        | 0  | 1        | 0        |

| Loopback B1 Towards Digital Interface                  | LBB1     | 0              | 0 | 0 | 1        | 1        | 1  | 0        | 0        |

| Loopback B2 Towards Digital Interface                  | LBB2     | 0              | 0 | 0 | 1        | 1        | 1  | 0        | 1        |

| Clear All Loopbacks (Note 6)                           | CAL      | 0              | 0 | 0 | 1        | 1        | 0  | 1        | 1        |

| Control Device State Reading                           |          |                |   |   | <u>'</u> | <u>'</u> |    | <u>'</u> | <u>'</u> |

| Enable the Device State Output on the NOCST            | ENST     | 1              | 0 | 0 | 1        | 0        | 0  | 1        | 0        |

| Enable the Device State Sulput Off the NOOUT           | LIVOI    | 1 1            |   |   | 1 1      |          |    | 1 1      |          |

TABLE 4. Control Register Functions (Continued)

| TABLE 4. CONTOUR                                      | TABLE 41 CONTROL (CONTRIBUTE) |            |   |   |   |   |    |    |    |

|-------------------------------------------------------|-------------------------------|------------|---|---|---|---|----|----|----|

| Function                                              | Mnemonic                      | Bit Number |   |   |   |   |    |    |    |

|                                                       |                               | 7          | 6 | 5 | 4 | 3 | 2  | 1  | 0  |

| Control Device State Reading                          |                               |            |   |   |   |   |    |    |    |

| Disable the Device State Output on the NOCST (Note 6) | DISST                         | 1          | 0 | 0 | 1 | 0 | 0  | 1  | 1  |

| Control of Additional Interrupts                      |                               |            |   |   |   |   |    |    |    |

| Enable the Slip and RMFE Interrupts                   | ENINT                         | 1          | 0 | 0 | 1 | 0 | 1  | 0  | 0  |

| Disable the Slip and RMFE Interrupts (Note 6)         | DISINT                        | 1          | 0 | 0 | 1 | 0 | 1  | 0  | 1  |

| Control Polarity of B Channel Data                    |                               |            |   |   |   |   |    |    |    |

| Invert B1 Channel Data                                | INVB1                         | 1          | 0 | 0 | 1 | 1 | 1  | 0  | 1  |

| Invert B2 Channel Data                                | INVB2                         | 1          | 0 | 0 | 1 | 1 | 1  | 1  | 0  |

| Normal B1, B2 Data (Note 6)                           | NRMB12                        | 1          | 0 | 0 | 1 | 1 | 1  | 1  | 1  |

| Pin Signal Selection                                  |                               |            |   |   |   |   |    |    |    |

| Redefine Pin Signals (See Table 1)                    | PINDEF                        | 1          | 1 | 1 | 0 | 0 | x2 | x1 | х0 |

|                                                       |                               |            |   |   |   |   |    |    |    |

Note 6: Indicates initial state following Power-on initialization.

Note 7: Slave-slave mode.

Note 8: DACCD is the power up default in TES mode and DACCE is the power up default in TEM mode.

**TABLE 5. Status Register Functions**

| Function                                                                      | Mnemonic   |   |    |    |    |    |    |    |    |

|-------------------------------------------------------------------------------|------------|---|----|----|----|----|----|----|----|

|                                                                               |            | 7 | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Line Signal Detected Far-End                                                  | LSD        | 0 | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| Activation Pending                                                            | AP         | 0 | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| Activation Indication                                                         | Al         | 0 | 0  | 0  | 0  | 1  | 1  | 0  | 0  |

| Error Indication                                                              | EI         | 0 | 0  | 0  | 0  | 1  | 1  | 1  | 0  |

| Deactivation Indication                                                       | DI         | 0 | 0  | 0  | 0  | 1  | 1  | 1  | 1  |

| End of D-ch Tx Message                                                        | EOM        | 0 | 0  | 0  | 0  | 0  | 1  | 1  | 0  |

| Lost Contention for D-ch                                                      | CON        | 0 | 0  | 0  | 0  | 0  | 1  | 1  | 1  |

| Multiframe Receiver Buffer 1 (SC1/Q)                                          | MFR1       | 0 | 0  | 1  | 1  | M1 | M2 | МЗ | M4 |

| Multiframe Receiver Buffer 2 (SC2)                                            | MFR2       | 0 | 1  | 0  | 1  | M1 | M2 | МЗ | M4 |

| Multiframe Clock (5 ms or 30 ms)                                              | MFC        | 0 | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| Additional Interrupts after ENINT Comman                                      | nd         |   |    |    |    |    |    |    |    |

| Receive Multiframe Error                                                      | RMFE       | 0 | 0  | 0  | 0  | 0  | 1  | 0  | 1  |

| Phase Slip in Data Buffer for Bx Data                                         | SLIP TX    | 0 | 0  | 0  | 0  | 1  | 0  | 0  | 1  |

| Phase Slip in Data Buffer for Br Data                                         | SLIP RX    | 0 | 0  | 0  | 0  | 1  | 0  | 1  | 0  |

| Phase Slip for Both Bx and Br Data                                            | SLIP TX/RX | 0 | 0  | 0  | 0  | 1  | 0  | 1  | 1  |

| NO Change Return Status                                                       | •          |   |    |    |    |    |    |    |    |

| NOC Status after DISST Command (Note 9)                                       | NOC        | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| NOC Status after ENST Command<br>See <i>Table 6</i> for Device State Decoding | NOCST      | 1 | S3 | S2 | S1 | 0  | 0  | 0  | 0  |

Note 9: Indicates initial state following Power-on Initialization.

### STATUS INDICATOR DESCRIPTIONS

LSD This interrupt indicates that the far-end of the line is attempting to Activate the interface. May be used as an alternative to the LSD pin to "wake-up" a microprocessor.

AP If set, indicates that either INFO 1 frames have been identified in an NT receiver, or INFO 2 or INFO 4 frames have been identified in a TE re-

ceiver. Requires an AR control instruction to allow Activation to be completed.

This interrupt occurs when the closing flag of a D-channel message has been transmitted by a TE on the S interface, indicating successful completion of a packet. The Interrupt associated with this bit can be disabled via the Control Register if decired.

CON This interrupt occurs when, during transmission of

- a packet in the D channel, a received E bit does not match the last transmitted D bit, indicating a lost collision.

- Al This interrupt indicates that the interface has been successfully Activated in response to an Activation Request.

- El Set when loss of frame alignment is detected.

- DI If set, indicates that the interface has been Deactivated

- MFR1 This interrupt indicates when the Multiframe SC1/Q channel data buffer requires servicing, see Multiframe Maintenance section. The MID1 command disables this interrupt.

- MFR2 This interrupt indicates when the Multiframe SC2 channel data buffer requires servicing, see Multiframe Maintenance section. The MID2 command disables this interrupt.

- MFC This status interrupt provides a transmit multiframe clock. It can be selected to occur on every multiframe boundary (5 ms) by the MFC1E command or on each 6 multiframe boundary (30 ms) by the MFC6E command. This interrupt can be used to synchronize the SC1/Q and SC2 multiframe transmit messages.

- RMFE A bipolar Violation or DC balance error causes this Receive Multiframe Error Interrupt in both NT and TE modes. At the NT end, upon receiving the RMFE interrupt, the local microcontroller must inform the TEs with a FECV message (via the MFT1H register). The NT or the TE end can keep a count of RMFE interrupts to monitor the line block error rate at its receiver.

- SLIP This interrupt indicates if the clock phase shift in the jitter/wander buffers exceeded the phase shift limit and changed the internal data buffer delay to accommodate it. One interrupt is generated and is coded as X'09 for Tx buffer slip: X'0A for Rx buffer slip: and X'0B for both Tx and Rx buffer slip.

- NOC This NOC status is returned for every command when there is no change of status to be reported. It is read in the power-up default state and after the DISST command. No interrupt is generated.

- NOCST This status response occurs only after the ENST command. The NOCST status is returned in response to any subsequent command when there is no status change that needs to be reported with an interrupt. It contains the device activation state information, see the section on Activation State machine access.

## CONTROL REGISTER INSTRUCTIONS ACTIVATION/DEACTIVATION

- PUP This power-up command enables all analog circuitry, starts the XTAL and resets the state machines to the de-activated state, i.e. transmitting INFO 0 (no signal). It also inhibits the LSD output.

- PDN This power-down command immediately forces the device to a low power state, without sequencing through any of the de-activation states. It should therefore only be used after the TP3420A has been put in a known state, e.g. in a TE after a DI status in-

- dication has been reported. It also enables the LSD circuit.

- AR Activation Request initiates the specified Activation sequence. It is recommended that an AR be delayed at least 2 ms after the device is powered-up using the PUP command.

- DR Deactivation Request, which forces the device through the appropriate deactivation sequence specified in I.430. Should be used at the NT end only.

- FI2 Effective only in NT modes, and only after Activation has been completed, this instruction forces the NT to transmit INFO 2 frames instead of INFO 4, normally to allow testing at the U interface. Provided INFO 3 is still being received from the TE(s), an AP Status Interrupt will be generated and loop synchronization maintained, but 2B+D transmission is inhibited. To restore full loop activation, with the NT sending INFO 4, an AR command is required in the normal way.

- MMA Intended for test equipment applications, this instruction allows the receive line interface (Li±) to be connected to the TE-to-NT direction twisted pair and to activate on the received INFO 3 signals while being the master of the DSI. The received 2B+D can then be passively monitored (the line transmit output Lo± would not be connected). TE Master mode must be selected first (TEM).

#### **DEVICE MODES**

- NTA NT Mode, Adaptive Sampling should be selected when the device is in an NT on any wiring configuration up to the maximum specified length for operation. Multiple terminals, if required, must be grouped within approximately 100 meters of each other (depending on cable capacitance, see I.430). The Digital System Interface is a slave to external BCLK and FS sources.

- NTF NT Mode Fixed Sampling may be selected when the device is in an NT on a passive bus wiring configuration up to approximately 200 meters in length (depending on cable type). In this mode the receiver DPLL is disabled and sampling of the received symbols is fixed, to enable multiple terminals (nominally up to 8) to be connected anywhere along the passive bus. Again, the DSI is a slave to external BCLK and FS sources.

- TEM TE Mode DSI Master should be selected when the device is in a TE. The TP3420A is then the source of the BCLK and FS signals, and access to the Transmit D channel, including the priority and contention resolution control, is enabled as described in the section on TE Mode D-Channel Access.

- TES TE Mode DSI Slave, otherwise known as "Slave-slave" mode, should be selected when the device is used on the T-interface side of an NT-2. The TP3420A System Interface is then driven by BCLK and FS sources in the NT-2. Data buffers and a clock re-synchronizer enable this interface to function with jittering sources for BCLK and FS. All D Channel access control circuitry is disabled, i.e. D Channel data at the Bx input is continuously transmitted to the line; there is no monitoring of the D-echo channel from the network direction, and DREQ instructions are ignored. Also, the SCLK function is enabled at the DEN<sub>x</sub>/SCLK pin.

#### **DIGITAL INTERFACE FORMATS**

DIF1) These instructions select the format of the DIF2) Digital Interface timing, see *Figure 3* and

DIF3) Figure 4.

DIF4)

#### **BCLK FREQUENCY SETTINGS**

BCLK1

These instructions change the frequency of a

BCLK2

selected Digital Interface Format. They

BCLK3

should only be used after the Digital Interface Format has been selected.

However, if another DIF command is applied after this command, it will override the BCLK setting

T. . . . . . .

The default BCLK settings for the DIF

formats are as follows:

DIF1→BCLK1 DIF2→BCLK2 DIF3→BCLK3 DIF4→BCLK4

#### **B CHANNEL CONTROL**

BDIR) These commands provide for the exchange

BEX ) of data between the B1 and B2 channels as

it passes through the device, (Note 10).

B1E) When either or both B channels are

B1D) disabled, binary 1s are transmitted on the

B2E) line in those B channel bit positions,

B2D) regardless of data at the Bx input, and the Br output is TRI-STATE in those bit

positions.

INVB1, INVB2 NRMB12 These commands allow control over the polarity of the data transmitted over the B1 and B2 channel. The default or the NRMB12 command sets the data to be operated in

command sets the data to be operated in normal mode. See section on operation over restricted channels.

Note 10: When enabling a B channel in conjunction with the BEX Command, the channels are referenced at the Digital System Interface, not the line interface e.g. to connect the B1 slot on the DSI with the B2 slot on the line interface, use the BEX and B1E commands.

#### **D CHANNEL ACCESS**

DREQ1) DREQ2) This is a request from Layer 2 device to the TP3420A (in the TE modes) to attempt to transmit a D channel message at the S interface. Use DREQ1 to select the access priority for a Class 1 message (Q.931 Signaling), or DREQ2 for a Class 2 message.

DACCD is the power-up default condition in DACCD TES mode, and DACCE is the power-up

default condition in TEM mode. The D channel Access algorithm can be enabled (by DACCE) or disabled (DACCD) in both TES mode or TEM mode. The D support a passive bus network lines. The DENx pin signal provides the flow control strobe according to the access algorithm.

DCKE) This command alters pin signals to provide

direct D-channel flow control with certain HDLC devices. Pin 8 provides gated (DEN $_{x}$ ) DTCK, Pin 18 provides gated (DEN $_{R}$ ) DRCK, and Pin 11 inputs TxD data.

See applications note to interface with MC68302 for use of this command.

EIE Enable EOM interrupt.

EID Disable EOM interrupt.

EBITI, These commands allow control over the EBITO, D-Echo bit generated in the NT mode EBITNRM device. The default state or the EBITNRM

command sets Echo bit to its normal condition which is to reflect the received D bit back out to the TEs as the Echo bit. The EBITO command forces the Echo bit to be set to "0" on every frame going back to the TEs. The EBITI command forces the transmitted Echo bit to be inverted from that which is computed from incoming D bits.

#### LOOPBACK TEST MODES

Three classes of loopback mode are available on the SID, selected by writing the appropriate Control instruction.

LBS This loopback at the system interface loops the two B channels and the D channel from the  $B_x$  input to the  $B_r$  output. It may be set either when the device is activated, in which case it is transparent (i.e. the channels are also transmitted to the line), or when it is deactivated.

LBL1/2 These loopbacks turn each individual B channel from the line receive input back to the line transmit output. They may be set separately or together.

LBB1/2 These loopbacks at the Digital System Interface loop the B1 (LBB1) or the B2 (LBB2) channel data from the  $B_x$  input to the  $B_r$  output. The  $B_x$  input data is also sent to the line transmit output.

CAL This command clears all loopbacks.

### **EXTERNAL SELF-ACTIVATING LOOPBACK**

A quick self-test of the device is possible by connecting together the line sides of the transmit and receive transformers. NTA or NTF mode must be selected, and the device can then be activated by the normal command sequence (Note 11).

Note 11: This test mode is not possible by direct connection of  $L_0\pm$  and  $L_i\pm$  pins due to incompatible internal bias voltages.

#### **MULTIFRAME TRANSMIT AND RECEIVE REGISTERS**

| MFT1L) | With the device in TE Mode, data entered in  |

|--------|----------------------------------------------|

| MFT1H) | M1, M2, M3 and M4 bits of MTF1L is           |

| MFT2)  | transmitted towards the NT in multiframe bit |

| MFR1)  | positions Q1, Q2, Q3 and Q4 respectively.    |

| MFR2)  | With the device in NT Mode, data entered     |

| MIE1)  | (via MFT1L, MFT1H) in the M bit positions is |

| MID1)  | transmitted towards the TE in multiframe bit |

| MID2)  | positions S11, S12, S13 and S14              |

|        | respectively. Data entered via MFT2          |

|        | command in the M bit positions is            |

|        | transmitted in multiframe bit positions S21, |

|        | S22, S23, S24 respectively. The Multiframe   |

|        | Channel and Interrupts (MFR1, MFR2) must     |

|        | be enabled by the MIE1, MIE2 to use these    |

|        | channels. The MID1, MID2 commands will       |

|        | disable the interrupts MFR1, MFR2 (and in    |

|        | NT mode only, it will also disable the       |

|        | multiframing clock to the TEs). See also the |

|        | section on Multiframe Maintenance Channel.   |

#### **MULTIFRAME MESSAGE REPETITION AND** VALIDATION

| MFC1E)<br>MFC6E)<br>MFC1D) | These commands control the frequency of<br>the MFC Interrupt that is used as an aid to<br>the software to transmit multiframe |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| MFC6D)                     | commands. If both MFC1E and MFC6E                                                                                             |

|                            | commands are set, then the MFC Interrupt                                                                                      |

|                            | will occur every multiframe (5 ms). The                                                                                       |

|                            | interrupt may be disabled with MFC1D,                                                                                         |

|                            | MFC6D. The MFC6E command also enables                                                                                         |

|                            | the internal 6 multiframe counter that                                                                                        |

|                            | ensures that every MFT1L command is sent                                                                                      |

|                            | for 6 consecutive multiframes before sending                                                                                  |

|                            | another command loaded in the MFT1L                                                                                           |

|                            | register. The MFC6D also disables the                                                                                         |

|                            | internal 6 multiframe counter. See also the                                                                                   |

|                            | section on Multiframe Maintenance Channel.                                                                                    |

**ENINT** This command enables the RMFE and SLIP interrupts and thus accesses new features of TP3420A.

DISINT Disables RMFE and SLIP interrupts.

ENV) DISV)

ENV enables the 3-times validation of certain SC1/Q and SC2 channel messages (Table 8) before generating the MFR1 and MFR2 interrupt respectively. DISV disables this circuit so that the MFR1 and MFR2 interrupts are generated whenever there is a change in the received multiframe word in

either channel.

ENST) DISST)

ENST enables the state of the internal Activation State machine to be reported to the microcontroller by the NOCST response to any MICROWIRE command thereafter. The DISST causes the NOCST to be replaced by the normal NOC status. See the section on Activation State machine access.

PINDEF

This command is used to choose alternate pin functions on Pins 8 and 18. Please see Table 1 for the selection values.

#### **ACTIVATION STATE MACHINE ACCESS**

The TP3420A has a mechanism which allows the microcontroller to read the internal activation state of the chip. The MI-CROWIRE command ENST (Enable Status) X'92 enables the device state information to be output as a MICROWIRE status word NOCST (1,S3,S2,S1,0,0,0,0) in response to any subsequent MICROWIRE command. However, if a state change interrupt occurs, e.g., an AP (Activation Pending) then the interrupt status value is returned, otherwise the NOCST status is returned. See Table 6 below to relate the values of the S3, S2, S1 bits to internal activation state of the device.

TABLE 6. TP3420A Activation State Table

| NT   | TE | S3 | S2 | S1 |

|------|----|----|----|----|

| G1   | F1 | 0  | 0  | 0  |

| G1.1 | F2 | 0  | 0  | 1  |

| G1.2 | F3 | 0  | 1  | 0  |

| G2   | F4 | 0  | 1  | 1  |

| _    | F5 | 1  | 0  | 0  |

| _    | F6 | 1  | 0  | 1  |

| _    | F7 | 1  | 1  | 0  |

| G3   | F8 | 1  | 1  | 1  |

A clean way of monitoring the device state is to write a ENST command, followed immediately by a DISST (Disable Status) command. The NOCST status returned at the end of the DISST contains the actual state of the device. Subsequent MICROWIRE commands will be responded by NOC (0,0,0,0,0,0,0,0). This method makes it easy for the software to keep track of when to expect the device state via the NOCST.

Another method would be to repeat the NOP command a couple of times after a ENST command and observe that the device state information (through the NOCST) is repeated to be sure of the state of the device.

### IDENTIFYING A TP3420A FROM A TP3420 DEVICE

The TP3420A on power-up default is functionally compatible with a TP3420 device, and hence software written for a TP3420 is applicable for a TP3420A device. Additional device features may be invoked by MICROWIRE commands. A simple way of identifying a TP3420A from a TP3420 is as fol-

Upon application of power, write ENST followed by DISST MICROWIRE commands to the device and evaluate the NOCST status word. If the device is a TP3420A the value should be 1000000, indicating the device is in F1/G0 state. A TP3420 device will ignore the ENST/DISST commands and return the normal NOC (00000000) status back.

### MAINTENANCE LOOPBACKS

The TP3420A supports all the ANSI T1.605 and I.430 loopback modes and some additional loopback modes to allow greater flexibility in performing fault isolation.

- B1 digital loopback (using LBB1 command) with any FSa/FSb relationship in all TE or NT modes.

- 2. B2 digital loopback (LBB2) with any FSa/FSb relationship in all TE or NT modes.

- Contiguous B1+B2 (128 kbit/s) digital loopback (LBB1, LBB2) in TEM mode and in NT/TES modes if FSa is phase synchronous with FSb.

- Contiguous B1+B2+D (144 kbit/s) digital loopback (LBD) in TEM mode and in NT/TES modes if FSa is phase synchronous with FSb.

- B1 line loopback (using LBL1) with any FSa/FSb relationship in all TE or NT modes.

- B2 line loopback (using LBL2) with any FSa/FSb relationship in all TE nor NT modes.

- Contiguous B1+B2 (128 kbit/s pipe) line loopback (LBL1, LBL2) with equal delay, available in TEM mode, and in NT/TES modes if FSa is phase synchronous with FSh

Note that a line loopback for the D channel is not specified in the CCITT I.430 or the T1-605 specification, to ensure that D channel signaling is transparently passed end-to-end.

#### **ACTIVATION/DEACTIVATION: TP3420A IN NT MODE**

Activation (i.e. transmission and loop synchronization) may be initiated from either end of the loop.

Activation initiated from the NT: to initiate Activation from the NT, the TP3420A must be powered up, using a PUP command, followed (Note 12) by an AR instruction to the Control Register. Network timing, i.e., an 8 kHz input to FS<sub>a</sub>, must be present at this time. The device then begins to send data framed as INFO 2 type, in which bits in the B, D and D-echo channels are set to binary 0. These frames are detected by the TE, which replies with data framed as INFO 3 type, synchronized to received frames. A flywheel circuit in the TP3420A NT searches for 3 consecutive correctly formatted receive frames to acquire frame synchronization. If Multiframing is enabled (MIE), 60 correct frames (3 multiframes) are required to achieve full loop synchronization. When it is correctly in sync with received frames, the NT interrupts the control processor with Status Indication type AP. A second AR command is required to cause the NT to send INFO 4 frames, in which the B and D channels are enabled for transmission; Status Indication type AI is then set, and the INT output is pulled low to indicate Activation complete.

Note 12: A delay of  $\geq$ 2 msecs is recommended to ensure that all internal circuits have settled.

Activation initiated by a TE: when Activation is initiated by a TE, the TP3420A in NT mode will detect the incoming INFO 1 signal and, if it is powered-down will pull the LSD pin and INT low, either of which can be used to "wake-up" a microprocessor. A PUP command must then be written to power-up the TP3420. Upon identifying the INFO 1 signal, the device will set Status Indication type AP and pull  $\overline{\text{INT}}$  low to indicate that Activation is pending. No INFO 2 frames will be transmitted until a Control instruction type AR is written to the device, which allows the Activation sequence to proceed as described above.

Once Activated, loss of frame alignment is assumed by the TP3420A when a time which is equivalent to three frames has passed without it detecting any of the valid pairs of line code violations which obey the framing rule. If the NT does detect alignment loss it will start to transmit INFO 2. At this point the Error Indication (EI) primitive is set, the  $\overline{\text{INT}}$  output is pulled low and the receiver searches to identify the incoming signal and attempt to re-acquire loop synchronization. If it successfully re-establishes synchronization with the incoming signal (INFO 3 frames), a further interrupt is gener-

ated with Status Indication type AI and re-activation can be completed by sending an AR command. If, however, the receiver subsequently identifies that the incoming line signal has ceased, i.e. INFO 0 is being received, Status Indicator EI is set and ĪNT pulled low, with the transmitted frames changed to INFO 2. Deactivation can then be completed by a DR command, following which Status Indication type DI is set and the ĪNT output pulled low to indicate De-activation. If required, a PDN instruction may be written to the Control Register to power-down the device and enable the LSD output

I.430 recommends 2 timers should be available in an NT. An Activation Request to the TP3420A should be associated with the start of an external Timer 1, if required. Timer 1 should be stopped when the Al interrupt is generated following successful Activation. If Timer 1 expires before Al is generated, however, Control Instruction type DR should be written to the device to force de-activation. Timer 2, which is specified to prevent unintentional reactivation, is not required since the TP3420A can uniquely recognise INFO 1 frames.

## ACTIVATION/DEACTIVATION: TP3420A IN TE MODE