Data Sheet: Technical Data

### Document Number: MC34932 Rev. 4.0, 8/2016

# Dual 5.0 A H-Bridge

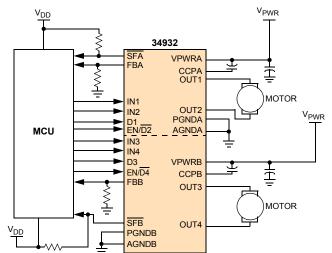

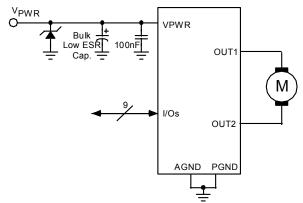

The 34932 is a monolithic H-Bridge Power IC in a robust thermally enhanced package. The 34932 has two independent monolithic H-Bridge Power ICs in the same package. They are designed for any low voltage DC servo motor control application within the current and voltage limits stated in this specification. This device is powered by SMARTMOS technology.

Each H-Bridge in the 34932 is able to control inductive loads with currents up to 5.0 A peak. RMS current capability is subject to the degree of heatsinking provided to the device package. Internal peak current limiting (regulation) is activated at load currents above 6.5 A ±1.5 A. Output loads can be pulse-width modulated (PWMed at frequencies up to 20 kHz. A load current feedback feature provides a proportional (0.24% of the load current) current output suitable for monitoring by a microcontroller's A/D input. A status flag output reports undervoltage, overcurrent, and overtemperature fault conditions.

Two independent inputs provide polarity control of two half-bridge totem pole outputs. Two independent disable inputs are provided to force the H-Bridge outputs to tri-state (high-impedance off state).

#### **Features**

- 5.0 V to 36 V continuous with 24 V nominal operating voltage (transient operation from 5.0 V to 40 V)

- 235 m $\Omega$  maximum R<sub>DS(on)</sub> at T<sub>J</sub> = 150 °C (each H-Bridge MOSFET)

- 3.0 V and 5.0 V TTL/CMOS logic compatible inputs

- Output short-circuit protection (short to VPWR or GND)

- Overcurrent limiting (regulation) via internal constant-off-time PWM

- Temperature dependant current limit threshold reduction to allow for continuous operation without shutdown

- All inputs have an internal source/sink to define the default (floating input) states

- Sleep mode with current draw < 20  $\mu$ A (each half with inputs floating or set to match default logic states)

# 34932 Industrial

### H-BRIDGE

### **Applications**

- DC motor control

- · DC brushed and servo motor driver

- · Copiers, printers

- Factory automation

- POS, ATM, vending kiosks

- Robotics

- · Security camera control

- Ticketing, toll systems

Figure 1. MC34932 simplified application diagram

# 1 Orderable parts

Table 1. Orderable part variations

| Part number | PWM frequency | Temperature (T <sub>A</sub> ) | Package     | Notes |

|-------------|---------------|-------------------------------|-------------|-------|

| MC34932EK   | 11 kHz        | -40 °C to 85 °C               | F4 COLOW ED | (4)   |

| MC34932SEK  | 20 kHz        | -40 C 10 65 C                 | 54 SOICW-EP | (1)   |

### Notes

1. To order parts in Tape & Reel, add the R2 suffix to the part number.

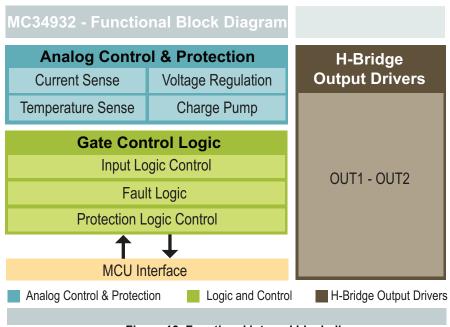

# 2 Internal block diagram

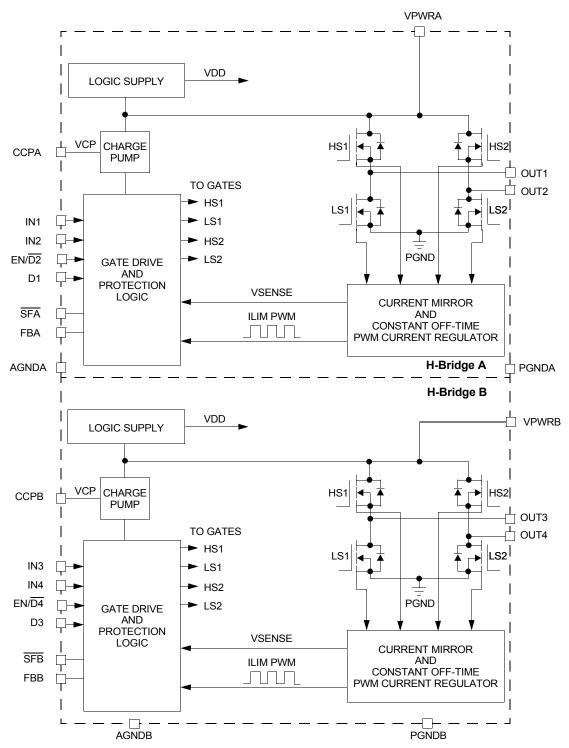

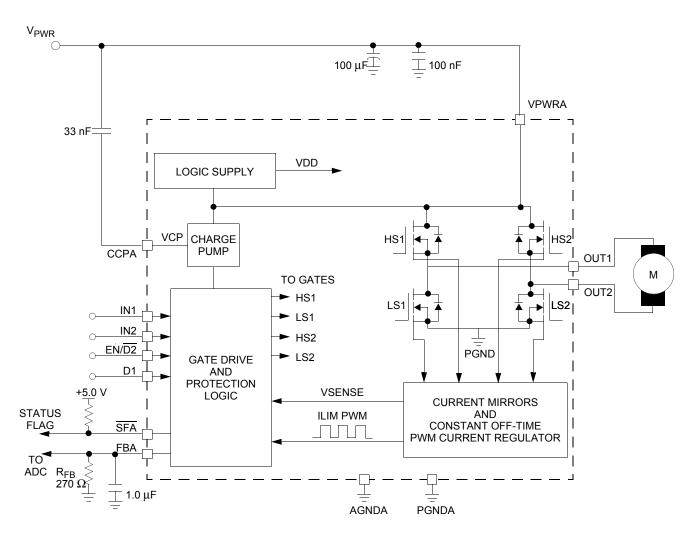

Figure 2. 34932 simplified internal block diagram

# 3 Pin connections

# 3.1 Pinout diagram

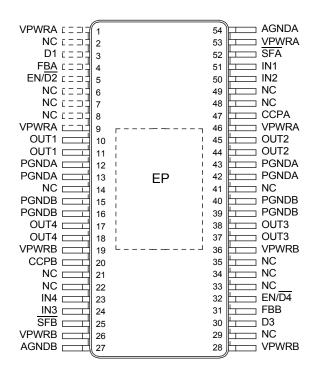

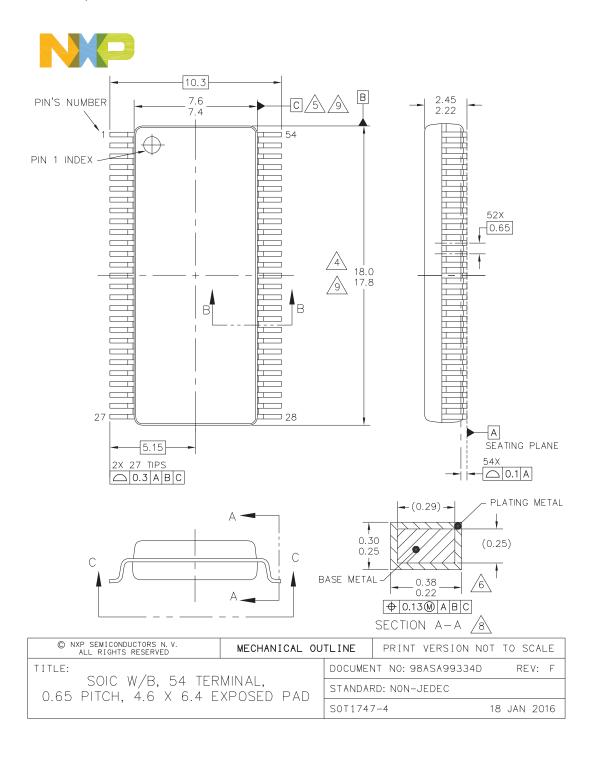

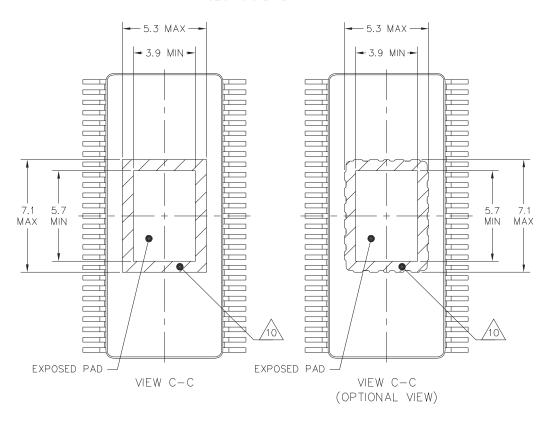

54 SOICW-EP Transparent Top View

Figure 3. 34932 pin connections

A functional description of each pin can be found in the Functional Description section beginning on page 12.

Table 2. 34932 pin definitions

| Pin number        | Pin name | Pin function     | Formal name                      | Definition                                                                                                                                                                                                                                          |

|-------------------|----------|------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                 | D1       | Logic Input      | Disable Input 1<br>(Active High) | When D1 is logic HIGH, both OUT1 and OUT2 are tri-stated. Schmitt trigger input with $\sim 80~\mu\text{A}$ source so default condition = disabled.                                                                                                  |

| 4                 | FBA      | Analog<br>Output | Feedback                         | H-Bridge A load current feedback output provides ground referenced 0.24% of the high-<br>side output current. (Tie to GND through a resistor if not used.)                                                                                          |

| 5                 | EN/D2    | Logic Input      | Enable Input                     | When EN/\overline{D2} is logic HIGH, H-Bridge A is operational. When EN/\overline{D2} is logic LOW, the H-Bridge A outputs are tri-stated and H-Bridge A is placed in Sleep Mode. (logic input with ~80 μA sink so default condition = Sleep Mode.) |

| 1, 9, 46, 53      | VPWRA    | Power Input      | Positive Power<br>Supply         | These pins must be connected together physically as close as possible and directly soldered down to a wide, thick, low resistance supply plane on the PCB.                                                                                          |

| 10, 11            | OUT1     | Power<br>Output  | H-Bridge Output 1                | H-Bridge A source of HS1 and drain LS1.                                                                                                                                                                                                             |

| 12, 13, 42,<br>43 | PGNDA    | Power<br>Ground  | Power Ground                     | High-current power ground pins must be connected together physically as close as possible and directly soldered down to a wide, thick, low resistance ground plane on the PCB. PGNDA should be connected to PGNDB with a low-impedance path.        |

Table 2. 34932 pin definitions (continued)

| Pin number                                             | Pin name       | Pin function                 | Formal name                      | Definition                                                                                                                                                                                                                                             |

|--------------------------------------------------------|----------------|------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15, 16, 39,<br>40                                      | PGNDB          | Power<br>Ground              | Power Ground                     | High-current power ground pins must be connected together physically as close as possible and directly soldered down to a wide, thick, low resistance ground plane on the PCB. PGNDB should be connected to PGNDA with a low-impedance path.           |

| 17, 18                                                 | OUT4           | Power<br>Output              | H-Bridge Output 4                | H-Bridge B Source of HS2 and drain of LS2.                                                                                                                                                                                                             |

| 19, 26, 28,<br>36                                      | VPWRB          | Power Input                  | Positive Power<br>Supply         | These pins must be connected together physically as close as possible and directly soldered down to a wide, thick, low resistance supply plane on the PCB.                                                                                             |

| 20                                                     | ССРВ           | Analog<br>Output             | Charge Pump<br>Capacitor         | External reservoir capacitor connection for H-Bridge B internal charge pump; connected to VPWRB. Allowable values are 30 to 100 nF. <b>Note</b> : This capacitor is required for the proper performance of the device.                                 |

| 23                                                     | IN4            | Logic Input                  | Input 4                          | Logic input control of OUT4.                                                                                                                                                                                                                           |

| 24                                                     | IN3            | Logic Input                  | Input 3                          | Logic input control of OUT3.                                                                                                                                                                                                                           |

| 25                                                     | SFB            | Logic Output<br>- Open Drain | Status Flag B<br>(Active Low)    | H-Bridge B open drain active LOW Status Flag output (requires an external pull-up resistor to V <sub>DD</sub> . Maximum permissible load current < 0.5 mA. Maximum V <sub>SFLOW</sub> < 0.4 V at 0.3 mA. Maximum permissible pull-up voltage < 7.0 V.) |

| 30                                                     | D3             | Logic Input                  | Disable Input 3<br>(Active High) | When D3 is logic HIGH, both OUT3 and OUT4 are tri-stated. Schmitt trigger input with ~80 μA source so default condition = disabled.                                                                                                                    |

| 31                                                     | FBB            | Analog<br>Output             | Feedback B                       | H-Bridge B load current feedback output provides ground referenced 0.24% of the high-<br>side output current. (Tie to GND through a resistor if not used.)                                                                                             |

| 32                                                     | EN/D4          | Logic Input                  | Enable Input                     | When EN/D4 is logic HIGH, H-Bridge B is operational. When EN/D4 is logic LOW, the H-Bridge B outputs are tri-stated and H-Bridge B is placed in Sleep Mode. (logic input with ~80μA sink so default condition = Sleep Mode.)                           |

| 37, 38                                                 | OUT3           | Power<br>Output              | H-Bridge Output 3                | H-Bridge B Source of HS1 and drain of LS1.                                                                                                                                                                                                             |

| 44, 45                                                 | OUT2           | Power<br>Output              | H-Bridge Output 2                | H-Bridge A source of HS2 and drain of LS2.                                                                                                                                                                                                             |

| 47                                                     | CCPA           | Analog<br>Output             | Charge Pump<br>Capacitor         | External reservoir capacitor connection for H-Bridge A internal charge pump; connected to VPWRA. Allowable values are 30 to 100 nF. <b>Note</b> : This capacitor is required for the proper performance of the device.                                 |

| 50                                                     | IN2            | Logic Input                  | Input 2                          | Logic input control of OUT2.                                                                                                                                                                                                                           |

| 51                                                     | IN1            | Logic Input                  | Input 1                          | Logic input control of OUT1; e.g., when IN1 is logic HIGH, OUT1 is set to VPWRA, and when IN1 is logic LOW, OUT1 is set to PGNDA. (Schmitt trigger Input with ~80 μA source so default condition = OUT1 HIGH.)                                         |

| 52                                                     | SFA            | Logic Output<br>- Open Drain | Status Flag<br>(Active Low)      | H-Bridge A open drain active LOW Status Flag output (requires an external pull-up resistor to V <sub>DD</sub> . Maximum permissible load current < 0.5 mA. Maximum V <sub>SFLOW</sub> < 0.4 V at 0.3 mA. Maximum permissible pull-up voltage < 7.0 V.) |

| 54<br>27                                               | AGNDA<br>AGNDB | Analog<br>Ground             | Analog Signal<br>Ground          | The low-current analog signal ground must be connected to PGND via low-impedance path (< 10 m $\Omega$ , 0 Hz to 20 kHz).                                                                                                                              |

| 2, 6 - 8, 14,<br>21, 22, 29,<br>33 - 35, 41,<br>48, 49 | NC             | None                         | No Connect                       | These pins have no electrical connection or function.                                                                                                                                                                                                  |

| EP                                                     | EP             | Thermal Pad                  | Exposed Pad                      | Exposed TAB is also the main heatsinking path for the device and must be connected to ground.                                                                                                                                                          |

## 4 Electrical characteristics

Ratings

Approximate Junction-to Case Thermal Resistance<sup>(9)</sup>

## 4.1 Maximum ratings

### Table 3. Maximum ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device. These parameters are not production tested.

**Symbol**

R<sub>THJC</sub>

Value

< 1.0

Unit

°C/W

| Electrical ratings                                                                                                     | ·                                           |                               |    |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------|----|

| Power Supply Voltage  Normal Operation (Steady-state) Transient Overvoltage <sup>(1)</sup>                             | V <sub>PWR(SS)</sub><br>V <sub>PWR(T)</sub> | -0.3 to 36<br>-0.3 to 40      | V  |

| Logic Input Voltage <sup>(2)</sup>                                                                                     | V <sub>IN</sub>                             | -0.3 to 7.0                   | V  |

| SFA, SFB Output <sup>(3)</sup>                                                                                         | VSF                                         | -0.3 to 7.0                   | V  |

| Continuous Output Current <sup>(4)</sup>                                                                               | I <sub>OUT(CONT)</sub>                      | 5.0                           | А  |

| ESD Voltage <sup>(5)</sup> • Human Body Model  • Machine Model  • Charge Device Model  • Corner Pins  • All Other Pins | V <sub>ESD1</sub><br>V <sub>ESD2</sub>      | ±2000<br>±200<br>±750<br>±500 | V  |

| hermal ratings                                                                                                         |                                             |                               |    |

| Storage Temperature                                                                                                    | T <sub>STG</sub>                            | -65 to 150                    | °C |

| Operating Temperature <sup>(6)</sup> • Ambient  • Junction                                                             | T <sub>A</sub>                              | -40 to 85<br>-40 to 150       | °C |

| Peak Package Reflow Temperature During Reflow <sup>(7),(8)</sup>                                                       | T <sub>PPRT</sub>                           | Note 8                        | °C |

|                                                                                                                        |                                             |                               | _  |

#### Notes

- 1. Device survives repetitive transient overvoltage conditions for durations not to exceed 500 ms at duty cycle not to exceed 5.0%. External protection is required to prevent device damage in case of a reverse power condition.

- 2. Exceeding the maximum input voltage on IN1, IN2, IN3, IN4, EN/\(\overline{D2}\), EN/\(\overline{D4}\), D1, or D3 may cause a malfunction or permanent damage to the device.

- 3. Exceeding the pull-up resistor voltage on the open drain SFA or SFB pin may cause permanent damage to the device.

- Continuous output current capability is dependent on sufficient package heatsinking to keep junction temperature ≤150 °C.

- 5. ESD testing is performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), Machine Model ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ), and the Charge Device Model (CDM), Robotic ( $C_{ZAP}$  = 4.0 pF).

- 6. The limiting factor is junction temperature, taking into account the power dissipation, thermal resistance, and heat sinking provided. Brief non-repetitive excursions of junction temperature above 150 °C can be tolerated, provided the duration does not exceed 30 seconds maximum. (Non-repetitive events are defined as not occurring more than once in 24 hours.)

- 7. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 8. NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to <a href="https://www.nxp.com">www.nxp.com</a>, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

- 9. Exposed heatsink pad plus the power and ground pins comprise the main heat conduction paths. The actual R<sub>θJB</sub> (junction-to-PC board) values varies depending on solder thickness and composition and copper trace thickness and area. Maximum current at maximum die temperature represents ~16 W of conduction loss heating in the diagonal pair of output MOSFETs. Therefore, the R<sub>θJA</sub> must be < 5.0 °C/W for maximum current at 70 °C ambient. Module thermal design must be planned accordingly.</p>

### 4.2 Static electrical characteristics

### Table 4. Static electrical characteristics

Characteristics noted under conditions 5.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted. Specifications given for H-Bridge A apply symmetrically to H-Bridge B.

| Characteristic                                                                                                                                                                       | Symbol                                                 | Min.             | Тур.          | Max.            | Unit         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|---------------|-----------------|--------------|

| Power inputs (VPWR)                                                                                                                                                                  |                                                        |                  | I.            |                 |              |

| Operating Voltage Range <sup>(10)</sup> • Steady-state • Transient (t < 500 ms) <sup>(11)</sup>                                                                                      | V <sub>PWR</sub> (SS)<br>V <sub>PWR</sub> (t)          | 5.0<br>–         | -<br>-        | 36<br>40        | V            |

| Sleep State Supply Current <sup>(12)</sup> • EN/\overline{D2} = Logic [0], IN1, IN2, D1 = Logic [1], and I <sub>OUT</sub> = 0 A                                                      | I <sub>PWR(SLEEP)</sub>                                | -                | 15            | 20              | μΑ           |

| Standby Supply Current (Part Enabled) • I <sub>OUT</sub> = 0 A, V <sub>EN</sub> = 5.0 V                                                                                              | I <sub>PWR(STANDBY)</sub>                              | -                | _             | 18              | mA           |

| Undervoltage Lockout Thresholds  VPWR(FALLING) VPWR(RISING) Hysteresis                                                                                                               | Vuvlo(active)<br>Vuvlo(inactive)<br>Vuvlo(hys)         | 4.15<br>-<br>150 | -<br>-<br>200 | -<br>5.0<br>350 | V<br>V<br>mV |

| Charge pump                                                                                                                                                                          |                                                        |                  |               | •               |              |

| Charge Pump Voltage (CP Capacitor = 33 nF), No PWM<br>• $V_{PWR}$ = 5.0 V<br>• $V_{PWR}$ = 36 V                                                                                      | V <sub>CP</sub> -V <sub>PWR</sub>                      | 3.5<br>-         | -             | _<br>12         | V            |

| Charge Pump Voltage (CP Capacitor = 33 nF), PWM = 11 kHz for MC34932EK and 20 kHz for MC34932SEK  V <sub>PWR</sub> = 5.0 V V <sub>PWR</sub> = 36 V                                   | V <sub>CP</sub> -V <sub>PWR</sub>                      | 3.5<br>-         | -<br>-        | -<br>12         | V            |

| Control inputs                                                                                                                                                                       |                                                        |                  |               |                 |              |

| Operating Input Voltage (IN1, IN2, D1, EN/\overline{D2}, IN3, IN4, D3, EN/\overline{D4})                                                                                             | VI                                                     | -                | _             | 5.5             | V            |

| Input Voltage (IN1, IN2, D1, EN/\overline{D2}, IN3, IN4, D3, EN/\overline{D4})  Logic Threshold LOW  Hysteresis                                                                      | V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>HYS</sub> | 2.0<br>-<br>250  | -<br>-<br>400 | -<br>1.0<br>-   | V<br>V<br>mV |

| Logic Input Currents, VPWR = 8.0 V  Input EN/\overline{D2}, EN/\overline{D4} (internal pull-downs), V_{IH} = 5.0 V  Inputs IN1, IN2, D1, IN3, IN4, D3 (internal pull-ups), VIL = 0 V | I <sub>IN</sub>                                        | 20<br>-200       | 80<br>-80     | 200<br>-20      | μА           |

#### Notes

- 10. Device specifications are characterized over the range of 8.0 V ≤ V<sub>PWR</sub> ≤ 36 V. Continuous operation above 36 V may degrade device reliability. Device is operational down to 5.0 V, but below 8.0 V the output resistance may increase by 50 percent.

- 11. Device survives the transient overvoltage indicated for a maximum duration of 500 ms. Transient not to be repeated more than once every 10 seconds.

- 12.  $I_{PWR(SLEEP)}$  is with Sleep Mode activated and  $EN/\overline{D2}$ , = logic [0], and IN1, IN2, D1 = logic [1] or with these inputs left floating. Typical value characterized under the following conditions:  $T_A = 85$  °C and  $V_{PWR} = 36$  V.

#### Table 4. Static electrical characteristics (continued)

Characteristics noted under conditions 5.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted. Specifications given for H-Bridge A apply symmetrically to H-Bridge B.

| Characteristic                                                                                                                                                                                                                       | Symbol                               | Min.                                        | Тур.                                       | Max.                                       | Unit                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------|--------------------------------------------|--------------------------------------------|----------------------------|

| Power outputs OUT1, OUT2                                                                                                                                                                                                             | l                                    |                                             |                                            |                                            |                            |

| Output-ON Resistance <sup>(14)</sup> , I <sub>LOAD</sub> = 3.0 A  • V <sub>PWR</sub> = 8.0 V, T <sub>J</sub> = 25 °C  • V <sub>PWR</sub> = 8.0 V, T <sub>J</sub> = 150 °C  • V <sub>PWR</sub> = 5.0 V, T <sub>J</sub> = 150 °C       | R <sub>DS(ON)</sub>                  | -<br>-<br>-                                 | 120<br>_<br>_                              | _<br>235<br>325                            | mΩ                         |

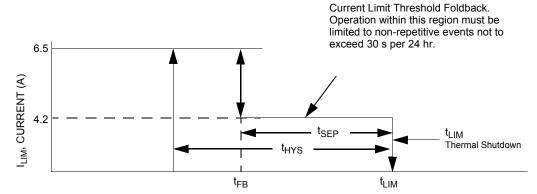

| Output Current Regulation Threshold<br>• $T_J < T_{FB}$<br>• $T_J \ge T_{FB}$ (Fold back Region - see Figure 9 and Figure 11) <sup>(13)</sup>                                                                                        | I <sub>LIM</sub>                     | 5.2<br>–                                    | 6.5<br>4.2                                 | 8.0<br>–                                   | A                          |

| High-side Short-circuit Detection Threshold (Short-circuit to Ground) <sup>(13)</sup>                                                                                                                                                | I <sub>SCH</sub>                     | 11                                          | 13                                         | 16                                         | Α                          |

| Low-side Short-circuit Detection Threshold (Short-circuit to V <sub>PWR</sub> ) <sup>(13)</sup>                                                                                                                                      | I <sub>SCL</sub>                     | 9.0                                         | 11                                         | 14                                         | Α                          |

| Output Leakage Current <sup>(15)</sup> , Outputs off, V <sub>PWR</sub> = 36 V MC34932EK and MC34932SEK  V <sub>OUT</sub> = V <sub>PWR</sub> V <sub>OUT</sub> = Ground                                                                | loutleak                             | _<br>-140                                   |                                            | 100<br>-                                   | μА                         |

| Output MOSFET Body Diode Forward Voltage Drop, I <sub>OUT</sub> = 3.0 A                                                                                                                                                              | V <sub>F</sub>                       | -                                           | -                                          | 2.0                                        | V                          |

|                                                                                                                                                                                                                                      | T <sub>LIM</sub><br>T <sub>HYS</sub> | 175<br>–                                    | _<br>12                                    | 200<br>-                                   | °C                         |

| Current Foldback at T <sub>J</sub> <sup>(13)</sup>                                                                                                                                                                                   | T <sub>FB</sub>                      | 165                                         | -                                          | 185                                        | °C                         |

| Current Foldback to Thermal Shutdown Separation <sup>(13)</sup>                                                                                                                                                                      | T <sub>SEP</sub>                     | 10                                          | -                                          | 15                                         | °C                         |

| High-side current sense feedback                                                                                                                                                                                                     |                                      | •                                           |                                            |                                            |                            |

| Feedback Current (pin FB sourcing current) <sup>(16)</sup> • I <sub>OUT</sub> = 0.0 mA  • I <sub>OUT</sub> = 300 mA  • I <sub>OUT</sub> = 500 mA  • I <sub>OUT</sub> = 1.5 A  • I <sub>OUT</sub> = 3.0 A  • I <sub>OUT</sub> = 6.0 A | I <sub>FB</sub>                      | 0.0<br>0.0<br>0.35<br>2.86<br>5.71<br>11.43 | -<br>270<br>0.775<br>3.57<br>7.14<br>14.29 | 50<br>750<br>1.56<br>4.28<br>8.57<br>17.15 | μΑ<br>μΑ<br>mA<br>mA<br>mA |

| Status flag <sup>(17)</sup>                                                                                                                                                                                                          |                                      |                                             |                                            |                                            |                            |

| Status Flag Leakage Current <sup>(18)</sup> • V <sub>SF</sub> = 5.0 V                                                                                                                                                                | ISFLEAK                              | -                                           | _                                          | 5.0                                        | μΑ                         |

| Status Flag SET Voltage <sup>(19)</sup> • $I_{\overline{SF}} = 300 \ \mu A$                                                                                                                                                          | V <del>SF</del> LOW                  | -                                           | _                                          | 0.4                                        | ٧                          |

#### Notes

- 13. This parameter is Guaranteed By Design.

- 14. Output-ON resistance as measured from output to VPWR and from output to GND.

- 15. Outputs switched OFF via D1.

- 16. Accuracy is better than 20% from 0.5 A to 6.0 A. Recommended terminating resistor value:  $R_{FB}$  = 270  $\Omega$ .

- Status Flag output is an open drain output requiring a pull-up resistor to logic V<sub>DD</sub>.

- 18. Status Flag Leakage Current is measured with Status Flag HIGH and not SET.

- 19. Status Flag Set Voltage measured with Status Flag LOW and SET with  $I_{\overline{SF}}$  = 300  $\mu$ A. Maximum allowable sink current from this pin is < 500  $\mu$ A. Maximum allowable pull-up voltage < 7.0 V.

## 4.3 Dynamic electrical characteristics

### Table 5. Dynamic electrical characteristics

Characteristics noted under conditions 5.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                               | Symbol                          | Min.       | Тур.       | Max.       | Unit |

|------------------------------------------------------------------------------|---------------------------------|------------|------------|------------|------|

| Timing characteristics                                                       |                                 |            |            |            |      |

| PWM Frequency <sup>(20)</sup> • MC34932EK • MC34932SEK                       | f <sub>PWM</sub>                | -<br>-     | _<br>_     | 11<br>20   | kHz  |

| Maximum Switching Frequency During Current Limit Regulation <sup>(21)</sup>  | f <sub>MAX</sub>                | -          | _          | 20         | kHz  |

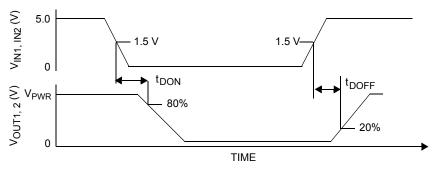

| Output ON Delay <sup>(22)</sup> • V <sub>PWR</sub> = 24 V                    | t <sub>DON</sub>                | -          | _          | 18         | μs   |

| Output OFF Delay <sup>(22)</sup> • V <sub>PWR</sub> = 24 V                   | t <sub>DOFF</sub>               | _          | _          | 12         | μs   |

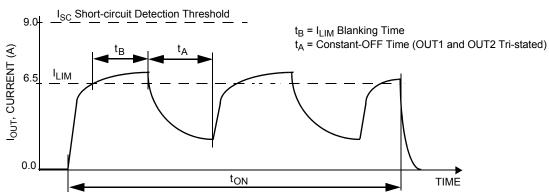

| I <sub>LIM</sub> Output Constant-OFF Time <sup>(23),(25)</sup>               | t <sub>A</sub>                  | 15         | 20.5       | 32         | μs   |

| I <sub>LIM</sub> Blanking Time <sup>(24),(25)</sup>                          | t <sub>B</sub>                  | 12         | 16.5       | 27         | μs   |

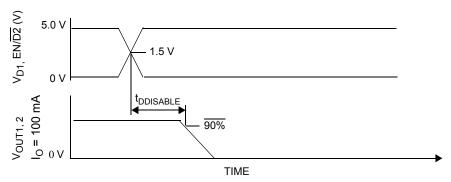

| Disable Delay Time <sup>(26)</sup>                                           | t <sub>DDISABLE</sub>           | -          | _          | 8.0        | μs   |

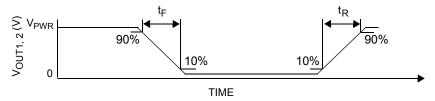

| Output Rise and Fall Time <sup>(27)</sup> • MC34932EK • MC34932SEK           | t <sub>F</sub> , t <sub>R</sub> | 1.9<br>0.2 | 3.9<br>1.1 | 8.0<br>1.5 | μs   |

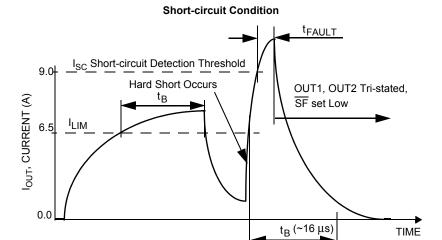

| Short-circuit/Overtemperature Turn-OFF (Latch-OFF) Time <sup>(28),(29)</sup> | t <sub>FAULT</sub>              | -          | _          | 8.0        | μs   |

| Power-ON Delay Time <sup>(29)</sup>                                          | t <sub>POD</sub>                | -          | 1.0        | 5.0        | ms   |

| Output MOSFET Body Diode Reverse Recovery Time <sup>(29)</sup>               | t <sub>RR</sub>                 | 75         | 100        | 150        | ns   |

| Charge Pump Operating Frequency <sup>(29)</sup>                              | f <sub>CP</sub>                 | -          | 7.0        | -          | MHz  |

#### Notes

- 20. The maximum PWM frequency should be limited to frequencies < 11 kHz for MC34932EK and < 20 kHz for MC34932SEK in order to allow the internal high-side driver circuitry time to fully enhance the high-side MOSFETs at a duty cycle range of 15 to 85%.

- 21. The internal current limit circuitry produces a constant-OFF-time Pulse Width Modulation of the output current. The output load's inductance, capacitance, and resistance characteristics affect the total switching period (OFF-time + ON-time), and thus the PWM frequency during current limit.

- 22. \* Output Delay is the time duration from 1.5 V on the IN1 or IN2 input signal to the 20% or 80% point (dependent on the transition direction) of the OUT1 or OUT2 signal. If the output is transitioning HIGH-to-LOW, the delay is from 1.5 V on the input signal to the 80% point of the output response signal. If the output is transitioning LOW-to-HIGH, the delay is from 1.5 V on the input signal to the 20% point of the output response signal. See Figure 4, page 10.

- 23. The time during which the internal constant-OFF time PWM current regulation circuit has tri-stated the output bridge.

- 24. The time during which the current regulation threshold is ignored so the short-circuit detection threshold comparators may have time to act.

- 25. Parameter guaranteed by characterization.

- 26. \* Disable Delay Time measurement is defined in Figure 5, page 10.

- 27. Rise Time is from the 10% to the 90% level and Fall Time is from the 90% to the 10% level of the output signal with  $V_{PWR}$  = 24 V,  $R_{LOAD}$  = 3.0 ohm. See Figure 6, page 10.

- 28. Load currents ramping up to the current regulation threshold become limited at the I<sub>LIM</sub> value (see Figure 7). The short-circuit currents possess a di/dt which ramps up to the I<sub>SCH</sub> or I<sub>SCL</sub> threshold during the I<sub>LIM</sub> blanking time, registering as a short-circuit event detection and causing the shutdown circuitry to force the output into an immediate tri-state latch-OFF (see Figure 8). Operation in Current Limit mode may cause junction temperatures to rise. Junction temperatures above ~160 °C causes the output current limit threshold to "fold back", or decrease, until ~175 °C is reached, after which the t<sub>LIM</sub> thermal latch-OFF occurs. Permissible operation within this fold back region is limited to non-repetitive transient events of duration not to exceed 30 seconds (see Figure 9).

- 29. Parameter is Guaranteed By Design.

# 4.4 Timing diagrams

Figure 4. Output delay time

Figure 5. Disable delay time

Figure 6. Output switching time

### **Overload Condition**

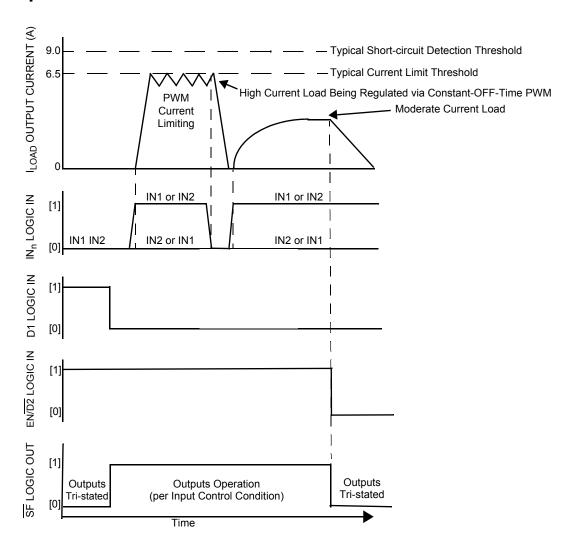

Figure 7. Current limit blanking time and constant-off time

Figure 8. Short-circuit detection turn-off time  $t_{\mbox{\scriptsize FAULT}}$

Figure 9. Output current limiting foldback region

# 5 Functional description

### 5.1 Introduction

The 34932 has two identical H-Bridge drivers in the same package. The only connection shared internally is the Analog Ground (AGND). This description is given for the H-Bridge A half of the total device. However, the H-Bridge B half exhibits identical behavior.

Numerous protection and operational features (speed, torque, direction, dynamic breaking, PWM control, and closed-loop control) make the 34932 a very attractive, cost-effective solution for controlling a broad range of small DC motors. The 34932 outputs are capable of supporting peak DC load currents of up to 5.0 A from a 36 V V<sub>PWR</sub> source. An internal charge pump and gate drive circuitry which can support external PWM frequencies up to 11 kHz in MC34932EK and 20 kHz in MC34932SEK.

The 34932 has an analog feedback (current mirror) output pin (the FB pin) which provides a constant-current source ratioed to the active high-side MOSFETs' current. This can be used to provide monitoring of output current to facilitate closed-loop operation for motor speed/torque control, or for the detection of open load conditions.

Two independent inputs, IN1 and IN2, provide control of the two totem-pole half-bridge outputs. Two independent disable inputs, D1 and  $EN/\overline{D2}$ , provide the means to force the H-bridge outputs to a high-impedance state (all H-bridge switches OFF). The  $EN/\overline{D2}$  pin also controls an enable function allowing the IC to be placed in a power-conserving Sleep mode.

The 34932 has output current limiting (via constant OFF-time PWM current regulation), output short-circuit detection with latch-OFF, and overtemperature detection with latch-OFF. Once the device is latched-OFF due to a fault condition, either of the disable inputs (D1 or EN/D2), or V<sub>PWR</sub> must be to clear the status flag.

Current limiting (Load Current Regulation) is accomplished by a constant-OFF time PWM method using current limit threshold triggering. The current limiting scheme is unique in that it incorporates a junction temperature-dependent current limit threshold. This means the current limit threshold is reduced to around 4.2 A as the junction temperature increases above 160 °C. When the temperature is above 175 °C, overtemperature shutdown (latch-OFF) occurs. This combination of features allows the device to continue operating for short periods of time (< 30 seconds) with unexpected loads, while still retaining adequate protection for both the device and the load.

## 5.2 Functional pin description

### 5.2.1 Power ground and analog ground (PGND and AGND)

The power and analog ground pins should be connected together with a very low-impedance connection.

# 5.2.2 Positive power supply (VPWR)

VPWR pins are the power supply inputs to the device. All VPWR pins must be connected together on the printed circuit board with as short as possible traces, offering as low an impedance as possible between pins.

# 5.2.3 Status flag ( $\overline{SF}$ )

This pin is the device fault status output. This output is an active LOW open drain structure requiring a pull-up resistor to  $V_{DD}$ . The maximum  $V_{DD}$  is < 7.0 V. Refer to Table 6 for the  $\overline{\text{SF}}$  Output status definition.

# 5.2.4 Input 1, 2 and disable input 1 (IN1, IN2, and D1)

These pins are input control pins used to control the outputs. These pins are 3.0 V/5.0 V CMOS-compatible inputs with hysteresis. IN1 and IN2 independently control OUT1 and OUT2, respectively. D1 input is used to tri-state disable the H-Bridge outputs.

When D1 is SET (D1 = logic HIGH) in the disable state, outputs OUT1 and OUT2 are both tri-state disabled; however, the rest of the device circuitry is fully operational and the supply I<sub>PWR(STANDBY)</sub> current is reduced to a few mA. Refer to Table 4.

# 5.2.5 H-Bridge output (OUT1, OUT2)

These pins are the outputs of the H-bridge with integrated free-wheeling diodes. The bridge output is controlled using the IN1, IN2, D1, and  $EN/\overline{D2}$  inputs. The outputs have PWM current limiting above the  $I_{LIM}$  threshold. The outputs also have thermal shutdown (tri-state latch-OFF) with hysteresis as well as short circuit latch-OFF protection.

A disable timer (time  $t_B$ ) is incorporated to distinguish between load currents higher than the  $I_{LIM}$  threshold and short circuit currents. This timer is activated at each output transition.

### 5.2.6 Charge pump capacitor (CCP)

This pin is the charge pump output pin and connection for the external charge pump reservoir capacitor. The allowable value is from 30 to 100 nF. This capacitor must be connected from the CCP pin to the VPWR pin. The device cannot operate properly without the external reservoir capacitor.

# 5.2.7 Enable input/disable input 2 (EN/ $\overline{D2}$ )

The  $EN/\overline{D2}$  pin performs the same function as D1 pin, when it goes to a logic LOW the <u>outputs</u> are immediately tri-stated. It is also used to place the device in a Sleep mode so as to consume very low currents. When the  $EN/\overline{D2}$  pin voltage is a logic LOW state, the device is in the Sleep mode. The device is enabled and fully operational when the EN pin voltage is logic HIGH. An internal pull-down resistor maintains the device in Sleep mode in the event EN is driven through a high-impedance I/O or an unpowered microcontroller, or the EN/ $\overline{D2}$  input becomes disconnected.

### 5.2.8 Feedback (FB)

The 34932 has a feedback output (FB) for monitoring of H-Bridge high-side output currents to facilitate closed-loop operation for motor speed and torque control.

The FB pin provides current sensing feedback of the H-Bridge high-side drivers. When running in the forward or reverse direction, a ground-referenced 0.24% of load current is output to this pin. Through the use of an external resistor to ground, the proportional feedback current can be converted to a proportional voltage equivalent and the controlling microcontroller can measure the current proportional voltage with its analog-to-digital converter (ADC). This is intended to provide the user with only first-order motor current feedback for motor torque control. The resistance range for the linear operation of the FB pin is  $100 \Omega < R_{FB} < 300 \Omega$ .

If PWM-ing is implemented using the disable pin input (only D1), a small filter capacitor ( $\sim$ 1.0  $\mu$ F) may be required in parallel with the R<sub>FB</sub> resistor to ground for spike suppression.

## 5.3 Functional internal block description

Figure 10. Functional internal block diagram

## 5.3.1 Analog control and protection circuitry

An on-chip voltage regulator supplies the internal logic. The charge pump provides gate drive for the H-Bridge MOSFETs. The Current and Temperature sense circuitry provides detection and protection for the output drivers. Output undervoltage protection shuts down the MOSFETS.

## 5.3.2 Gate control logic

The 34932 is a monolithic H-Bridge Power IC designed primarily for any low-voltage DC servo motor control application within the current and voltage limits stated for the device. Two independent inputs provide polarity control of two half-bridge totem-pole outputs. Two independent disable inputs are provided to force the H-Bridge outputs to tri-state (high-impedance off-state).

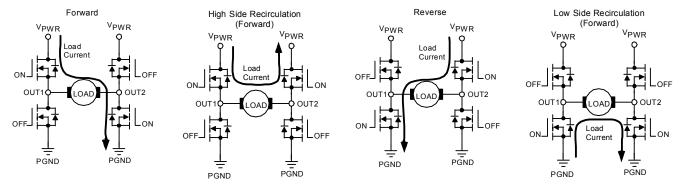

### 5.3.3 H-Bridge output drivers: OUT1 and OUT2

The H-Bridge is the power output stage. The current flow from OUT1 to OUT2 is reversible and under full control of the user by way of the Input Control Logic. The output stage is designed to produce full load control under all system conditions. All protective and control features are integrated into the control and protection blocks. The sensors for current and temperature are integrated directly into the output MOSFET for maximum accuracy and dependability.

# 6 Functional device operation

# 6.1 Operational modes

Figure 11. Operating states

# 6.2 Logic commands

### Table 6. Truth table

The tri-state conditions and the status flag are reset using D1 or  $\overline{D2}$ . The truth table uses the following notations: L = LOW, H = HIGH, X = HIGH or LOW, and Z = High-impedance. All output power transistors are switched off.

| Doubles extern |       | Input co | nditions | Status | Out | puts |      |

|----------------|-------|----------|----------|--------|-----|------|------|

| Device state   | EN/D2 | D1       | IN1      | IN2    | SF  | OUT1 | OUT2 |

| Forward        | Н     | L        | Н        | L      | Н   | Н    | L    |

| Reverse        | Н     | L        | L        | Н      | Н   | L    | Н    |

#### Table 6. Truth table

The tri-state conditions and the status flag are reset using D1 or  $\overline{D2}$ . The truth table uses the following notations: L = LOW, H = HIGH, X = HIGH or LOW, and Z = High-impedance. All output power transistors are switched off.

| Bustonestate                         |       | Input co | nditions |     | Status | Out  | puts |

|--------------------------------------|-------|----------|----------|-----|--------|------|------|

| Device state                         | EN/D2 | D1       | IN1      | IN2 | SF     | OUT1 | OUT2 |

| Freewheeling Low                     | Н     | L        | L        | L   | Н      | L    | L    |

| Freewheeling High                    | Н     | L        | Н        | Н   | Н      | Н    | Н    |

| Disable 1 (D1)                       | Н     | Н        | х        | х   | L      | Z    | Z    |

| IN1 Disconnected                     | Н     | L        | Z        | х   | Н      | Н    | Х    |

| IN2 Disconnected                     | Н     | L        | х        | Z   | Н      | х    | Н    |

| D1 Disconnected                      | Н     | Z        | х        | х   | L      | Z    | Z    |

| Undervoltage Lockout <sup>(30)</sup> | Н     | Х        | Х        | Х   | L      | Z    | Z    |

| Overtemperature <sup>(31)</sup>      | Н     | х        | х        | х   | L      | Z    | Z    |

| Short-circuit <sup>(31)</sup>        | Н     | Х        | Х        | Х   | L      | Z    | Z    |

| Sleep mode EN/D2                     | L     | Х        | х        | х   | Н      | Z    | Z    |

| EN/D2 disconnected                   | Z     | Х        | х        | х   | Н      | Z    | Z    |

#### Notes

- 30. In the event of an undervoltage condition, the outputs tri-state and status flag is SET logic LOW. Upon undervoltage recovery, status flag is reset automatically or automatically cleared and the outputs are restored to their original operating condition.

- 31. When a short-circuit or overtemperature condition is detected, the power outputs are tri-state latched-OFF independent of the input signals and the status flag is latched to logic LOW. To reset from this condition requires the toggling of either D1, EN/D2, or V<sub>PWR</sub>.

Figure 12. 34932 power stage operation

## 6.3 Protection and diagnostic features

# 6.3.1 Short-circuit protection

If an output short-circuit condition is detected, the power outputs tri-state (latch-OFF) independent of the input (IN1 and IN2) states, and the fault status output flag  $(\overline{SF})$  is SET to logic LOW. If the D1 input changes from logic HIGH to logic LOW, or if the EN/D2 input changes from logic LOW to logic HIGH, the output bridge becomes operational again and the fault status flag resets (cleared) to a logic HIGH state.

The output stage always switches into the mode defined by the input pins (IN1, IN2, D1, and  $EN/\overline{D2}$ ), provided the device junction temperature is within the specified operating temperature range.

### 6.3.2 Internal PWM current limiting

The maximum current flow under normal operating conditions should be less than 5.0 A. The instantaneous load currents is limited to  $I_{LIM}$  via the internal PWM current limiting circuitry. When the  $I_{LIM}$  threshold current value is reached, the output stages are tri-stated for a fixed time ( $T_A$ ) of 20  $\mu$ s typical. Depending on the time constant associated with the load characteristics, the output current decreases during the tri-state duration until the next output ON cycle occurs.

The PWM current limit threshold value is dependent on the device junction temperature. When -40 °C <  $T_J$  <160 °C,  $I_{LIM}$  is between the specified minimum/maximum values. When  $T_J$  exceeds 160 °C, the  $I_{LIM}$  threshold decreases to 4.2 A. Shortly above 175 °C the device overtemperature circuit detects  $t_{LIM}$  and an overtemperature shutdown occurs. This feature implements a graceful degradation of operation before thermal shutdown occurs, thus allowing for intermittent unexpected mechanical loads on the motor's gear-reduction train to be handled.

#### Important:

Die temperature excursions above 150 °C are permitted only for non-repetitive durations <30 seconds. Provision must be made at the system level to prevent prolonged operation in the current-foldback region.

### 6.3.3 Overtemperature shutdown and hysteresis

If an overtemperature condition occurs, the power outputs are tri-stated (latched-OFF) and the fault status flag  $(\overline{SF})$  is SET to logic LOW. To reset from this condition, D1 must change from logic HIGH to logic LOW, or EN/ $\overline{D2}$  must change from logic LOW to logic HIGH. When reset, the output stage switches ON again, provided the temperature is below the overtemperature threshold limit, EN/D2 clears the fault. When the junction temperature is below the overtemperature threshold limit minus the hysteresis, D1 clears the fault.

#### Important:

Resetting from the fault condition clears the fault status flag. Powering down and powering up the device also resets the 34932 from the fault condition.

### 6.3.4 Output avalanche protection

If VPWR were to become an open circuit, the outputs would likely tri-state simultaneously due to the disable logic. This could result in an unclamped inductive discharge. The VPWR input to the 34932 should not exceed 40 V during this transient condition, to prevent electrical overstress of the output drivers. This can be accomplished with a zener clamp or MOV, and/or an appropriately valued input capacitor with sufficiently low ESR (see Figure 13).

Figure 13. Avalanche protection

# 7 Typical applications

### 7.1 Introduction

A typical application schematic is shown in Figure 14. For precision high-current applications in harsh, noisy environments, the V<sub>PWR</sub> bypass capacitor may need to be substantially larger.

Figure 14. 34932 typical application schematic 1/2 device

# 8 Packaging

# 8.1 Package dimensions

For the most current package revision, visit www.nxp.com and perform a keyword search using the 98Axxxxxxxxx listed below. Dimensions shown are provided for reference ONLY.

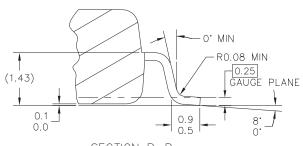

SECTION B-B

| NXP SEMICONDUCTORS N. V. ALL RIGHTS RESERVED | MECHANICAL OU                                               | TLINE   | PRINT    | VERSION   | NOT TO S | CALE |

|----------------------------------------------|-------------------------------------------------------------|---------|----------|-----------|----------|------|

| TITLE:                                       | A 418 1 A 1                                                 | DOCUMEN | NT NO: 9 | 8ASA99334 | D RE     | V: F |

| / '                                          | SOIC W/B, 54 TERMINAL,<br>0.65 PITCH, 4.6 X 6.4 EXPOSED PAD |         |          |           |          |      |

| 0.03 111611, 4.0 % 0.4 E                     | NI OSLO I AD                                                | S0T1747 | 7-4      |           | 18 JAN   | 2016 |

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS B AND C TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.46 mm. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 mm.

- A EXACT SHAPE OF EACH CORNER IS OPTIONAL.

- THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 mm AND 0.3 mm FROM THE LEAD TIP.

- THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM. THIS DIMENSION IS DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTER-LEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

- THESE DIMENSION RANGES DEFINE THE PRIMARY KEEP-OUT AREA. MOLD LOCKING AND RESIN BLEED CONTROL FEATURES MAY BE VISIBLE, AND THEY MAY EXTEND TO 0.5mm FROM MAXIMUM EXPOSED PAD SIZE.

| © NXP SEMICONDUCTORS N. V.<br>ALL RIGHTS RESERVED | MECHANICAL OU | TLINE   | PRINT VERSION     | NOT TO SCALE |

|---------------------------------------------------|---------------|---------|-------------------|--------------|

| TITLE:                                            | N (1N 1 A 1   | DOCUMEN | NT NO: 98ASA99334 | D REV: F     |

| SOIC W/B, 54 TER<br>0.65 PITCH, 4.6 X 6.4 E       |               | STANDAF | RD: NON-JEDEC     |              |

| 0.03                                              | NI OSLD I AD  | S0T1747 | 7-4               | 18 JAN 2016  |

NXP Semiconductors 21

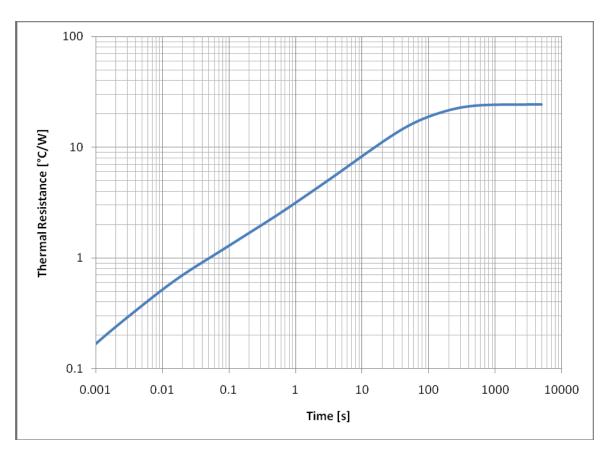

## 9 Thermal addendum

### 9.1 Introduction

This thermal addendum is provided as a supplement to the MC34932 technical datasheet. The addendum provides thermal performance information critical in the design and development of system applications. All electrical, application, and packaging information is provided in the datasheet.

## 9.2 Package and thermal considerations

The MC34932 is offered in a 54-pin SOICW-EP. There is a single heat source (P), a single junction temperature ( $T_J$ ), and thermal resistance ( $R_{\theta,IA}$ ).

$$\{T_J\} = [R_{\theta JA}] \cdot \{P\}$$

The stated values are solely for a thermal performance comparison of one package to another in a standardized environment. This methodology is not meant to, and does not predict the performance of a package in an application-specific environment. Stated values were obtained by measurement and simulation according to the standards listed below.

Table 7. Table of thermal resistance data

| Rating                                    |                         |                           | Value | Unit | Notes     |

|-------------------------------------------|-------------------------|---------------------------|-------|------|-----------|

| Junction to Ambient<br>Natural Convection | Single Layer board (1s) | $R_{	heta JA}$            | 58.8  | °C/W | (32),(33) |

| Junction to Ambient<br>Natural Convection | Four layer board (2s2p) | $R_{	heta JA}$            | 24.4  | °C/W | (32),(34) |

| Junction to Board                         |                         | $R_{	heta JB}$            | 7.0   | °C/W | (35)      |

| Junction to Case (bottom / flag)          |                         | R <sub>θJC</sub> (bottom) | 0.36  | °C/W | (38)      |

| Junction to Case (top)                    |                         | R <sub>θJC</sub> (top)    | 18.0  | °C/W | (36)      |

| Junction to Package Top                   | Natural Convection      | $\Psi_{JT}$               | 2.0   | °C/W | (37)      |

#### Notes

- 32. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 33. Per JEDEC JESD51-2 with the single layer board (JESD51-3) horizontal.

- 34. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- 35. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 36. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 37. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 38. Thermal resistance between the die and the case bottom/flag surface (simulated) (flag bottom side fixed to ambient temperature).

Figure 15. Transient thermal resistance  $R_{\theta JA}\,MC34932EK$  on 2s2p test board

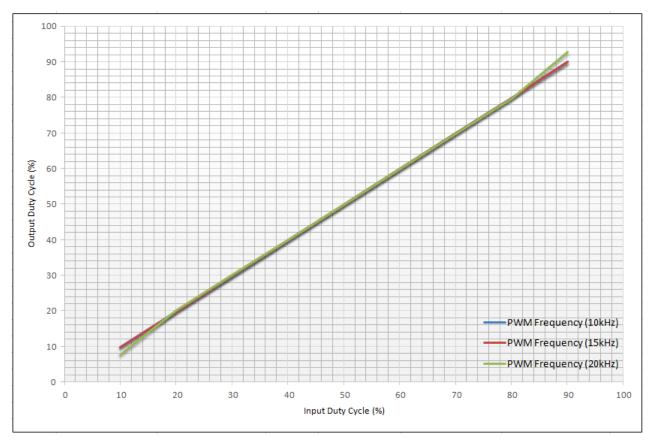

Figure 16. Typical duty cycle linearity over frequency at 36 V for MC34932SEK

Operating the part continuously at more than 24 V and up to 36 V while switching the outputs at high frequencies causes additional power dissipation on the die due to high switching losses. This could result in junction temperature  $(T_J)$  exceeding the thermal foldback temperature  $(T_{FB})$  and even thermal shutdown  $(T_{LIM})$  threshold. Hence, while operating the part at such conditions, it is important to consider methods to keep the junction temperature  $(T_J)$  below 165 °C to prevent the part exceeding the thermal foldback temperature threshold  $(T_{FB})$  and limit the current internally.

# 10 Reference section

Table 8. Thermal analysis reference documents

| Reference      | Reference Description                                                         |  |

|----------------|-------------------------------------------------------------------------------|--|

| AN4146         | Thermal Modeling and Simulation of 12V Gen3 eXtreme Switch Devices with SPICE |  |

| BASICTHERMALWP | Basic Principles of Thermal Analysis for Semiconductor Systems                |  |

# 11 Revision history

| Revision | Date    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 7/2013  | Initial Release based the 33932 Data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.0      | 10/2013 | Reduced the sleep mode current specifications                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.0      | 2/2015  | <ul> <li>Updated as per PCN # 16555</li> <li>Added new part number MC34931SEK with higher slew rate to support PWM frequency up to 20 kHz</li> <li>Updated the operating voltage up to 36 V (max.) after characterization and testing</li> <li>Changed the rise/fall time, sleep current, output leakage current, sleep and stand-by current based on test and characterization data</li> <li>Added performance curves of key parameters to show operation up to 36 V</li> </ul> |

| 4.0      | 9/2015  | <ul> <li>Changed the document classification from Advance Information to Technical Data</li> <li>Added a column for PWM frequency to Table 1</li> </ul>                                                                                                                                                                                                                                                                                                                          |

|          | 8/2016  | Updated to NXP document form and style                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### How to Reach Us:

Home Page: NXP.com

Web Support:

http://www.nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no expressed or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation, consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by the customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address:

http://www.nxp.com/terms-of-use.html.

NXP, the NXP logo, Freescale, the Freescale logo and SMARTMOS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. All rights reserved.

© 2016 NXP B.V.

Document Number: MC34932

Rev. 4.0 8/2016