## **PRM**<sup>™</sup> Regulator

## **High Efficiency Converter**

#### **Features**

- 48.0 V input (38.0 V to 55.0 V), non-isolated ZVS buck-boost regulator

- 20.0 V to 55.0 V adjustable output range

- 500 W output power in 1.11 in<sup>2</sup> footprint

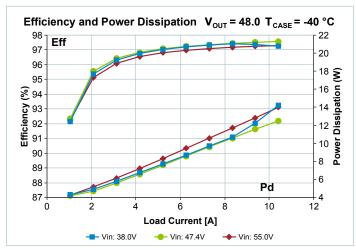

- · 97.8% typical efficiency, at full load

- 1729 W/in3 (106 W/cm3) Power Density

- 4.01 MHrs MTBF (MIL-HDBK-217 Plus Parts Count)

- Pin selectable operating mode

- Adaptive Loop

- Remote Sense / Slave

- Full VI Chip® Package

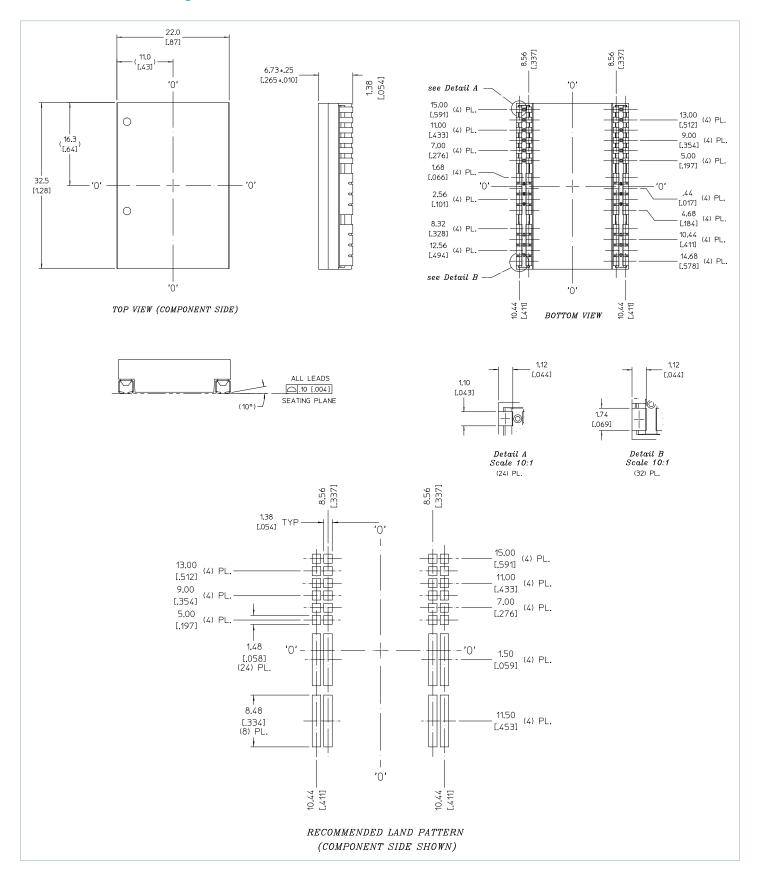

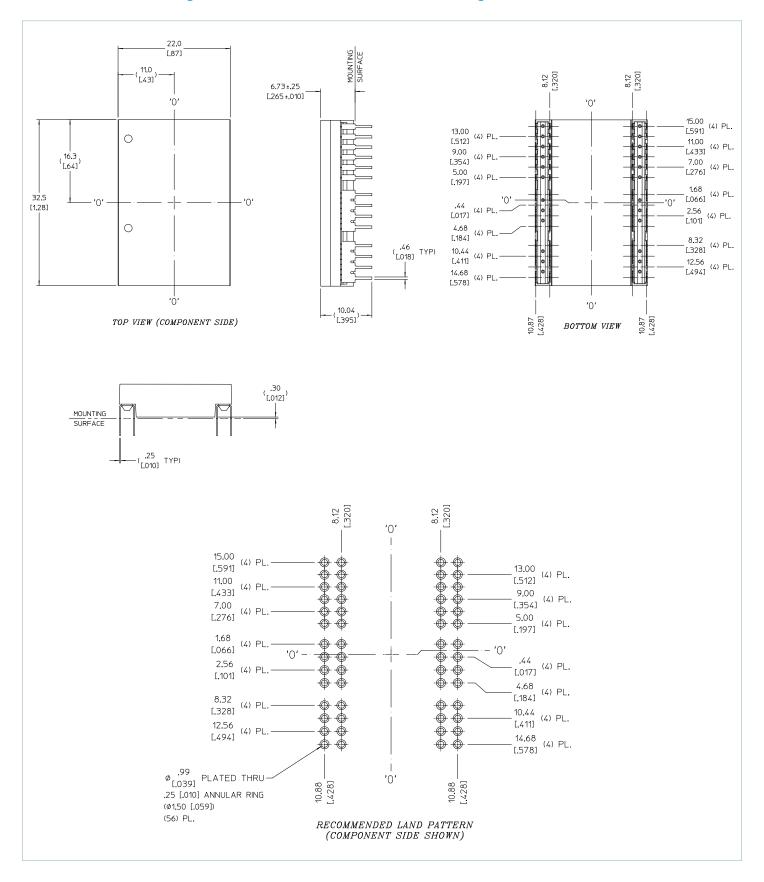

- 32.5mm x 22.0mm x 6.73mm

### **Typical Applications**

- High Density Power Supply DC-DC rail outputs

- · High Density ATE system DC-DC power

- Telecom NPU and ASIC core power

- Communications Systems

- Non-isolated and isolated power converters

| Product Ratings                                      |                            |  |  |  |  |  |

|------------------------------------------------------|----------------------------|--|--|--|--|--|

| $V_{IN} = 38.0 \text{ V to } 55.0 \text{ V}$         | P <sub>OUT</sub> = 500 W   |  |  |  |  |  |

| V <sub>OUT</sub> = 48.0 V<br>(20.0 V to 55.0 V Trim) | I <sub>OUT</sub> = 10.42 A |  |  |  |  |  |

#### **Product Description**

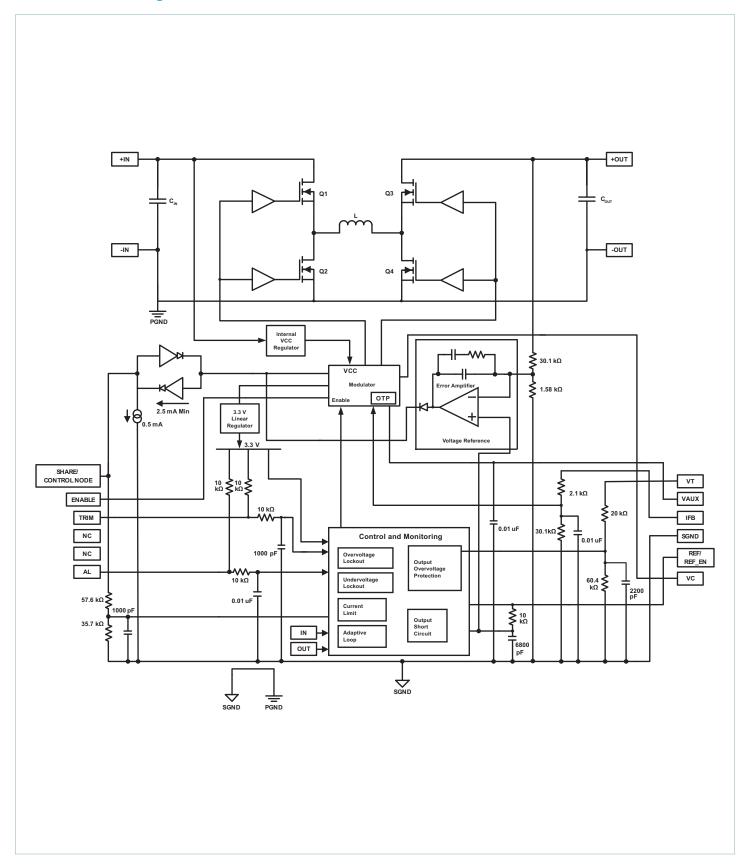

The VI Chip® PRM™ Regulator is high efficiency converter, operating from a 38.0 to 55.0 Vdc input to generate a regulated 20.0 to 55.0 Vdc output. The ZVS buck-boost topology enables high switching frequency (~1.03 MHz) operation with high conversion efficiency. High switching frequency reduces the size of reactive components enabling power density up to 1729 W/in³.

The Full VI Chip® package is compatible with standard pickand-place and surface mount assembly processes with a planar thermal interface area and superior thermal conductivity.

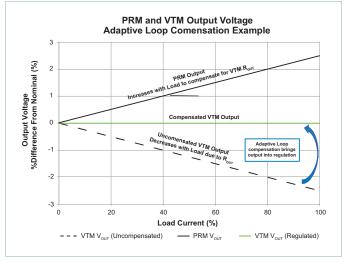

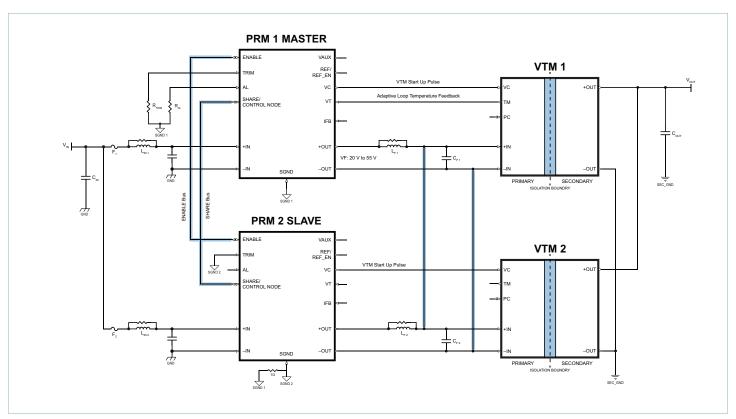

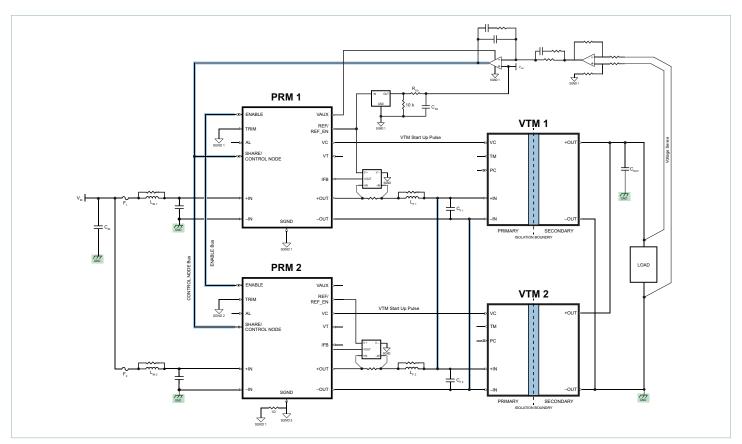

In a Factorized Power Architecture™ system, the PRM and downstream VTM™ current multiplier minimize distribution and conversion losses in a high power solution, providing an isolated, regulated output voltage.

The PRM48By480x500A00 has two selectable modes of regulation depending on the application requirements.

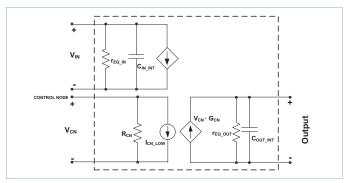

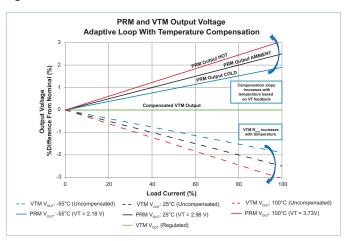

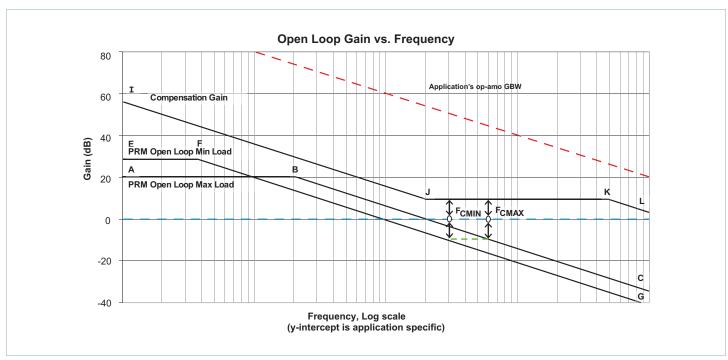

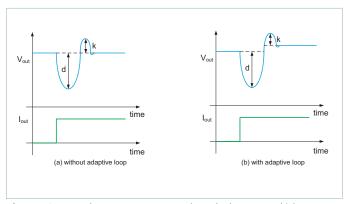

In Adaptive Loop Operation, the PRM48By480x500A00 utilizes a unique feed-forward scheme that enables precise regulation of an isolated POL voltage without the need for remote sensing and voltage feedback.

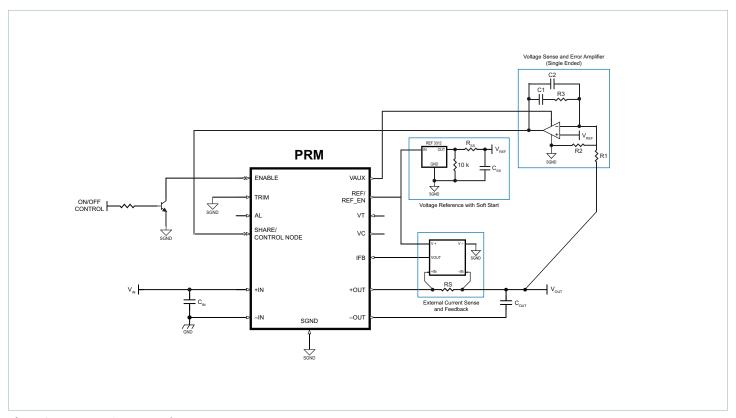

In Remote Sense Operation, the internal regulation circuitry is disabled, and an external control loop and current sensor maintain regulation. This affords flexibility in the design of both voltage and current compensation loops to optimize performance in the end application.

## **Typical Applications**

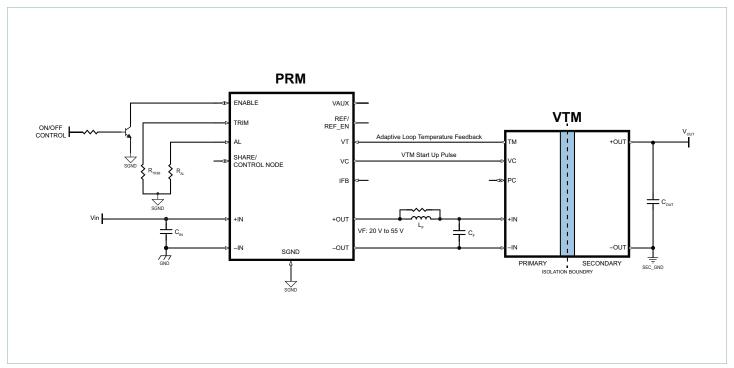

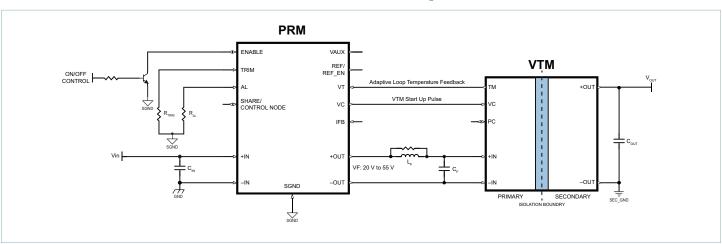

Typical Application: PRM48By480x500A00 + VTM Adaptive Loop Configuration

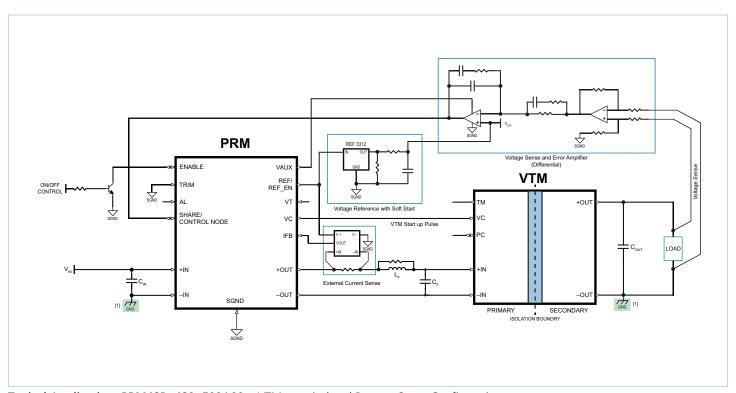

Typical Application: PRM48By480x500A00 + VTM, non-isolated Remote Sense Configuration

$<sup>^{[1]}</sup>$  Non-Isolated Configuration: -Out connected to -IN

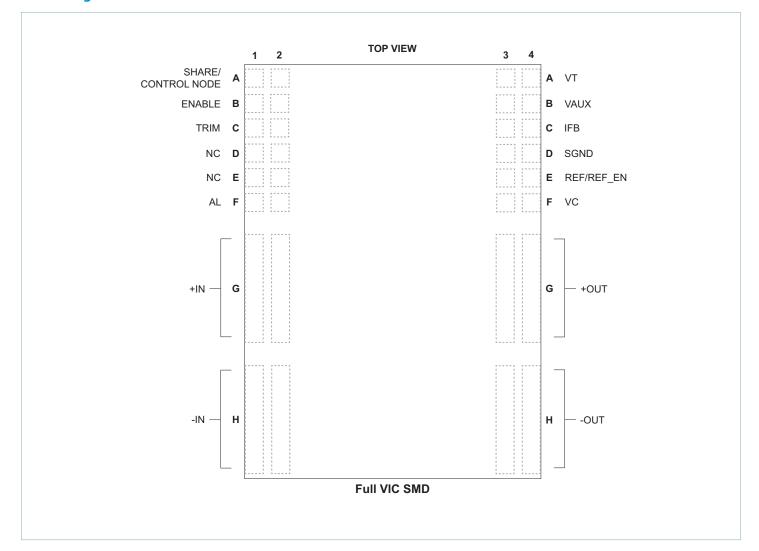

## **Pin Configuration**

## **Pin Descriptions**

| Pin<br>Number | Signal Name                                | Туре                   | Function                                                                                                                                                 |

|---------------|--------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2        | SHARE<br>(Adaptive Loop / Slave Operation) | BIDIR                  | Parallel sharing control bus for master-slave configuration.                                                                                             |

| AT, AZ        | CONTROL NODE<br>(Remote Sense Operation)   | INPUT                  | Modulator control node input. Driven by external error amplifier in Remote Sense Operation.                                                              |

| A3, A4        | VT<br>(Adaptive Loop Operation)            | INPUT                  | VTM TM input for temperature compensation. Leave disconnected for Remote Sense Operation.                                                                |

| B1, B2        | ENABLE                                     | BIDIR                  | Enables power supply when allowed to float high. 5 V during normal operation.                                                                            |

| B3, B4        | VAUX                                       | OUTPUT                 | 9 V auxiliary bias voltage.                                                                                                                              |

| C1, C2        | TRIM                                       | INPUT                  | Selects operating mode. Adjusts output voltage in Adaptive Loop Operation.                                                                               |

| C3, C4        | IFB<br>(Remote Sense Operation)            | INPUT                  | Current sense input for current limit and overcurrent protection in Remote Sense Operation.<br>Leave disconnected for Adaptive Loop Operation.           |

| D1, D2        | NC                                         | n/a                    | Do not connect this pin.                                                                                                                                 |

| D3, D4        | SGND                                       | INPUT                  | Signal ground, reference for analog controls. Kelvin connected internally to –IN and –OUT.                                                               |

| E1, E2        | NC                                         | n/a                    | Do not connect this pin.                                                                                                                                 |

| E3, E4        | REF<br>(Adaptive Loop Operation)           | OUTPUT                 | Reference voltage for internal error amplifier in Adaptive Loop Operation.                                                                               |

| E3, E4        | REF_EN<br>(Remote Sense Operation)         | OUTPUT                 | Powers and enables external control circuit voltage reference in Remote Sense Operation.                                                                 |

| F1, F2        | AL (Adaptive Loop Operation)               | INPUT                  | Adaptive loop gain control. Sets the magnitude of the Adaptive Loop load line in Adaptive Loop Operation. Leave disconnected for Remote Sense Operation. |

| F3, F4        | VC                                         | OUTPUT                 | Bias voltage to power VTM module during start up                                                                                                         |

| G1,G2         | +IN                                        | INPUT<br>POWER         | Positive input power terminal                                                                                                                            |

| G3,G4         | +OUT                                       | OUTPUT<br>POWER        | Positive output power terminal                                                                                                                           |

| H1,H2         | -IN                                        | INPUT<br>POWER RETURN  | Negative input power terminal. Connected internally to -OUT.                                                                                             |

| H3,H4         | -OUT                                       | OUTPUT<br>POWER RETURN | Negative output power terminal. Connected internally to -IN.                                                                                             |

## **Part Ordering Information**

| Device    | Input Voltage<br>Range | Package Type                        | Output Voltage x 10 | Temperature Grade                    | Output Power | Revision | Version      |

|-----------|------------------------|-------------------------------------|---------------------|--------------------------------------|--------------|----------|--------------|

| PRM       | 48B                    | F                                   | 480                 | Т                                    | 500          | А        | 00           |

| PRM = PRM | 48B = 38.0 V - 55.0 V  | F = Full VIC SMD<br>T = Full VIC TH | 480 = 48.0 V        | T = -40 to 125°C<br>M = -55 to 125°C | 500 = 500 W  | А        | 00 = AL / RS |

## **Standard Models**

| Part Number                         | V <sub>IN</sub> | Package Type          | V <sub>OUT</sub>             | Temperature  | Power            | Version          |  |

|-------------------------------------|-----------------|-----------------------|------------------------------|--------------|------------------|------------------|--|

| PRM48B <b>F</b> 480 <b>T</b> 500A00 | 38.0 V - 55.0 V | Full VIC              | 48.0 V<br>(20.0 V to 55.0 V) | -40 to 125°C | 500 W            | AL / RS          |  |

| PRM48B <b>F</b> 480 <b>M</b> 500A00 |                 | SMD                   |                              | -55 to 125°C |                  | (Pin Selectable) |  |

| PRM48B <b>T</b> 480 <b>T</b> 500A00 | 38.0 V - 55.0 V | Full VIC              | 48.0 V                       | -40 to 125°C | 500 W            | AL / RS          |  |

| PRM48B <b>T</b> 480 <b>M</b> 500A00 | 36.0 V - 33.0 V | TH (20.0 V to 55.0 V) | -55 to 125°C                 | 300 W        | (Pin Selectable) |                  |  |

## **Absolute Maximum Ratings**

The ABSOLUTE MAXIMUM ratings below are stress ratings only. Operation at or beyond these maximum ratings can cause permanent damage to device. Electrical specifications do not apply when operating beyond rated operating conditions. Operating beyond rated operating conditions for extended period of time may affect device reliability. All voltages are specified relative to SGND unless otherwise noted. Positive pin current represents current flowing out of the pin.

| Parameter                                                                      | Comments                         | Min  | Max    | Unit |

|--------------------------------------------------------------------------------|----------------------------------|------|--------|------|

| CHARE / CONTROL NORE                                                           |                                  | -0.3 | 10.5   | V    |

| SHARE / CONTROL NODE                                                           |                                  |      | +/-10  | mA   |

| NABLE  N to -IN  AUX  GND  B  EF / REF _EN  RIM  L  T  C to -OUT               |                                  | -0.3 | 5.5    | V    |

| ENABLE                                                                         |                                  |      | +/-10  | mA   |

| INI to INI                                                                     | Continuous, non-operating        | -1   | 80     | V    |

| EF / REF _EN  RIM AL TT C to -OUT OUT to -OUT Output Current nternal Operating | 100 ms, non-Operating            |      | 100    | V    |

| VALIV                                                                          |                                  | -0.5 | 10.5   | V    |

| VAUX                                                                           |                                  |      | +/-100 | mA   |

| SGND                                                                           |                                  |      | +/-100 | mA   |

| IFB                                                                            |                                  | -0.5 | 5.7    | V    |

|                                                                                |                                  | -0.3 | 3.6    | V    |

| REF / REF _EN                                                                  | Remote Sense Operation (REF _EN) |      | 10     | mA   |

| _                                                                              | Adaptive Loop Operation (REF)    |      | 3.4    | mA   |

| TRIM                                                                           |                                  | -0.3 | 3.6    | V    |

| AL                                                                             |                                  | -0.3 | 3.6    | V    |

| VT                                                                             |                                  | -0.3 | 4.8    | V    |

| VC to OUT                                                                      |                                  | -0.5 | 18     | V    |

| VC to =001                                                                     |                                  |      | +/-1.8 | А    |

| +OUT to -OUT                                                                   |                                  | -1   | 62     | V    |

| Output Current                                                                 |                                  |      | 14.5   | А    |

| Internal Operating                                                             | T Grade                          | -40  | 125    | °C   |

| Temperature                                                                    | M Grade                          | -55  | 125    | °C   |

| Storage                                                                        | T Grade                          | -40  | 125    | °C   |

| Temperature                                                                    | M Grade                          | -65  | 125    | °C   |

## **Electrical Specifications**

Specifications apply over all line and load conditions, and trim from 20.0 V to 55.0 V, unless otherwise noted; **Boldface** specifications apply over the temperature range of -40°C < T<sub>INT</sub> < 125°C; All Other specifications are at T<sub>INT</sub> = 25°C unless otherwise noted.

| Attribute Symbol                  |                          | Conditions / Notes                                                                                           |       | Тур  | Max   | Unit   |

|-----------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------|-------|------|-------|--------|

|                                   |                          | Power Input Specification                                                                                    |       |      |       |        |

| Input Voltage Range               | V <sub>IN</sub>          | Continuous, operating                                                                                        | 38.0  | 48.0 | 55.0  | V      |

| V <sub>IN</sub> Slew Rate         | dV <sub>IN</sub> /dt     | $0 \le V_{\text{IN}} \le 55.0 \text{ V}$                                                                     | 0.001 | 40.0 | 1000  | V/ms   |

| Initialization Voltage            | V <sub>INIT</sub>        | Internal micro controller initialization voltage                                                             | 0.001 | 10   | 1000  | V      |

| Initialization Delay              | t <sub>INIT</sub>        | From V <sub>IN</sub> first crossing V <sub>INIT</sub>                                                        | 5.0   | 7.0  | 9.0   | ms     |

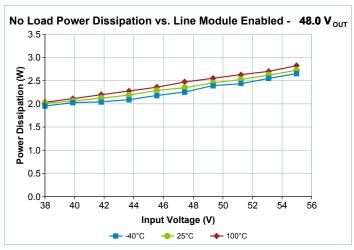

| No Load Power Dissipation         | P <sub>NL</sub>          | ENABLE HIGH, V <sub>IN</sub> = 48.0 V                                                                        |       | 2.4  | 3.5   | W      |

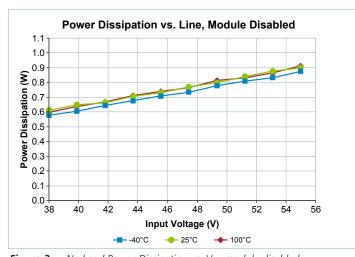

| Input Quiescent Current           | I <sub>QC</sub>          | ENABLE LOW, $V_{IN} = 48.0 \text{ V}$                                                                        |       | 14.5 | 20.0  | mA     |

| Input Current                     | I <sub>IN DC</sub>       | I <sub>OUT</sub> = 10.42 A, V <sub>IN</sub> = 48.0 V, V <sub>OUT</sub> = 48.0 V                              |       | 10.7 | 11.0  | А      |

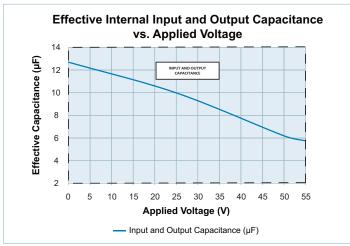

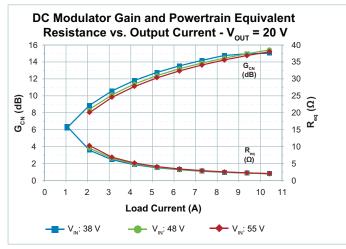

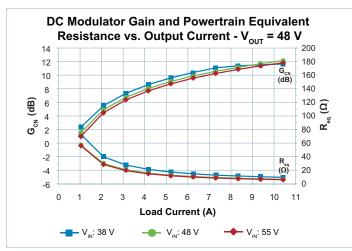

| Input Capacitance (Internal)      | C <sub>IN_INT</sub>      | Effective value, V <sub>IN</sub> = 48.0 V (see Fig. 13)                                                      |       | 6    |       | μF     |

| Input Capacitance (Internal) ESR  | R <sub>CIN</sub>         | Effective value, $V_{IN} = 48.0 \text{ V}$                                                                   |       | 1.5  |       | mΩ     |

|                                   |                          |                                                                                                              |       |      |       |        |

|                                   |                          | Power Output Specification                                                                                   |       |      |       | I      |

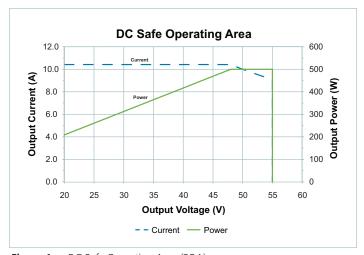

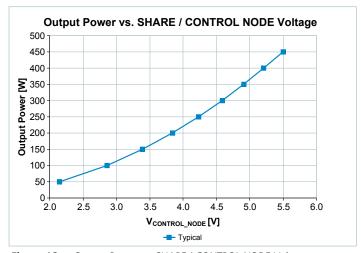

| Rated Output Current              | I <sub>OUT</sub>         | Standalone and Master Operation, see Figure 1, SOA                                                           |       |      | 10.42 | А      |

| Rated Output Power                | P <sub>OUT</sub>         | Standalone and Master Operation, see Figure 1, SOA                                                           |       |      | 500   | W      |

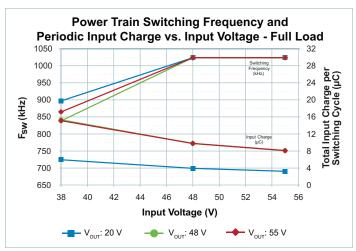

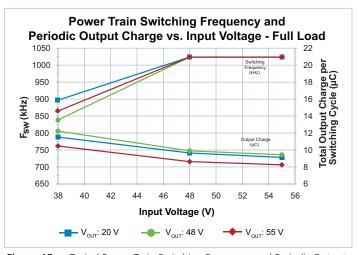

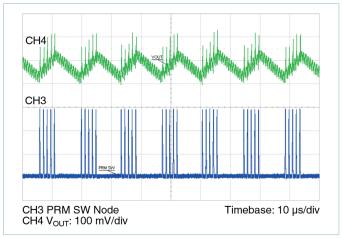

|                                   |                          | $V_{IN} = 48.0 \text{ V } V_{OUT} = 48.0 \text{ V},$                                                         | 0.94  | 1.03 | 1.07  | MHz    |

| Switching Frequency               | F <sub>SW</sub>          | $I_{OUT} = 5.21 \text{ A, } T_{INT} = 25^{\circ}\text{C}$                                                    | 0.54  | 1.05 | 1.07  | IVIIIZ |

|                                   | . 344                    | Over line, load, trim and temperature,                                                                       | 0.70  |      | 1.07  | MHz    |

|                                   |                          | exclusive of burst mode                                                                                      | 0.70  |      | 1.07  | 171112 |

|                                   |                          | From V <sub>IN</sub> first crossing V <sub>IN_UVLO+_SUPV</sub>                                               |       | 20   |       | μs     |

| Output Turn-ON Delay              | t <sub>ON</sub>          | to ENABLE high; t <sub>INIT</sub> expired                                                                    |       |      |       |        |

|                                   |                          | From ENABLE pin release to ENABLE high, $V_{\text{IN}}$ applied, $t_{\text{OFF}}$ expired                    |       | 20   |       | μs     |

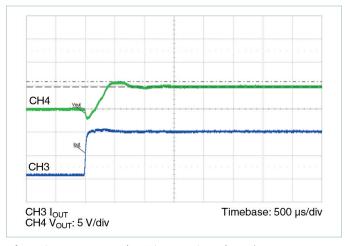

| Start up Sequence Timeout         | t <sub>STARTUP_SEQ</sub> | From ENABLE high to start up sequence complete                                                               |       | 17   |       | ms     |

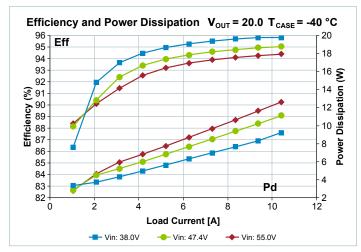

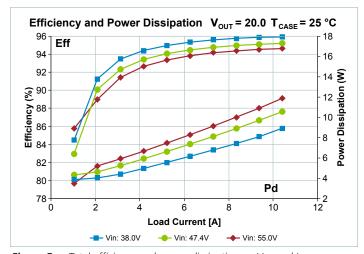

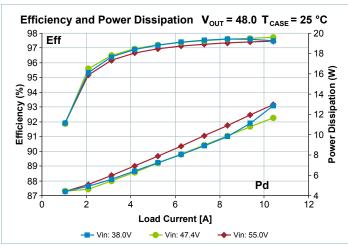

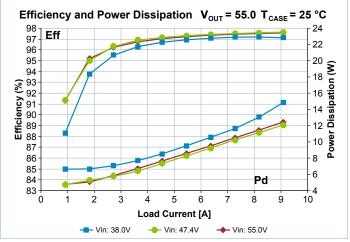

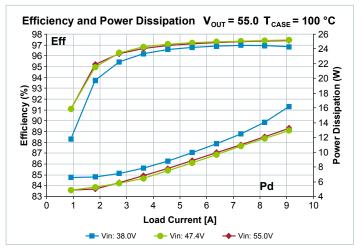

|                                   |                          | $V_{IN} = 48.0 \text{ V}, V_{OUT} = 48.0 \text{ V}, I_{OUT} = 10.42 \text{ A}, T_{INT} = 25^{\circ}\text{C}$ | 96.3  | 97.8 |       | %      |

|                                   |                          | $V_{IN} = 48.0 \text{ V}, V_{OUT} = 48.0 \text{ V}, I_{OUT} = 5.21 \text{ A}, T_{INT} = 25^{\circ}\text{C}$  | 96.0  | 97.3 |       | %      |

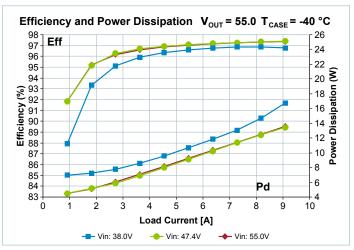

| Efficiency Ambient                | $\eta_{AMB}$             | $V_{IN} = 38.0 \text{ V to } 55.0 \text{ V},$                                                                |       |      |       | 0/     |

|                                   |                          | $V_{OUT} = 48.0 \text{ V}, I_{OUT} = 10.42 \text{ A}, T_{INT} = 25^{\circ}\text{C}$                          |       |      |       | %      |

|                                   |                          | V <sub>IN</sub> = 38.0 V to 55.0 V,                                                                          |       |      |       | %      |

|                                   |                          | $I_{OUT} = 10.42 \text{ A}, T_{INT} = 25^{\circ}\text{C}, \text{ over trim}$                                 | 93.5  |      |       | 70     |

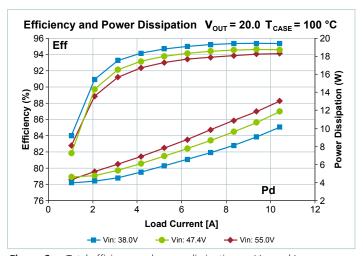

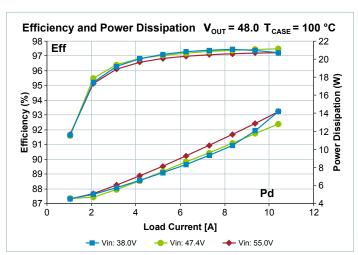

|                                   |                          | $V_{IN} = 48.0 \text{ V}, V_{OUT} = 48.0 \text{ V},$                                                         | 96.3  | 97.3 |       | %      |

|                                   |                          | I <sub>OUT</sub> = 10.42 A, T <sub>INT</sub> = 100°C                                                         | 50.5  | 57.5 |       | /0     |

|                                   |                          | $V_{IN} = 48.0 \text{ V}, V_{OUT} = 48.0 \text{ V},$                                                         | 96.0  | 97.0 |       | %      |

| Efficiency Hot                    | $\eta_{HOT}$             | I <sub>OUT</sub> = 5.21 A, T <sub>INT</sub> = 100°C                                                          | 50.0  | 57.0 |       | ,,,    |

| Emelency Flot                     | HOI                      | $V_{IN} = 38.0 \text{ V to } 55.0 \text{ V}$ , $V_{OUT} = 48.0 \text{ V}$ ,                                  | 96.0  |      |       | %      |

|                                   |                          | I <sub>OUT</sub> = 10.42 A, T <sub>INT</sub> = 100°C                                                         |       |      |       | , , ,  |

|                                   |                          | $V_{IN} = 38.0 \text{ V to } 55.0 \text{ V}$ , $I_{OUT} = 10.42 \text{ A}$ ,                                 | 93.0  |      |       | %      |

|                                   |                          | $T_{INT} = 100$ °C, over trim                                                                                |       |      |       |        |

| Efficiency Over Temperature       | η                        | $>$ 50% load and $V_{OUT} = 48.0 V$ ; over temperature                                                       | 95.5  |      |       | %      |

|                                   | '                        | >50% load; over temperature and trim                                                                         | 91.0  |      |       | %      |

| Output Discharge current          | I <sub>OD</sub>          | Average Value                                                                                                |       | 0.5  |       | mA     |

| Output Voltage Ripple             | V <sub>OUT_PP</sub>      | $V_{IN} = 48.0 \text{ V}, V_{OUT} = 48.0 \text{ V},$                                                         |       | 750  | 1500  | mV     |

|                                   | * OU1_PP                 | $I_{OUT} = 10.42 \text{ A, } C_{OUT\_EXT} = 0 \text{ F, } 20 \text{ MHz BW}$                                 |       | , 50 | 1500  | 111 V  |

| Output Inductance (Parasitic)     | L <sub>OUT_PAR</sub>     | Frequency @ 1.03 MHz, Simulated J-Lead model                                                                 |       | 1.9  |       | nH     |

| Output Capacitance (Internal)     | C <sub>OUT_INT</sub>     | Effective value, V <sub>OUT</sub> = 48.0 V (see Fig.13)                                                      |       | 6    |       | μF     |

| Output Capacitance (Internal) ESR | R <sub>COUT</sub>        | Effective value, V <sub>OUT</sub> = 48.0 V                                                                   |       | 1.5  |       | mΩ     |

## **Electrical Specifications (cont.)**

Specifications apply over all line and load conditions, and trim from 20.0 V to 55.0 V, unless otherwise noted; **Boldface** specifications apply over the temperature range of -40°C < T<sub>INT</sub> < 125°C; All Other specifications are at T<sub>INT</sub> = 25°C unless otherwise noted.

| Attribute                                       | Symbol                     | Conditions / Notes                                                                                                                                                                          | Min   | Тур   | Max   | Unit |

|-------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

|                                                 |                            |                                                                                                                                                                                             |       |       |       |      |

|                                                 |                            | wer Output Specifications: Adaptive Loop Operation                                                                                                                                          |       | 10.00 |       | .,   |

| Output Voltage Setpoint                         | V <sub>OUT_SET</sub>       | No load, trim Inactive, Adaptive Loop load line inactive                                                                                                                                    | 47.00 | 48.00 | 49.00 | V    |

| Output Voltage Trim Range                       | V <sub>OUT</sub>           |                                                                                                                                                                                             | 20.0  |       | 55.0  | V    |

| Output Voltage Rise Time                        | t <sub>RISE_VOUT</sub>     | From soft start initiated to output voltage settled                                                                                                                                         | 1.7   | 1.8   | 1.9   | ms   |

| Output Voltage Load Regulation                  | V <sub>OUT_REG_LOAD</sub>  | Adaptive loop load line inactive                                                                                                                                                            |       | 0.02  | 0.2   | %    |

| Output Voltage Line Regulation                  | V <sub>OUT_REG_LINE</sub>  | Adaptive loop load line inactive                                                                                                                                                            |       | 0.02  | 0.2   | %    |

| Total Regulation Error                          | V <sub>OUT_REG_TOTAL</sub> | PRM output voltage, Adaptive Loop load line inactive                                                                                                                                        |       |       | 0.2   | %    |

| Total AL Regulation Error                       | V <sub>OUT_REG_</sub> AL   | VTM output voltage, total Adaptive Loop regulation, $V_{OUT} = 48.0 \text{ V}$ , trim inactive                                                                                              |       | 1     | 3     | %    |

| iotal AL Negulation Error                       | V OUT_REG_AL               | VTM output voltage, total Adaptive Loop regulation, trim active, exclusive of external resistor tolerances                                                                                  |       |       | 5     | %    |

| Output Current Limit                            | I <sub>LIMIT</sub>         | $V_{IN}$ = 48.0 V, $V_{OUT}$ = 48.0 V, $T_{INT}$ = 25°C, constant current limit after supervisory limit detection time $t_{LIM\_SUPV}$                                                      | 11.3  | 12.5  | 14    | А    |

|                                                 |                            | Over line, load, trim and temperature                                                                                                                                                       | 10.4  |       | 14.5  | А    |

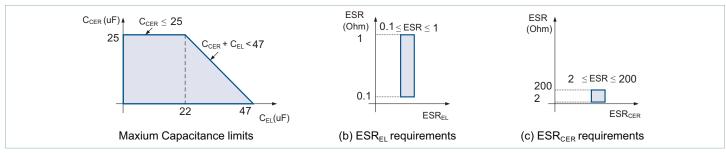

| Load Capacitance (Electrolytic)                 | C <sub>LOAD_ALEL</sub>     | ver line, load, trim and temperature 10.4  1 $\Omega \le \text{ESR} \le 1 \Omega$ , See Figure 32,  tal capacitance (C <sub>LOAD_ALEL</sub> + C <sub>LOAD_CER</sub> ) $\le 47  \mu\text{F}$ |       | 47    | μF    |      |

| Load Capacitance (Ceramic)                      | C <sub>LOAD_CER</sub>      | 2 m $\Omega$ ≤ ESR ≤ 200 m $\Omega$ , See Figure 32                                                                                                                                         |       |       | 25    | μF   |

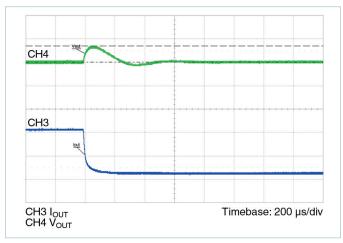

| Load Transient Voltage Deviation                | V <sub>TRANS</sub>         | 10% ↔ 100% load step, 10 A/µsec, 0 µF C <sub>OUT</sub> , deviation from initial setpoint                                                                                                    |       |       | 4.8   | V    |

| Load Transient Recovery Time                    | t                          | 10% ↔ 100% load step, 10 A/µsec, 0 µF C <sub>OUT</sub> ,<br>Recovery to 90% of final value, Adaptive Loop<br>load line inactive                                                             |       | 100   |       | μs   |

| Load Hansiett Necovery Time                     | t <sub>TRANS</sub>         | 10% ↔ 100% load step, 10 A/ $\mu$ sec, 0 $\mu$ F C <sub>OUT</sub> , Recovery to 90% of final value, Adaptive Loop load line active, V <sub>AL</sub> = 0.96 V                                |       | 500   |       | μs   |

|                                                 | Devere                     | w Output Specifications: Slave Operation with Al Master                                                                                                                                     |       |       |       |      |

|                                                 | Powe                       | r Output Specifications: Slave Operation with AL Master Slave Operation within an array, up to 5°C case                                                                                     |       |       |       |      |

|                                                 |                            | temperature differential, master-slave configuration                                                                                                                                        |       |       | 8.3   | Α    |

| Rated Current Within an Array                   | I <sub>OUT_ARRAY</sub>     | Slave Operation within an array, up to 30°C case                                                                                                                                            |       |       |       |      |

|                                                 |                            | temperature differential, master-slave configuration                                                                                                                                        |       |       | 7.3   | А    |

|                                                 |                            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                       |       |       |       |      |

|                                                 |                            | Slave Operation within an array, up to 5°C case                                                                                                                                             |       |       | 400   | W    |

| Rated Power Within an Array                     | P <sub>OUT_ARRAY</sub>     | temperature differential, master-slave configuration                                                                                                                                        |       |       |       |      |

| -                                               | _                          | Slave Operation within an array, up to 30°C case                                                                                                                                            |       |       | 350   | W    |

|                                                 |                            | temperature differential, master-slave configuration                                                                                                                                        |       |       |       |      |

|                                                 |                            | Equal input, and output voltage at full load; $V_{IN} = 48.0 \text{ V}$ , $V_{OUT} = 48.0 \text{ V}$                                                                                        |       |       | 15    | %    |

| Current Sharing Difference<br>(Master to Slave) | I <sub>OUT_SHARE_MS</sub>  | Equal input and output voltage at full load;<br>Over line and trim, with 25°C $\leq$ T <sub>C</sub> $\leq$ 100°C and $\leq$ 5°C<br>part-part temp. mismatch                                 |       |       | 15    | %    |

|                                                 |                            | Equal input, and output voltage at full load;<br>Over line and trim, with 25°C $\leq$ T <sub>C</sub> $\leq$ 100°C<br>and $\leq$ 30°C part-part temp. mismatch                               |       |       | 20    | %    |

## **Electrical Specifications (cont.)**

Specifications apply over all line and load conditions, and trim from 20.0 V to 55.0 V, unless otherwise noted; **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C; All Other specifications are at  $T_{INT}$  = 25°C unless otherwise noted.

| Attribute                     | Symbol                     | Conditions / Notes                                                                              | Min  | Тур | Max  | Unit   |

|-------------------------------|----------------------------|-------------------------------------------------------------------------------------------------|------|-----|------|--------|

|                               |                            |                                                                                                 |      |     |      |        |

|                               | Power                      | Output Specifications: Slave Operations (cont.)                                                 |      |     |      |        |

|                               |                            | Equal input, output, and SHARE voltage at full load;                                            |      |     | 5    | %      |

|                               |                            | $V_{IN} = 48.0 \text{ V}, V_{OUT} = 48.0 \text{ V}$                                             |      |     |      | ,,     |

|                               |                            | Equal input, output and SHARE voltage at full load;                                             |      |     |      |        |

| Current Sharing Difference    | I <sub>OUT</sub> SHARE SS  | Over line and trim, with 25°C $\leq$ T <sub>C</sub> $\leq$ 100°C                                |      |     | 10   | %      |

| (Slave to Slave)              | IOUI_SHAKE_SS              | and ≤ 5°C part-part temp. mismatch                                                              |      |     |      |        |

|                               |                            | Equal input, output, and SHARE voltage at full load;                                            |      |     |      |        |

|                               |                            | Over line and trim, with 25°C $\leq$ T <sub>C</sub> $\leq$ 100°C                                |      |     | 15   | %      |

|                               |                            | and ≤ 30°C part-part temp. mismatch                                                             |      |     |      |        |

| Maying the Array Cite         | NI                         | Maximum number of parallel devices,                                                             |      |     | 5    | PRMs   |

| Maximum Array Size            | N <sub>PRMS_PARALLEL</sub> | master-slave configuration                                                                      |      |     | 3    | PRIVIS |

|                               | Power                      | Output Specifications: Remote Sense Operation                                                   |      |     |      |        |

| Output Voltage Range          | V <sub>OUT</sub>           |                                                                                                 | 20.0 |     | 55.0 | V      |

|                               |                            | Remote Sense Operation within an array,                                                         |      |     |      |        |

|                               |                            | up to 5°C case temperature differential                                                         |      |     | 9.4  | Α      |

| Rated Current Within an Array | I <sub>OUT_ARRAY</sub>     | Remote Sense Operation within an array,                                                         |      |     |      |        |

|                               |                            | up to 30°C case temperature differential                                                        |      |     | 8.3  | Α      |

|                               |                            | Remote Sense Operation within an array,                                                         |      |     |      |        |

|                               |                            | up to 5°C case temperature differential                                                         |      |     | 450  | W      |

| Rated Power Within an Array   | P <sub>OUT_ARRAY</sub>     | Remote Sense Operation within an array,                                                         |      |     |      |        |

|                               |                            | up to 30°C case temperature differential                                                        |      |     | 400  | W      |

|                               |                            | Equal input, output, and CONTROL NODE voltage                                                   |      |     |      |        |

|                               |                            | at full load; $V_{IN} = 48.0 \text{ V}$ , $V_{OUT} = 48.0 \text{ V}$                            |      |     | 5    | %      |

|                               |                            | Equal input, output and CONTROL NODE voltage at                                                 |      |     |      |        |

|                               |                            | full load; Over line and trim, with 25°C $\leq$ T <sub>C</sub> $\leq$ 100°C                     |      |     | 10   | %      |

| Current Sharing Difference    | I <sub>OUT SHARE RS</sub>  | and ≤ 5°C part-part temp. mismatch                                                              |      |     |      |        |

|                               | -OOT_STARLE_RS             | Equal input, output, and CONTROL NODE voltage at                                                |      |     |      |        |

|                               |                            | full load; Over line and trim,                                                                  |      |     | 15   | %      |

|                               |                            | with $25^{\circ}\text{C} \le T_{\text{C}} \le 100^{\circ}\text{C}$ and $\le 30^{\circ}\text{C}$ |      | 13  |      | ,-     |

|                               |                            | part-part temp. mismatch (worst case)                                                           |      |     |      |        |

|                               |                            | Maximum number of parallel devices, Remote Sense                                                |      |     |      |        |

| Maximum Array Size            | N <sub>PRMS_PARALLEL</sub> | configuration, CONTROL NODE externally driven                                                   |      |     | 10   | PRMs   |

## **Electrical Specifications (cont.)**

Specifications apply over all line and load conditions, and trim from 20.0 V to 55.0 V, unless otherwise noted; **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C; All Other specifications are at  $T_{INT}$  = 25°C unless otherwise noted.

| Attribute                                         | Symbol                      | Conditions / Notes                                                   | Min  | Тур  | Max  | Unit |

|---------------------------------------------------|-----------------------------|----------------------------------------------------------------------|------|------|------|------|

|                                                   |                             | Powertrain Protections                                               |      |      |      |      |

| Input Undervoltage Turn-ON                        | V <sub>IN_UVLO+</sub>       | Powertrain Protections                                               |      | 24.5 | 26.0 | V    |

| Input Undervoltage Turn-OFF                       | VIN_UVLO+                   | Instantaneous powertrain shutdown, detected after t <sub>BLANK</sub> | 22.0 | 23.3 | 20.0 | V    |

| Input Undervoltage Hysteresis                     | VIN_UVLO-                   | (VIN_UVLO+) - (VIN_UVLO-)                                            | 0.6  | 1.2  | 1.5  | V    |

| Input Overvoltage Turn-ON                         |                             | (VIN_UVLO+) - (VIN_UVLO-)                                            | 58.0 | 62.0 | 1.5  | V    |

| Input Overvoltage Turn-OFF                        | V <sub>IN_OVLO</sub> -      | Instantaneous powertrain shutdown datasted after t                   | 56.0 | 64.0 | 66.0 | V    |

|                                                   | V <sub>IN_OVLO+</sub>       | Instantaneous powertrain shutdown, detected after t <sub>BLANK</sub> | 1.0  |      | 66.0 |      |

| Input Overvoltage Hysteresis                      | V <sub>OVLO_HYST</sub>      | (V <sub>IN_OVLO+</sub> ) - (V <sub>IN_OVLO-</sub> )                  | 1.6  | 2.0  | 2.4  | V    |

| Output Overvoltage Threshold                      | V <sub>OUT_OVP+</sub>       | Instantaneous shutdown, detected after t <sub>PROT</sub>             | 56.0 | 58.3 | 60.0 | V    |

| Minimum Current Limited Vout                      | V <sub>OUT_UVP</sub>        |                                                                      |      |      | 12   | V    |

| Overtemperature Shutdown Setpoint                 | T <sub>INT_OTP</sub>        | Instantaneous shutdown, detected after t <sub>PROT</sub>             | 125  |      |      | °C   |

| Output Power Limit                                | P <sub>PROT</sub>           |                                                                      | 500  |      |      | W    |

| Short Circuit V <sub>OUT</sub> Threshold          | V <sub>SC_VOUT</sub>        |                                                                      |      | 8.8  |      | V    |

| Short Circuit V <sub>OUT</sub> Recovery Threshold | V <sub>SC_VOUTR</sub>       |                                                                      |      | 9.5  |      | V    |

| Short Circuit CONTROL NODE Threshold              | $V_{SC\_VCN}$               |                                                                      |      | 7.2  |      | V    |

| Short Circuit CONTROL NODE                        | V                           |                                                                      |      | 6.9  |      | V    |

| Recovery Threshold                                | $V_{SC\_VCNR}$              |                                                                      |      | 0.9  |      | v    |

| Short Circuit Timeout                             | +                           | Short circuit fault detected after V <sub>SC_VOUT</sub>              |      | 5    |      | no.c |

| Short Circuit Timeout                             | t <sub>SC</sub>             | and V <sub>SC_VCN</sub> thresholds persist for this time             |      | 5    |      | ms   |

| Short Circuit Recovery Time                       | t <sub>SCR</sub>            | Excludes t <sub>OFF</sub>                                            |      | 75   |      | ms   |

| Overcurrent (IFB) and                             | t <sub>BLANK</sub>          |                                                                      | 50   | 120  | 150  | μs   |

| Input Over/Undervoltage Blanking Time             | RLANK                       |                                                                      | 30   | 120  | 150  | μ3   |

| Overtemperature, Output Overvoltage               |                             |                                                                      |      |      |      |      |

| and ENABLE Shutdown Response Time                 | t <sub>PROT</sub>           |                                                                      |      | 2    |      | μs   |

| (Hardware)                                        |                             |                                                                      |      |      |      |      |

|                                                   |                             | Powertrain Supervisory Limits                                        |      |      |      |      |

| Input Undervoltage Turn-ON                        |                             | rowertrain supervisory Limits                                        |      |      |      |      |

| (Supervisory)                                     | V <sub>IN_UVLO+_SUPV</sub>  |                                                                      |      | 35.7 | 37.1 | V    |

| Input Undervoltage Turn-OFF                       |                             |                                                                      |      | 05 - |      | , .  |

| (Supervisory)                                     | V <sub>IN_UVLOSUPV</sub>    | Powertrain shutdown, detected after t <sub>LIM_SUPV</sub>            | 32.2 | 33.6 |      | V    |

| Input Undervoltage Hysteresis                     |                             |                                                                      |      |      |      |      |

| (Supervisory)                                     | V <sub>UVLO_HYST_SUPV</sub> | $(V_{IN\_UVLO+\_SUPV})$ - $(V_{IN\_UVLO-\_SUPV})$                    | 1.8  | 2.1  | 2.4  | V    |

| Input Overvoltage Turn-ON                         |                             |                                                                      |      |      |      |      |

| (Supervisory)                                     | V <sub>IN_OVLOSUPV</sub>    |                                                                      | 55.5 | 57.5 |      | V    |

| Input Overvoltage Turn-OFF                        |                             |                                                                      |      |      |      |      |

| (Supervisory)                                     | V <sub>IN_OVLO+_SUPV</sub>  | Powertrain shutdown, detected after t <sub>LIM_SUPV</sub>            |      | 58.7 | 60.7 | V    |

| Input Overvoltage Hysteresis                      |                             |                                                                      |      |      |      |      |

| (Supervisory)                                     | V <sub>OVLO_HYST_SUPV</sub> | (V <sub>IN_UVLO+_SUPV</sub> ) - (V <sub>IN_UVLOSUPV</sub> )          | 0.9  | 1.2  | 1.5  | V    |

| Undertemperature Shutdown Setpoint                |                             | T Grade                                                              |      |      | -40  | °C   |

| (Supervisory)                                     | T <sub>INT_UTP</sub>        | M Grade                                                              |      |      | -55  | °C   |

| Supervisory Limit Response Time                   | t <sub>LIM</sub> SUPV       | 5.555                                                                |      |      | 150  | μs   |

| Supervisory Limit Nesponse Time                   | LIM_SUPV                    |                                                                      |      |      | 1.50 | μ3   |

## **Signal Specifications**

Specifications apply over all line and load conditions,  $T_{INT} = 25^{\circ}\text{C}$  and output voltage from 20.0 V to 55.0 V, unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C (T-grade).

#### **ENABLE**

- The ENABLE pin enables and disables the PRM

- In PRM array configurations, ENABLE pins should be connected in order to synchronize start up

- ENABLE is 5 V with 1.8 mA source capability during normal operation

| Signal Type            | State     | Attribute                       | Symbol                    | Conditions / Notes                             | Min  | Тур  | Max  | Unit |

|------------------------|-----------|---------------------------------|---------------------------|------------------------------------------------|------|------|------|------|

|                        | Normal    | ENABLE Voltage                  | $V_{ENABLE}$              |                                                | 4.7  | 5.0  | 5.3  | V    |

| Analog Output          | Operation | ENABLE Current                  | I <sub>ENABLE_OP</sub>    |                                                |      |      | 1.8  | mA   |

| Analog Output          | Start up  | ENABLE Source Current           | I <sub>ENABLE_EN</sub>    | After t <sub>OFF</sub>                         |      | 90   |      | μΑ   |

|                        |           | Minimum Time to Start           | t <sub>OFF</sub>          |                                                | 13.0 | 15.0 | 17.0 | ms   |

|                        | Start up  | ENABLE<br>Enable Threshold      | V <sub>ENABLE_EN</sub>    |                                                |      | 2.5  | 3.2  | V    |

| Digital Input / Output | C+an dlay | ENABLE Disable Threshold        | V <sub>ENABLE_DIS</sub>   |                                                | 0.97 | 2.40 |      | V    |

|                        | Standby   | ENABLE<br>Resistance (External) | R <sub>ENABLE_EXT</sub>   | Resistance to SGND required to disable the PRM |      |      | 235  | Ω    |

| Digital Output         | Fault     | ENABLE<br>Sink Current to SGND  | I <sub>ENABLE_FAULT</sub> | ENABLE voltage 1 V or above                    |      |      | 4    | mA   |

|                     |                    | V                              | /AUX: Auxill          | ary Voltage Source                                                                                        |     |     |      |      |

|---------------------|--------------------|--------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Intended to power   | auxiliary circuits |                                |                       |                                                                                                           |     |     |      |      |

| 9 V during normal o | operation with 5   | mA source capability           |                       |                                                                                                           |     |     |      |      |

| Signal Type         | State              | Attribute                      | Symbol                | Conditions / Notes                                                                                        | Min | Тур | Max  | Unit |

| Analog Output       |                    | VAUX Voltage                   | $V_{VAUX}$            |                                                                                                           | 8.6 | 9.0 | 9.5  | V    |

|                     | Normal             | VAUX Current                   | I <sub>VAUX</sub>     |                                                                                                           |     |     | 5    | mA   |

|                     | Operation          | VAUX Voltage Ripple            | V <sub>VAUX_PP</sub>  | $I_{OUT} = 0A$ , $C_{VAUX\_EXT} = 0$ . Maximum specification includes powertrain operation in burst mode. |     | 100 | 400  | mV   |

|                     | Transition         | VAUX Capacitance<br>(External) | C <sub>VAUX_EXT</sub> |                                                                                                           |     |     | 0.04 | μF   |

|                     | ITANSILION         | Transition VAUX Fault Response | t <sub>FR_VAUX</sub>  | From fault recognition to                                                                                 |     | 30  |      | μs   |

|                                           |                                                                                    |                      | VC: V                  | TIVI Control                                         |      |     |      |      |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------|----------------------|------------------------|------------------------------------------------------|------|-----|------|------|--|--|--|

| <ul> <li>Pulsed voltage source</li> </ul> | Pulsed voltage source used to power and synchronize downstream VTM during start up |                      |                        |                                                      |      |     |      |      |  |  |  |

| • 14 V, 10 ms typical voltage pulse       |                                                                                    |                      |                        |                                                      |      |     |      |      |  |  |  |

| Signal Type                               | State                                                                              | Attribute            | Symbol                 | Conditions / Notes                                   | Min  | Тур | Max  | Unit |  |  |  |

|                                           |                                                                                    | VC Voltage           | \/                     | Connected to VTM VC or equivalent,                   | 13   | 14  | 18   | V    |  |  |  |

|                                           |                                                                                    |                      | V <sub>VC_START</sub>  | $I_{VC} = 115 \text{ mA}, \ C_{VC} = 3.2 \text{ uF}$ | 13   | 14  | 10   | V    |  |  |  |

| Analog Output                             | Start up                                                                           | VC Available Current | I <sub>VC_START</sub>  | $V_{C} = 14 \text{ V}, V_{IN} > 20 \text{ V}$        | 200  |     |      | mA   |  |  |  |

| Analog Output                             | Start up                                                                           | VC Duration          | t <sub>VC</sub>        |                                                      | 7    | 10  | 16   | ms   |  |  |  |

|                                           |                                                                                    | VC Slew Rate         | dVC/dt                 | Connected to VTM or equivalent,                      |      |     |      | .,,  |  |  |  |

|                                           |                                                                                    | vc siew hate         | uvc/ut                 | $I_{VC} = 115 \text{ mA}, \ C_{VC} = 3.2 \text{ uF}$ | 0.02 |     | 0.25 | V/µs |  |  |  |

|                                           |                                                                                    | ENABLE to VC Delay   | t <sub>ENABLE-VC</sub> |                                                      |      | 20  |      | μs   |  |  |  |

Specifications apply over all line and load conditions,  $T_{INT} = 25^{\circ}\text{C}$  and output voltage from 20.0 V to 55.0 V, unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C (T-grade).

#### **SGND: Signal Ground**

- All control signals must be referenced to this pin, with the exception of VC

- SGND is internally connected to -IN and -OUT

| Signal Type           | State | Attribute                    | Symbol            | Conditions / Notes | Min  | Тур | Max | Unit |

|-----------------------|-------|------------------------------|-------------------|--------------------|------|-----|-----|------|

| Analog Input / Output | Any   | Maximum Allowable<br>Current | I <sub>SGND</sub> |                    | -100 |     | 100 | mA   |

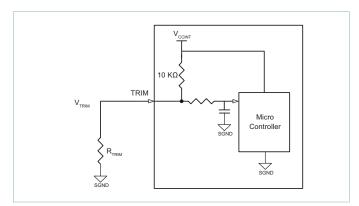

#### **TRIM**

- TRIM is used to select operating mode and trim the output voltage in Adaptive Loop Operation

- $\bullet$  Internal pullup to  $V_{CC\_INT}$  through 10  $k\Omega$  resistor

- When pulled below 0.45 V during power up, Remote Sense / Slave Operation is selected

- When allowed to pull up above 0.55 V during power up, Adaptive Loop Operation is selected

- Operating mode is detected during power up and cannot be changed unless input power is cycled

| Signal Type  | State          | Attribute                                         | Symbol                   | Conditions / Notes                                                                                                           | Min  | Тур   | Max   | Unit |

|--------------|----------------|---------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------|

|              | Normal         | Internally Generated VCC                          | V <sub>CC_INT</sub>      |                                                                                                                              | 3.20 | 3.28  | 3.36  | V    |

|              | Operation      | Internal Pullup Resistance to V <sub>CC_INT</sub> | R <sub>TRIM_INT</sub>    | 0.5% tolerance resistor                                                                                                      | 9.83 | 10.00 | 10.18 | kΩ   |

| Analog Input |                | Mode Detection<br>Delay                           | t <sub>MODE_DETECT</sub> | From ENABLE high to mode detected, after $V_{\text{IN}}$ first applied                                                       | 100  | 140   | 200   | μs   |

|              | Mode<br>Detect | Remote Sense<br>Enable Threshold                  | V <sub>RS_MODE_EN</sub>  | Pull <b>below</b> this value during first<br>start up after application of power to<br>enable Remote Sense / Slave Operation | 0.45 |       |       | V    |

|              |                | Remote Sense<br>Disable Threshold                 | V <sub>RS_MODE_DIS</sub> | Pull <b>above</b> this value during first<br>start up after application of power to<br>enable Adaptive Loop Operation        |      |       | 0.55  | V    |

Specifications apply over all line and load conditions,  $T_{INT} = 25^{\circ}\text{C}$  and output voltage from 20.0 V to 55.0 V, unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C (T-grade).

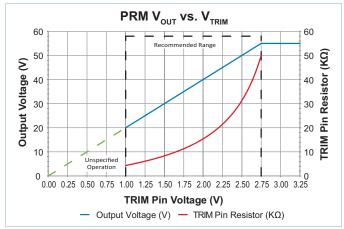

#### **TRIM (Adaptive Loop Operation Only)**

- Provides dynamic trim control over the PRM output voltage in Adaptive Loop Operation

- Sampled prior to every start up to detect if trim is active or inactive

- Output voltage is equal to 20 times the voltage at the TRIM pin when applied TRIM voltage is within the active range

- Trim state is detected during normal operation and cannot be changed until start up is initiated

| Signal Type  | State               | Attribute                                    | Symbol                    | Conditions / Notes                                                                   | Min  | Тур  | Max  | Unit  |

|--------------|---------------------|----------------------------------------------|---------------------------|--------------------------------------------------------------------------------------|------|------|------|-------|

|              |                     | Trim Enable Threshold                        | V <sub>TRIM_EN</sub>      | Pull <b>below</b> this value during                                                  | 3.10 |      |      | V     |

|              |                     |                                              | _                         | start up to enable trim control                                                      |      |      |      |       |

|              |                     | Trim Disable Threshold                       | $V_{TRIM\_DIS}$           | Pull <b>above</b> this value during start up to disable trim control                 |      |      | 3.20 | V     |

|              | Start up            | Minimum Trim Disable                         | D                         | Minimum TRIM resistance required                                                     | 10   |      |      | МΩ    |

|              |                     | Resistance                                   | R <sub>TRIM_DIS_MIN</sub> | to disable trim                                                                      | 10   |      |      | IVILL |

|              |                     | Trim Capacitance                             | C <sub>TRIM_EXT</sub>     |                                                                                      |      |      | 100  | pF    |

|              |                     | (External)                                   |                           | For a FNIADIE L'alant TDINA a contral                                                | 400  | 1.40 | 200  |       |

| Analog Input |                     | Trim Sample Delay TRIM Pin                   | t <sub>ENABLE_TRIM</sub>  | From ENABLE high to TRIM sampled                                                     | 100  | 140  | 200  | μs    |

| Analog Input |                     | Analog Range                                 | V <sub>TRIM_RANGE</sub>   | See Figure 26                                                                        | 1.00 |      | 2.75 | V     |

|              | Navasal             | TRIM Gain                                    | G <sub>TRIM</sub>         | $V_{\text{OUT}}$ / $V_{\text{TRIM}}$ , $V_{\text{TRIM}}$ applied within active range |      | 20   |      | V/V   |

|              | Normal<br>Operation | Trim Accuracy                                | % <sub>ACC_TRIM</sub>     | Vout accuracy, exclusive of external resistor tolerance                              |      | 0.5  | 2.0  | %     |

|              |                     | V <sub>OUT</sub> Referred<br>Trim Resolution | V <sub>OUT_RES</sub>      |                                                                                      |      | 200  |      | mV    |

|              |                     | Trim Latency                                 | t <sub>TRIM_LAT</sub>     |                                                                                      | 60   | 120  | 240  | μs    |

|              |                     | Trim Bandwidth                               | BW <sub>TRIM</sub>        | -3dB point                                                                           |      | 1.2  |      | kHz   |

Specifications apply over all line and load conditions,  $T_{INT} = 25^{\circ}\text{C}$  and output voltage from 20.0 V to 55.0 V, unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C (T-grade).

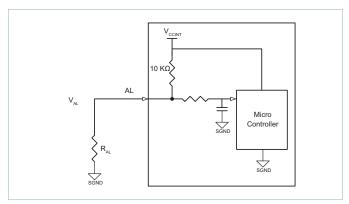

#### AL: Adaptive Loop (Adaptive Loop Operation Only)

- Provides Adaptive Loop load line programming in Adaptive Loop Operation

- $\bullet$  Internal pullup to  $V_{CC\_INT}$  through 10  $k\Omega$  resistor

- Sampled prior to every start up to detect if Adaptive Loop load line is active or inactive

- Leave open to disable Adaptive Loop load line

- Not used in Remote Sense Operation

| Signal Type  | State     | Attribute                         | Symbol                  | Conditions / Notes                           | Min  | Тур   | Max   | Unit  |

|--------------|-----------|-----------------------------------|-------------------------|----------------------------------------------|------|-------|-------|-------|

|              |           | AL Enable Threshold               | V <sub>AL_EN</sub>      | Pull <b>below</b> this value during start up | 3.10 |       |       | V     |

|              |           | AL Eliable Tilleshold             | VAL_EN                  | to enable AL load line                       | 5.10 |       |       | •     |

|              |           | AL Disable Threshold              | $V_{AL\_DIS}$           | Pull <b>above</b> this value during start up |      |       | 3.20  | V     |

|              |           | 7 12 2 13 G 2 1 1 1 1 2 3 1 2 1 G | * AL_DIS                | to disable AL load line                      |      |       | 55    | •     |

|              | Start up  | Minimum AL Disable                | R <sub>AL_DIS_MIN</sub> | Minimum AL resistance required               | 10   |       |       | МΩ    |

|              |           | Resistance                        | TAL_DIS_IVIIN           | to disable AL load line                      |      |       |       | 14122 |

|              |           | AL Capacitance                    | $C_{AL_EXT}$            |                                              |      |       | 100   | pF    |

|              |           | (External)                        | -AL_LXI                 |                                              |      |       |       | 15.   |

|              |           | AL Sample Delay                   | t <sub>ENABLE_AL</sub>  | From ENABLE high to AL sampled               | 100  | 140   | 200   | μs    |

|              |           | Internally generated              | V <sub>CC_INT</sub>     |                                              | 3.20 | 3.28  | 3.36  | V     |

| Analog Input |           | VCC                               | • CC_IIVI               |                                              |      | 3.20  | 5.50  | •     |

|              |           | Internal Pullup                   | R <sub>AL_INT</sub>     | 0.5% tolerance resistor                      | 9.83 | 10.00 | 10.18 | kΩ    |

|              |           | Resistance to V <sub>CC_INT</sub> | · ·AL_INI               | ora ya tarenamee nesistar                    |      | 10.00 |       |       |

|              | Normal    | AL Pin Analog Range               | $V_{AL\_RANGE}$         |                                              | 0    |       | 3.10  | V     |

|              | Operation | AL Gain                           | $G_AL$                  | Positive correction slope, VT inactive       |      | 0.5   |       | Ω/\   |

|              | Operation | AL Load Line Accuracy             | % <sub>ACC_LL_AL</sub>  | Full load slope accuracy exclusive           |      | 0.5   | 2.0   | %     |

|              |           | AL LOGG LINE Accuracy             | /UACC_LL_AL             | of external resistor tolerance               |      | 0.5   | 2.0   | /0    |

|              |           | AL Load Line Resolution           | LL <sub>AL_RES</sub>    |                                              |      | 3     |       | mΩ    |

|              |           | Maximum Output                    | Va                      | Maximum increase from no                     |      |       | 5     | V     |

|              |           | Referred Compensation             | V <sub>OUT_AL_MAX</sub> | load setpoint, V <sub>OUT</sub> ≤ 55.0 V     |      |       | ,     | V     |

|              |           | AL Latency                        | t <sub>AL_LAT</sub>     |                                              | 60   | 120   | 240   | μs    |

|              |           | AL Bandwidth                      | BW <sub>AL</sub>        | -3dB point                                   |      | 1.2   |       | kHz   |

Specifications apply over all line and load conditions,  $T_{INT} = 25^{\circ}\text{C}$  and output voltage from 20.0 V to 55.0 V, unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C (T-grade).

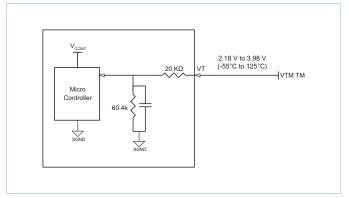

#### VT: VTM Temperature (Adaptive Loop Operation Only)

- VTM temperature compensation for Adaptive Loop regulation

- Adjusts the slope of the Adaptive Loop load line to account for changes in VTM output resistance over temperature

- Connect to TM pin of compatible downstream VTM to enable temperature compensation

- Leave disconnected to disable temperature compensation

| Signal Type  | State     | Attribute                         | Symbol               | Conditions / Notes                                           | Min  | Тур  | Max  | Unit |

|--------------|-----------|-----------------------------------|----------------------|--------------------------------------------------------------|------|------|------|------|

|              |           | Internal Resistance<br>to SGND    | $R_{VT\_INT}$        |                                                              |      | 80.4 |      | kΩ   |

|              |           | VT Enable Threshold               | $V_{VT\_EN}$         |                                                              |      |      | 2.1  | V    |

|              |           | VT Disable Threshold              | $V_{VT\_DIS}$        | Pull below this value to disable VT temperature compensation | 1.9  |      |      | V    |

| Analog Input | Normal    | VT Disable Default<br>Temperature | $T_{VT\_DIS}$        | Default AL temperature setting when VT disabled              |      | 25   |      | °C   |

| Analog Input | Operation | VT Analog Range                   | $V_{VT\_OP}$         |                                                              | 2.18 |      | 3.98 | V    |

|              |           | VT Temperature                    | $TC_{VT}$            | VT within active range, referenced to 2.98 V                 |      | 30   |      | %/V  |

|              |           | Coefficient                       | TC <sub>VT</sub>     | VTM TM voltage applied, .01V/°K, referenced to 25°C          |      | 0.3  |      | %/C  |

|              |           | VT Resolution                     | TC <sub>VT_RES</sub> | VTM TM voltage applied, .01V/°K                              |      | 0.4  |      | °C   |

|              |           | VT Latency                        | $t_{VT\_LAT}$        |                                                              | 60   | 120  | 240  | μs   |

|              |           | Bandwidth                         | $BW_{VT}$            | -3dB point                                                   |      | 4.8  |      | kHz  |

#### **REF: Reference (Adaptive Loop Operation Only)**

- Functions as REF pin in Adaptive Loop Operation

- REF represents the internal voltage reference for the voltage control circuit

- $\bullet$   $V_{OUT}$  approximately equal to 20 times REF voltage

| Signal Type   | State      | Attribute               | Symbol                  | Symbol Conditions / Notes                 |    | Тур | Max | Unit  |

|---------------|------------|-------------------------|-------------------------|-------------------------------------------|----|-----|-----|-------|

|               |            | REF Voltage             | $V_{REF}$               | $V_{OUT} = 48.0 \text{ V, trim inactive}$ |    | 2.4 |     | V     |

|               |            | REF to V <sub>OUT</sub> | C                       | V <sub>OUT</sub> / V <sub>RFF</sub>       |    | 20  |     | V / V |

|               | Normal     | Scale Factor            | G <sub>REF_VOUT</sub>   | VOUT / VREF                               |    | 20  |     | V / V |

|               | Operation  | REF Resistance          | D                       |                                           | 10 |     |     | МΩ    |

| Analog Output | Орегация   | (External)              | R <sub>REF_EXT</sub>    |                                           | 10 |     |     | IVISZ |

| Analog Output |            | REF Capacitance         | C <sub>REF_EXT</sub>    |                                           |    |     | 200 | n.E   |

|               |            | (External)              |                         |                                           |    |     | 200 | pF    |

|               |            | REF Voltage Ripple      | V <sub>REF_PP</sub>     | Includes burst mode, 20 MHz BW            |    | 25  |     | mV    |

|               |            | ENABLE to REF Delay     | t <sub>ENABLE_REF</sub> | ENABLE low to REF low                     |    | 120 |     | μs    |

|               | Transition | VAUX to REF Delay       | +                       | VAUX = 8.1 V to REF soft start            |    |     |     |       |

|               |            | VAUX to INEF Delay      | t <sub>VAUX_REF</sub>   | ramp initiated                            |    |     |     | ms    |

Specifications apply over all line and load conditions,  $T_{INT} = 25^{\circ}\text{C}$  and output voltage from 20.0 V to 55.0 V, unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C (T-grade).

#### REF\_EN: Reference Enable (Remote Sense and Slave Operation Only)

- Functions as REF\_EN pin in Remote Sense and Slave Operation

- REF\_EN signals successful start up and powertrain ready to operate

- Intended to power and enable the external feedback circuit reference in Remote Sense Operation

- 3.25 V, 4 mA regulated voltage source

| Signal Type   | State      | Attribute                     | Symbol                     | Conditions / Notes             | Min  | Тур  | Max  | Unit |

|---------------|------------|-------------------------------|----------------------------|--------------------------------|------|------|------|------|

|               |            | REF_EN Voltage                | $V_{REF\_EN}$              | REF_EN unloaded                | 2.72 | 3.25 | 3.37 | V    |

|               | Normal     | REF_EN Source<br>Impedance    | R <sub>OUT_REF_EN</sub>    |                                |      | 50   | 100  | Ω    |

|               |            | REF_EN Current                | I <sub>REF_EN</sub>        |                                |      |      | 4    | mΑ   |

| Analog Output | Operation  | REF_EN Capacitance (External) | C <sub>REF_EN_EXT</sub>    |                                |      |      | 0.1  | μF   |

|               |            | REF_EN Voltage Ripple         | $V_{REF\_EN\_PP}$          | Includes burst mode, 20 MHz BW |      | 25   |      | mV   |

|               |            | ENABLE to REF_EN Delay        | t <sub>ENABLE_REF_EN</sub> | ENABLE low to REF_EN low       |      | 120  |      | μs   |

|               | ITALISHION | VAUX to REF_EN<br>Delay       | t <sub>VAUX_REF_EN</sub>   | VAUX = 8.1 V to REF_EN high    |      | 1    |      | ms   |

#### **Share (Adaptive Loop and Slave Operation Only)**

- Functions as SHARE pin in master slave array configuration

- Current share bus for array operation (master/slave scheme)

- Sources current and provides SHARE signal in master operation

- Sinks constant current when externally driven in active range (Slave Operation)

| Signal Type   | State               | Attribute                     | Symbol                  | Conditions / Notes          | Min  | Тур  | Max  | Unit |

|---------------|---------------------|-------------------------------|-------------------------|-----------------------------|------|------|------|------|

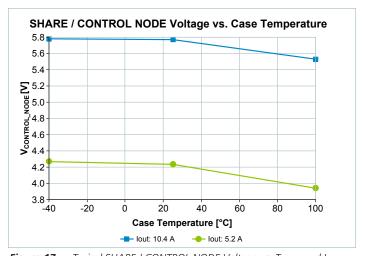

|               | Standalone/         | SHARE Voltage<br>Active Range | $V_{SHARE}$             |                             | 0.79 |      | 7.40 | V    |

| Analog Output | Master<br>Operation | SHARE Available<br>Current    | I <sub>SHARE</sub>      | V <sub>SHARE</sub> > 0.79 V | 2.5  |      |      | mA   |

|               | Орегиноп            | SHARE Resistance to SGND      | R <sub>SHARE</sub>      |                             |      | 93.3 |      | kΩ   |

| Analog Input  | Slave<br>Operation  | SHARE Sink Current            | I <sub>SHARE_SINK</sub> | V <sub>SHARE</sub> > 0.79 V | 0.25 | 0.50 | 0.75 | mA   |

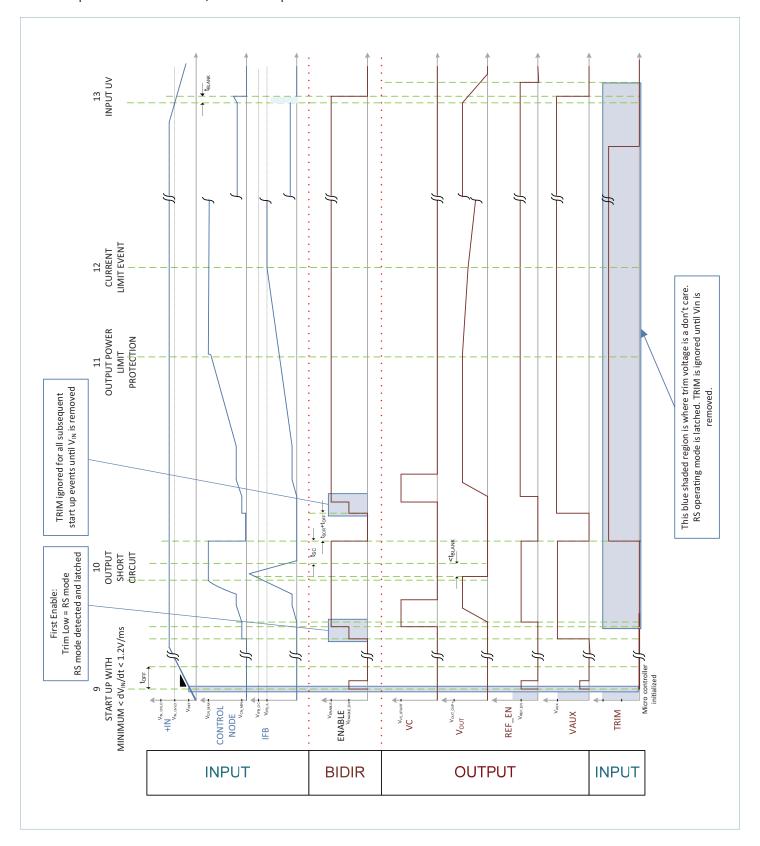

Specifications apply over all line and load conditions,  $T_{INT} = 25^{\circ}\text{C}$  and output voltage from 20.0 V to 55.0 V, unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C (T-grade).