#### Is Now Part of

## ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

September 2015

## FAN2315 15 A Synchronous Buck Regulator

#### **Features**

V<sub>IN</sub> Range: 4.5 V to 18 V

■ High Efficiency: Over 96% Peak

Continuous Output Current: 15 A

PFM Mode for Light-Load Efficiency

Excellent Line and Load Transient Response

■ Precision Reference: ±1% Over Temperature

Output Voltage Range: 0.6 to 5.5 V

Programmable Frequency: 200 kHz to 1 MHz

Programmable Soft-Start

Low Shutdown Current

Adjustable Sourcing Current Limit

Internal Boot Diode

Thermal Shutdown

Halogen and Lead Free, RoHS Compliant

## **Applications**

- Servers and Desktop Computers

- NVDC Notebooks, Netbooks

- Game Consoles

- Telecommunications

- Storage

- Base Stations

## **Description**

The FAN2315 is a highly efficient synchronous buck regulator. The regulator is capable of operating with an input range from 4.5 V to 18 V and supporting up to 15 A load currents.

The FAN2315 utilizes Fairchild's constant on-time control architecture to provide excellent transient response and to maintain a relatively constant switching frequency. The device utilizes Pulse Frequency Modulation (PFM) mode to maximize light-load efficiency by reducing switching frequency when the inductor is operating in discontinuous conduction mode at light loads.

Switching frequency and over-current protection can be programmed to provide a flexible solution for various applications. Output over-voltage, under-voltage, over-current, and thermal shutdown protections help prevent damage to the device during fault conditions. A hysteresis feature restarts the device when normal operating temperature is reached.

## **Ordering Information**

| Part Number | Configuration            | Operating<br>Temperature Range | Output<br>Current (A) | Package                           |

|-------------|--------------------------|--------------------------------|-----------------------|-----------------------------------|

| FAN2315MPX  | PFM with Ultrasonic Mode | -40 to 125°C                   | 15                    | 34-Lead, PQFN,<br>5.5 mm x 5.0 mm |

.

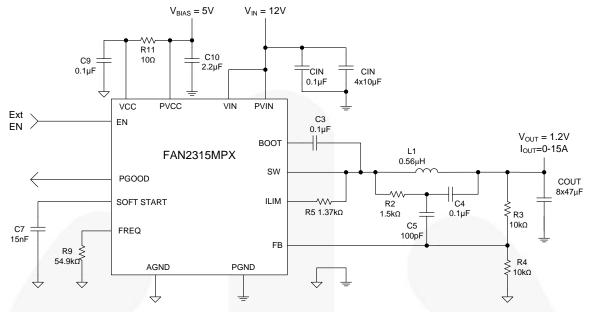

## **Typical Application Diagram**

Figure 1. Typical Application

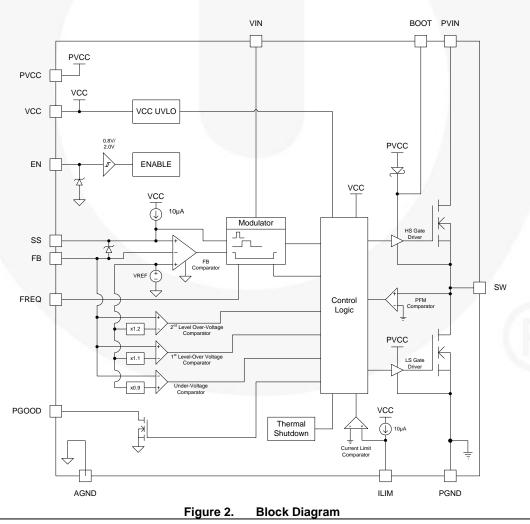

## **Functional Block Diagram**

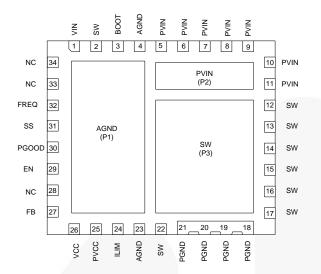

## **Pin Configuration**

SW  $\stackrel{\mathsf{Z}}{>}$ 2 NC PVIN 34 NC PVIN 33 FREQ SW 12 32 SS SW 31 30 PGOOD ΕN SW 29 15 SW 16 28 NC FB SW 27 22 23 24 AGND VCC ΝS ∑ ∐

Figure 3. Pin Assignments, Bottom View

Figure 4. Pin Assignments, Top View

## **Pin Definitions**

| Name  | Pad / Pin        | Description                                                                                                                                                                                                                                                             |  |  |  |

|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PVIN  | P2, 5-11         | Power input for the power stage                                                                                                                                                                                                                                         |  |  |  |

| VIN   | 1                | put to the modulator for input voltage feed-forward                                                                                                                                                                                                                     |  |  |  |

| PVCC  | 25               | Ower input for the low-side gate driver and boot diode                                                                                                                                                                                                                  |  |  |  |

| VCC   | 26               | Power supply input for the controller                                                                                                                                                                                                                                   |  |  |  |

| PGND  | 18-21            | Power ground for the low-side power MOSFET and for the low-side gate driver                                                                                                                                                                                             |  |  |  |

| AGND  | P1, 4, 23        | nalog ground for the analog portions of the IC and for substrate                                                                                                                                                                                                        |  |  |  |

| SW    | P3, 2, 12-17, 22 | Switching node; junction between high-and low-side MOSFETs                                                                                                                                                                                                              |  |  |  |

| воот  | 3                | Supply for high-side MOSFET gate driver. A capacitor from BOOT to SW supplies the charge to turn on the N-channel high-side MOSFET. During the freewheeling interval (low-side MOSFET on), the high-side capacitor is recharged by an internal diode connected to PVCC. |  |  |  |

| ILIM  | 24               | Current limit. A resistor between ILIM and SW sets the current limit threshold.                                                                                                                                                                                         |  |  |  |

| FB    | 27               | Output voltage feedback to the modulator                                                                                                                                                                                                                                |  |  |  |

| EN    | 29               | Enable input to the IC. Pin must be driven logic high to enable, or logic low to disable.                                                                                                                                                                               |  |  |  |

| SS    | 31               | Soft-start input to the modulator                                                                                                                                                                                                                                       |  |  |  |

| FREQ  | 32               | On-time and frequency programming pin. Connect a resistor between FREQ and AGND to program on-time and switching frequency.                                                                                                                                             |  |  |  |

| PGOOD | 30               | Power good; open-drain output indicating V <sub>OUT</sub> is within set limits.                                                                                                                                                                                         |  |  |  |

| NC    | 28, 33-34        | Leave pin open or connect to AGND.                                                                                                                                                                                                                                      |  |  |  |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol            | Parameter                | Conditions                                       | Min. | Max. | Unit |

|-------------------|--------------------------|--------------------------------------------------|------|------|------|

| $V_{PVIN}$        | Power Input              | Referenced to PGND                               | -0.3 | 25.0 | V    |

| V <sub>IN</sub>   | Modulator Input          | Referenced to AGND                               | -0.3 | 25.0 | V    |

| \/                | Boot Voltage             | Referenced to PVCC                               | -0.3 | 26.0 | V    |

| $V_{BOOT}$        |                          | Referenced to PVCC, <20 ns                       | -0.3 | 30.0 | V    |

| \/                | CW Voltage to CND        | Referenced to PGND, AGND                         | -1   | 25   | V    |

| $V_{SW}$          | SW Voltage to GND        | Referenced to PGND, AGND < 20 ns                 | -5   | 25   | V    |

| \/                | Boot to SW Voltage       | Referenced to SW                                 | -0.3 | 6.0  | V    |

| $V_{BOOT}$        | Boot to PGND             | Referenced to PGND                               | -0.3 | 30.0 | V    |

| V <sub>PVCC</sub> | Gate Drive Supply Input  | Referenced to PGND, AGND                         | -0.3 | 6.0  | V    |

| V <sub>VCC</sub>  | Controller Supply Input  | Referenced to PGND, AGND                         | -0.3 | 6.0  | V    |

| $V_{ILIM}$        | Current Limit Input      | Referenced to AGND                               | -0.3 | 6.0  | V    |

| $V_{FB}$          | Output Voltage Feedback  | Referenced to AGND                               | -0.3 | 6.0  | V    |

| V <sub>EN</sub>   | Enable Input             | Referenced to AGND                               | -0.3 | 6.0  | V    |

| V <sub>SS</sub>   | Soft Start Input         | Referenced to AGND                               | -0.3 | 6.0  | V    |

| $V_{FREQ}$        | Frequency Input          | Referenced to AGND                               | -0.3 | 6.0  | V    |

| $V_{PGOOD}$       | Power Good Output        | Referenced to AGND                               | -0.3 | 6.0  | V    |

| ECD               | Flactus static Dischause | Human Body Model, JESD22-A114 <sup>(1)</sup>     |      | 2000 | V    |

| ESD               | Electrostatic Discharge  | Charged Device Model, JESD22-C101 <sup>(2)</sup> |      | 2500 | V    |

| TJ                | Junction Temperature     |                                                  |      | +150 | °C   |

| T <sub>STG</sub>  | Storage Temperature      |                                                  | -55  | +150 | °C   |

#### Note:

- Exception for FB pin up to 350V

- 2. Exception for FB pin up to 500V

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol            | Parameter               | Conditions                       | Min. | Max. | Unit |

|-------------------|-------------------------|----------------------------------|------|------|------|

| V <sub>PVIN</sub> | Power Input             | Referenced to PGND               | 4.5  | 18   | V    |

| V <sub>IN</sub>   | Modulator Input         | Referenced to AGND               | 4.5  | 18   | V    |

| TJ                | Junction Temperature    |                                  | -40  | +125 | °C   |

| I <sub>LOAD</sub> | Load Current            | T <sub>A</sub> =25°C, No Airflow |      | 20   | Α    |

| V <sub>PVCC</sub> | Gate Drive Supply Input | Referenced to PGND, AGND         | 4.5  | 5.5  | V    |

## **Thermal Characteristics**

The thermal characteristics were evaluated on a 4-layer PCB structure (1 oz/1 oz/1 oz/1 oz) measuring 7 cm x 7 cm).

| Symbol        | Parameter                                                   |     | Unit |

|---------------|-------------------------------------------------------------|-----|------|

| $\Theta_{JA}$ | Thermal Resistance, Junction-to-Ambient                     |     | °C/W |

| Ψις           | Thermal Characterization Parameter, Junction-to-Top of Case | 2.7 | °C/W |

| <b>Ψ</b> JРСВ | Thermal Characterization Parameter, Junction-to-PCB         | 2.3 | °C/W |

## **Electrical Characteristics**

Unless otherwise noted;  $V_{IN}\!=\!12$  V,  $V_{OUT}\!=\!1.2$  V, and  $T_A\!=\!T_J\!=\!-40$  to  $125^{\circ}C.$   $^{(4)}$

| Symbol                      | Parameter                                      | Condition                                                                             | Min. | Тур. | Max. | Unit   |

|-----------------------------|------------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|--------|

| Supply Curre                | ent                                            |                                                                                       |      |      | ·    | •      |

| I <sub>VIN,SD</sub>         | Shutdown Current                               | EN=0 V                                                                                |      |      | 10   | μΑ     |

| $I_{VIN,Q}$                 | Quiescent Current                              | EN=5 V, Not Switching                                                                 |      |      | 1.8  | mA     |

| I <sub>VIN,GateCharge</sub> | Gate Charge Current                            | EN=5 V, f <sub>SW</sub> =500 kHz                                                      |      | 22   |      | mA     |

| Reference, F                | eedback Comparator                             |                                                                                       |      |      |      |        |

| $V_{FB}$                    | FB Voltage Trip Point                          |                                                                                       | 590  | 596  | 602  | mV     |

| I <sub>FB</sub>             | FB Pin Bias Current                            |                                                                                       | -100 | 0    | 100  | nA     |

| Modulator                   |                                                |                                                                                       |      |      |      |        |

| t <sub>ON</sub>             | On-Time Accuracy                               | R <sub>FREQ</sub> =56.2 k, V <sub>IN</sub> =10 V,<br>t <sub>ON</sub> =250 ns, No Load | -20  |      | 20   | %      |

| t <sub>OFF,MIN</sub>        | Minimum SW Off-Time                            |                                                                                       |      | 320  | 374  | ns     |

| D <sub>MIN</sub>            | Minimum Duty Cycle                             | FB=1 V                                                                                |      | 0    |      | %      |

| f <sub>MINF</sub>           | Minimum Frequency Clamp                        |                                                                                       | 18.2 | 25.4 | 32.7 | kHz    |

| Soft-Start                  |                                                |                                                                                       |      |      | , h  |        |

| I <sub>SS</sub>             | Soft-Start Current                             | SS=0.5 V                                                                              | 7    | 10   | 13   | μA     |

| t <sub>ON,SSMOD</sub>       | SS On-Time Modulation                          | SS<0.6 V                                                                              | 25   |      | 100  | %      |

| V <sub>SSCLAMP,NOM</sub>    | Nominal Soft-Start Voltage Clamp               | V <sub>FB</sub> =0.6 V                                                                |      | 400  |      | mV     |

| V <sub>SSCLAMP,OVL</sub>    | Soft-Start Voltage Clamp in Overload Condition | V <sub>FB</sub> =0.3 V, OC Condition                                                  |      | 40   |      | mV     |

| PFM Zero-Cı                 | ossing Detection Comparator                    |                                                                                       |      |      |      |        |

| V <sub>OFF</sub>            | ZCD Offset Voltage                             | T <sub>A</sub> =T <sub>J</sub> =25°C                                                  | -6   |      | 0    | mV     |

| Current Limi                | t                                              |                                                                                       |      |      |      |        |

| I <sub>LIM</sub>            | Valley Current Limit Accuracy                  | T <sub>A</sub> =T <sub>J</sub> =25°C, I <sub>VALLEY</sub> =18 A                       | -10  |      | 10   | %      |

| V <sub>ILIM,OFFSET</sub>    | Comparator Offset                              |                                                                                       | -1   | À    | 1    | mV     |

| K <sub>ILIM</sub>           | I <sub>LIM</sub> Set-Point Scale Factor        |                                                                                       |      | 80   |      |        |

| I <sub>LIMTC</sub>          | Temperature Coefficient                        |                                                                                       | 1    | 4000 |      | ppm/°C |

| Enable                      |                                                |                                                                                       |      |      |      |        |

| V <sub>TH+</sub>            | Rising Threshold                               |                                                                                       |      |      | 2.0  | V      |

| V <sub>TH-</sub>            | Falling Threshold                              |                                                                                       | 0.8  |      |      | V      |

| I <sub>ENLK</sub>           | Enable Pin Leakage                             | EN=1.2 V                                                                              |      |      | 100  | nA     |

| I <sub>ENLK</sub>           | Enable Pin Leakage                             | EN=5 V                                                                                |      |      | 76   | μA     |

| UVLO                        |                                                | •                                                                                     |      |      |      | 1      |

| V <sub>ON</sub>             | V <sub>CC</sub> Good Threshold Rising          |                                                                                       |      |      | 4.4  | V      |

| V <sub>HYS</sub>            | Hysteresis Voltage                             |                                                                                       |      | 160  |      | mV     |

Continued on the following page...

## **Electrical Characteristics** (Continued)

Unless otherwise noted; V\_IN=12 V, V\_OUT=1.2 V, and T\_A=T\_J=-40 to 125 °C.  $^{(4)}$

| Symbol                  | Parameter                                  | Condition                | Min. | Тур. | Max. | Unit |

|-------------------------|--------------------------------------------|--------------------------|------|------|------|------|

| Fault Protect           | etion                                      | •                        |      | •    |      | •    |

| V <sub>UVP</sub>        | PGOOD UV Trip Point                        | On FB Falling            | 86   | 89   | 92   | %    |

| V <sub>VOP1</sub>       | PGOOD OV Trip Point                        | On FB Rising             | 108  | 111  | 115  | %    |

| V <sub>OVP2</sub>       | Second OV Trip Point                       | On FB Rising; LS=On      | 118  | 122  | 125  | %    |

| R <sub>PGOOD</sub>      | PGOOD Pull-Down Resistance                 | I <sub>PGOOD</sub> =2 mA |      |      | 125  | Ω    |

| t <sub>PG,SSDELAY</sub> | PGOOD Soft-Start Delay                     |                          | 0.82 | 1.42 | 2.03 | ms   |

| I <sub>PG,LEAK</sub>    | PGOOD Leakage Current                      |                          |      |      | 1    | μA   |

| Thermal Shi             | utdown                                     |                          |      |      |      |      |

| T <sub>OFF</sub>        | Thermal Shutdown Trip Point <sup>(3)</sup> |                          |      | 155  |      | °C   |

| T <sub>HYS</sub>        | Hysteresis <sup>(3)</sup>                  |                          |      | 15   |      | °C   |

| Internal Boo            | otstrap Diode                              |                          |      |      |      |      |

| V <sub>FBOOT</sub>      | Forward Voltage                            | I <sub>F</sub> =10 mA    |      |      | 0.6  | V    |

| I <sub>R</sub>          | Reverse Leakage                            | V <sub>R</sub> =5 V      |      |      | 1000 | μΑ   |

#### Notes:

- Guaranteed by design; not production tested.

Device is 100% production tested at T<sub>A</sub>=25°C. Limits over that temperature are guaranteed by design.

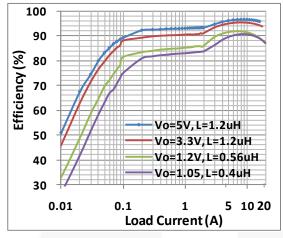

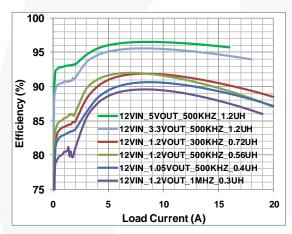

Figure 5. Efficiency vs. Load Current with  $V_{\text{IN}}$ =12 V and  $f_{\text{SW}}$ =500 kHz

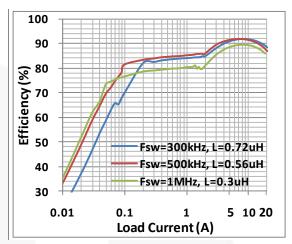

Figure 7. Efficiency vs. Load Current with V<sub>IN</sub>=12 V

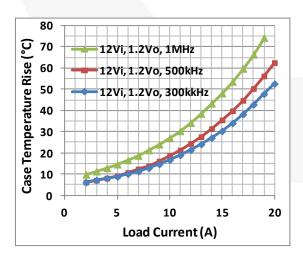

Figure 9. Case Temperature Rise vs. Load Current on 4-Layer PCB, 1 oz Copper, 7 cm x 7 cm

Figure 6. Efficiency vs. Load Current with  $V_{IN}=12\ V$  and  $V_{OUT}=1.2\ V$

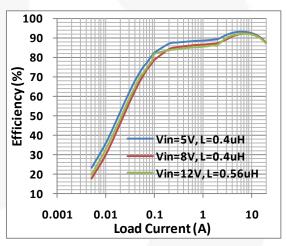

Figure 8. Efficiency vs. Load Current with  $V_{OUT}$ =1.2 V and  $f_{SW}$ =500 kHz

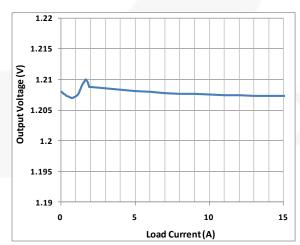

Figure 10. Load Regulation

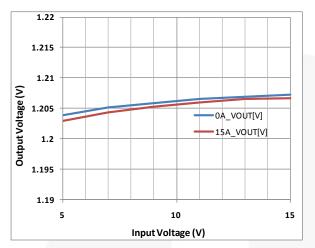

Figure 11. Line Regulation

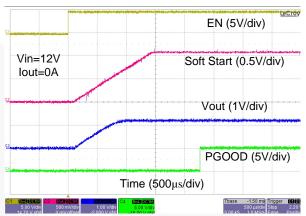

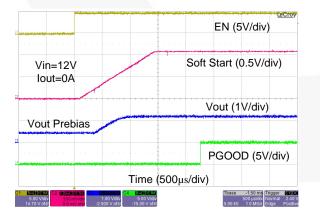

Figure 12. Startup Waveforms with 0 A Load Current

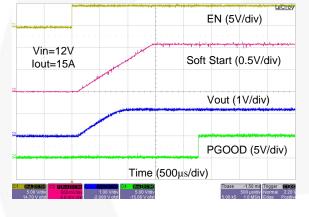

Figure 13. Startup Waveforms with 15 A

Load Current

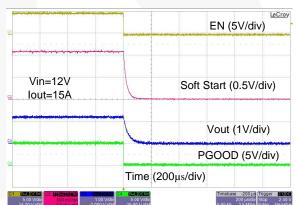

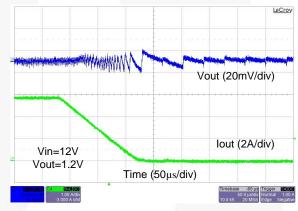

Figure 14. Shutdown Waveforms with 15 A Load Current

Figure 15. Startup Waveforms with Prebias Voltage on Output

Figure 16. Static Load Ripple at Light-Load

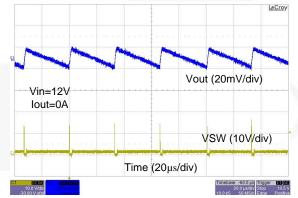

Figure 17. Static Load Ripple at Full Load

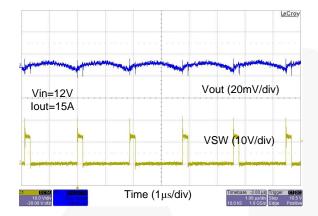

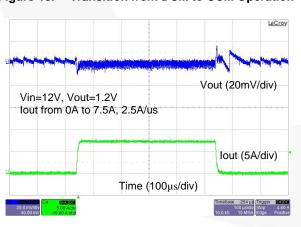

Figure 18. Transition from DCM to CCM Operation

Figure 19. Transition from CCM to DCM Operation

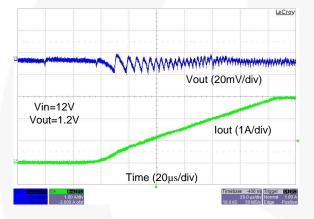

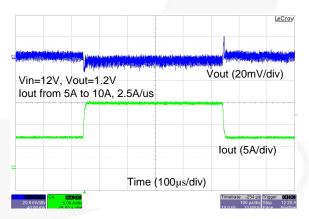

Figure 20. Load Transient from 0% to 50% Load Current

Figure 21. Load Transient from 50% to 100% Load Current

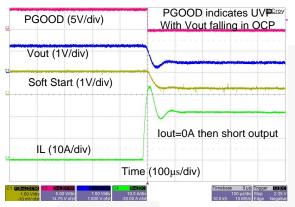

Figure 22. Over-Current Protection with Heavy Load Applied

Figure 23. Over-Voltage Protection Level 1 and Level 2

#### **Circuit Operation**

The FAN2315 uses a constant on-time modulation architecture with a  $V_{\rm IN}$  feed-forward input to accommodate a wide  $V_{\rm IN}$  range. This method provides fixed switching frequency ( $f_{\rm SW}$ ) operation when the inductor operates in Continuous Conduction Mode (CCM) and variable frequency when operating in Pulse Frequency Mode (PFM) at light loads. Additional benefits include excellent line and load transient response, cycle-by-cycle current limiting, and no loop compensation required.

At the beginning of each cycle, FAN2315 turns on the high-side MOSFET (HS) for a fixed duration ( $t_{ON}$ ). At the end of  $t_{ON}$ , HS turns off for a duration ( $t_{OFF}$ ) determined by the operating conditions. Once the FB voltage ( $V_{FB}$ ) falls below the reference voltage ( $V_{REF}$ ), a new switching cycle begins.

The modulator provides a minimum off-time ( $t_{OFF-MIN}$ ) of 320 ns to provide a guaranteed interval for low-side MOSFET (LS) current sensing and PFM operation.  $t_{OFF-MIN}$  is also used to provide stability against multiple pulsing and limits maximum switching frequency during transient events.

#### **Enable**

The enable pin is TTL compatible, which supports low-shutdown-current applications, such as notebooks.  $V_{\rm CC}$  should be applied after  $V_{\rm IN}$  /  $PV_{\rm IN}$  is applied to the circuit.

The EN pin can be directly driven by logic voltages of 5 V, 3.3 V, 2.5 V, etc. If the EN pin is driven by 5 V logic, a small current flows into the pin when the EN pin voltage exceeds the internal clamp voltage of 4.3 V. To eliminate clamp current flowing into the EN pin use a voltage divider to limit the EN pin voltage to < 4 V.

#### **Constant On-time Modulation**

The FAN2315 uses a constant on-time modulation technique, in which the HS MOSFET is turned on for a fixed time, set by the modulator, in response to the input voltage and the frequency setting resistor. This on-time is proportional to the desired output voltage, divided by the input voltage. With this proportionality, the frequency is essentially constant over the load range where inductor current is continuous.

For buck converter in Continuous-Conduction Mode (CCM), the switching frequency f<sub>SW</sub> is expressed as:

$$f_{SW} = \frac{V_{OUT}}{V_{IN} \times t_{ON}} \tag{1}$$

The on-time generator sets the on-time  $(t_{ON})$  for the high-side MOSFET, which results in the switching frequency of the regulator during steady-state operation. To maintain a relatively constant switching frequency over a wide range of input conditions, the input voltage information is fed into the on-time generator.

ton is determined by:

$$t_{ON} = \frac{C_{tON}}{I_{tON}} \times 2V \tag{2}$$

where ItON is:

$$I_{tON} = \frac{1}{10} \times \frac{V_{IN}}{R_{FREO}} \tag{3}$$

where  $R_{\text{FREQ}}$  is the frequency-setting resistor described in the Setting Switching Frequency section;  $C_{\text{toN}}$  is the internal 2.2 pF capacitor; and  $I_{\text{toN}}$  is the  $V_{\text{IN}}$  feed-forward current that generates the on-time.

The FAN2315 implements open-circuit detection on the FREQ pin to protect the output from an infinitely long on-time. In the event the FREQ pin is left floating, switching of the regulator is disabled. The FAN2315 is designed for  $V_{\text{IN}}$  input range 4.5 to 18 V,  $f_{\text{SW}}$  200 kHz to 1 MHz, resulting in an  $I_{\text{ION}}$  ratio of 1 to 16.

As the ratio of  $V_{\text{OUT}}$  to  $V_{\text{IN}}$  increases,  $t_{\text{OFF,min}}$  introduces a limit on the maximum switching frequency as calculated in the following equation, where the factor 1.2 is included in the denominator to add some headroom for transient operation:

$$f_{SW} < \frac{\left(1 - \frac{V_{OUT}}{V_{IN,min}}\right)}{1.2 \times t_{OFF,min}} \tag{4}$$

#### Soft-Start (SS)

A conventional soft-start ramp is implemented to provide a controlled startup sequence of the output voltage. A current is generated on the SS pin to charge an external capacitor. The lesser of the voltage on the SS pin and the reference voltage is used for output regulation.

To reduce  $V_{OUT}$  ripple and achieve a smoother ramp of the output voltage,  $t_{ON}$  is modulated during soft-start.  $t_{ON}$  starts at 50% of the steady-state on-time (PWM Mode) and ramps up to 100% gradually.

During normal operation, the SS voltage is clamped to 400 mV above the FB voltage. The clamp voltage drops to 40 mV during an overload condition to allow the converter to recover using the soft-start ramp once the overload condition is removed. On-time modulation during SS is disabled when an overload condition exists.

To maintain a monotonic soft-start ramp, the regulator is forced into PFM Mode during soft-start. The minimum frequency clamp is disabled during soft-start.

The nominal startup time is programmable through an internal current source charging the external soft-start capacitor  $C_{\text{SS}}$ :

$$C_{SS} = \frac{I_{SS} \times t_{SS}}{V_{REF}} \tag{5}$$

where

C<sub>SS</sub> = External soft-start programming capacitor;

$I_{SS}$  = Internal soft-start charging current source, 10  $\mu$ A:

tss = Soft-start time; and

$V_{RFF} = 600 \text{ mV}$

For example; for 1 ms startup time, C<sub>SS</sub>=15 nF.

The soft-start option can be used for ratiometric tracking.

When EN is LOW, the soft-start capacitor is discharged.

#### Startup on Pre-Bias

FAN2315 allows the regulator to start on a pre-bias output,  $V_{\text{OUT}}$ , and ensures  $V_{\text{OUT}}$  is not discharged during the soft-start operation.

To guarantee no glitches on  $V_{OUT}$  at the beginning of the soft-start ramp, the LS is disabled until the first positive-going edge of the PWM signal. The regulator is also forced into PFM Mode during soft-start to ensure the inductor current remains positive, reducing the possibility of discharging the output voltage.

#### **PVCC**

The FAN2315 requires an external source connected to PVCC to supply power to the internal gate drivers. The PVCC pin should be bypassed with a 2.2  $\mu F$  ceramic capacitor.

#### V<sub>cc</sub> Bias Supply and UVLO

The  $V_{CC}$  rail supplies power to the controller. It is generally connected to the PVCC rail through a low-pass filter of a 10  $\Omega$  resistor and 0.1  $\mu$ F capacitor to minimize any noise sources from the driver supply.

An Under-Voltage Lockout (UVLO) circuit monitors the  $V_{CC}$  voltage to ensure proper operation. Once the  $V_{CC}$  voltage is above the UVLO threshold, the part begins operation after an initialization routine of 50  $\mu$ s. There is no UVLO circuitry on either the PVCC or  $V_{IN}$  rails.

#### **Pulse Frequency Modulation (PFM)**

One of the key benefits of using a constant on-time modulation scheme is the seamless transitions in and out of Pulse Frequency Modulation (PFM) Mode. The PWM signal is not slave to a fixed oscillator and, therefore, can operate at any frequency below the target steady-state frequency. By reducing the frequency during light-load conditions, the efficiency can be significantly improved.

The FAN2315 provides a Zero-Crossing Detector (ZCD) circuit to identify when the current in the inductor reverses direction. To improve efficiency at light load, the LS MOSFET is turned off around the zero crossing to eliminate negative current in the inductor. For predictable operation entering PFM mode the controller waits for nine consecutive zero crossings before allowing the LS MOSFET to turn off.

In PFM Mode,  $f_{SW}$  varies or modulates proportionally to the load; as load decreases,  $f_{SW}$  also decreases. The switching frequency, while the regulator is operating in PFM, can be expressed as:

$$f_{SW} = \frac{2 \times L \times I_{OUT}}{t_{ON}^2 \times (V_{IN} - V_{OUT})} \times \frac{V_{OUT}}{V_{IN}}$$

(6)

where L is inductance and I<sub>OUT</sub> is output load current.

#### **Minimum Frequency Clamp**

To maintain a switching frequency above the audible range, the FAN2315 clamps the switching frequency to a minimum value of 18 kHz. The LS MOSFET is turned

on to discharge the output and trigger a new PWM cycle. The minimum frequency clamp is disabled during soft-start.

#### **Protection Features**

The converter output is monitored and protected against over-current, over-voltage, under-voltage, and high-temperature conditions.

#### **Over-Current Protection (OCP)**

The FAN2315 uses current information through the LS to implement valley-current limiting. While an OC event is detected, the HS is prevented from turning on and the LS is kept on until the current falls below the user-defined set point. Once the current is below the set point, the HS is allowed to turn on.

During an OC event, the output voltage may droop if the load current is greater than the current the converter is providing. If the output voltage drops below the UV threshold, an overload condition is triggered. During an overload condition, the SS clamp voltage is reduced to 40 mV and the on-time is fixed at the steady-state duration. By nature of the control method; as V<sub>OUT</sub> drops, the switching frequency is lower due to the reduced rate of inductor current decay during the off-time.

The ILIM pin has an open-detection circuit to provide protection against operation without a current limit.

#### **Under-Voltage Protection (UVP)**

If  $V_{FB}$  is below the under-voltage threshold of -11%  $V_{REF}$  (534 mV), the part enters UVP and PGOOD pulls LOW.

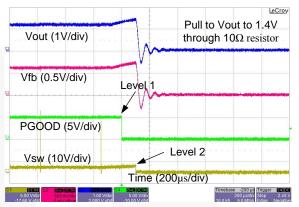

#### Over-Voltage Protection (OVP)

There are two levels of OV protection: +11% and +22%. During an OV event, PGOOD pulls LOW.

When  $V_{FB}$  is > +11% of  $V_{REF}$  (666 mV), both HS and LS turn off. By turning off the LS during an OV event,  $V_{OUT}$  overshoot can be reduced when there is positive inductor current by increasing the rate of discharge. Once the  $V_{FB}$  voltage falls below  $V_{REF}$ , the latched OV signal is cleared and operation returns to normal.

A second over-voltage detection is implemented to protect the load from more serious failure. When  $V_{FB}$  rises +22% above the  $V_{REF}$  (732 mV), the HS turns off, but the LS is forced on until a power cycle on VCC.

#### **Over-Temperature Protection (OTP)**

FAN2315 incorporates an over-temperature protection circuit that disables the converter when the die temperature reaches 155°C. The IC restarts when the die temperature falls below 140°C.

#### Power Good (PGOOD)

The PGOOD pin serves as an indication to the system that the output voltage of the regulator is stable and within regulation. Whenever  $V_{\text{OUT}}$  is outside the regulation window or the regulator is at overtemperature (UV, OV, and OT), the PGOOD pin is pulled LOW.

PGOOD is an open-drain output that asserts LOW when  $V_{\text{OUT}}$  is out of regulation or when OT is detected.

## **Application Information**

#### **Stability**

Constant on-time stability consists of two parameters: stability criterion and sufficient signal at V<sub>FB</sub>.

Stability criterion is given by:

$$R_{ESR} \times C_{OUT} \gg \frac{t_{ON}}{2} \tag{7}$$

Sufficient signal requirement is given by:

$$\Delta I_{IND} \times R_{ESR} > \Delta V_{FB}$$

(8)

where  $\Delta I_{\text{IND}}$  is the inductor current ripple and  $\Delta V_{\text{FB}}$  is the ripple voltage on  $V_{\text{FB}}$ , which should be  $\geq$ 12 mV.

In certain applications, especially designs utilizing only ceramic output capacitors, there may not be sufficient ripple magnitude available on the feedback pin for stable operation. In this case, an external circuit can be added to inject ripple voltage into the FB pin.

There are some specific considerations when selecting the RCC ripple injector circuit. For typical applications, the value of C4 can be selected as 0.1  $\mu$ F and approximate values for R2 and C5 can be determined using the following equations.

R2 must be small enough to develop 12 mV of ripple:

$$R2 < \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN} \times 0.012V \times C4 \times f_{SW}}$$

$$\tag{9}$$

R2 must be selected such that the R2C4 time constant enables stable operation:

$$R2 < \frac{0.33 \times 2\pi \times f_{SW} \times L_{OUT} \times C_{OUT}}{C4}$$

(10)

The minimum value of C5 can be selected to minimize the capacitive component of ripple appearing on the feedback pin:

$$C5_{MIN} = \frac{L_{OUT} \times C_{OUT} \times (R3 + R4)}{R2 \times R3 \times R4 \times C4}$$

(11)

Using the minimum value of C5 generally offers the best transient response, and 100 pF is a good initial value in many applications. Under some operating conditions, excessive pulse jitter may be observed. To reduce jitter and improve stability, the value of C5 can be increased:

$$C5 \ge 2 \times C5_{MIN} \tag{12}$$

#### 5 V PVcc

The PV<sub>CC</sub> is supplied from an external source to provide power to the drivers and V<sub>CC</sub>. It is crucial to keep this pin decoupled to PGND with a  $\geq 1~\mu F$  X5R or X7R ceramic capacitor. Because V<sub>CC</sub> powers internal analog circuit, it is filtered from PV<sub>CC</sub> with a 10  $\Omega$  resistor and 0.1  $\mu F$  X7R decoupling ceramic capacitor to AGND.

#### Setting the Output Voltage (Vout)

The output voltage  $V_{\text{OUT}}$  is regulated by initiating a highside MOSFET on-time interval when the valley of the divided output voltage appearing at the FB pin reaches  $V_{\text{REF}}$ . Since this method regulates at the valley of the output ripple voltage, the actual DC output voltage on  $V_{\text{OUT}}$  is offset from the programmed output voltage by the average value of the output ripple voltage. The initial  $V_{\text{OUT}}$  setting of the regulator can be programmed from 0.6 V to 5.5 V by an external resistor divider (R3 and R4):

$$R4 = \frac{R3}{\left(\frac{V_{OUT}}{V_{RFF}}\right) - 1} \tag{13}$$

where V<sub>REF</sub> is 600 mV.

For example; for 1.2 V  $V_{OUT}$  and 10  $k\Omega$  R3, then R4 is 10  $k\Omega$ . For 600 mV  $V_{OUT}$ , R4 is left open. VFB is trimmed to a value of 596 mV when  $V_{REF}$ =600 mV, so the final output voltage, including the effect of the output ripple voltage, can be approximated by the equation:

$$V_{OUT} = V_{FB} \times \left[ 1 + \frac{R3}{R4} \right] + \left[ \frac{V_{rip}}{2} \right]$$

(14)

#### Setting the Switching Frequency (fsw)

f<sub>SW</sub> is programmed through external R<sub>FREQ</sub> as follows:

$$R_{FREQ} = \frac{V_{OUT}}{20 \times C_{tON} \times f_{SW}} \tag{15}$$

where  $C_{\text{tON}}$ =2.2 pF internal capacitor that generates  $t_{\text{ON}}$ . For example; for  $f_{\text{SW}}$ =500 kHz and  $V_{\text{OUT}}$ =1.2 V, select a standard value for  $R_{\text{FREO}}$ =54.9 k $\Omega$ .

#### **Inductor Selection**

The inductor is typically selected based on the ripple current ( $\Delta I_L$ ), which is approximately 25% to 45% of the maximum DC load. The inductor current rating should be selected such that the saturation and heating current ratings exceed the intended currents encountered in the application over the expected temperature range of operation. Regulators that require fast transient response use smaller inductance and higher current ripple; while regulators that require higher efficiency keep ripple current on the low side.

The inductor value is given by:

$$L = \frac{(V_{IN} - V_{OUT})}{\Delta I_L \times f_{SW}} \times \frac{V_{OUT}}{V_{IN}}$$

(16)

For example: for 12 V V<sub>IN</sub>, 1.2 V V<sub>OUT</sub>, 15 A load, 25%  $\Delta$ I<sub>L</sub>, and 500 kHz f<sub>SW</sub>; L is 576 nH, and a standard value of 560 nH is selected.

#### **Input Capacitor Selection**

Input capacitor  $C_{\text{IN}}$  is selected based on voltage rating, RMS current  $I_{\text{CIN}(\text{RMS})}$  rating, and capacitance. For capacitors having DC voltage bias derating, such as ceramic capacitors, higher rating is strongly recommended. RMS current rating is given by:

$$I_{CIN(RMS)} = I_{LOAD-MAX} \times \sqrt{D \times (1-D)}$$

(17)

where  $I_{\text{LOAD-MAX}}$  is the maximum load current and D is the duty cycle  $V_{\text{OUT}}/V_{\text{IN}}.$  The maximum  $I_{\text{CIN}(\text{RMS})}$  occurs at 50% duty cycle.

The capacitance is given by:

$$C_{IN} = \frac{I_{LOAD-MAX} \times D \times (1 - D)}{f_{SW} \times \Delta V_{IN}}$$

(18)

where  $\Delta V_{IN}$  is input voltage ripple, normally 1% of  $V_{IN}$ .

For example; for  $V_{IN}$ =12 V,  $\Delta V_{IN}$ =120 mV,  $V_{OUT}$ =1.2 V, 15 A load, and  $f_{SW}$ =500 kHz;  $C_{IN}$  is 22.5  $\mu$ F and  $I_{CIN(RMS)}$  is 4.5  $A_{RMS}$ . Select four 10  $\mu$ F 25V-rated ceramic capacitors with X7R or similar dielectric, recognizing that the capacitor DC bias characteristic indicates that the capacitance value falls approximately 40% at  $V_{IN}$ =12 V, with a resultant small increase in  $\Delta V_{IN}$  ripple voltage above 120 mV used in the calculation. Also, each 10  $\mu$ F can carry over 3  $A_{RMS}$  in the frequency range from 100 kHz to 1 MHz, exceeding the input capacitor current rating requirements. An additional 0.1  $\mu$ F capacitor may be needed to suppress noise generated by high frequency switching transitions.

#### **Output Capacitor Selection**

Output capacitor  $C_{\text{OUT}}$  is also selected based on voltage rating, RMS current  $I_{\text{COUT}(\text{RMS})}$  rating, and capacitance. For capacitors having DC voltage bias derating, such as ceramic capacitors, higher rating is highly recommended.

When calculating  $C_{\text{OUT}}$ , usually the dominant requirement is the current load step transient. If the unloading transient requirement ( $I_{\text{OUT}}$  transitioning from HIGH to LOW), is satisfied, then the load transient ( $I_{\text{OUT}}$  transitioning LOW to HIGH), is also usually satisfied. The unloading  $C_{\text{OUT}}$  calculation, assuming  $C_{\text{OUT}}$  has negligible parasitic resistance and inductance in the circuit path, is given by:

$$C_{OUT} = L \times \frac{I_{MAX}^2 - I_{MIN}^2}{(V_{OUT} + \Delta V_{OUT})^2 - V_{OUT}^2}$$

(19)

where  $I_{MAX}$  and  $I_{MIN}$  are maximum and minimum load steps, respectively and  $\Delta V_{OUT}$  is the voltage overshoot, usually specified at 3 to 5%.

For example: for V<sub>I</sub>=12 V, V<sub>OUT</sub>=1.2 V, 10 A I<sub>MAX</sub>, 5 A I<sub>MIN</sub>,  $f_{SW}$ =500 kHz, L<sub>OUT</sub>=560 nH, and 4%  $\Delta$ V<sub>OUT</sub> deviation of 48 mV; the C<sub>OUT</sub> value is calculated to be 356  $\mu$ F. This capacitor requirement can be satisfied using eight 47  $\mu$ F, 6.3 V-rated X5R ceramic capacitors. This calculation applies for load current slew rates that are faster than the inductor current slew rate, which can be defined as V<sub>OUT</sub>/L during the load current removal.

#### **Setting the Current Limit**

Current limit is implemented by sensing the inductor valley current across the LS MOSFET  $V_{DS}$  during the LS on-time. The current limit comparator prevents a new

on-time from being started until the valley current is less than the current limit.

The set point is configured by connecting a resistor from the ILIM pin to the SW pin. A trimmed current is output onto the ILIM pin, which creates a voltage across the resistor. When the voltage on ILIM goes negative, an over-current condition is detected.

R<sub>ILIM</sub> is calculated by:

$$R_{ILIM} = 1.08 \times K_{ILIM} \times I_{VALLEY} \tag{20}$$

where  $K_{\text{ILIM}}$  is the current source scale factor, and  $I_{\text{VALLEY}}$  is the inductor valley current when the current limit threshold is reached. The factor 1.08 accounts for the temperature offset of the LS MOSFET compared to the control circuit.

With the constant on-time architecture, HS is always turned on for a fixed on-time; this determines the peak-to-peak inductor current.

Current ripple  $\Delta I$  is given by:

$$\Delta I_L = \frac{(V_{IN} - V_{OUT}) \times t_{ON}}{L} \tag{21}$$

From the equation above, the worst-case ripple occurs during an output short circuit (where  $V_{\text{OUT}}$  is 0 V). This should be taken into account when selecting the current limit set point.

The FAN2315 uses valley-current sensing, the current limit ( $I_{\text{ILIM}}$ ) set point is the valley ( $I_{\text{VALLEY}}$ ).

The valley current level for calculating R<sub>ILIM</sub> is given by:

$$I_{VALLEY} = I_{LOAD (CL)} - \frac{\Delta I_L}{2}$$

(22)

where  $I_{LOAD\ (CL)}$  is the DC load current when the current limit threshold is reached.

For example: In a converter designed for 15 A steady-state operation and 4.5 A current ripple, the current-limit threshold could be selected at 120% of  $I_{LOAD,(MAX)}$  to accommodate transient operation and inductor value decrease under loading. As a result,  $I_{LOAD,(MAX)}$  is 18 A,  $I_{VALLEY}$ =15.75 A, and  $R_{ILIM}$  is selected as the standard value of 1.37 k $\Omega$ .

#### **Boot Resistor**

In some applications, especially with higher input voltage, the  $V_{SW}$  ring voltage may exceed derating guidelines of 80% to 90% of absolute rating for  $V_{SW}.$  In this situation, a resistor can be connected in series with the boot capacitor (C3 in Figure 1) to reduce the turn-on speed of the high-side MOSFET to reduce the amplitude of the  $V_{SW}$  ring voltage.

## **Printed Circuit Board (PCB) Layout Guidelines**

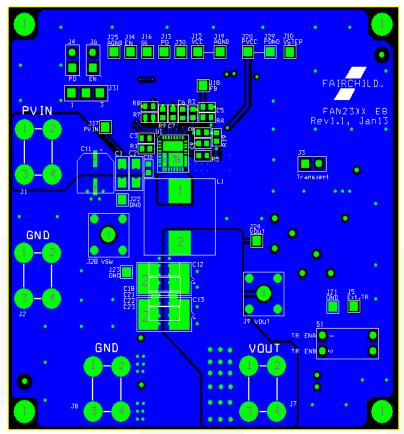

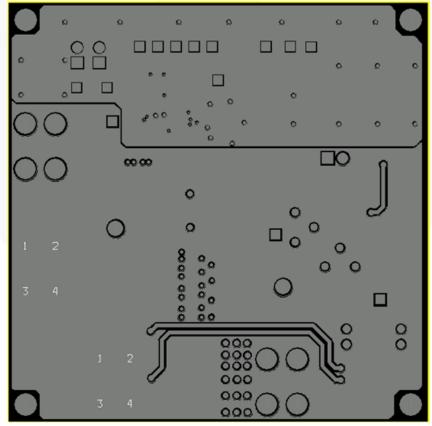

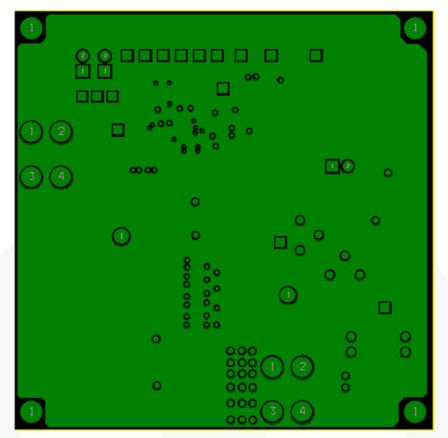

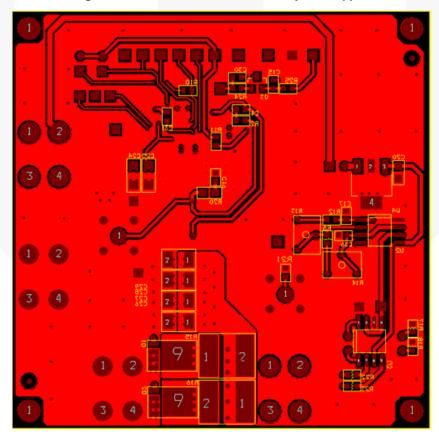

The following points should be considered before beginning a PCB layout using the FAN2315. A sample PCB layout from the evaluation board is shown in Figure 24 through Figure 27 following the layout guidelines.

Power components consisting of input capacitors, output capacitors, inductor, and devices should be placed on a common side of the PCB in close proximity to each other and connected using surface copper.

Sensitive analog components including SS, FB, ILIM, FREQ, and EN should be placed away from the high-voltage switching circuits such as SW and BOOT, and connected to their respective pins with short traces.

The inner PCB layer closest to the device should have Power Ground (PGND) under the power processing portion of the device (PVIN, SW, and PGND). This inner PCB layer should have a separate Analog Ground (AGND) under the P1 pad and the associated analog components. AGND and PGND should be connected together near the IC between PGND pins 18-21 and AGND pin 23 which connects to P1 thermal pad.

The AGND thermal pad (P1) should be connected to AGND plane on inner layer using four 0.25 mm vias spread under the pad. No vias are included under PVIN (P2) and SW (P3) to maintain the PGND plane under the power circuitry intact.

Power circuit loops that carry high currents should be arranged to minimize the loop area. Primary focus

should be directed to minimize the loop for current flow from the input capacitor to PVIN, through the internal MOSFETs, and returning to the input capacitor. The input capacitor should be placed as close to the PVIN terminals as possible.

The current return path from PGND at the low-side MOSFET source to the negative terminal of the input capacitor can be routed under the inductor and also through vias that connect the input capacitor and low-side MOSFET source to the PGND region under the power portion of the IC.

The SW node trace which connects the source of the high-side MOSFET and the drain of the low-side MOSFET to the inductor should be short and wide.

To control the voltage across the output capacitor, the output voltage divider should be located close to the FB pin, with the upper FB voltage divider resistor connected to the positive side of the output capacitor, and the bottom resistor should be connected to the AGND portion of the device.

When using ceramic capacitor solutions with external ramp injection circuitry (R2, C4, C5 in Figure 1), R2 and C4 should be connected near the inductor, and coupling capacitor C5 should be placed near FB pin to minimize FB pin trace length.

Decoupling capacitors for PVCC and VCC should be located close to their respective device pins.

SW node connections to BOOT, ILIM, and ripple injection resistor R2 should be made through separate traces.

Figure 24. Evaluation Board Top Layer Copper

Figure 25. Evaluation Board Inner Layer 1 Copper

Figure 26. Evaluation Board Inner Layer 2 Copper

Figure 27. Evaluation Board Bottom Layer Copper

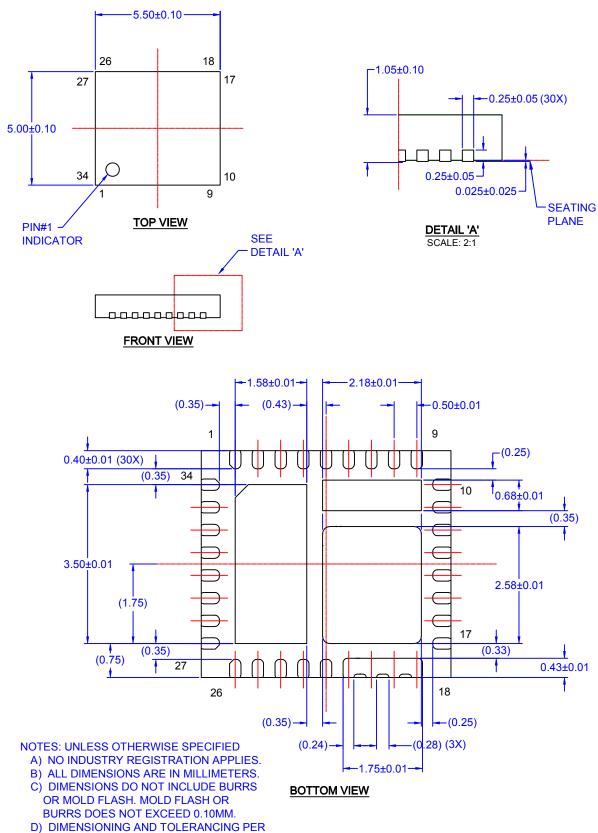

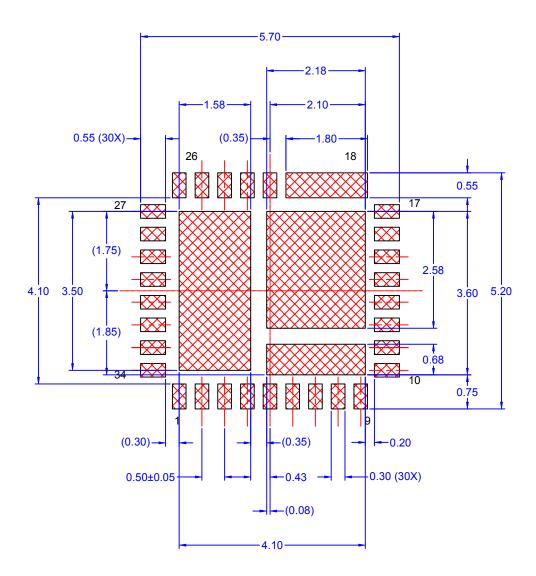

- ASME Y14.5M-2009.

- E) DRAWING FILE NAME: MKT-PQFN34AREV2

- F) FAIRCHILD SEMICONDUCTOR

LAND PATTERN RECOMMENDATION

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and h

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative