**SA1638**

#### **DESCRIPTION**

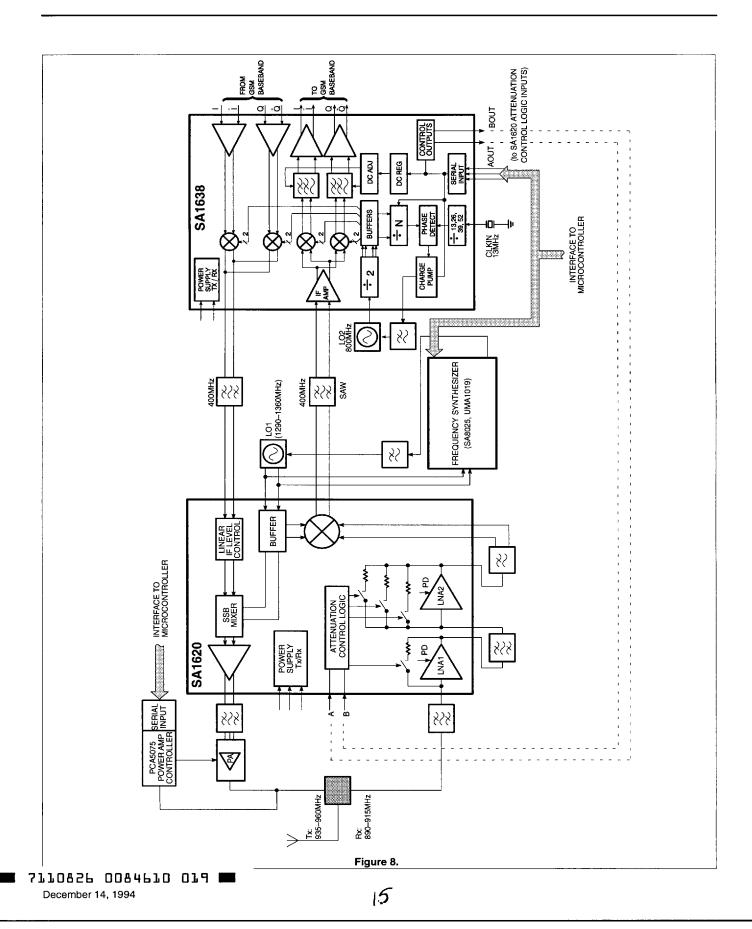

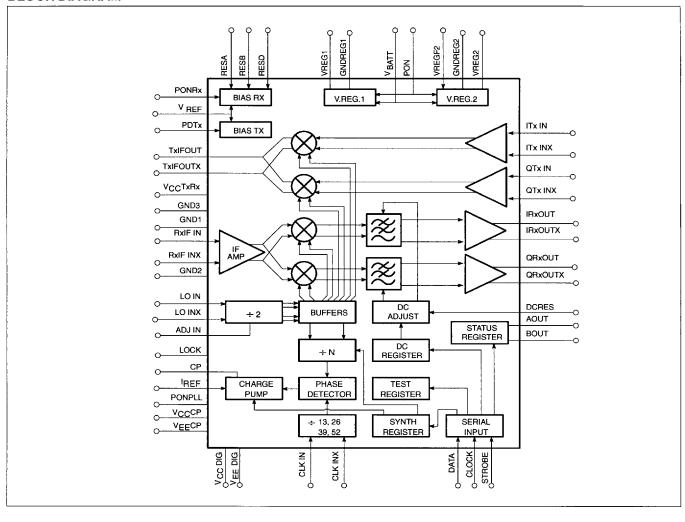

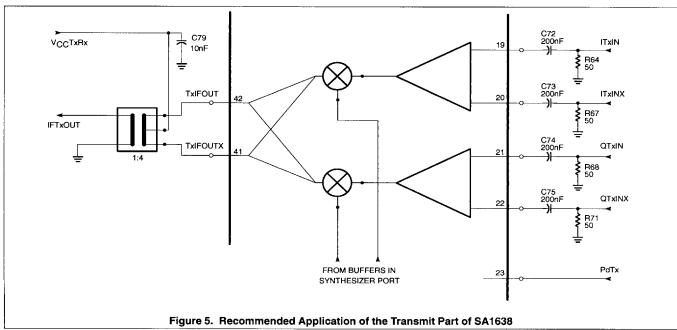

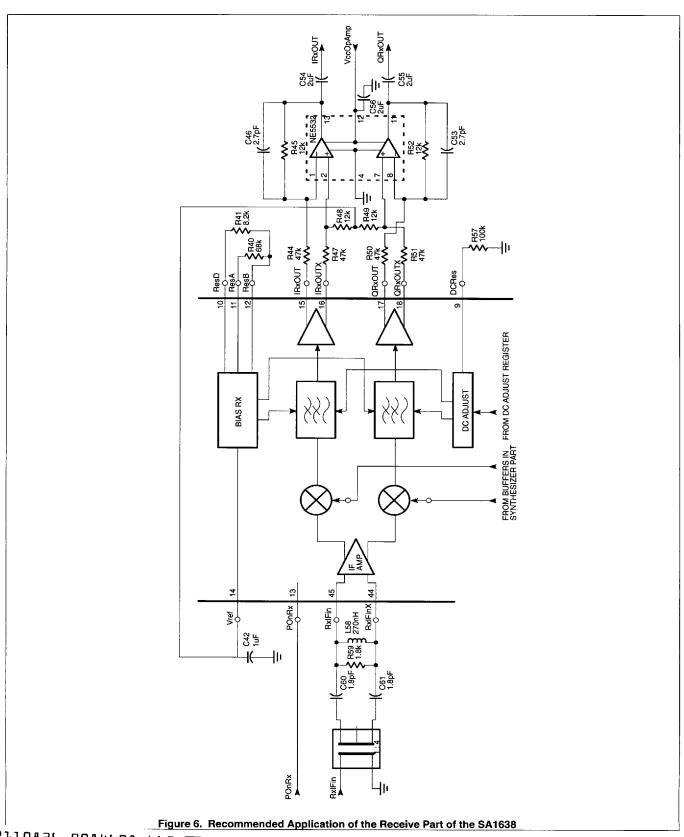

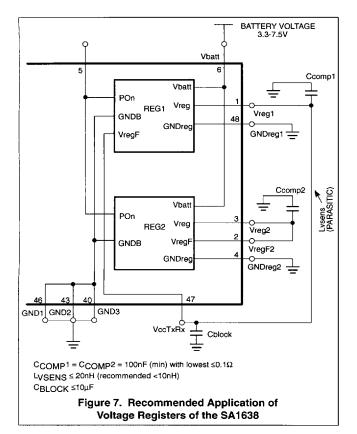

The SA1638 is a combined Rx and Tx IF I/Q circuit. The receive path contains an IF amplifier, a pair of quadrature down-mixers, and a pair of baseband filters and amplifiers. A second pair of mixers in the transmit path transposes a quadrature baseband input up to the IF frequency. An external VCO signal is divided down internally and buffered to provide quadrature local oscillator signals for the mixers. A further divider chain, reference divider and phase detector are provided to avoid the need for an external IF synthesizer. Rx or Tx path or the entire circuit may be powered down by logic inputs. On-board voltage regulators are provided to allow direct connection to a battery supply.

#### **FEATURES**

- Direct supply: 3.3V to 7.5V

- Two DC regulators giving 3.0V output

- Low current consumption: 14mA for Rx or 18mA for Tx

- Input/output IF frequency from 70-500MHz

- Internal IF PLL for synthesizing the local oscillator signal

- High performance on-board integrated receive filters with bandwidth tunable between 50kHz to 1MHz

- Switchable alternative bandwidth setting available to allow channel bandwidth flexibility in operation

- Designed for a widely used I and Q baseband GSM interface

- · Control registers power up in a default state

- Optional DC offset trim capability to <200mV</li>

- Only a standard reference input frequency required, choice of 13, 26, 39 or 52MHz

- Fully compatible with SA1620 GSM RF front-end

#### **APPLICATIONS**

- IF circuitry for GSM 900MHz hand-held units

- IF circuitry for PCN (DCS1800) hand-held units

- Quadrature up and down mixer stage

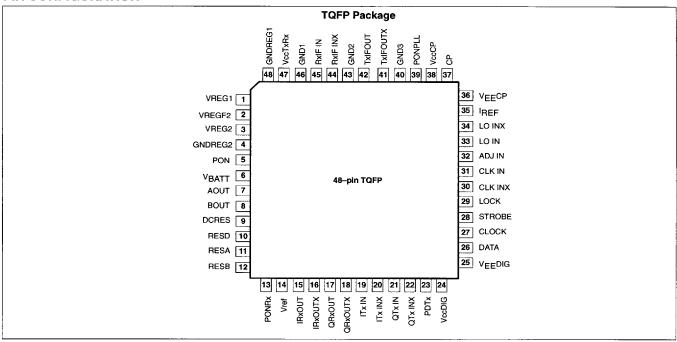

#### PIN CONFIGURATION

#### ORDERING INFORMATION

| DESCRIPTION                       | TEMPERATURE RANGE | ORDER CODE | DWG#  |

|-----------------------------------|-------------------|------------|-------|

| 48-Pin Thin Quad Flat Pack (TQFP) | -40 to +85°C      | SA1638BE   | 1706B |

7110826 0084596 919 ■

SA1638

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL             | PARAMETER                           | RATING     | UNITS |

|--------------------|-------------------------------------|------------|-------|

| V <sub>CCXXX</sub> | Supply voltages                     | 2.7 to 5.5 | ٧     |

| V <sub>CC</sub> CP | Charge pump supply voltage          | 2.9 to 5.5 | V     |

| V <sub>BATT</sub>  | Battery voltage                     | 3.3 to 7.5 | ٧     |

| T <sub>A</sub>     | Operating ambient temperature range | -40 to +85 | °C    |

### **BLOCK DIAGRAM**

SA1638

### **PIN DESCRIPTIONS**

| Pin No. | Pin Name             | Description                                                                                                    |

|---------|----------------------|----------------------------------------------------------------------------------------------------------------|

| 1       | VREG1                | Output voltage of regulator 1                                                                                  |

| 2       | VREGF2               | Feedback of regulator 2                                                                                        |

| 3       | VREG2                | Output voltage of regulator 2                                                                                  |

| 4       | GNDREG2              | Ground of regulator 2                                                                                          |

| 5       | PON                  | Power-on input for voltage regulators 1 and 2 (active high)                                                    |

| 6       | V <sub>BATT</sub>    | Input voltage for regulators 1 and 2                                                                           |

| 7       | AOUT                 | Control output (for SA1620 attenuation select A pin)                                                           |

| 8       | BOUT                 | Control output (for SA1620 attenuation select B pin)                                                           |

| 9       | DCRES                | Reference resistor for DC offset circuit                                                                       |

| 10      | RESD                 | Additional external current defining resistor for filters                                                      |

| 11      | RESA                 | Principal external current defining resistor for filters                                                       |

| 12      | RESB                 | Principal external current defining resistor for filters                                                       |

| 13      | PONRx                | Power-on input for Rx (active high)                                                                            |

| 14      | V <sub>REF</sub>     | Reference voltage                                                                                              |

| 15      | IRXOUT               | In-phase differential receive baseband output                                                                  |

| 16      | IRxOUTX              | In-phase differential receive baseband output                                                                  |

| 17      | QRxOUT               | Quadrature differential receive baseband output                                                                |

| 18      | QRxOUTX              | Quadrature differential receive baseband output                                                                |

| 19      | ITx IN               | In-phase differential transmit baseband input                                                                  |

| 20      | ITx INX              | In-phase differential transmit baseband input                                                                  |

| 21      | QTx IN               | Quadrature differential transmit baseband input                                                                |

| 22      | QTx INX              | Quadrature differential transmit baseband input                                                                |

| 23      | PDTx                 | Power-on for transmitter (active low)                                                                          |

| 24      | V <sub>CC</sub> DIG  | Digital circuit supply                                                                                         |

| 25      | V <sub>EE</sub> DIG  | Digital ground                                                                                                 |

| 26      | DATA                 | Serial data input                                                                                              |

| 27      | CLOCK                | Serial clock input                                                                                             |

| 28      | STROBE               | Serial strobe input                                                                                            |

| 29      | LOCK                 | Test control/synthesizer lock indicator                                                                        |

| 30      | CLK INX              | Differential reference divider input                                                                           |

| 31      | CLK IN               | Differential reference divider input                                                                           |

| 32      | ADJ IN               | Used for test only                                                                                             |

| 33      | LOIN                 | Differential LO input                                                                                          |

| 34      | LO INX               | Differential LO input                                                                                          |

| 35      | I <sub>REF</sub>     | Reference current for charge pump                                                                              |

| 36      | V <sub>EE</sub> CP   | Charge pump ground                                                                                             |

| 37      | CP CP                | Charge pump output                                                                                             |

| 38      | V <sub>CC</sub> CP   | Charge pump circuit supply                                                                                     |

| 39      | POnPLL               | Power-on input for synthesizer circuits (active high)                                                          |

| 40      | Gnd3                 | Ground (internal connection to GND1 and GND2)                                                                  |

| 41      | TxIFOUTX             | Differential transmit IFoutput                                                                                 |

| 42      | TxIFOUT              | Differential transmit iFoutput                                                                                 |

| 43      | GND2                 | Ground (internal connection to GND1 and GND3)                                                                  |

| 44      | RxIF INX             | Differential receive IF input                                                                                  |

| 45      | RxIF IN              | Differential receive IF input                                                                                  |

| 46      | GND1                 | Ground (internal connection to GND2 and GND3)                                                                  |

| 47      | V <sub>CC</sub> TxRx | Transmit and receive circuits supply voltage (also feedback of Regulator 1)                                    |

| 48      | GNDREG1              | Ground of regulator 1                                                                                          |

|         |                      | D protection diodes at Pins 41 and 42. Thus, open collector outputs may have increased DC voltage or higher AC |

NOTE: There are no ESD protection diodes at Pins 41 and 42. Thus, open collector outputs may have increased DC voltage or higher Alpeak voltage.

■ 7110826 0084598 **791** ■

SA1638

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL            | PARAMETER                                            | RATING                           | UNITS |

|-------------------|------------------------------------------------------|----------------------------------|-------|

| V <sub>CCXX</sub> | Supply voltages                                      | -0.3 to +6.0                     | ٧     |

| $V_{BATT}$        | Battery voltage                                      | -0.3 to +8.0                     | V     |

| V <sub>IN</sub>   | Voltage applied to any other pin                     | -0.3 to (V <sub>CCXX</sub> +0.3) | V     |

| ΔVG               | Any GND pin to any other GND pin                     | 0                                | V     |

| PD                | Power dissipation, T <sub>A</sub> = 25°C (still air) | 300                              | mW    |

| T <sub>JMAX</sub> | Maximum operating junction temperature               | 150                              | °C    |

| P <sub>MAX</sub>  | Maximum power input/output                           | +20                              | dBm   |

| Т <sub>STG</sub>  | Storage temperature range                            | -65 to +150                      | °C    |

#### **Voltage Regulators**

$T_A = 25$ °C,  $P_{ON} = 3V$ ,  $P_{ON}RX = 0V$ , PDTX = 3V, PDPLL = 0V,  $V_{BATT} = 3.3V$ ,  $I_{LOAD} = 15$ mA,  $V_{REG}1$  connected to  $V_{CC}TxRx$ ,  $V_{REG}2$  connected to  $V_{REG}$ ; unless otherwise stated.

| SYMBOL                                    | PARAMETER                                | TEST CONDITIONS                      |           | UNITS |      |         |  |

|-------------------------------------------|------------------------------------------|--------------------------------------|-----------|-------|------|---------|--|

| STMBUL                                    | PARAMETER                                | TEST CONDITIONS                      | Min Typ I |       | Max  | T UNITS |  |

| V <sub>REG</sub> 1,<br>V <sub>REG</sub> 2 | Nominal V <sub>OUT</sub>                 |                                      | 2.85      |       | 3.15 | ٧       |  |

| V <sub>BATT</sub>                         |                                          |                                      | 3.3       |       | 7.5  | V       |  |

| ILOAD <sup>1</sup>                        | V <sub>REG</sub> 1 or V <sub>REG</sub> 2 |                                      |           |       | 30   | mA      |  |

| IBATT                                     |                                          | I <sub>LOAD</sub> = 0mA              |           | 7     |      | mA      |  |

| IBATT PD                                  | $P_{ON} = 0V$                            | I <sub>LOAD</sub> = 0mA              |           |       | 75   | μΑ      |  |

| C <sub>REG</sub> 12                       | V <sub>REG</sub> 1 cap load              |                                      | 0.1       |       | 1000 | μF      |  |

| C <sub>REG</sub> 2 <sup>2</sup>           | V <sub>REG</sub> 2 cap load              |                                      | 0.1       |       | 500  | μF      |  |

| BW                                        | Bandwidth                                |                                      | 100       |       |      | kHz     |  |

| LINEREG                                   | Line regulation                          | DC, V <sub>BATT</sub> = 3.3V to 7.5V | -0.4      |       | 0.4  | %       |  |

| LOADREG                                   | Load regulation                          | I <sub>LOAD</sub> = 15mA to 30mA     | -5        |       | 5    | %       |  |

- At T<sub>j</sub> ≥ 150°C a thermal switch reduces the output current.

Recommended load capacitors: In every case C<sub>REG</sub>1 = C<sub>REG</sub>2 = 100nF to ground with series resistance ≤0.1Ω. Additional capacitor optional  $\leq 1000 \mu F$  with series resistance  $\leq 5\Omega$ .

- Feedthrough attenuation from the logic input P<sub>ON</sub> to the outputs V<sub>REG</sub>1 and V<sub>REG</sub>2: ≥40dB.

Maximum dissipation is determined by the operating ambient temperature and the thermal resistance, θ<sub>JA</sub>. 48-pin TQFP: θ<sub>JA</sub> = 67°C/W.

SA1638

#### DC ELECTRICAL CHARACTERISTICS

$V_{CC}XXX = PONRx = PONPLL = +3V; \ V_{EE}XXX = GND1 = GND2 = GND3 = PDTx = 0V; \ T_A = 25^{\circ}C, \ unless \ otherwise \ stated.$

| CVMDOL            | DADAMETED                                                              | TEST COMPITIONS                    |                           | LIMITS |                           |       |  |  |  |  |

|-------------------|------------------------------------------------------------------------|------------------------------------|---------------------------|--------|---------------------------|-------|--|--|--|--|

| SYMBOL            | PARAMETER                                                              | TEST CONDITIONS                    | MIN                       | TYP    | MAX                       | UNITS |  |  |  |  |

| lcc               | Supply current                                                         |                                    | 1                         |        |                           |       |  |  |  |  |

|                   | Rx and IF synthesizer active                                           | PONRx = PONPLL = PDTx = Hi         |                           | 14     | 17                        |       |  |  |  |  |

|                   | Tx and IF synthesizer active                                           | PONRx = PDTx = Low;<br>PONPLL = Hi |                           | 18     | 21                        | mA    |  |  |  |  |

|                   | Power-down mode                                                        | PONRx = PONPLL = Low;<br>PDTx = Hi |                           | .007   |                           |       |  |  |  |  |

| $V_{REF}$         | Reference voltage                                                      | Generated internally               |                           | 1.5    |                           | ٧     |  |  |  |  |

| IV <sub>REF</sub> | V <sub>REF</sub> I <sub>SINK</sub> I <sub>SOURCE</sub>                 |                                    |                           |        | 100<br>250                | μΑ    |  |  |  |  |

| Digital inp       | outs (PDTx, P <sub>ON</sub> Rx, P <sub>ON</sub> PLL, P <sub>ON</sub> ) |                                    |                           |        |                           |       |  |  |  |  |

| V <sub>IH</sub>   | High level input voltage range                                         |                                    | 2.0                       |        | V <sub>CC</sub> TxRx      | ٧     |  |  |  |  |

| V <sub>IL</sub>   | Low level input voltage range                                          |                                    | 0                         |        | 0.8                       | ٧     |  |  |  |  |

| Digital inp       | uts (Clock, Data, Strobe)                                              |                                    |                           |        |                           |       |  |  |  |  |

| V <sub>IH</sub>   | High level input voltage range                                         |                                    | 0.7 × V <sub>CC</sub> DIG |        | V <sub>CC</sub> Dig       | V     |  |  |  |  |

| V <sub>IL</sub>   | Low level input voltage range                                          |                                    | 0                         |        | 0.3 × V <sub>CC</sub> DIG | ٧     |  |  |  |  |

| Digital out       | tputs (LOCK, AOUT, BOUT)                                               |                                    | •                         |        |                           |       |  |  |  |  |

| V <sub>OH</sub>   | Output voltage HIGH                                                    | 1 <sub>O</sub> = -2mA              | V <sub>CC</sub> DIG - 0.4 |        |                           | ٧     |  |  |  |  |

| V <sub>OL</sub>   | Output voltage LOW                                                     | I <sub>O</sub> = 2mA               |                           |        | 0.4                       | ٧     |  |  |  |  |

### **AC ELECTRICAL CHARACTERISTICS**

$V_{CC}XXX = P_{ON}PLL = +3V; V_{EE}XXX = GND1 = GND2 = GND3 = PDTx = 0V; \\ f_{LO} = 800MHz; \\ T_{A} = 25^{\circ}C \text{ unless otherwise stated.} \\$

| SYMBOL            | PARAMETER                              | TEST COMPLETIONS                                   |     | LIMITS              |                          | UNITS             |  |

|-------------------|----------------------------------------|----------------------------------------------------|-----|---------------------|--------------------------|-------------------|--|

| STMBUL            | PARAMETER                              | TEST CONDITIONS                                    | MIN | TYP                 | MAX                      | UNITS             |  |

| IF Transm         | it Modulator                           | •                                                  |     |                     | •                        |                   |  |

| BW                | Input modulation bandwidth             | 200Ω source impedance                              |     | 2                   |                          | MHz               |  |

|                   | Input signal amplitude                 | Centered on V <sub>REF</sub> (V)                   |     | V <sub>REF</sub> /2 | V <sub>REF</sub> /1.75   | V <sub>PK</sub>   |  |

| THD               | Total harmonic distortion <sup>1</sup> |                                                    |     | -50                 |                          | dBc               |  |

| R <sub>INTx</sub> | Input resistance                       | Between pins: ITxIn and ITxInX or QTxIn and QTxInX | 10  |                     |                          | kΩ                |  |

| C <sub>INTx</sub> | Input capacitance                      | At ITxin, ITxinX,<br>QTxin, QTxinX                 |     |                     | 10                       | pF                |  |

|                   | Output saturation limit                |                                                    |     |                     | V <sub>CC</sub> TxRx-0.3 | ٧                 |  |

|                   | DC output current                      | At pins TxIFOUT and TxIFOUTX                       |     | 2.0                 |                          | mA                |  |

|                   | Offset between DC output currents      | At pins TxIFOUT and TxIFOUTX                       |     | tbd                 |                          | μΑ                |  |

|                   | Output current                         |                                                    |     | 0.25                |                          | mA <sub>RMS</sub> |  |

| S <sub>LO</sub>   | LO suppression                         |                                                    |     | -36                 |                          | dB                |  |

| SSB               | Sideband suppression                   |                                                    |     | -42                 |                          | dB                |  |

|                   | Equivalent input noise                 | at 10kHz                                           |     | tbd                 |                          | nV/√Hz            |  |

| ton               | Turn ON time                           |                                                    |     | 5                   |                          | μs                |  |

| toff              | Turn OFF time                          |                                                    |     | 5                   |                          | μs                |  |

**=** 7110826 0084600 17T **==**

SA1638

### AC ELECTRICAL CHARACTERISTICS (Continued)

|                                |                                                                                 |                                                                             |     | LIMITS                       |      | LINUTO            |  |

|--------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|------------------------------|------|-------------------|--|

| SYMBOL                         | PARAMETER                                                                       | TEST CONDITIONS                                                             | MIN | TYP                          | MAX  | UNITS             |  |

| IF Receive                     | er .                                                                            |                                                                             |     |                              |      |                   |  |

| RInRx                          | Differential input impedance                                                    | f <sub>IN</sub> = 400MHz                                                    |     | 5                            |      | kΩ                |  |

| ROutRx                         | Output impedance                                                                |                                                                             |     | 1                            |      | kΩ                |  |

|                                | Output common mode voltage                                                      | į                                                                           |     | V <sub>REF</sub>             |      | ٧                 |  |

| f3dB                           | Low pass filter -3dB bandwidth                                                  | 68kΩ resistor between pins<br>RESA and RESB                                 | 72  | 80                           | 88   | kHz               |  |

|                                | Low pass filter attenuation:<br>200kHz<br>400kHz<br>600kHz<br>6.5MHz<br>13.0MHz | 68kΩ external resistor<br>between RESA and RESB                             |     | 34<br>64<br>80<br>>80<br>>80 |      | dB                |  |

| VG                             | Voltage gain                                                                    | Differential output PD into<br>GSM baseband relative to<br>1200Ω source EMF | 43  | 50                           | 58   | dB                |  |

| NF                             | Noise figure at minimum gain                                                    | 1200Ω source and external matching resistor and inductor                    |     | 5.8                          |      | dB                |  |

|                                | Channel matching:<br>Gain<br>Phase                                              |                                                                             |     | 1.0<br>5.0                   |      | dB<br>degrees     |  |

|                                | Output DC offset <sup>2</sup>                                                   | Differential                                                                |     | 200                          |      | mV                |  |

| P <sub>-1dB</sub>              | Input 1dB compression point:<br>In band<br>200kHz<br>400kHz<br>600kHz           | 1200Ω source EMF                                                            |     | -52<br>-41<br>-41<br>-41     |      | dBV               |  |

| ton                            | Turn-0n time                                                                    | POnRx = V <sub>EE</sub>                                                     |     | 5                            |      | μs                |  |

| toff                           | Turn-off time                                                                   | POnRx = V <sub>EE</sub>                                                     |     | 5                            |      | μs                |  |

| IF Synthes                     | sizer                                                                           |                                                                             |     |                              |      |                   |  |

| fLO                            | Local oscillator input frequency range                                          |                                                                             | 140 |                              | 1000 | MHz               |  |

| Z <sub>LOIN</sub>              | Differential input impedance                                                    | Between pins LO <sub>IN</sub> and LO <sub>IN</sub> X                        |     | tbd                          |      | ΩllpF             |  |

|                                | LO input range                                                                  | Referred to 50Ω                                                             | 300 |                              | 550  | mV <sub>P-P</sub> |  |

|                                | Programmable divider:<br>Division range<br>Step size                            |                                                                             | 64  | 1                            | 511  |                   |  |

| fclk                           | Reference clock input frequency                                                 |                                                                             |     | 13, 26, 39 or 52             |      | MHz               |  |

| Z <sub>CLKIN</sub>             | Differential input impedance                                                    | Between pins ClkIn and<br>ClkInX                                            |     | 10    1.0                    |      | kΩ ll pF          |  |

|                                | CLK input sensitivity                                                           | Referred to 50Ω                                                             |     | 200                          |      | mV <sub>P-P</sub> |  |

| I <sub>REF</sub>               | Charge pump input reference current                                             |                                                                             |     | 31.2                         |      | μА                |  |

| l I <sub>CP</sub> l            | Charge pump output current:  C0C2 = 000  C0C2 = 111  Step size                  | I <sub>REF</sub> =31.2μA,<br>V <sub>CP</sub> = V <sub>CC</sub> CP/2         |     | 0.5<br>1.0<br>0.071          |      | mA                |  |

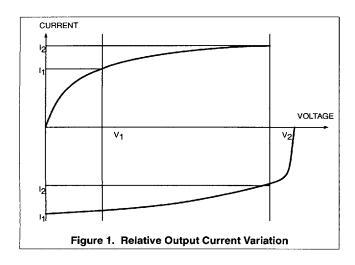

| $\frac{\Delta I_{CP}}{I_{CP}}$ | Relative output current variation <sup>3</sup>                                  | I <sub>REF</sub> =31.2μA                                                    |     |                              | ±10  | %                 |  |

| ΔI <sub>CP_M</sub>             | Output current matching <sup>4</sup>                                            | $I_{REF}$ =31.2μA,<br>$V_{CP}$ = $V_{CC}$ CP/2                              |     |                              | ±50  | μА                |  |

- Parameter measured relative to modulation sideband amplitude.

After programming the DC offset register for minimum offset.

### 7110826 0084601 006

SA1638

#### **FUNCTIONAL DESCRIPTION**

### **Serial Programming Input**

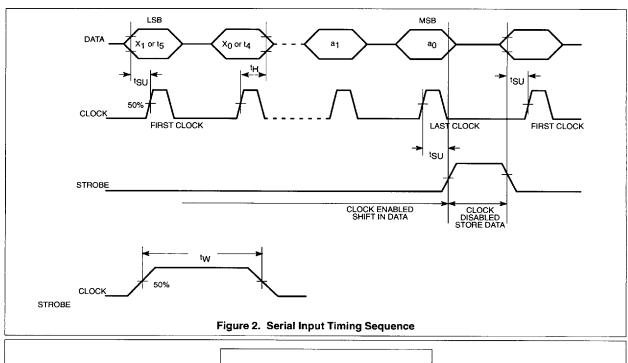

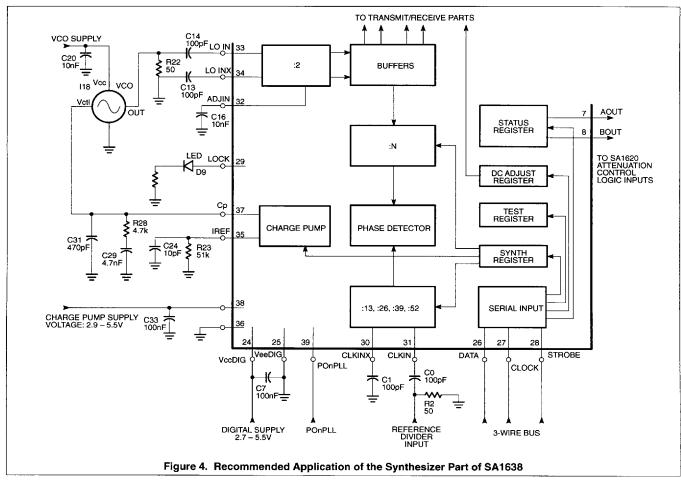

The serial input is a 3-wire input (CLOCK, STROBE, DATA) to program the counter ratios, charge pump current, status- and DC-offset register, mode select and test register. The programming data is structured into two 21-bit words; each word includes 4 chip address bits and 1 subaddress bit. Figure 2 shows the timing diagram of the serial input. When the STROBE = L, the clock driver is enabled and on the positive edges of the CLOCK the signal on DATA input is clocked into a shift register. When the STROBE = H, the clock is disabled and the data in the shift register remains stable. Depending on the value of the subaddress bit the data is latched into different working registers. Table 1 shows the contents of each word.

#### **Default States**

Upon power up (V $_{CC}$ DIG is applied) a reset signal is generated, which sets all registers to a default state. These default states are shown in Table 1.

#### Reference Divider

The reference divider can be programmed to four different division ratios (:13, :26, :39, :52), see registers r0, r1; default setting: divide by 13.

#### **Main Divider**

The external VCO signal, applied to the  $\rm LO_{IN}$  and  $\rm LO_{IN}X$  inputs, is divided by two and then fed to the main divider (:N). The main divider is a programmable 9 bit divider, the minimum division ratio is divide by 64. The division ratio is binary coded and set in the registers n0 to n8. The default setting is a divide by 400.

At the completion of a main divider cycle, a main divider output is generated which will drive the phase detector.

#### **Phase Detector**

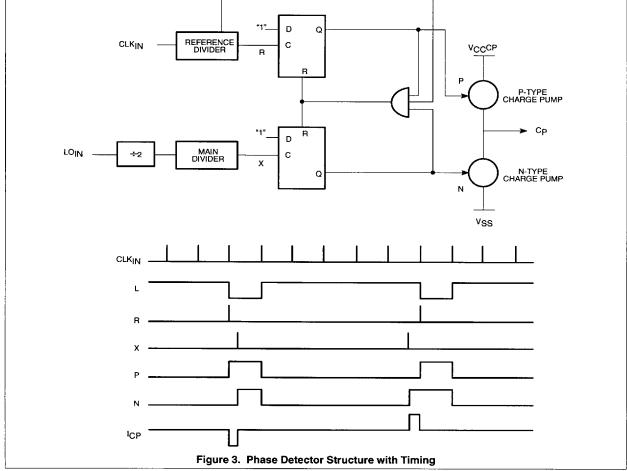

The phase detector is a D-type flip-flop phase and frequency detector shown in Figure 3. The flip-flops are set by the negative edges of the output signals of the dividers. The rising edge of the signal L will reset the flip-flops after both flip-flops have been set. Around zero phase error this has the effect of delaying the reset for 1 reference input cycle. This avoids non-linearity or deadband around zero phase error. The flip-flops drive on-chip charge pumps.

7110826 0084602 T42 🖿

December 14, 1994

A source current from the charge pump indicates the VCO frequency will be increased; a sink current indicates the VCO frequency will be decreased.

#### **Current Setting**

The charge pump current is defined by the current set between the pin  $I_{REF}$  and  $V_{SS}.$  The current value to be set there is 31.2 $\mu A.$  This current can be set by an external resistor to be connected between the pin  $I_{REF}$  and  $V_{SS}.$  The typical value  $R_{EXT}$  (current setting resistor) can be calculated with the formula

$$R_{EXT}~=~\frac{V_{CC}CP-1.4V}{31.2\mu\text{A}}$$

The current can be set to zero by connecting the pin I<sub>REF</sub> to V<sub>CC</sub>CP.

#### **Charge Pumps**

The charge pumps at pin CP are driven by the phase dectector and the current value is determined by the binary value of the charge pumps register CN = c0, c1, c2, default 1mA. The active charge pump current is typically:

$$II_{CP}I = CN \cdot 71\mu A + 500\mu A$$

#### **Lock Detect**

The output LOCK is H when the phase detector indicates a lock condition. This condition is defined as a phase difference of less than  $\pm 1$  cycle on the reference input  $\text{CLK}_{\text{IN}}$ ,  $\text{CLK}_{\text{IN}}$ X.

#### **Test Modes**

The LOCK output is selectable as a test output. Bits x0, x1 control the selection, the default setting is normal lock output as described in the Lock detect section. The selection of a Bit x0, x1 combination has a twofold effect: First it routes a divider output signal to the LOCK pin, second it disables mixer stages in the transmit path:

|    |    | sizzal at LOOK ziz                                      | Transmit Mixer |         |  |  |  |

|----|----|---------------------------------------------------------|----------------|---------|--|--|--|

| x0 | x1 | signal at LOCK pin                                      | l-mixer        | Q-mixer |  |  |  |

| 0  | 0  | normal lock detect                                      | on             | on      |  |  |  |

| 1  | 0  | CLK <sub>IN</sub> divided by reference<br>divider ratio | off            | on      |  |  |  |

| 0  | 1  | LOIN divided by 2 * (main divider ratio)                | on             | off     |  |  |  |

| 1  | 1  | main divider output, that goes to the phase detector    | off            | off     |  |  |  |

#### **Power Down Modes**

There are 4 power-on pins in the SA1638:  $P_{ON}$ ,  $P_{ON}Rx$ ,  $P_{ON}Tx$ ,  $P_{ON}PLL$ .

$P_{ON}$  = H powers up both voltage regulators  $V_{REG}1$  and  $V_{REG}2$ .  $P_{ON}$  should be set to L, if these internal voltage regulators are not to be used.

P<sub>ON</sub>Rx = H powers up the receiver part.

$P_{ON}Tx = L$  powers up the transmitter part.

$P_{ON}PLL = H$  powers up the synthesizer part. As it also powers up the first divide by 2 stage for generating the 0/90 degree phase shifted signals for the transmit and receive mixers, it also has to be set H if either the transmit part or the receive part is used.  $P_{ON}PLL = L$  powers down the dividers, resets the phase detector and disconnects the current setting pin  $I_{REF}$ . In  $P_{ON}PLL = L$  mode, the values in the serial input registers are still kept and the part still can be reprogrammed.

SA1638

Table 1. Definition of SA1638 Serial Registers

| First | data w                                                                                                                                                                                                                                                                                                                                           | ord: (s | hown    | with d     | efault v                                                                                                                                                                                                | /alues                                    | )                  |                                                                      |                                                                                            |                                                                               |                                                          |                                                                    |                                                       |                            |             |         |        |            |          |        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------|----------------------------|-------------|---------|--------|------------|----------|--------|

| Ac    | dress                                                                                                                                                                                                                                                                                                                                            | SA16    | 38      | Sub<br>Adr | N-Divider                                                                                                                                                                                               |                                           |                    |                                                                      |                                                                                            |                                                                               |                                                          |                                                                    | Ref ÷ Reg                                             |                            | Charge-Pump |         | ump    | Synth Test |          |        |

| MSB   |                                                                                                                                                                                                                                                                                                                                                  |         |         |            |                                                                                                                                                                                                         |                                           |                    |                                                                      |                                                                                            |                                                                               |                                                          |                                                                    |                                                       | l                          |             | L       |        |            | <b>.</b> | LSB    |

| a0    | a1                                                                                                                                                                                                                                                                                                                                               | a2      | а3      | sa         | n0                                                                                                                                                                                                      | n1                                        | n2                 | n3                                                                   | n4                                                                                         | n5                                                                            | n6                                                       | n7                                                                 | n8                                                    | r0                         | r1          | c0      | c1     | c2         | х0       | x1     |

| 1     | 1                                                                                                                                                                                                                                                                                                                                                | 1       | 0       | 0          | 1                                                                                                                                                                                                       | 1                                         | 0                  | 0                                                                    | 1                                                                                          | 0                                                                             | 0                                                        | 0                                                                  | 0                                                     | 0                          | 0           | 1       | 1      | 1          | 0        | 0      |

|       |                                                                                                                                                                                                                                                                                                                                                  |         | Add     | dress:     | 4 bits                                                                                                                                                                                                  | bits, a0a3, fixed to 1110                 |                    |                                                                      |                                                                                            |                                                                               |                                                          |                                                                    |                                                       |                            |             |         |        |            |          |        |

|       |                                                                                                                                                                                                                                                                                                                                                  | S       | Sub:Ade | dress:     | 1 bit,                                                                                                                                                                                                  | 1 bit, sa, fixed to 0 for first data word |                    |                                                                      |                                                                                            |                                                                               |                                                          |                                                                    |                                                       |                            |             |         |        |            |          |        |

|       |                                                                                                                                                                                                                                                                                                                                                  |         | N-D     | ivider:    | 9 bits, n0n8, values 64 (00100 0000) to 511 (111111111) allowed for IF-choice, default 400                                                                                                              |                                           |                    |                                                                      |                                                                                            |                                                                               |                                                          |                                                                    |                                                       |                            |             |         |        |            |          |        |

| R     | eferend                                                                                                                                                                                                                                                                                                                                          | e Divid | der Re  | gister:    | 2 bits                                                                                                                                                                                                  | , r0r1                                    | , 00 = -           | ÷13, 01                                                              | = ÷26,                                                                                     | , 10 = ÷                                                                      | 39, 11                                                   | = ÷52.                                                             | Defau                                                 | lt: 00                     |             |         |        |            |          |        |

|       | Chai                                                                                                                                                                                                                                                                                                                                             | ge-Pui  | mp Reg  | gister:    |                                                                                                                                                                                                         |                                           |                    |                                                                      |                                                                                            |                                                                               | tor for o                                                |                                                                    | pumps<br>rent                                         | , value                    | s 000 =     | = minim | ium cu | rrent to   | 111 =    |        |

| Secor | Synthesizer-Test Register:  2 bits, x0x1, default 00 00 lock detect at LOCK pin 10 reference signal divided by the reference divider ratio at LOCK pin 01 main input signal divided by 2 × (main divider ratio) at LOCK pin 11 main divider output signal going to the phase detector at LOCK pin  Second data word: (shown with default values) |         |         |            |                                                                                                                                                                                                         |                                           |                    |                                                                      |                                                                                            |                                                                               |                                                          |                                                                    |                                                       |                            |             |         |        |            |          |        |

|       | 14                                                                                                                                                                                                                                                                                                                                               | CA4C    | 20      | Sub        | Sta                                                                                                                                                                                                     | Status DC Offset Register                 |                    |                                                                      |                                                                                            |                                                                               |                                                          |                                                                    |                                                       |                            |             |         |        |            |          |        |

| AC    | aress                                                                                                                                                                                                                                                                                                                                            | SA163   | 38      | Adr        | Re                                                                                                                                                                                                      | Reg I-Channel Q-Channel                   |                    |                                                                      |                                                                                            |                                                                               |                                                          | Mode Select Register                                               |                                                       |                            |             |         |        |            |          |        |

| MSB   |                                                                                                                                                                                                                                                                                                                                                  |         |         |            |                                                                                                                                                                                                         |                                           | •                  |                                                                      |                                                                                            |                                                                               | •                                                        |                                                                    |                                                       |                            |             |         |        |            |          | LSB    |

| a0    | a1                                                                                                                                                                                                                                                                                                                                               | a2      | а3      | sa         | s0                                                                                                                                                                                                      | s1                                        | i0                 | i1                                                                   | i2                                                                                         | i3                                                                            | q0                                                       | q1                                                                 | q2                                                    | q3                         | t0          | t1      | t2     | t3         | t4       | t5     |

| 1     | 1                                                                                                                                                                                                                                                                                                                                                | 1       | 0       | 1          | 1                                                                                                                                                                                                       | 1                                         | 0                  | 0                                                                    | 0                                                                                          | 0                                                                             | 0                                                        | 0                                                                  | 0                                                     | 0                          | 0           | 0       | 0      | 0          | 0        | 0      |

|       |                                                                                                                                                                                                                                                                                                                                                  |         | Add     | dress:     | 4 bits,                                                                                                                                                                                                 | , a0a                                     | 3, fixed           | to 111                                                               | 0                                                                                          |                                                                               |                                                          |                                                                    |                                                       |                            |             |         |        |            |          |        |

|       |                                                                                                                                                                                                                                                                                                                                                  |         | ub:Add  |            | 1 bit, sa, fixed to 1 for second data word                                                                                                                                                              |                                           |                    |                                                                      |                                                                                            |                                                                               |                                                          |                                                                    |                                                       |                            |             |         |        |            |          |        |

|       |                                                                                                                                                                                                                                                                                                                                                  | Stat    | tus Reç | gister:    | 2 bits,<br>LNA1                                                                                                                                                                                         | s0s<br>and Li                             | 1, contr<br>NA2 of | ols gai<br>the SA                                                    | n/atten<br>1620 d                                                                          | uation<br>ata she                                                             | setting:<br>eet.                                         | s of SA                                                            | 1620 d                                                | ata sh                     | eet, see    | a Table | 4, Gai | n Cont     | rol Log  | ic for |

|       | I                                                                                                                                                                                                                                                                                                                                                | OC Off: | set Reç | gister:    | 4 bits per channel, i0i3 and q0q3, no correction as default i0 and q0 switches offset polarity, 0 to lower voltage, 1 to higher voltage i1i3 and q1q3, 000 no correction to 111 max. correction enabled |                                           |                    |                                                                      |                                                                                            |                                                                               |                                                          |                                                                    |                                                       |                            |             |         |        |            |          |        |

|       | Мо                                                                                                                                                                                                                                                                                                                                               | de Sel  | ect Reç | gister:    | 6 bits,                                                                                                                                                                                                 | , tO.                                     | t5,                | 0xxxx<br>1xxxx<br>x0xxx<br>x1xxx<br>xx00x<br>xx01x<br>xx11x<br>xxxx0 | x = Rx<br>x = Rx<br>x = Rx<br>x = Rx<br>x = LLL<br>x = LLL<br>x = LLL<br>x = LLL<br>0 = Rx | interna<br>interna<br>LO inp<br>LO inp<br>on wir<br>off<br>on wit<br>LP filte | al path A<br>al path I<br>ut appl<br>ut repla<br>th medi | AC cou<br>DC cou<br>ied<br>aced by<br>ium ext<br>externa<br>BW = 8 | ipled<br>y DC of<br>ternal to<br>al tune (<br>80kHz ( | fset<br>une (Al<br>'ADJ IN | •           |         |        |            |          |        |

SA1638

December 14 1994

7110826 0084604 815 📟

SA1638

### **PIN FUNCTIONS**

| PIN<br>No. | PIN<br>MNEMONIC      | DC V | EQUIVALENT CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PIN<br>No. | PIN<br>MNEMONIC      | DC V | EQUIVALENT CIRCUIT                              |

|------------|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------|------|-------------------------------------------------|

| 47         | V <sub>CC</sub> TxRx | 3.0  | BG 2.5 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10         | RES <sub>D</sub>     | 0.05 | 下                                               |

| 48         | GND <sub>REG</sub> 1 | 0.0  | 35k 1<br>25k 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11         | RESA                 | 0.00 | 15 40 43 46                                     |

| 1          | V <sub>REG</sub> 1   | 3.0  | 40 43 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                      |      | <u></u>                                         |

| 2          | V <sub>REG</sub> F2  | 3.0  | BG 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                      |      |                                                 |

| 3          | V <sub>REG</sub> 2   | 3.0  | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                      |      | $\bigoplus_{i=1}^{k}$                           |