- Internal Look Ahead for Fast Counting

- Carry Output for N-Bit Cascading

- Synchronous Counting

- Synchronously Programmable

- Package Options Include Plastic "Small Outline" Packages, Ceramic Chip Carriers, and Standard Plastic and Ceramic 300-mil DIPs

- Dependable Texas Instruments Quality and Reliability

### description

These synchronous, presettable counters feature an internal carry look-ahead for application in high-speed counting designs. The 'HC160 and 'HC162 are decade counters, and the 'HC161 and 'HC163 are 4-bit binary counters. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change coincident with each other when so instructed by the count-enable inputs and internal gating. This mode of operation eliminates the output counting spikes that are normally associated with synchronous (ripple clock) counters. A buffered clock input triggers the four flip-flops on the rising (positive-going) edge of the clock input waveform.

These counters are fully programmable; that is, they may be preset to any number between 0 and 9 or 15. As presetting is synchronous, setting up a low level at the load input disables the counter and causes the outputs to agree with the setup data after the next clock pulse regardless of the levels of the enable inputs.

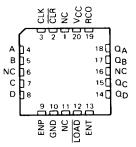

SN54HC' . . . J PACKAGE SN74HC' . . . D OR N PACKAGE (TOP VIEW)

| CLR | Ū١         | U 16 | Vcc          |

|-----|------------|------|--------------|

| CLK | <b>□</b> 2 | 15   | RCO          |

| Α   | []₃        | 14   | QΑ           |

| В   | ۵⁴         | 13   | QB           |

| С   | [[5        | 12   | αc           |

| D   | Пе         | 11   | $\sigma_{D}$ |

| ENP | ď٦         | 10   | ENT          |

| GND | ∏8         | 9    | LOAD         |

SN54HC' . . . FK PACKAGE

(TOP VIEW)

NC - No internal connection

The clear function for the 'HC160 and 'HC161 is asynchronous and a low level at the clear input sets all four of the flip-flop outputs low regardless of the levels of the clock, load, or enable inputs.

The clear function for the 'HC162 and 'HC163 is synchronous and a low level at the clear input sets all four of the flip-flop outputs low after the next low-to-high transition of the clock input, regardless of the levels of the enable inputs. This synchronous clear allows the count length to be modified easily by decoding the Q outputs for the maximum count desired. The active-low output of the gate used for decoding is connected to the clear input to synchronously clear the counter to 0000 (LLLL).

The carry look-ahead circuitry provides for cascading counters for n-bits synchronous applications without additional gating. Instrumental in accomplishing this function are two count-enable inputs and a ripple carry output. Both count-enable inputs (ENP and ENT) must be high to count, and ENT is fed forward to enable the ripple carry output. The ripple carry output (RCO) thus enabled will produce a high-level pulse while the count is maximum (9 or 15 with  $\Omega_{\rm A}$  high). This high-level overflow ripple carry pulse can be used to enable successive cascaded stages. Transitions at the ENP or ENT are allowed regardless of the level of the clock input.

PRODUCTION DATA documents contain information current as of publication data. Products conform to specifications per the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1982, Texas Instruments Incorporated

2-217

POST OFFICE BOX 655012 • DALLAS TEXAS 75265

**HCMOS Devices**

These counters feature a fully independent clock circuit. Changes at control inputs (ENP, ENT, or LOAD) that will modify the operating mode have no effect on the contents of the counter until clocking occurs. The function of the counter (whether enabled, disabled, loading, or counting) will be dictated solely by the conditions meeting the stable setup and hold times.

The SN54HC160 through SN54HC163 are characterized for operation over the full military temperature range of -55 °C to 125 °C. The SN74HC160 through SN74HC163 are characterized for operation from -40°C to 85°C.

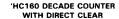

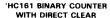

# logic symbols†

#### **'HC162 DECADE COUNTER** WITH SYNCHRONOUS CLEAR

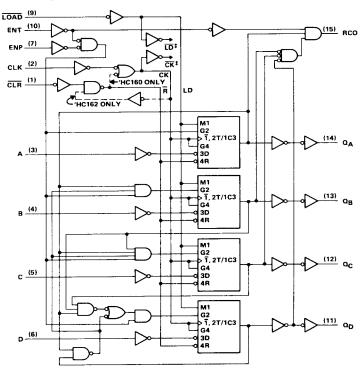

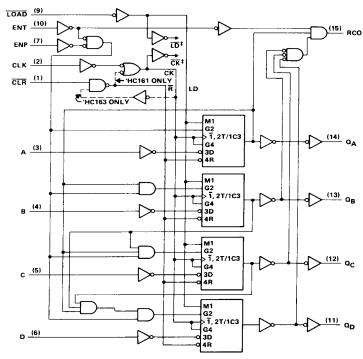

## 'HC160 and 'HC162 logic diagram (positive logic)

$<sup>^{\</sup>dagger}$  These symbols are in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for D, J, and N packages.

2-219

For the sake of simplicity, the routing of the complementary signals D and CK is not shown on this overall logic diagram. The uses of these signals are shown on the logic diagram of the D/T flip-flops.

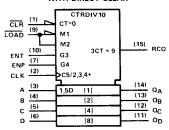

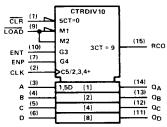

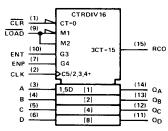

## logic symbols†

#### **'HC163 BINARY COUNTER** WITH SYNCHRONOUS CLEAR

## 'HC161 and 'HC163 logic diagram (positive logic)

<sup>&</sup>lt;sup>†</sup> These symbols are in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for D, J, and N packages.

POST OFFICE BOX 655012 . DALLAS, TEXAS 75265

For the sake of simplicity, the routing of the complementary signals LD and CK is not shown on this overall logic diagram. The uses of these signals are shown on the logic diagram of the D/T flip-flops.

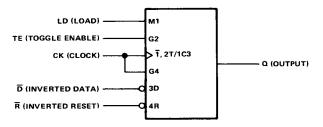

logic symbol, each D/T flip-flop (positive logic)

logic diagram, each D/T flip-flop (positive logic)

$<sup>^{\</sup>dagger}$  The origins of the signals  $\overline{\text{LD}}$  and  $\overline{\text{CK}}$  are shown in the logic diagrams of the overall devices.

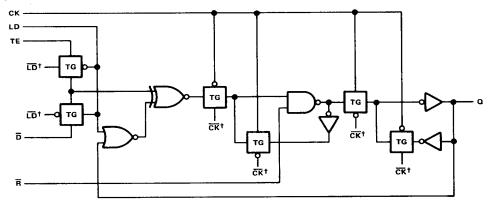

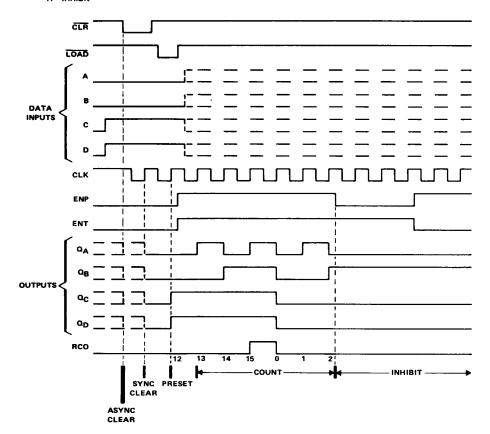

## 'HC160 and 'HC162 output sequence

Illustrated below is the following sequence:

- 1. Clear outputs to zero (SN54HC160 and SN74HC160 are asynchronous; SN54HC162 and SN74HC162 are synchronous)

- 2. Preset to BCD seven

- 3. Count to eight, nine, zero, one, two, and three

- 4. Inhibit

Illustrated below is the following sequence:

- Clear outputs to zero (SN54HC161 and SN74HC161 are asynchronous; SN54HC163 and SN74HC163 are synchronous)

- 2. Preset to binary twelve

- 3. Count to thirteen, fourteen, zero, one, and two

- 4. Inhibit

2

**HCMOS Devices**

# absolute maximum ratings over operating free-air temperature range†

| Supply voltage, VCC0.5 V to 7                                         | V              |

|-----------------------------------------------------------------------|----------------|

| Input clamp current, $I_{ K }(V_i < 0 \text{ or } V_i > V_{CC})$      | ۱A             |

| Output clamp current, IOK (VO < 0 or VO > VCC)                        | ۱A             |

| Continuous output current, IQ (VQ = 0 to VCC)                         | ۱A             |

| Continuous current through VCC or GND pins                            | ۱A             |

| Lead temperature 1,6 mm (1/16 in) from case for 60 s: FK or J package | o.C            |

| Lead temperature 1,6 mm (1/16 in) from case for 10 s: D or N package  | <sup>2</sup> C |

| Storage temperature range                                             | ٥c             |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# recommended operating conditions

|          |                                        |                         | SN54HC' |     |      | SN74HC' |     |      |      |

|----------|----------------------------------------|-------------------------|---------|-----|------|---------|-----|------|------|

|          |                                        |                         | MIN     | NOM | MAX  | MIN     | NOM | MAX  | UNIT |

| Vcc      | Supply voltage                         |                         | 2       | 5   | 6    | 2       | 5   | 6    | V    |

|          |                                        | V <sub>CC</sub> = 2 V   | 1.5     |     |      | 1.5     |     |      |      |

| $V_{IH}$ | High-level input voltage               | $V_{CC} = 4.5 V$        | 3.15    |     |      | 3.15    |     |      | V    |

|          |                                        | V <sub>CC</sub> = 6 V   | 4.2     |     |      | 4.2     |     |      |      |

|          |                                        | V <sub>CC</sub> = 2 V   | 0       |     | 0.3  | 0       |     | 0.3  |      |

| $V_{IL}$ | Low-level input voltage                | $V_{CC} = 4.5 V$        | 0       |     | 0.9  | 0       |     | 0.9  | V    |

|          |                                        | $V_{CC} = 6 V$          | 0       |     | 1.2  | 0       |     | 1.2  |      |

| Vi       | Input voltage                          |                         | 0       |     | vcc  | 0       |     | Vcc  | V    |

| ٧o       | Output voltage                         | ,                       | 0       |     | Vcc  | 0       |     | Vcc  | V    |

|          |                                        | V <sub>CC</sub> = 2 V   | 0       |     | 1000 | 0       |     | 1000 |      |

| tt       | Input transition (rise and fall) times | V <sub>CC</sub> ≃ 4.5 V | 0       |     | 500  | ٥       |     | 500  | ns   |

|          |                                        | $V_{CC} = 6 V$          | 0       |     | 400  | 0       |     | 400  |      |

| TA       | Operating free-air temperature         |                         | - 55    |     | 125  | -40     |     | 85   | °C   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER      | TEST CONDITIONS                                         | V     | Т    | A = 25 | °C    | SN5 | 4HC'   | SN74HC' |      | LINIT |

|----------------|---------------------------------------------------------|-------|------|--------|-------|-----|--------|---------|------|-------|

| TANAMETER      | TEST COMDITIONS                                         | Vcc   | MIN  | TYP    | MAX   | MIN | MAX    | MIN     | MAX  | UNIT  |

|                |                                                         | 2 V   | 1.9  | 1.998  |       | 1.9 | ``     | 1.9     |      |       |

| į              | $V_I = V_{IH}$ or $V_{IL}$ , $I_{OH} = -20 \mu A$       | 4.5 V | 4.4  | 4.499  |       | 4.4 |        | 4.4     |      |       |

| ∨он            |                                                         | 6 V   | 5.9  | 5.999  |       | 5.9 |        | 5.9     |      | V     |

| [              | $V_I = V_{iH}$ or $V_{iL}$ , $I_{OH} = -4$ mA           | 4.5 V | 3.98 | 4.30   |       | 3.7 |        | 3.84    |      |       |

|                | $V_I = V_{IH}$ or $V_{IL}$ , $I_{OH} = -5.2$ mA         | 6 V   | 5.48 | 5.80   |       | 5.2 |        | 5.34    |      |       |

| Ī              |                                                         | 2 V   |      | 0.002  | 0.1   |     | 0.1    |         | 0.1  |       |

|                | $V_{I} = V_{IH} \text{ or } V_{IL},  I_{OL} = 20 \mu A$ | 4.5 V |      | 0.001  | 0.1   |     | 0.1    |         | 0.1  |       |

| VOL            |                                                         | 6 V   |      | 0.001  | 0.1   |     | 0.1    |         | 0.1  | V     |

|                | $V_I = V_{IH}$ or $V_{IL}$ , $I_{OL} = 4$ mA            | 4.5 V |      | 0.17   | 0.26  |     | 0.4    |         | 0.33 |       |

|                | $V_{l} = V_{lH}$ or $V_{lL}$ , $I_{OL} = 5.2$ mA        | 6 V   |      | 0.15   | 0.26  |     | 0.4    |         | 0.33 |       |

| l <sub>l</sub> | V <sub>I</sub> = V <sub>CC</sub> or 0                   | 6 V   |      | ± 0.1  | ± 100 |     | ± 1000 | -       | 1000 | nA    |

| Icc            | $V_I = V_{CC}$ or 0, $I_O = 0$                          | 6 V   |      |        | 8     |     | 160    |         | 80   | μА    |

| c. T           |                                                         | 2 to  |      | 3      | 10    |     |        |         | 10   |       |

| c <sub>i</sub> |                                                         | 6 V   |      | 3      | 10    |     | 10     |         | 10   | рF    |

| _ |                  |   |

|---|------------------|---|

|   |                  |   |

|   | u                | į |

|   | ă                | ١ |

|   | y                |   |

|   | C                |   |

|   | .=               |   |

|   | - 7              | į |

|   | a                |   |

|   | -                |   |

|   | C                |   |

|   |                  |   |

|   | U                | ١ |

|   | ~                |   |

|   | $\boldsymbol{C}$ |   |

|   | =                |   |

|   | 5                |   |

|   | •                |   |

|   | C'               |   |

|   | =                |   |

|   |                  |   |

| _               | •                | •                             | -     |      | •    | -   |                       |                                |     |      |

|-----------------|------------------|-------------------------------|-------|------|------|-----|-----------------------|--------------------------------|-----|------|

|                 | 1                | PARAMETER                     | vcc   | TA - | 25°C | TH  | HC160<br>IRU<br>HC163 | SN74HC160<br>THRU<br>SN74HC163 |     | UNIT |

|                 |                  |                               | 1     | MIN  | MAX  | MIN | MAX                   | MIN                            | MAX |      |

|                 |                  |                               | 2 V   | 0    | 6    | 0   | 4.2                   | 0                              | 5   |      |

| fclock          | Clock frequency  | ,                             | 4.5 V | 0    | 31   | 0   | 21                    | 0                              | 25  | MHz  |

| O.O.O.          |                  |                               | 6 V   | 0    | 36   | 0   | 25                    | 0                              | 29  |      |

|                 |                  |                               | 2 V   | 80   |      | 120 |                       | 100                            |     |      |

|                 |                  | CLK high or low               | 4.5 V | 16   |      | 24  |                       | 20                             |     |      |

|                 |                  | _                             | 6 V   | 14   |      | 20  |                       | 17                             |     |      |

| tw              | w Pulse duration |                               | 2 V   | 80   |      | 120 |                       | 100                            |     | กร   |

|                 |                  | CLR low ('HC160, 'HC161)      | 4.5 V | 16   |      | 24  |                       | 20                             |     |      |

|                 |                  | · ·                           | 6 V   | 14   |      | 20  |                       | 17                             |     |      |

|                 |                  |                               | 2 V   | 150  | •    | 225 |                       | 190                            |     |      |

|                 |                  | A, B, C, or D                 | 4.5 V | 30   |      | 45  |                       | 38                             |     |      |

|                 |                  |                               | 6 V   | 26   |      | 38  |                       | 32                             |     |      |

|                 |                  |                               | 2 V   | 135  |      | 205 |                       | 170                            |     |      |

|                 |                  | LOAD low                      | 4.5 V | 27   |      | 41  |                       | 34                             |     |      |

|                 | 1                |                               | 6 V   | 23   |      | 35  |                       | 29                             |     |      |

|                 |                  |                               | 2 V   | 170  |      | 255 |                       | 215                            |     |      |

|                 |                  | ENP, ENT                      | 4.5 V | 34   |      | 51  |                       | 43                             |     |      |

|                 | Setup time,      |                               | 6 V   | 29   |      | 43  |                       | 37                             |     |      |

| t <sub>su</sub> | before CLK1      |                               | 2 V   | 125  |      | 190 |                       | 155                            |     | ns   |

|                 |                  | CLR inactive ('HC160, 'HC161) | 4.5 V | 25   |      | 38  |                       | 31                             |     |      |

|                 |                  |                               | 6 V   | 21   |      | 32  |                       | 26                             |     |      |

|                 |                  |                               | 2 V   | 160  |      | 240 |                       | 200                            |     |      |

|                 |                  | CLR low ('HC162, 'HC163)      | 4.5 V | 32   |      | 48  |                       | 40                             |     |      |

|                 |                  |                               | 6 V   | 27   |      | 41  |                       | 34                             |     |      |

|                 |                  |                               | 2 V   | 160  |      | 240 |                       | 200                            |     | 1    |

|                 |                  | CLR inactive ('HC162, 'HC163) | 4.5 V | 32   |      | 48  |                       | 40                             |     |      |

|                 |                  |                               | 6 V   | 27   |      | 41  |                       | 34                             |     | l    |

|                 |                  |                               | 2 V   | 0    |      | 0   |                       | 0                              |     |      |

| th              | Hold time, all s | ynchronous inputs after CLK↑  | 4.5 V | 0    |      | 0   |                       | 0                              |     | ns   |

| .,              |                  | •                             | 6 V   | ٥ ا  |      | 0   |                       | 0                              |     | 1    |

switching characteristics over recommended operating free-air temperature range (unless otherwise noted), CL = 50 pF (see Note 1)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | vcc   | IA = 25°C |     | VCC TA = 25°C |     |     | HC160<br>HC161 | ĺ   | HC160<br>HC161 | UNIT |

|------------------|-----------------|----------------|-------|-----------|-----|---------------|-----|-----|----------------|-----|----------------|------|

|                  | (1141 017       | (001701)       |       | MIN       | TYP | MAX           | MIN | MAX | MIN            | MAX | 1              |      |

|                  |                 |                | 2 V   | 6         | 14  |               | 4.2 |     | 5              |     |                |      |

| f <sub>max</sub> |                 | İ              | 4.5 V | 31        | 40  |               | 21  |     | 25             |     | MHz            |      |

|                  |                 |                | 6 V   | 36        | 44  |               | 25  |     | 29             |     |                |      |

|                  |                 |                | 2 V   |           | 83  | 215           |     | 325 |                | 270 |                |      |

| t <sub>pd</sub>  | CLK             | RCO            | 4.5 V |           | 24  | 43            |     | 65  |                | 54  | ns             |      |

|                  |                 |                | 6 V   |           | 20  | 37            |     | 55  |                | 46  |                |      |

|                  |                 |                | 2 V   |           | 80  | 205           |     | 310 |                | 255 |                |      |

| <sup>t</sup> pd  | CLK             | Any Q          | 4.5 V |           | 25  | 41            |     | 62  |                | 51  | ns             |      |

|                  |                 |                | 6 V   |           | 21  | 35            |     | 53  |                | 43  |                |      |

|                  |                 |                | 2 V   |           | 62  | 195           |     | 295 |                | 245 |                |      |

| <sup>t</sup> pd  | ENT             | RCO            | 4.5 V |           | 17  | 39            |     | 59  |                | 49  | ns             |      |

|                  |                 |                | 6 V   |           | 14  | 33            |     | 50  |                | 42  |                |      |

|                  |                 |                | 2 V   |           | 105 | 210           |     | 315 |                | 265 |                |      |

| <sup>t</sup> PHL | CLR             | Any Q          | 4.5 V |           | 21  | 42            |     | 63  |                | 53  | ns             |      |

|                  |                 |                | 6 V   |           | 18  | 36            |     | 54  |                | 45  |                |      |

|                  |                 | [              | 2 V   |           | 110 | 220           |     | 330 |                | 275 |                |      |

| tPHL             | CLR             | RCO            | 4.5 V |           | 22  | 44            |     | 66  |                | 55  | ns             |      |

|                  |                 |                | 6 V   |           | 19  | 37            |     | 56  |                | 47  |                |      |

|                  |                 |                | 2 V   |           | 38  | 75            |     | 110 | -              | 95  | -              |      |

| tę               |                 | Any            | 4.5 V |           | 8   | 15            |     | 22  |                | 19  | ns             |      |

|                  |                 | ]              | 6 V   |           | 6   | 13            | !   | 19  |                | 16  |                |      |

| Cpd Power dissipation capacitance No load, TA = 25 °C 60 pF typ |  |                                |           |

|-----------------------------------------------------------------|--|--------------------------------|-----------|

|                                                                 |  | No load, T <sub>A</sub> = 25°C | 60 pF typ |

NOTE 1: Load circuit and voltage waveforms are shown in Section 1.

switching characteristics over recommended operating free-air temperature range (unless otherwise noted), CL = 50 pF (see Note 1)

| PARAMETER       | FROM<br>(INPUT) | TO<br>(OUTPUT) | vcc   | TA = 25°C |     | TA = 25°C SN54HC162 SN74HC16<br>SN54HC163 SN74HC16 |     |     | UNIT |     |     |

|-----------------|-----------------|----------------|-------|-----------|-----|----------------------------------------------------|-----|-----|------|-----|-----|

|                 | (1001)          | (001701)       |       | MIN       | TYP | MAX                                                | MIN | MAX | MIN  | MAX |     |

|                 |                 |                | 2 V   | 6         | 14  |                                                    | 4.2 |     | 5    |     |     |

| fmax            |                 |                | 4.5 V | 31        | 40  |                                                    | 21  |     | 25   |     | MHz |

|                 |                 |                | 6 V   | 36        | 44  |                                                    | 25  |     | 29   |     |     |

|                 |                 |                | 2 V   |           | 83  | 215                                                |     | 325 |      | 270 |     |

| tpd             | CLK             | RCO            | 4.5 V |           | 24  | 43                                                 | 1   | 65  |      | 54  | ns  |

|                 |                 |                | 6 V   |           | 20  | 37                                                 |     | 55  |      | 46  |     |

|                 |                 |                | 2 V   |           | 80  | 205                                                |     | 310 |      | 255 |     |

| t <sub>pd</sub> | CLK             | Any Q          | 4.5 V |           | 25  | 41                                                 |     | 62  |      | 51  | ns  |

|                 |                 |                | 6 V   |           | 21  | 35                                                 | l   | 53  |      | 43  |     |

|                 |                 |                | 2 V   |           | 62  | 195                                                | T   | 295 |      | 245 |     |

| t <sub>pd</sub> | ENT             | RCO            | 4.5 V |           | 17  | 39                                                 |     | 59  |      | 49  | ns  |

| · ·             |                 | +              | 6 V   |           | 14  | 3 <b>3</b>                                         |     | 50  |      | 42  |     |

|                 |                 |                | 2 V   |           | 38  | 75                                                 | Ī   | 110 |      | 95  |     |

| tt              |                 | Any            | 4.5 V |           | 8   | 15                                                 |     | 22  |      | 19  | ns  |

|                 |                 |                | 6 V   |           | 6   | 13                                                 | }   | 19  |      | 16  |     |

| C <sub>pd</sub> | Power dissipation capacitance | No load, T <sub>A</sub> = 25°C | 60 pF typ |

|-----------------|-------------------------------|--------------------------------|-----------|

|                 |                               |                                |           |

NOTE 1: Load circuit and voltage waveforms are shown in Section 1.

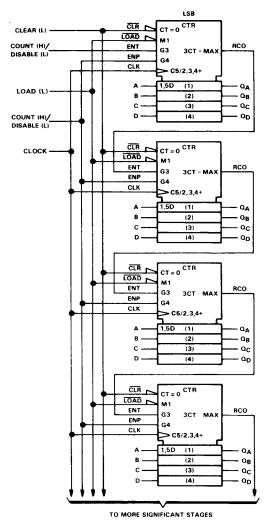

#### TYPICAL APPLICATION DATA

#### **N-BIT SYNCHRONOUS COUNTERS**

This application demonstrates how the look-ahead carry circuit can be used to implement a high-speed n-bit counter. The 'HC160 and 'HC162 will count in BCD, and the 'HC161 and 'HC163 will count in binary. Virtually any count mode (modulo-N, N<sub>1</sub>-to-N<sub>2</sub>, N<sub>1</sub>-to-maximum) can be used with this fast look-ahead circuit.

Texas VI

2-228

POST OFFICE BOX 655012 • DALLAS, TEXAS 75265

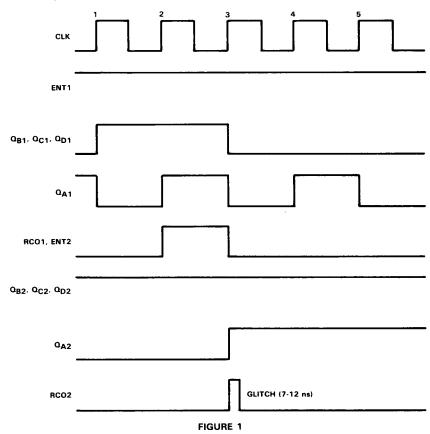

The application circuit shown on the preceding page is not valid for clock frequencies above 18 MHz (at 25 °C and 4.5 V V<sub>CC</sub>). The reason for this is that there is a "glitch" that is produced on the second stage's RCO output and every succeeding stage's RCO output. This glitch is common to all HC vendors that Texas Instruments has evaluated in addition to the bipolar equivalents ('LS, 'ALS, 'AS).

The glitch on RCO is caused because the propagation delay of the rising edge of Q<sub>A</sub> of the second stage is shorter than the propagation delay of the falling edge of ENT. The RCO output is the product of ENT, Q<sub>A</sub>, Q<sub>B</sub>, Q<sub>C</sub>, and Q<sub>D</sub> (ENT•Q<sub>A</sub>•Q<sub>B</sub>•Q<sub>C</sub>•Q<sub>D</sub>). The resulting glitch is about 7-12 ns in duration. Figure 1 illustrates the condition in which the glitch occurs. For the purposes of simplicity, only two stages are being considered, but the results can be applied to other stages. Q<sub>B</sub>, Q<sub>C</sub>, and Q<sub>D</sub> of the first and second stage are at logic one, and Q<sub>A</sub> of both stages are at logic zero (1110 1110) after the first clock pulse. On the rising edge of the second clock pulse, Q<sub>A</sub> and RCO of the first stage will go high. On the rising edge of the third clock pulse Q<sub>A</sub> and RCO of the first stage will return to a low level, and Q<sub>A</sub> of the second stage will go to a high level. It is at this time that the glitch on the RCO of the second stage will appear because of the "race condition" inside the chip.

The glitch will cause a problem in the next stage (stage three) if the glitch is still present when the next rising clock edge appears (clock pulse 4). To ensure that this does not happen, the clock frequency must be less than inverse of the sum of the clock-to-RCO propagation delay and the glitch duration ( $t_g$ ). In other words,  $t_{max} = 1/(t_{pd} \text{ CLK-to-RCO} + t_g)$ . For example, at 25 °C at 4.5 V V<sub>CC</sub>, the clock-to-RCO propagation delay is 43 ns and the maximum duration of the glitch is 12 ns. Therefore, the maximum clock frequency that the cascaded counters can use is 18 MHz. The following table contains the  $t_{clock}$ ,  $t_{w}$ , and  $t_{max}$  specifications for applications that use more than two 'HC160 family devices cascaded together.

## timing requirements over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                  |                                 | vcc   | <sup>T</sup> A − | 25°C | tř  | HC160<br>aru<br>HC163 | SN74I<br>th<br>SN74I | UNIT |     |

|----------------------------|---------------------------------|-------|------------------|------|-----|-----------------------|----------------------|------|-----|

|                            |                                 | 1     | MIN              | MAX  | MIN | MAX                   | MIN                  | MAX  | 1   |

| f <sub>clock</sub> Cłock f |                                 | 2 V   | 0                | 3.6  | 0   | 2.5                   | 0                    | 2.9  |     |

|                            | Cłock frequency                 | 4.5 V | 0                | 18   | 0   | 12                    | 0                    | 14   | MHz |

|                            |                                 | 6 V   | 0                | 21   | 0   | 14                    | 0                    | 17   |     |

|                            |                                 | 2 V   | 140              |      | 200 |                       | 170                  |      |     |

| tw Pulse de                | Pulse duration, CLK high or low | 4.5 V | 28               |      | 40  |                       | 36                   |      | ns  |

|                            |                                 | 1 6 V | 24               |      | 36  |                       | 30                   |      |     |

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted), $C_L = 50$ pF (see Note 1)

| PARAMETER | FROM<br>(INPUT) | TO<br>(OUTPUT) | vcc   |     | - 25 |     | ti<br>SN54 | HC160<br>hru<br>HC163 | th<br>SN74 | HC160<br>hru<br>HC163 | UNIT |

|-----------|-----------------|----------------|-------|-----|------|-----|------------|-----------------------|------------|-----------------------|------|

|           |                 |                | ļ     | MIN | TYP  | MAX | MIN        | MAX                   | MIN        | MAX                   |      |

|           |                 |                | 2 V   | 3.6 |      |     | 2.5        |                       | 2.9        |                       |      |

| fmax      |                 |                | 4.5 V | 18  |      |     | 12         |                       | 14         |                       | MHz  |

|           |                 |                | 6 V   | 21  |      |     | 14         |                       | 17         |                       | ŀ    |

NOTE 1: These limits apply only to applications which use more than two 'HC160 family devices cascaded together.

If the 'HC160 family is used as a single unit or only two cascaded together, then the maximum clock frequency that the devices can use is not limited because of the glitch. In these situations, the devices can be operated at the maximum specifications.

A glitch can appear on the RCO output of a single 'HC160 family device depending on the relationship of ENT to the clock input. Any application that uses the RCO output to drive any input except an ENT of another cascaded 'HC160 family device must take this into consideration.