DATA SHEET

# MB1515 ASSP

# BICMOS 2.5GHz PLL FREQUENCY SYNTHESIZER WITH BUILT-IN PRESCALER

## **DESCRIPTION**

The MB1515 is a serial input PLL (Phase-Locked Loop) frequency synthesizer with a built-in prescaler allowing for a pulse swallow system in the two modulus 2.5 GHz band. It is suitable for BS and TV tuners and CATV systems.

The synthesizer is powered by 5 V (typical). Using the latest proprietary process, current consumption has been reduced to Icc = 16 mA (typical).

## **FEATURES**

• Supply voltage: Vcc = 5 V

• High-speed operation capability: fin = 2.5 GHz (Pin = - 4 dBm)

• Low current consumption: Icc = 16 mA (typical)

Broad operating temperature range: Ta = - 40°C to +85°C

· Integrated Functions

24-bit shift register

24-bit latch

Reference divider

Binary 2-bit programmable reference counter (Divide ratios: 256, 512,

1024, and 2048)

Comparison Divider

Binary 5-bit swallow counter (Divide ratios: 0 to 31)

Binary 12-bit bit programmable counter (Divide ratios: 32 to 4095)

Phase comparator with phase conversion feature

Two modulus prescaler for 2.5 GHz band (Divide ratios: 256/272 and 512/528)

4-bit band switching signals

Control signal generator

Crystal oscillator

Charge pump

#### **MAXIMUM RATINGS**

| Parameter           | Symbol          | Value            | Units |

|---------------------|-----------------|------------------|-------|

| Supply voltage      | V <sub>CC</sub> | -0.5 to +7.0     | V     |

| Output voltage      | Vo              | -0.5 to V cc+0.5 | V     |

| Output current      | Io              | ±10              | mA    |

| Storage temperature | Tstg            | -55 to +125      | °C    |

#### RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol          | Min. | Тур. | Max             | Unit |

|-----------------------|-----------------|------|------|-----------------|------|

| Supply voltage        | V <sub>CC</sub> | 4.5  | 5.0  | 5.5             | V    |

| Input voltage         | VI              | GND  | _    | V <sub>CC</sub> | V    |

| Operating temperature | Та              | -40  | _    | +85             | °C   |

#### NOTES:

- To prevent damage caused by static electricity, an antistatic element is added and antistatic enhancement is also built into the circuit. However, the following handling cautions must be observed:

- Contain the device in a conductive case when storing or transporting it.

- Before handling, verify that the person handling the device, fixtures, and tools are not charged (grounded). Use a grounded conductive sheet as the work surface.

- Turn off power before connecting or disconnecting the device to or from the socket.

- Protect the lead with a conductive sheet when handling (such as transporting) a board on which this device is mounted.

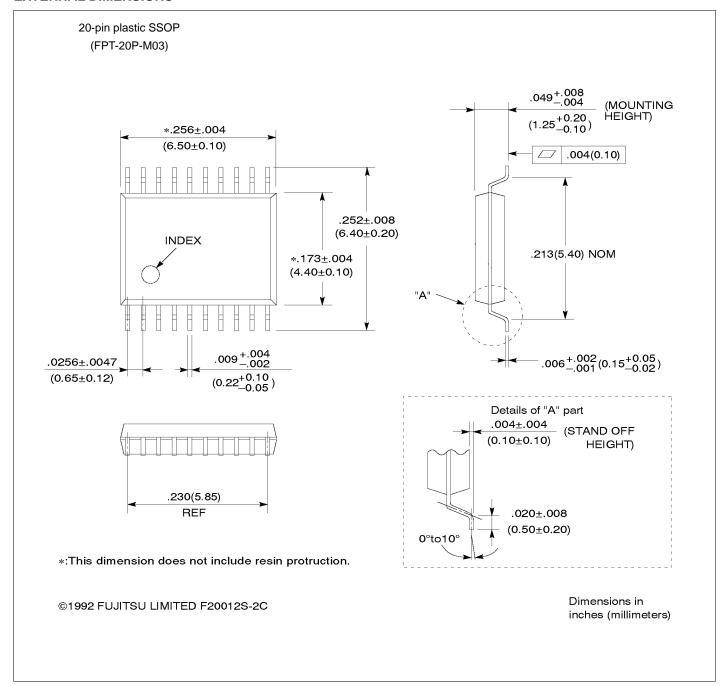

20-pin Plastic SSOP

(FPT-20P-M03)

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

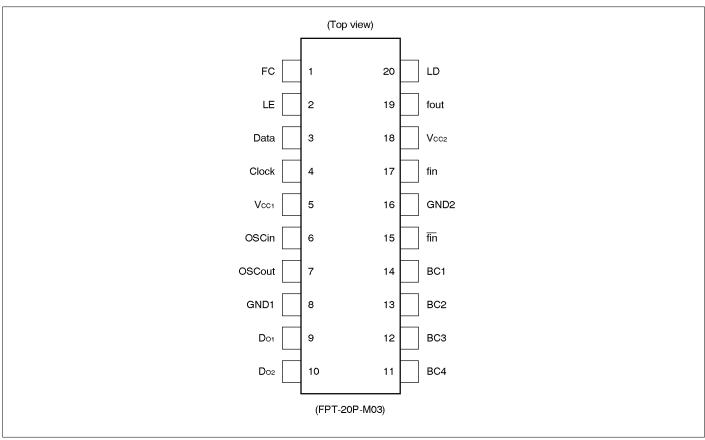

## **PIN ASSIGNMENT**

## **PIN DESCRIPTION**

| Pin No. | Pin name         | 1/0                                                                                     | Descriprion                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |                    |  |  |  |  |  |

|---------|------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|--|

| 1       | FC               | ı                                                                                       | Phase switch input pin to the phase comparator (with pull up resistor). This pin allows for inverting the polarity of phase comparator output, according to the polarity of the externally connected LPF and VCO. When FC is at "L" level, charge pump and phase comparator characteristics are reversed. This pin also toggles the output of the fout pin (test pin) between fr and fp. |                                                                                                                 |                    |  |  |  |  |  |

| 2       | LE               | I                                                                                       | Load enable signal input pin (with Schmitt trigger circuit). The pin sends shift register contents to the latch when LE is at "H" (or open).                                                                                                                                                                                                                                             |                                                                                                                 |                    |  |  |  |  |  |

| 3       | Data             | I                                                                                       | Serial data input pin using binary codes (with Schmitt trigger circuit).                                                                                                                                                                                                                                                                                                                 |                                                                                                                 |                    |  |  |  |  |  |

| 4       | Clock            | I                                                                                       | 24-bit shift register clock input pin (with Schmitt trigger circuit). Data is read a pulse.                                                                                                                                                                                                                                                                                              | t the rising edo                                                                                                | ge of the clock    |  |  |  |  |  |

| 5       | V <sub>CC1</sub> | _                                                                                       | Power supply pin (for PLL).                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |                    |  |  |  |  |  |

| 6       | OSCin            | I                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                          | Cystal oscillator connect pin and reference divider input pin. (OSCin: Oscillator input pin, OSCout: Oscillator |                    |  |  |  |  |  |

| 7       | OSCout           | 0                                                                                       | output pin)                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |                    |  |  |  |  |  |

| 8       | GND1             | _                                                                                       | Grounding pin (for PLL)                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                 |                    |  |  |  |  |  |

| 9       | DO1              | 0                                                                                       | Charge pump output pin. Phase characteristics invert with FC pin settings.                                                                                                                                                                                                                                                                                                               |                                                                                                                 |                    |  |  |  |  |  |

| 10      | DO2              | 0                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |                    |  |  |  |  |  |

| 11      | BC4              | 0                                                                                       | Band switch output pin (open collector output). Output is controlled by the serial data band bit setting. When BCX bit is "H", the BCX output transistor turns ON. When BCX bit is "H", the BCX output transistor turns OFF. (X: 1 to 4)                                                                                                                                                 |                                                                                                                 |                    |  |  |  |  |  |

| 12      | BC3              | 0                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |                    |  |  |  |  |  |

| 13      | BC2              | 0                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |                    |  |  |  |  |  |

| 14      | BC1              | 0                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |                    |  |  |  |  |  |

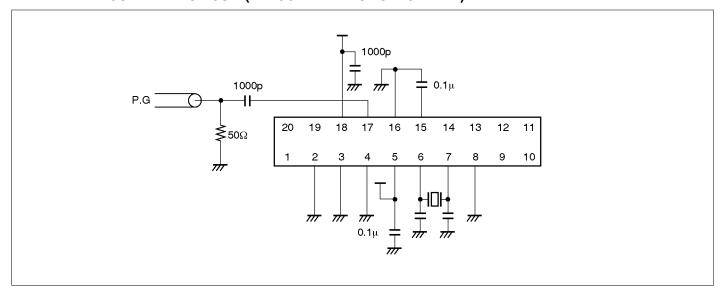

| 15      | fin              | I                                                                                       | fin's complementary input pin. Connect to ground via a capacitor.                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |                    |  |  |  |  |  |

| 16      | GND2             | _                                                                                       | Ground pin (for prescaler).                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |                    |  |  |  |  |  |

| 17      | fin              | I                                                                                       | Prescaler input pin. Input using ac coupling.                                                                                                                                                                                                                                                                                                                                            |                                                                                                                 |                    |  |  |  |  |  |

| 18      | V <sub>CC2</sub> | _                                                                                       | Power supply pin (for prescaler).                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |                    |  |  |  |  |  |

| 19      | fout             | 0                                                                                       | Phase comparator input monitor pin.Produces either the reference divider                                                                                                                                                                                                                                                                                                                 | FC                                                                                                              | Output Signal      |  |  |  |  |  |

|         |                  | output (fr)or the comparison divider output (fp) signal depending FC pin's input level. | output (fr) or the comparison divider output (fp) signal depending on the FC pin's input level.                                                                                                                                                                                                                                                                                          | "H"                                                                                                             | fr                 |  |  |  |  |  |

|         |                  |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                          | "L"                                                                                                             | fp                 |  |  |  |  |  |

| 20      | LD               | 0                                                                                       | Phase comparator output pin. LD is usually "H", and is set to "L" for the durat between fr and fp.                                                                                                                                                                                                                                                                                       | ion equivalent                                                                                                  | to the phase error |  |  |  |  |  |

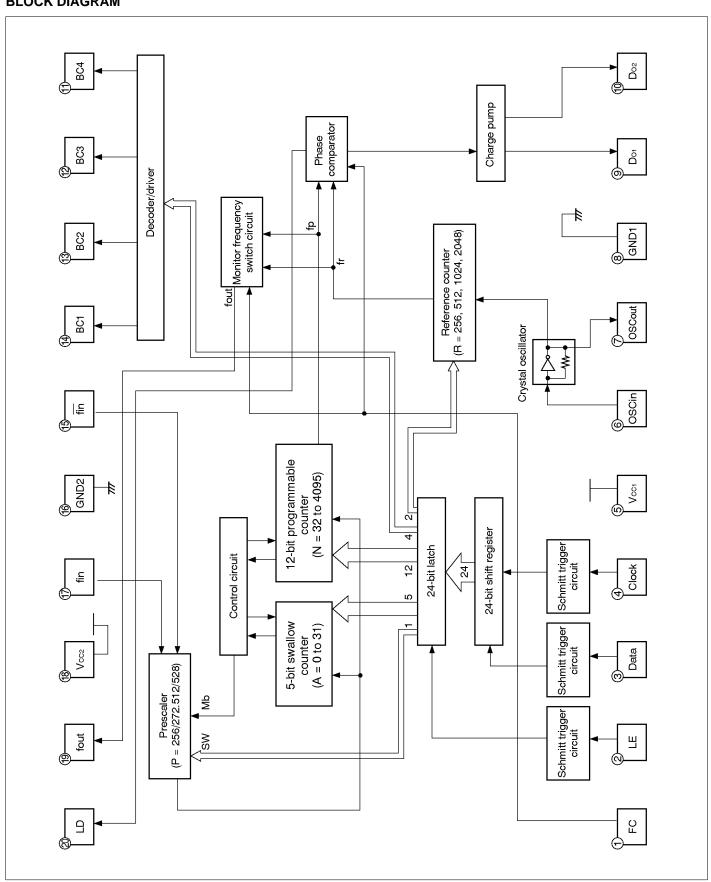

## **BLOCK DIAGRAM**

## **ELECTRICAL CHARACTERISTICS**

|                               |                      |                   |                                                                                                                   |                                | Value |                              |                  |

|-------------------------------|----------------------|-------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------|-------|------------------------------|------------------|

| Parameter                     |                      | Symbol            | Condition                                                                                                         | Min.                           | Тур.  | Max.                         | Units            |

| Power supply current          |                      | Icc               | When input at fin=2.5GHz and OSCin= 4MHz, V <sub>CC</sub> =5V. Other input pins are GND and output pins are open. | _                              | 16.0  | _                            | mA               |

| Operating frequency           | fin                  | fin               | Must be AC-coupled. The minimum operating frequency when coupled at 1000 pF.                                      | 100                            | _     | 2500                         | MHz              |

|                               | OSCin                | f <sub>OSC</sub>  | _                                                                                                                 | _                              | 4     | 10                           | MHz              |

|                               |                      | Pfin1             | 2300 to 2500 MHz                                                                                                  | -4                             | _     | 6                            | dBm              |

|                               |                      | Pfin2             | 1900 to 2300 MHz                                                                                                  | -7                             | _     | 6                            | dBm              |

| Permissible input voltage     | fin                  | Pfin3             | 1000 to 1900 MHz                                                                                                  | -10                            | _     | 6                            | dBm              |

|                               |                      | Pfin4             | 100 to 1000 MHz                                                                                                   | -20                            | _     | 6                            | dBm              |

|                               | OSCin                | Vosc              | _                                                                                                                 | 0.5                            | _     | _                            | V <sub>P-P</sub> |

| High level input voltage      | Other the fin        | V <sub>IH</sub>   |                                                                                                                   | V <sub>CC</sub> × 0.7<br>+ 0.4 |       |                              | V                |

| Low level input voltage       | and OSCin            | V <sub>IL</sub>   | _                                                                                                                 | _                              | _     | V <sub>CC</sub> ×0.3<br>-0.4 | V                |

| High level input current      | Data, Clock,         | I <sub>IH</sub>   | _                                                                                                                 | _                              | 1.0   | _                            | μΑ               |

|                               | LE                   | I <sub>IL</sub>   | _                                                                                                                 | _                              | -1.0  | _                            | μΑ               |

| Low level input current       | FC                   | I <sub>ILFC</sub> | _                                                                                                                 | _                              | -60   | _                            | μΑ               |

| Input current                 | OSCin                | I <sub>IOSC</sub> | _                                                                                                                 | _                              | ±50   | _                            | μΑ               |

| High level output voltage     | Excluding            | V <sub>OH</sub>   | When V <sub>CC</sub> = 5 V                                                                                        | 4.4                            | _     | _                            | V                |

| Low level output voltage      | Do and BC            | V <sub>OL</sub>   | _                                                                                                                 | _                              | _     | 0.4                          | V                |

| High impedance cutoff current | Do 1, 2 BC<br>1 to 4 | I <sub>OFF</sub>  | _                                                                                                                 | _                              | _     | 1.1                          | μΑ               |

| Output ourrant                | Excluding            | I <sub>OH</sub>   | _                                                                                                                 | -1.0                           | _     | _                            | mA               |

| Output current                | Do and BC            | I <sub>OL</sub>   | _                                                                                                                 | 1.0                            | _     | _                            | mA               |

| Output voltage breakdown      | BC1 to 4             | V <sub>B</sub>    | _                                                                                                                 | _                              | _     | 12                           | V                |

## **FUNCTIONAL DESCRIPTIONS**

## 1. Formula for calculation of divide ratio

Set divider's divide ratio according to the following formula:

fvco =  $[(P \times N) + (16 \times A)] \times fosc \div R$

where

fvco : Externally connected VCO output frequency

P : Prescaler divide ratio (256 or 512)

N : Binary 12-bit programmable counter setting (32 to 4095)

A : Binary 5-bit swallow counter setting (0 to 31)

fosc : Reference oscillation frequency

R : Reference counter setting (256, 512, 1024, 2048)

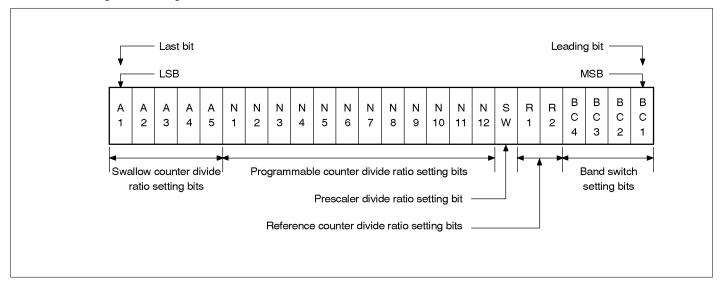

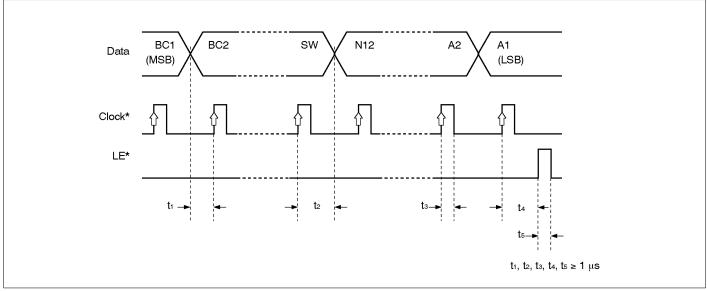

## 2. Serial data input procedure

Serial data is input from three inputs, Data pin, Clock pin and LE pin, allowing for control of the 4-bit band switch setting, the 3-bit reference divider and the 17-bit comparison divider respectively. The data is sequentially fetched into the internal shift register at the rising edge of the clock and transferred to the latch when load enable is at the "H" level.

The 24-bit shift register is configured as follows:

## • Band switch setting (BC1 to BC4)

When data set in the band bits is at "H," output is turned ON. When data is at "L," output is turned OFF.

## • Prescaler divide ratio (SW)

Divided by 256/272 when data set in the SW bit is at "H." Divided by 512/528 when data is at "L."

## • Divide ratios for 5-bit swallow counter (A1 to A5)

| Divide ratio A | A5 | A4 | А3 | A2 | A1 |

|----------------|----|----|----|----|----|

| 0              | 0  | 0  | 0  | 0  | 0  |

| 1              | 0  | 0  | 0  | 0  | 1  |

| 2              | 0  | 0  | 0  | 1  | 0  |

| •              | •  | •  | •  | •  | •  |

| •              | •  | •  | •  | •  | •  |

| 31             | 1  | 1  | 1  | 1  | 1  |

## Reference counter divide ratios (R1 and R2)

| Divide ratio R | R2 | R1 |

|----------------|----|----|

| 256            | 0  | 0  |

| 512            | 0  | 1  |

| 1024           | 1  | 0  |

| 2048           | 1  | 1  |

## • Divide ratios for 12-bit programmable counter (N1 to N12)

| Divide ratios | N12 | N11 | N10 | N9 | N8 | N7 | N6 | N5 | N4 | N3 | N2 | N1 |

|---------------|-----|-----|-----|----|----|----|----|----|----|----|----|----|

| 0             | 0   | 0   | 0   | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 1             | 0   | 0   | 0   | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 1  |

| 2             | 0   | 0   | 0   | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  |

| •             | •   | •   | •   | •  | •  | •  | •  | •  | •  | •  | •  | •  |

| •             | •   | •   | •   | •  | •  | •  | •  | •  | •  | •  | •  | •  |

| 4095          | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

## 3. Serial data input timings

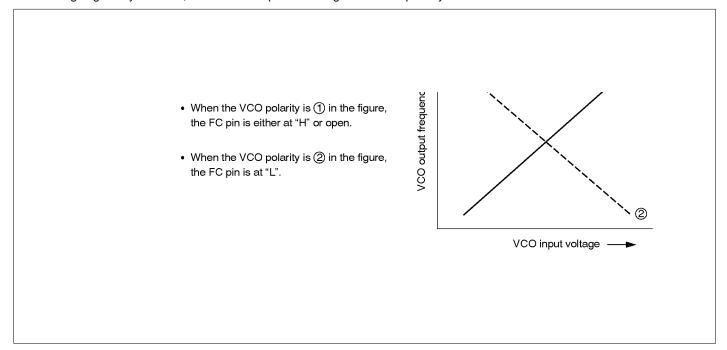

When designing the synthesizer, control the FC pin according to the VCO polarity.

<sup>\*:</sup> Fetches data at the rising edge of the clock.

## 4. FC pin input in relation to phase characteristics

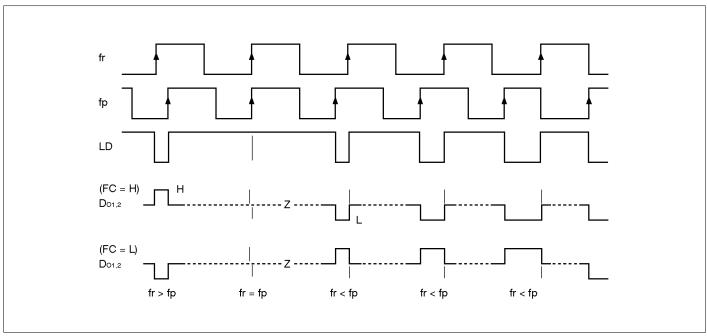

The FC pin switches the phase of the phase comparator. Phase characteristics (charge pump output) are inverted by controlling this pin. Output from the phase comparator input monitor pin (fout) is also controlled by this FC pin. The relation of FC pin input with Do and fout is as follows:

|                                                            | FC: "H" (     | (or open)           | FC:      | "L"                 |

|------------------------------------------------------------|---------------|---------------------|----------|---------------------|

|                                                            | DO1, DO2 fout |                     | DO1, DO2 | fout                |

| fr>fp                                                      | Н             | Outputs reference   | L        | Outputs comparison  |

| fr=fp                                                      | Z             | divider output (fr) | Z        | divider output (fp) |

| fr <fp< td=""><td>L</td><td></td><td>L</td><td></td></fp<> | L             |                     | L        |                     |

Z: high impedance

<sup>\*:</sup> Fetches data when LE is at "H" level.

When designing the synthesizer, control the FC pin according to the VCO polarity.

## PHASE COMPARATOR OUTPUT WAVEFORMS

## Notes:

- 1. The phase error is detected in a range of 2  $\pi$  to +2  $\pi$ .

- 2. Output of a "glitch" varies slightly with charge pump characteristics. This "glitch" is output to eliminate an dead band.

## **EXAMPLE MEASUREMENT CIRCUIT (PRESCALER INPUT SENSITIVITY)**

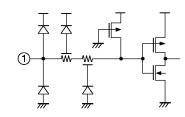

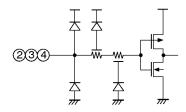

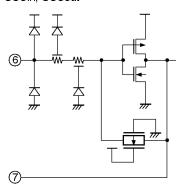

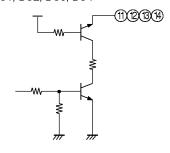

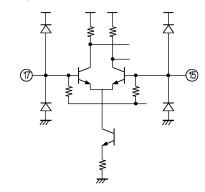

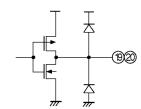

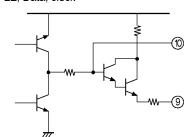

## **EQUIVALENT CIRCUIT DIAGRAM**

• LE, Data, clock

OSCin, OSCout

• BC1, BC2, BC3, BC4

• <del>fin</del>, fin

• LE, Data, clock

• LE, Data, clock

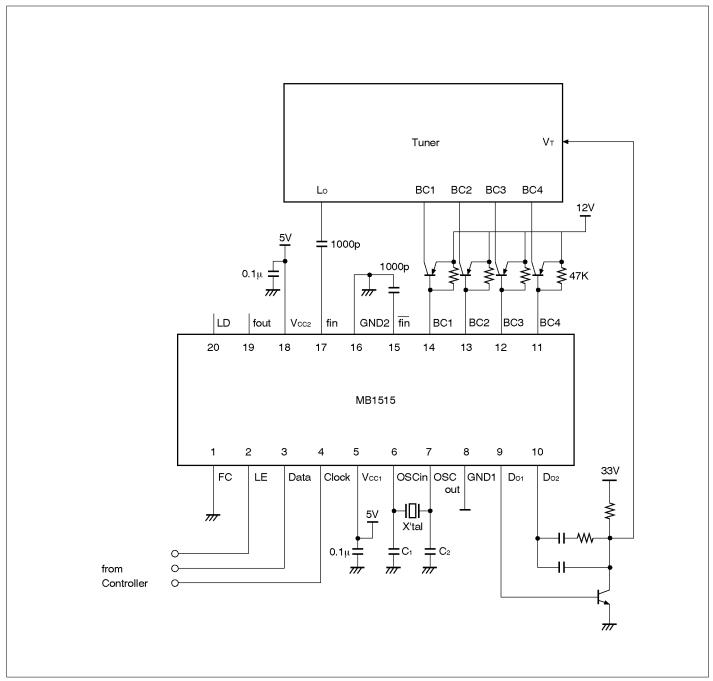

## **EXAMPLE APPLICATION**

C1, C2: Determined by the crystal oscillator

FC: with pull up resistor

## **ORDERING INFORMATION**

| Parts Number | Package                                | Notes |

|--------------|----------------------------------------|-------|

| MB1515PFV    | Plastic SSOP, 20 pins<br>(FPT–20P–M03) |       |

## **EXTERNAL DIMENSIONS**

## **NOTES**

## All Rights Reserved.

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical semiconductor applications. Complete information sufficient for construction purposes is not necessarily given.

The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu assumes no responsibility for inaccuracies.

The information contained in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu.

Fujitsu reserves the right to change products or specifications without notice.

This document contains information on a new product. Specification and information herein are subject to change without notice.

No part of this publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu.

# **FUJITSU LIMITED**

For further information please contact:

## **Japan**

FUJITSU LIMITED

Electronic Devices International

Sales and Engineering Support Division

1015, Kamikodanaka Nakahara-ku,

Kawasaki 211, Japan

Tel: (044) 754-3753

FAX: (044) 754-3332

#### North and South America

FUJITSU MICROELECTRONICS, INC. Logic Products Division 3545 North First Street San Jose, CA 95134-1804, USA Tel: 408-922-9000 FAX: 408-432-9044

## **Europe**

FUJITSU MIKROELEKTRONIK GmbH Am Siebenstein 6-10, 6072 Dreieich-Buchschlag, Germany Tel: (06103) 690-0 Telex: 411963

## Asia

FUJITSU MICROELECTRONICS ASIA PTE LIMITED 51 Bras Basah Road, Plaza By The Park, #06-04 to #06-07 Singapore 0719 Tel: 336-1600 Telex: 55573 FAX: 336-1609

## Sales Offices

FAX: (06103) 690-122

#### California

2880 Lakeside Drive, Suite 250 Santa Clara, CA 95054 (408) 982–1800

Century Center 2603 Main Street, #510 Irvine, CA 92714 (714) 724–8777

#### Colorado

12000 North Washington Street, #370 Thornton, CO 80241 (303) 254–9901

## Georgia

3500 Parkway Lane, #210 Norcross, GA 30092 (404) 449–8539

#### Illinois

One Pierce Place, #1245 Itasca, IL 60143–2662 (708) 250–8580

## **Massachusetts**

1000 Winter Street, #2500 Waltham, MA 02154 (617) 487–0029

## Minnesota

3800 West 80th Street, #430 Bloomington, MN 55431–4419 (612) 893–5570

#### **New York**

898 Veterans Memorial Highway Building 2, Suite 310 Hauppauge, NY 11788 (516) 582–8700

#### Oregon

15220 N.W. Greenbrier Parkway, #360 Beaverton, OR 97006 (503) 690–1909

#### Texas

14785 Preston Rd., #274 Dallas, TX 75240 (214) 233–9394

20515 SH 249, Suite 485 Houston, TX 77070 (713) 379–3030

©FUJITSU LIMITED 1994 DS04-21317-2E