## CHIPSET OF RINGING SUBSCRIBER LINE INTERFACE CIRCUIT (RSLIC) & QUAD PROGRAMMABLE PCM CODEC

PRELIMINARY IDT82V1671 (RSLIC) IDT82V1074 (CODEC)

## **FEATURES**

- · Programmable DC feeding characteristics

- · Programmable digital filters adapting to different requirements:

- Impedance matching

- Transhybrid balance

- Transmit and receive gain adjustment

- Frequency response correction

- Off-hook and ground-key detection

- AC/DC ring trip detection

- Programmable internal balanced ringing without external components

- · Supports external ringing

- Selectable MPI and GCI interfaces

- Supports A/µ-law compressed and linear data formats

- Programmable IO pins with relay-driving or analog input capability

- · Line polarity reversal

- Integrated FSK generator for sending Caller ID information

- On-hook transmission

- · 2 programmable tone generators per channel

- Integrated Universal Tone Detection (UTD) unit for fax/modem tone detection

- Integrated Test and Diagnosis Functions (ITDF)

- Three-party conference

- Only battery and 3.3 V power supply needed

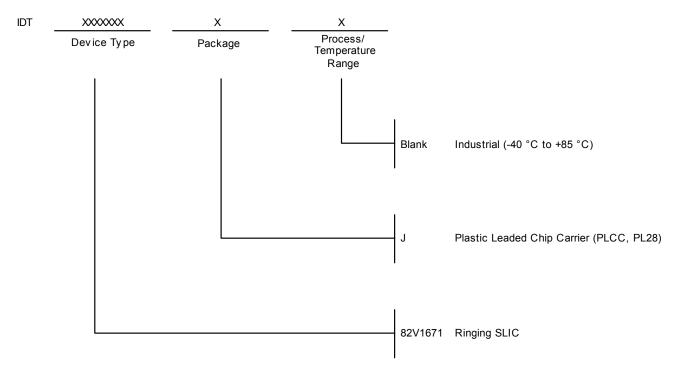

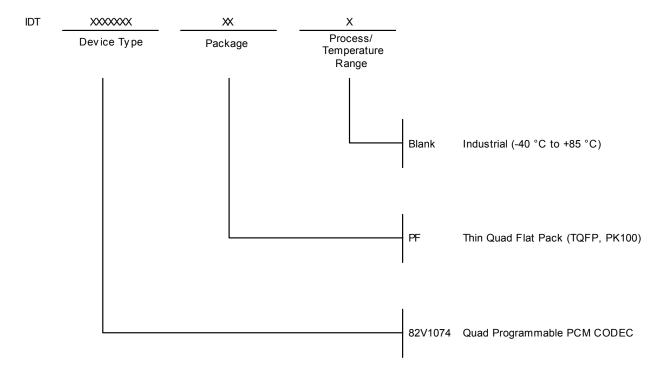

- · Package available:

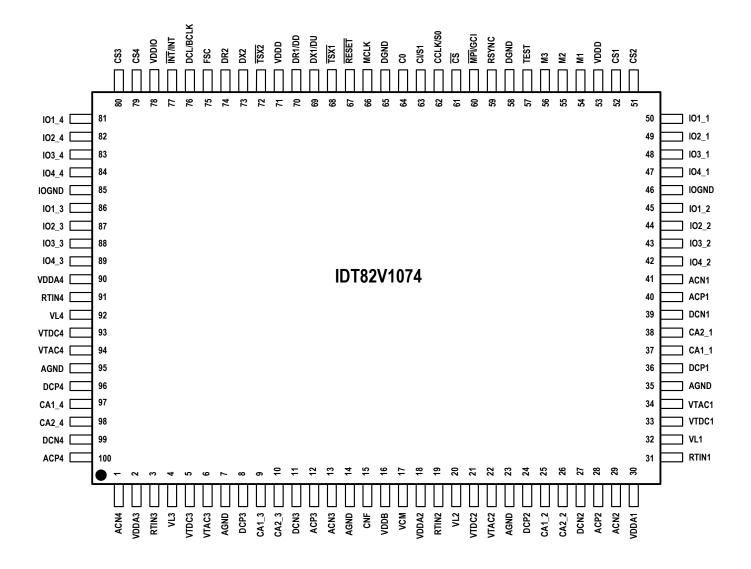

IDT82V1671: 28 pin PLCC IDT82V1074: 100 pin TQFP

## **DESCRIPTION**

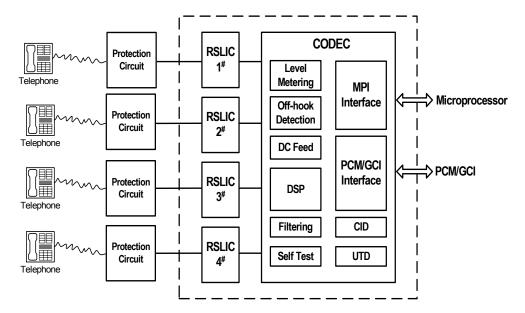

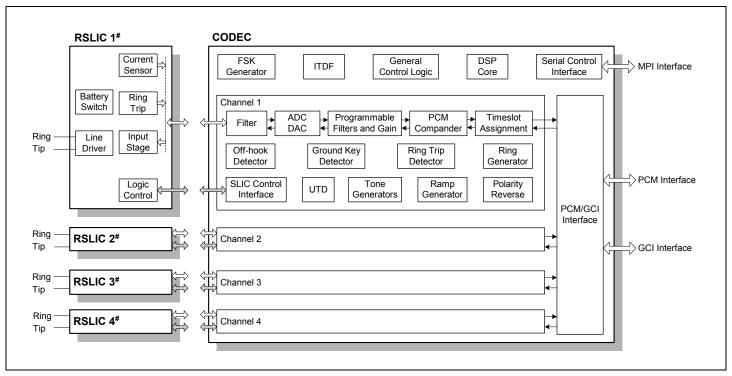

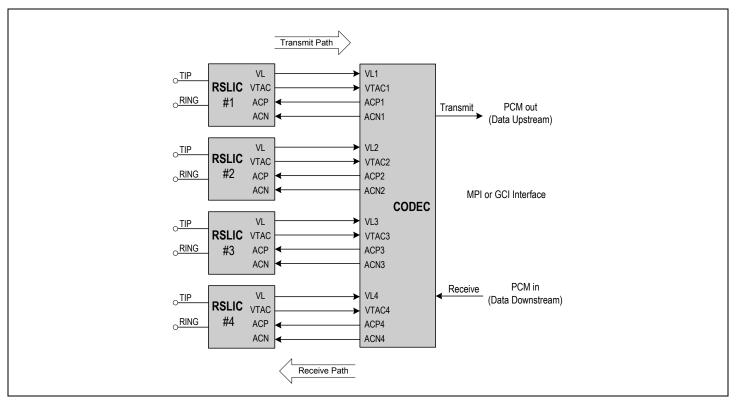

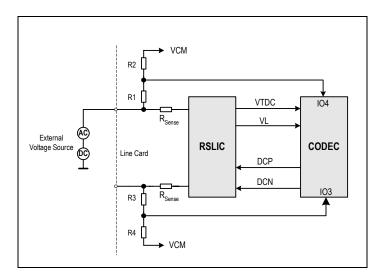

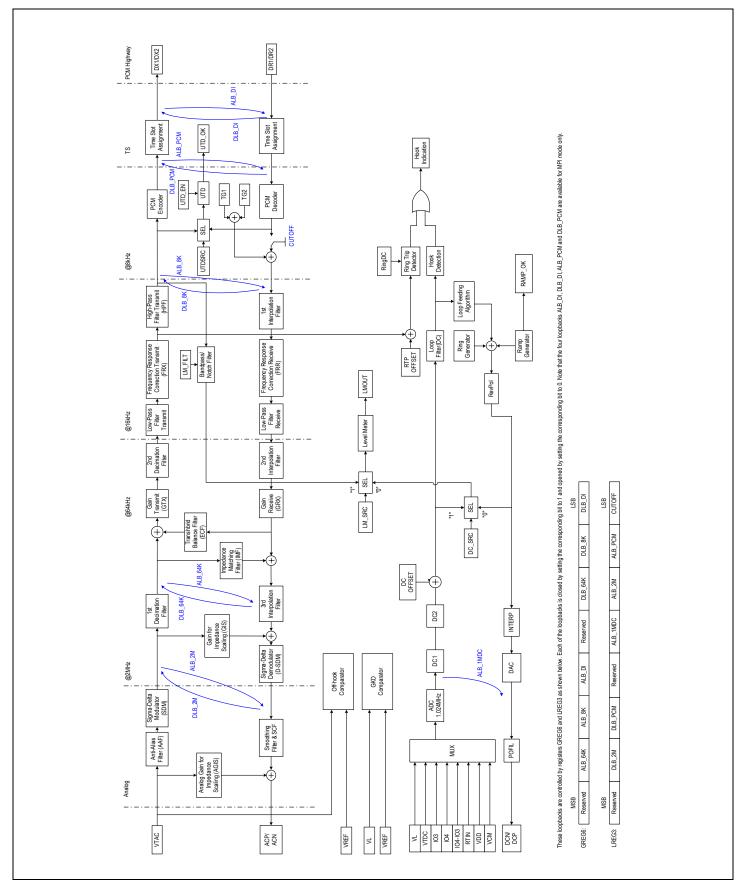

The RSLIC-CODEC chipset is comprised of one four-channel programmable PCM CODEC (IDT82V1074) and four single-channel ringing SLICs (IDT82V1671). The chipset provides a total solution for line card designs. In addition to providing a complete software programmable solution for BORSCHT, additional functions such as FSK generator, Universal Tone Detection (UTD) unit, tone generators, ringing generator, Integrated Test and Diagnosis Functions (ITDF), line polarity reversal and three-party conference are integrated in to the chipset. The high integration of system functions reduces board space requirements of the line card and saves cost.

The chipset is fully programmable via a Microprocessor Interface (MPI) or a General Circuit Interface (GCI). In both MPI and GCI modes, the chipset supports  $A/\mu$ -law companding format or linear data format.

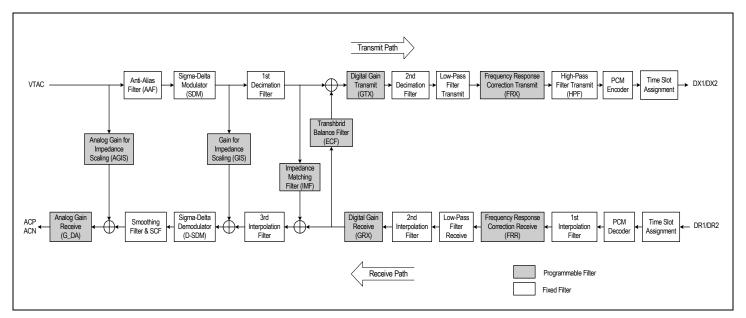

Programmable digital filters on the chipset provide the necessary transmit and receive filtering to realize impedance matching, transhybrid balance, frequency response correction and transmit/receive gains adjustment. The full programmability optimizes the performance of line card products and allows one line card to adapt to different requirements worldwide.

The powerful Integrated Test and Diagnosis Functions (ITDF) accomplish necessary tests and measurements without external test equipment or relays. This brings convenience to system maintenance and diagnosis.

This chipset can be used in digital telecommunication applications such as VoIP, VoATM, PBX, CO and DLC etc.

## **CHIPSET FUNCTIONAL BLOCK DIAGRAM**

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

**APRIL 22, 2003**

1

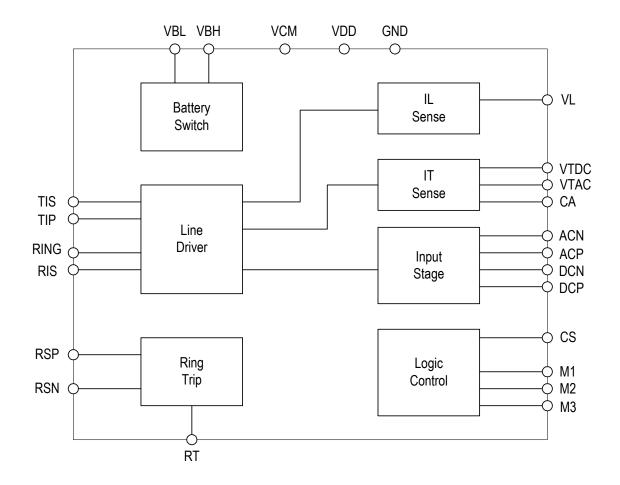

## **RSLIC FUNCTIONAL BLOCK DIAGRAM**

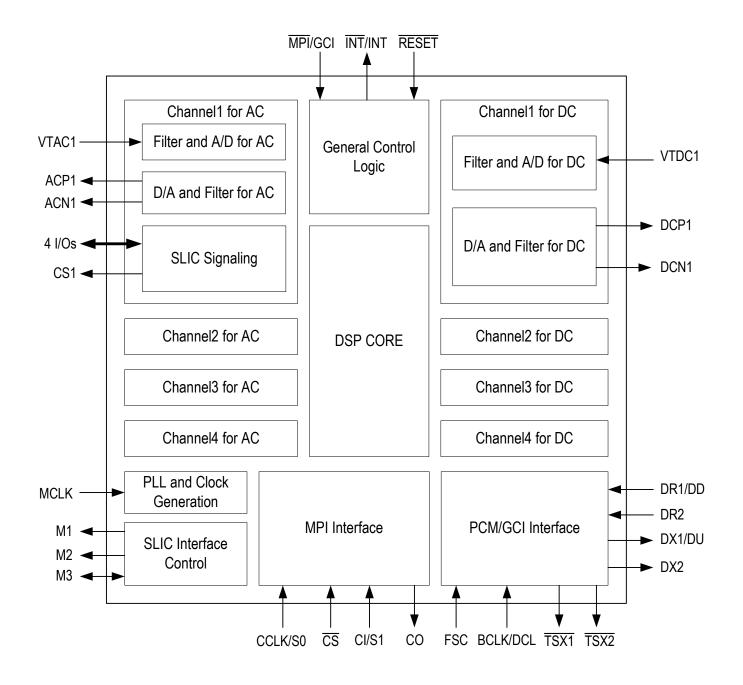

## **CODEC FUNCTIONAL BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| 1 | Pin C                  | Configur | ations      |                                              | 9       |  |  |  |

|---|------------------------|----------|-------------|----------------------------------------------|---------|--|--|--|

|   | 1.1                    | RSLIC    | Pin Confi   | guration                                     | <u></u> |  |  |  |

|   | 1.2                    | CODE     | C Pin Con   | nfiguration                                  | 10      |  |  |  |

| _ | D: E                   |          |             |                                              |         |  |  |  |

| 2 |                        | -        |             |                                              |         |  |  |  |

|   | 2.1                    |          |             | ription                                      |         |  |  |  |

|   | 2.2                    | CODE     | C Pin Des   | cription                                     | 12      |  |  |  |

| 3 | Fund                   | tional D | escriptio   | n                                            | 16      |  |  |  |

| • | 3.1 Functions Overview |          |             |                                              |         |  |  |  |

|   | •                      | 3.1.1    |             | unctions                                     |         |  |  |  |

|   |                        | 3.1.2    |             | al Functions                                 |         |  |  |  |

|   |                        | 3.1.3    |             | nmable Functions                             |         |  |  |  |

|   | 3.2                    |          |             |                                              |         |  |  |  |

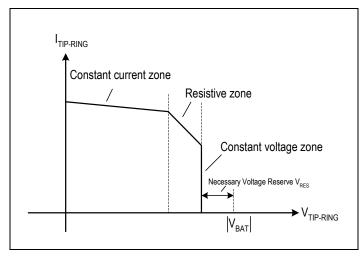

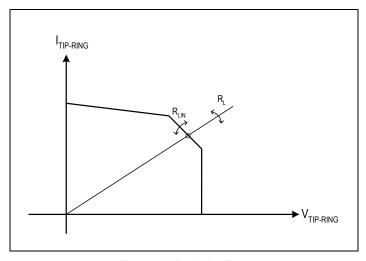

|   |                        | 3.2.1    | •           | ding Characteristic Zones                    |         |  |  |  |

|   |                        | 3.2.2    |             | t Current Zone                               |         |  |  |  |

|   |                        | 3.2.3    | Resistive   | e Zone                                       | 17      |  |  |  |

|   |                        | 3.2.4    | Constan     | t Voltage Zonet                              | 17      |  |  |  |

|   |                        | 3.2.5    | DC Feed     | ding Characteristics Configuration           | 18      |  |  |  |

|   | 3.3                    | Speec    |             | ing                                          |         |  |  |  |

|   |                        | 3.3.1    | AC Tran     | smission                                     | 19      |  |  |  |

|   |                        |          | 3.3.1.1     | Transmit Path                                | 19      |  |  |  |

|   |                        |          | 3.3.1.2     | Receive Path                                 | 20      |  |  |  |

|   |                        | 3.3.2    | Program     | mable Filters                                |         |  |  |  |

|   |                        |          | 3.3.2.1     | Impedance Matching                           |         |  |  |  |

|   |                        |          | 3.3.2.2     | Transhybrid Balance                          |         |  |  |  |

|   |                        |          | 3.3.2.3     | Frequency Response Correction                |         |  |  |  |

|   |                        |          | 3.3.2.4     | Gain Adjustment                              |         |  |  |  |

|   | 3.4                    | -        |             | rip                                          |         |  |  |  |

|   |                        | 3.4.1    |             | Ringing Mode                                 |         |  |  |  |

|   |                        |          | 3.4.1.1     | Internal Ringing Generation                  |         |  |  |  |

|   |                        | 2.4.0    | 3.4.1.2     | Ring Trip Detection In Internal Ringing Mode |         |  |  |  |

|   |                        | 3.4.2    |             | Ringing Mode                                 |         |  |  |  |

|   | 3.5                    | Cupon    |             | Ring Trip Detection In External Ringing Mode |         |  |  |  |

|   | 3.3                    | 3.5.1    | Supervision |                                              |         |  |  |  |

|   |                        | 3.5.2    |             |                                              |         |  |  |  |

|   | 3.6                    |          |             | arity Reversal                               |         |  |  |  |

|   | 3.0                    |          |             | I Processing                                 |         |  |  |  |

|   | 0.1                    | 3.7.1    | •           | enerator                                     |         |  |  |  |

|   |                        | 0.7.1    | 3.7.1.1     | DTMF Generation                              |         |  |  |  |

|   |                        | 3.7.2    | •           | neration for Caller ID                       |         |  |  |  |

|   |                        | 3.7.3    |             | al Tone Detection (UTD)                      |         |  |  |  |

|   |                        |          |             | Introduction                                 |         |  |  |  |

|   |                        |          |             | UTD Principle                                |         |  |  |  |

|   |                        |          |             | UTD Programming                              |         |  |  |  |

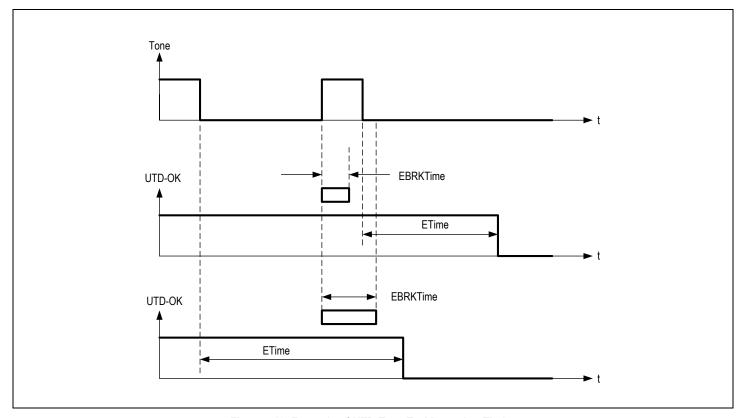

|   | 3.8                    | Three-   | Party Con   | ference                                      | 36      |  |  |  |

|   |                        | 3.8.1    | Introduc    | tion                                         | 36      |  |  |  |

|   |                        | 3.8.2    | PCM Int     | erface Configuration                         | 36      |  |  |  |

|   |                        | 3.8.3    | Control     | the Active PCM Channels                      | 37      |  |  |  |

|   | 3.9                    | ITDF     |             |                                              |         |  |  |  |

|   |                        | 3.9.1    |             | tion                                         |         |  |  |  |

|   |                        | 3.9.2    | Diagnos     | is and Test Functions                        | 39      |  |  |  |

|   |                        | 3.9.3    | •           | ed Signal Generators                         |         |  |  |  |

|   |                        | 3.9.4    |             | eter                                         |         |  |  |  |

|   |                        |          | 3.9.4.1     | Level Meter Source Selection                 | 39      |  |  |  |

|   |            |        | 3.9.4.2 Level Meter Gain Filter and Rectifier              | 40 |

|---|------------|--------|------------------------------------------------------------|----|

|   |            |        | 3.9.4.3 Level Meter Integrator                             | 41 |

|   |            |        | 3.9.4.4 Level Meter Result Register                        | 42 |

|   |            |        | 3.9.4.5 Level Meter Shift Factor                           | 42 |

|   |            |        | 3.9.4.6 Level Meter Threshold Setting                      |    |

|   |            | 3.9.5  | Measurement via AC Level Meter                             |    |

|   |            |        | 3.9.5.1 Current Measurement via VTAC                       |    |

|   |            |        | 3.9.5.2 AC Level Meter Operational State Flow              | 44 |

|   |            | 3.9.6  | Measurement via DC Level Meter                             |    |

|   |            |        | 3.9.6.1 Offset Current Measurement                         |    |

|   |            |        | 3.9.6.2 Leakage Current Measurement                        |    |

|   |            |        | 3.9.6.3 Loop Resistance Measurement                        |    |

|   |            |        | 3.9.6.4 Line Resistance Tip/GND and Ring/GND               |    |

|   |            |        | 3.9.6.5 Capacitance Measurement                            |    |

|   |            |        | 3.9.6.6 Voltage Measurement                                |    |

|   |            |        | 3.9.6.7 Voltage Offset Measurement                         |    |

|   |            |        | 3.9.6.8 Ring Trip Operational Amplifier Offset Measurement | 48 |

| 4 | Inter      | face   |                                                            | 40 |

| _ | 4.1        |        | MPI Interface                                              |    |

|   | 7.1        | 4.1.1  | MPI Control Interface                                      |    |

|   |            | 4.1.2  | PCM Interface                                              |    |

|   |            | 7.1.2  | 4.1.2.1 PCM Clock Configuration                            |    |

|   |            |        | 4.1.2.2 Time Slot Assignment                               |    |

|   |            |        | 4.1.2.3 PCM Highway Selection                              |    |

|   | 4.2        | GCI In | nterface                                                   |    |

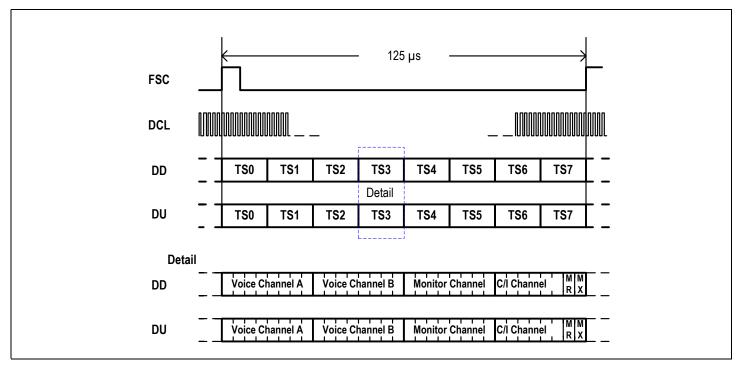

|   | 1.2        | 4.2.1  | Compressed GCI Mode                                        |    |

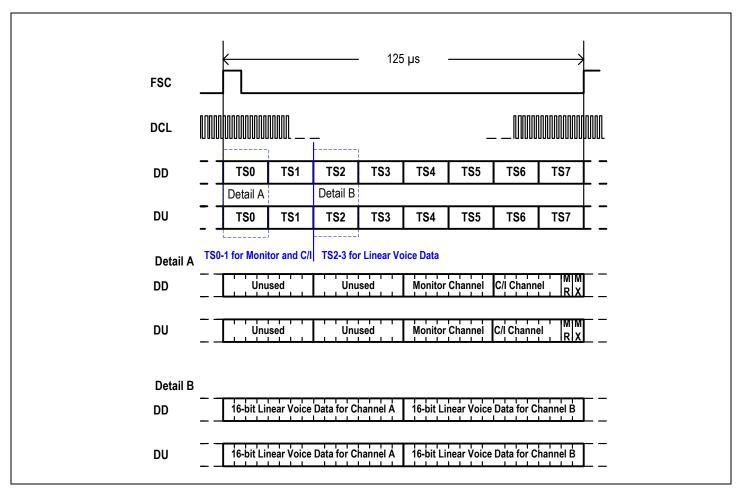

|   |            | 4.2.2  | Linear GCI Mode                                            |    |

|   |            | 4.2.3  | Command/Indication (C/I) Channel                           |    |

|   |            | 1.2.0  | 4.2.3.1 Downstream C/I Channel Byte                        |    |

|   |            |        | 4.2.3.2 Upstream C/I Channel Byte                          |    |

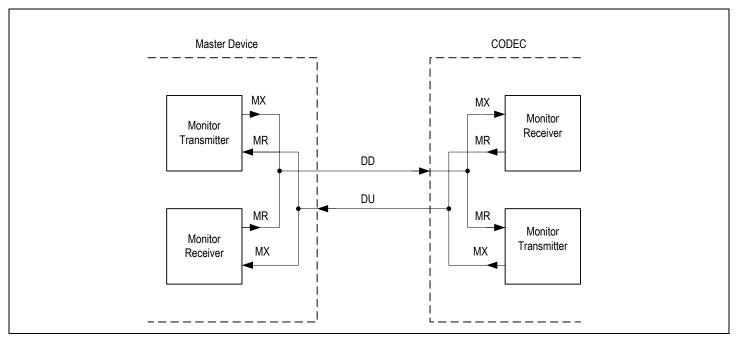

|   |            | 4.2.4  | GCI Monitor Transfer Protocol                              |    |

|   |            |        | 4.2.4.1 Monitor Channel Operation                          |    |

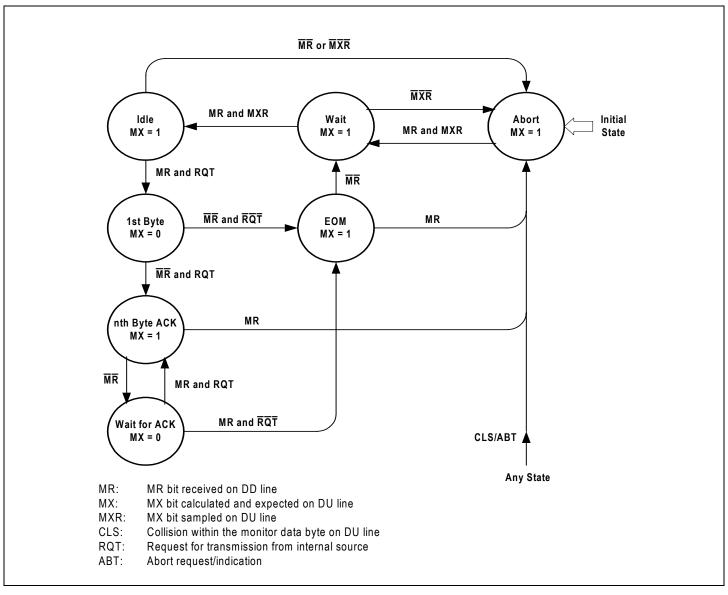

|   |            |        | 4.2.4.2 Monitor Handshake Procedure                        |    |

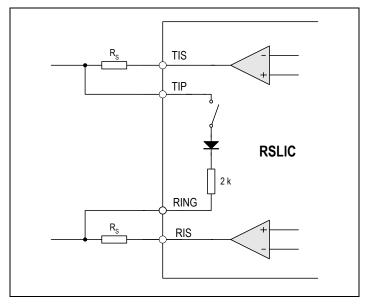

|   | 4.3        | Analog | g POTS Interface                                           |    |

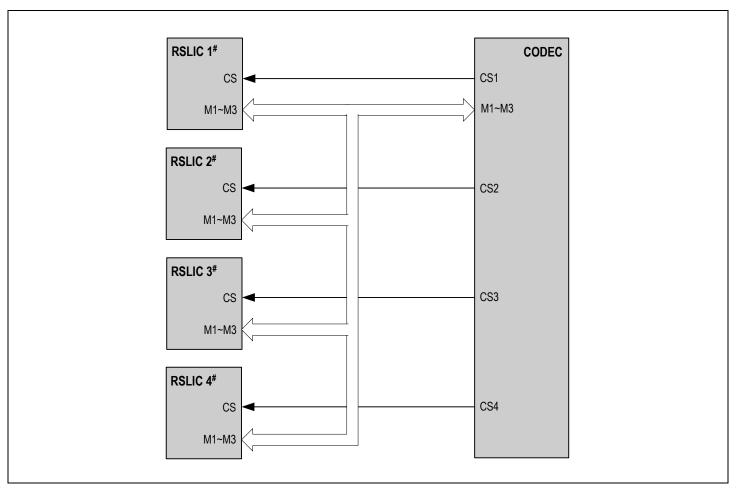

|   | 4.4        |        | C and CODEC Interface                                      |    |

|   |            |        |                                                            |    |

| 5 |            |        | ng                                                         |    |

|   | 5.1        |        | iew                                                        |    |

|   |            | 5.1.1  | MPI Programming                                            |    |

|   |            |        | 5.1.1.1 Broadcast Mode for MPI Programming                 |    |

|   |            | E 4 0  | 5.1.1.2 Identification Code for MPI Programming            |    |

|   |            | 5.1.2  | GCI Programming                                            |    |

|   |            |        | 5.1.2.1 Program Start Byte for GCI Programming             |    |

|   | <b>-</b> 0 | D      | 5.1.2.2 Identification Command for GCI Programming         |    |

|   | 5.2        |        | ter/RAM Commands                                           |    |

|   |            | 5.2.1  | Register/RAM Command Format                                |    |

|   |            | 5.2.2  | Addressing the Local Registers                             |    |

|   |            | 5.2.3  | Addressing the Global Registers                            |    |

|   |            | 5.2.4  | Addressing the FSK-RAM                                     |    |

|   | r 0        | 5.2.5  | Addressing the Coe-RAM                                     |    |

|   | 5.3        | _      | ters Description                                           |    |

|   |            | 5.3.1  | Registers Overview                                         |    |

|   |            | 5.3.2  | Global Registers List                                      |    |

|   | <i></i>    | 5.3.3  | Local Registers List                                       |    |

|   | 5.4        |        | amming Examples                                            |    |

|   |            | 5.4.1  | Programming Examples for MPI Mode                          |    |

|   |            |        | 5.4.1.1 Example of Programming the Local Registers via MPI | 82 |

|   |            |                                         | 5.4.1.2     | Example of Programming the Global Registers via MPI | 83  |  |  |  |

|---|------------|-----------------------------------------|-------------|-----------------------------------------------------|-----|--|--|--|

|   |            |                                         | 5.4.1.3     | Example of Programming the Coefficient-RAM via MPI  |     |  |  |  |

|   |            |                                         | 5.4.1.4     | Example of Programming the FSK-RAM via MPI          |     |  |  |  |

|   |            | 5.4.2                                   | -           | nming Examples for GCI Mode                         |     |  |  |  |

|   |            | • • • • • • • • • • • • • • • • • • • • | 5.4.2.1     | Example of Programming the Local Registers via GCI  |     |  |  |  |

|   |            |                                         |             | Example of Programming the Global Registers via GCI |     |  |  |  |

|   |            |                                         |             | Example of Programming the Coefficient-RAM via GCI  |     |  |  |  |

|   |            |                                         | 5.4.2.4     | Example of Programming the FSK-RAM via GCI          |     |  |  |  |

| _ | _          |                                         |             |                                                     |     |  |  |  |

| 6 | •          |                                         | •           | on                                                  |     |  |  |  |

|   | 6.1        |                                         | •           | S                                                   |     |  |  |  |

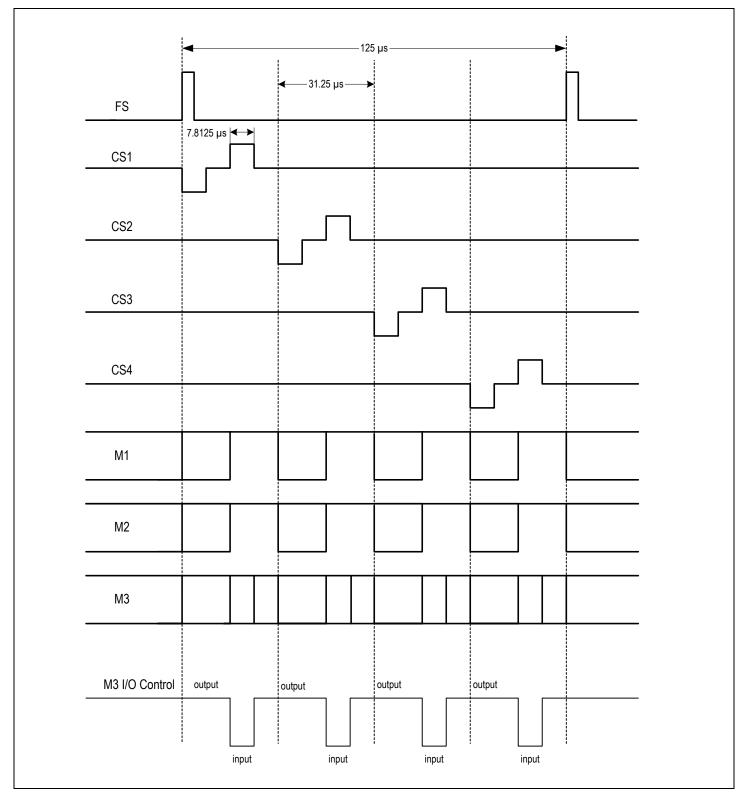

|   |            | 6.1.1                                   |             | Control Signaling                                   |     |  |  |  |

|   |            | 6.1.2                                   |             | Operating Modes                                     |     |  |  |  |

|   | 6.2        | 6.1.3                                   |             | Operating Modesn                                    |     |  |  |  |

|   | 6.3        |                                         |             | /Os of the CODEC                                    |     |  |  |  |

|   | 6.4        | •                                       |             | ng                                                  |     |  |  |  |

|   | 6.5        |                                         |             | Test Loopbacks                                      |     |  |  |  |

|   | 6.6        | •                                       |             | n Sequence                                          |     |  |  |  |

|   | 6.7        |                                         |             | On Sequence                                         |     |  |  |  |

|   | 6.8        |                                         |             | ter Reset                                           |     |  |  |  |

|   |            | 6.8.1                                   |             | On Reset and Hardware Reset                         |     |  |  |  |

|   |            | 6.8.2                                   |             | e Reset                                             |     |  |  |  |

| _ |            |                                         |             |                                                     | 00  |  |  |  |

| 7 |            |                                         |             | tics                                                |     |  |  |  |

|   | 7.1        |                                         |             | I Characteristics                                   |     |  |  |  |

|   |            | 7.1.1<br>7.1.2                          |             | Absolute Maximum Ratings                            |     |  |  |  |

|   |            | 7.1.2                                   |             | Thermal Information                                 |     |  |  |  |

|   | 7.2        |                                         |             | al Characteristics                                  |     |  |  |  |

|   | 1.2        | 7.2.1                                   |             | Absolute Maximum Ratings                            |     |  |  |  |

|   |            | 7.2.2                                   |             | Recommended Operating Conditions                    |     |  |  |  |

|   |            | 7.2.3                                   |             | Digital Interface                                   |     |  |  |  |

|   |            | 7.2.4                                   |             | Power Dissipation                                   |     |  |  |  |

|   | 7.3        | Chipse                                  |             | ission Characteristics                              |     |  |  |  |

|   |            | 7.3.1                                   | Absolute    | e Gain                                              | 95  |  |  |  |

|   |            | 7.3.2                                   | Gain Tra    | acking                                              | 95  |  |  |  |

|   |            | 7.3.3                                   |             | ncy Response                                        |     |  |  |  |

|   |            | 7.3.4                                   |             | _OSS                                                |     |  |  |  |

|   |            | 7.3.5                                   |             | Oelay                                               |     |  |  |  |

|   |            | 7.3.6                                   |             | n                                                   |     |  |  |  |

|   |            | 7.3.7                                   |             |                                                     |     |  |  |  |

|   | <b>-</b> 4 | 7.3.8                                   |             | innel Crosstalk                                     |     |  |  |  |

|   | 7.4        |                                         | _           | Characteristics                                     |     |  |  |  |

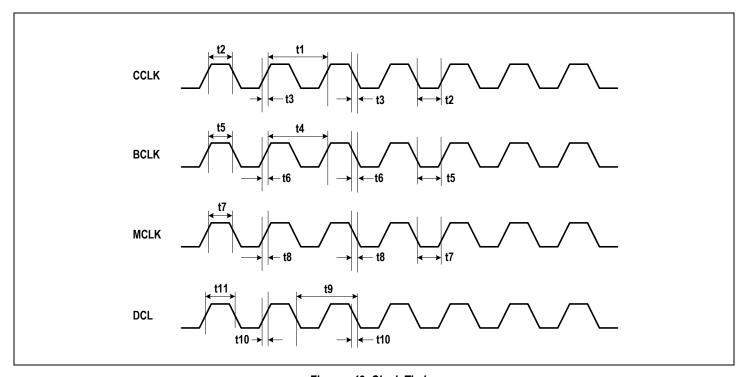

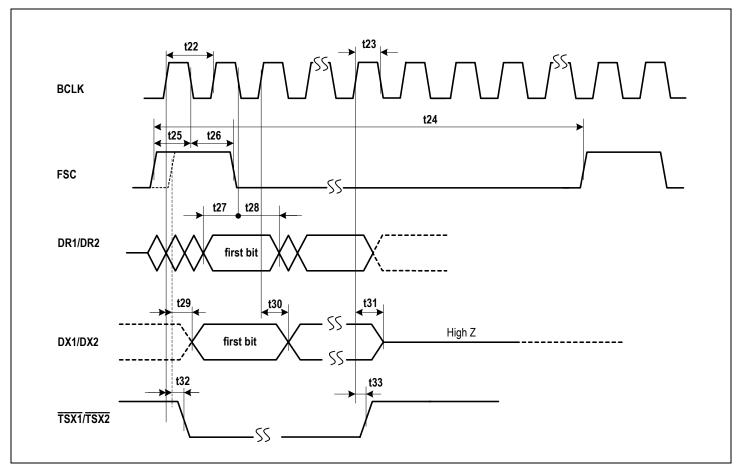

|   |            | 7.4.1                                   |             | iming                                               |     |  |  |  |

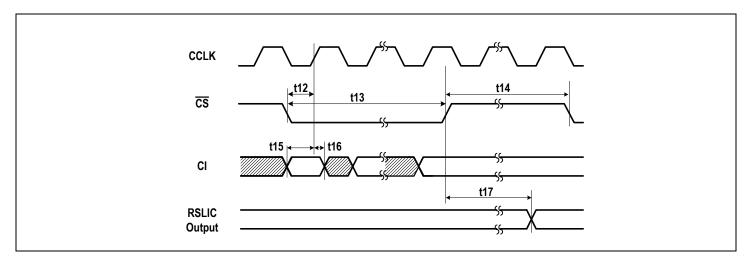

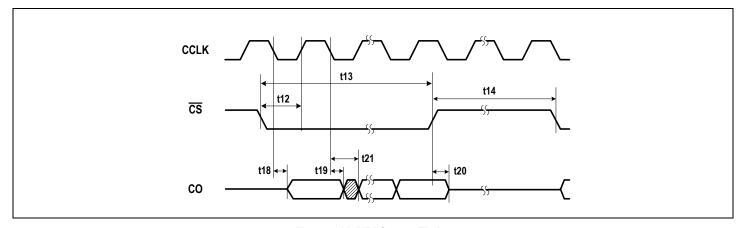

|   |            | 7.4.2                                   |             | ocessor Interface Timing                            |     |  |  |  |

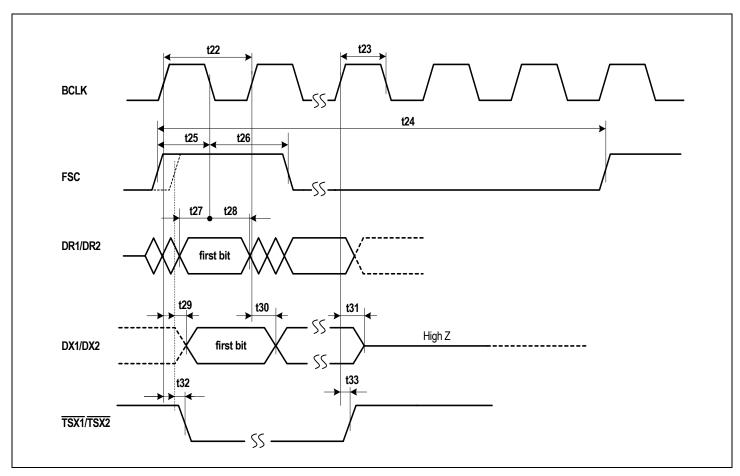

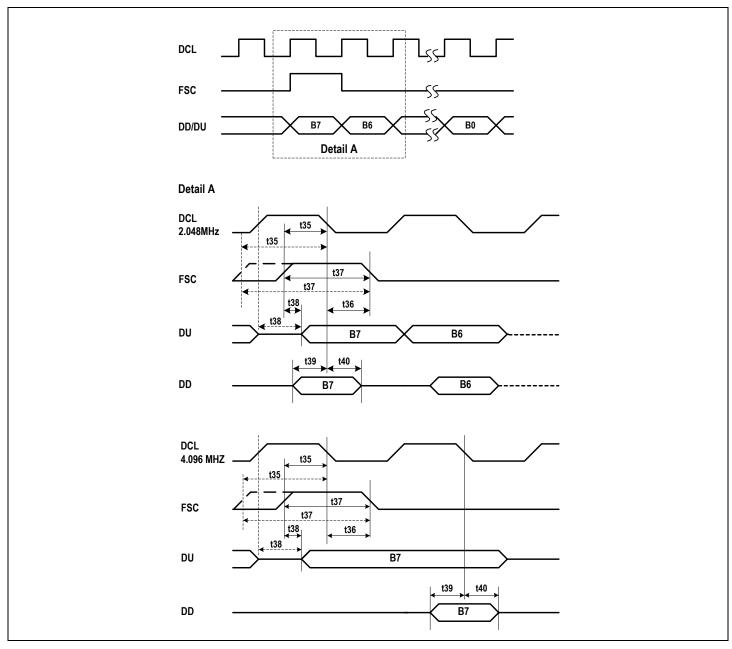

|   |            | 7.4.3<br>7.4.4                          |             | terface Timingerface Timing                         |     |  |  |  |

|   |            | 1.4.4                                   | GOTTILLE    | 31a0c 1111111g                                      | 102 |  |  |  |

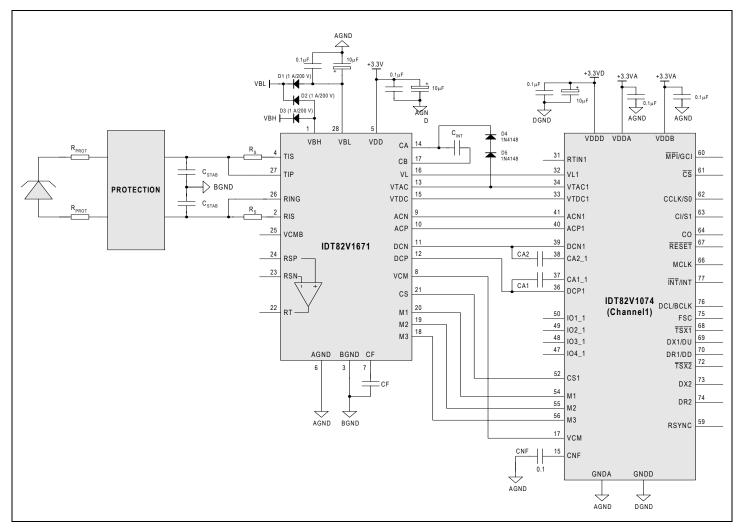

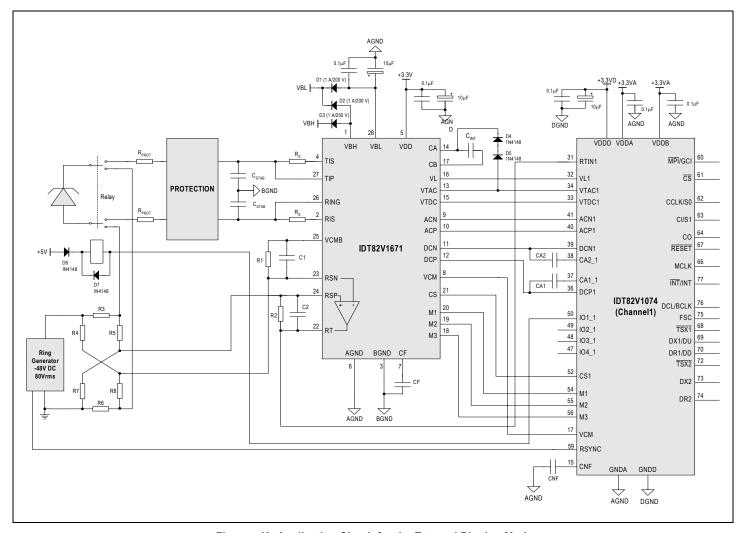

| 8 | Appl       |                                         |             |                                                     |     |  |  |  |

|   | 8.1        |                                         |             |                                                     |     |  |  |  |

|   | 8.2        | Applica                                 | ation Circu | uit for the External Ringing Mode                   | 104 |  |  |  |

| 9 | Orde       | erina Inf                               | ormation    |                                                     | 105 |  |  |  |

| - |            | J                                       |             | ***************************************             |     |  |  |  |

## **LIST OF FIGURES**

| Figure - 1  | Line Circuit Functions Included in the RSLIC-CODEC Chipset  |     |

|-------------|-------------------------------------------------------------|-----|

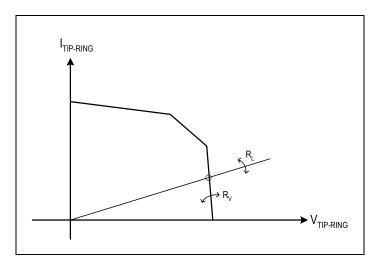

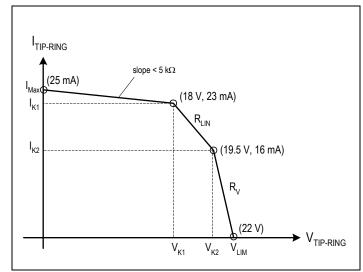

| Figure - 2  | DC Feeding Zones                                            |     |

| Figure - 3  | Constant Current Zone                                       |     |

| Figure - 4  | Resistive Zone                                              |     |

| Figure - 5  | Constant Voltage Zone                                       | 18  |

| Figure - 6  | DC Feeding Characteristics Configuration                    | 18  |

| Figure - 7  | Signal Paths for AC Transmission                            |     |

| Figure - 8  | Voice Signal Path of the CODEC                              | 19  |

| Figure - 9  | Nyquist Diagram                                             | 20  |

| Figure - 10 | Internal Balanced Ringing                                   | 22  |

| Figure - 11 | External Ringing Synchronization                            | 24  |

| Figure - 12 | Hysteresis for Off-Hook Detection                           | 26  |

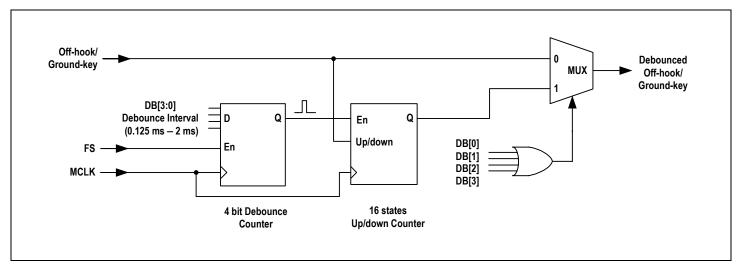

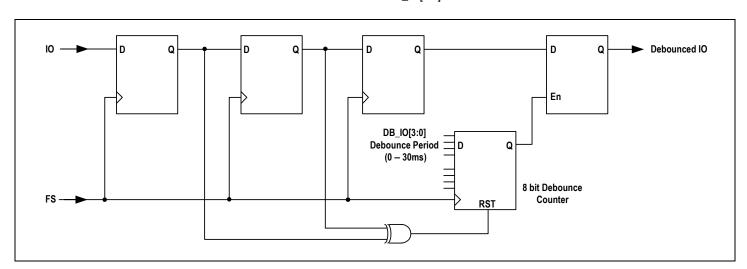

| Figure - 13 | Debounce Filter for Off-hook/Ground-key Detection           | 27  |

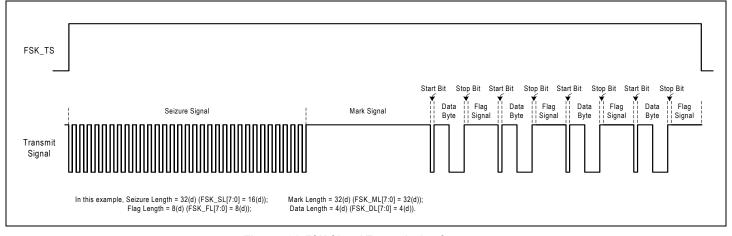

| Figure - 14 | FSK Signal Transmission Sequence                            | 30  |

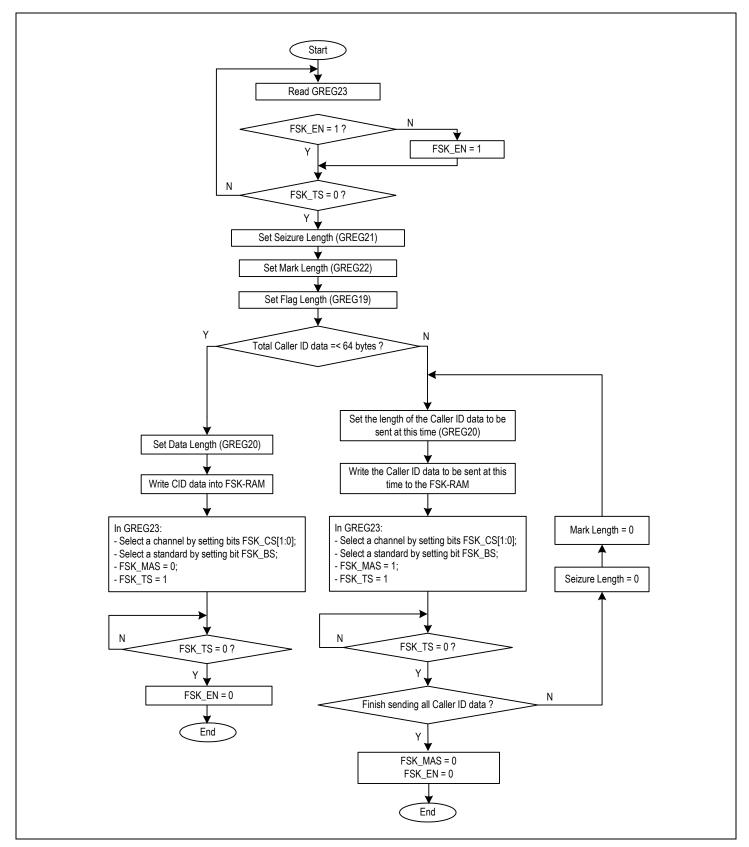

| Figure - 15 | Recommended Programming Flow Chart for FSK Generation       | 32  |

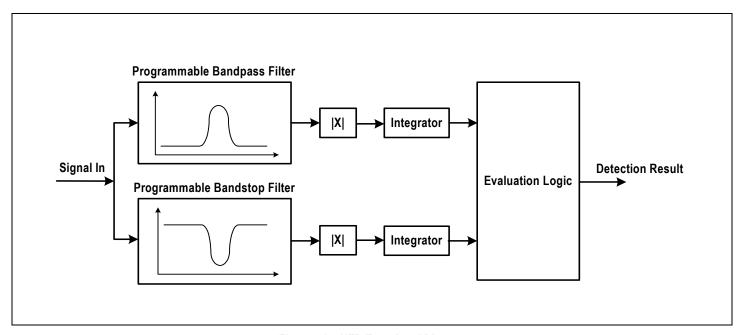

| Figure - 16 | UTD Functional Diagram                                      | 33  |

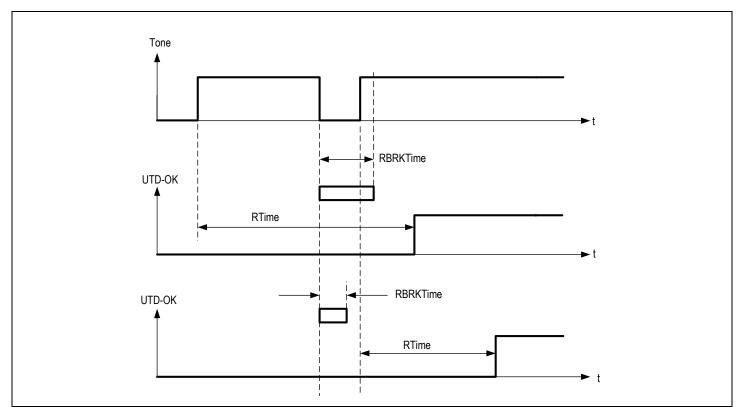

| Figure - 17 | Example of UTD Recognition Timing                           |     |

| Figure - 18 | Example of UTD Tone End Detection Timing                    |     |

| Figure - 19 | Conference Block Diagram                                    | 36  |

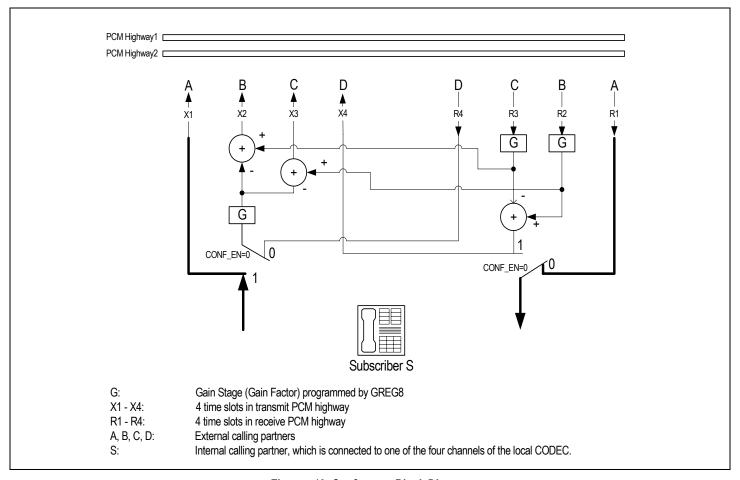

| Figure - 20 | Level Meter Block Diagram                                   |     |

| Figure - 21 | Continuous Measurement Sequence (AC & DC Level Meter)       | 41  |

| Figure - 22 | Single Measurement Sequence (AC & DC Level Meter)           |     |

| Figure - 23 | Example for Resistance Measurement                          | 45  |

| Figure - 24 | Differential Resistance Measurement                         | 45  |

| Figure - 25 | Capacitance Measurement                                     |     |

| Figure - 26 | External Voltage Measurement Principle                      | 47  |

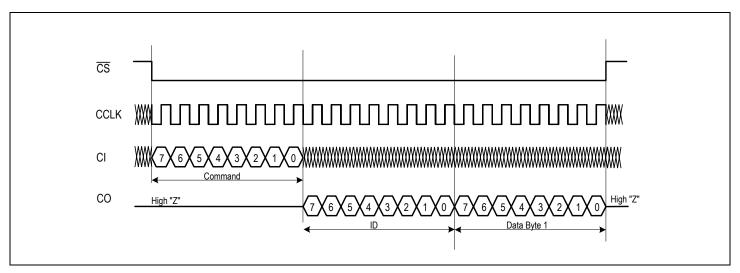

| Figure - 27 | MPI Read Operation Timing                                   | 49  |

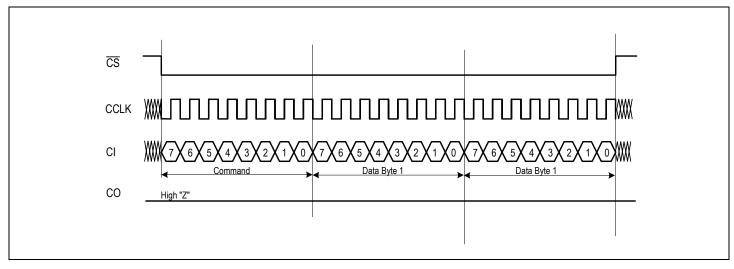

| Figure - 28 | MPI Write Operation Timing                                  |     |

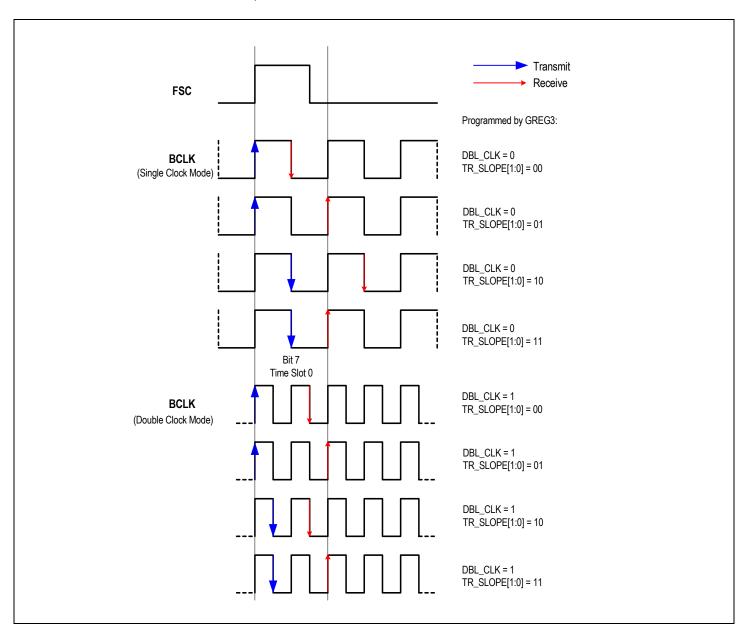

| Figure - 29 | PCM Clock Slope Select Waveform                             |     |

| Figure - 30 | Compressed GCI Frame Structure                              | 52  |

| Figure - 31 | Linear GCI Frame Structure                                  | 53  |

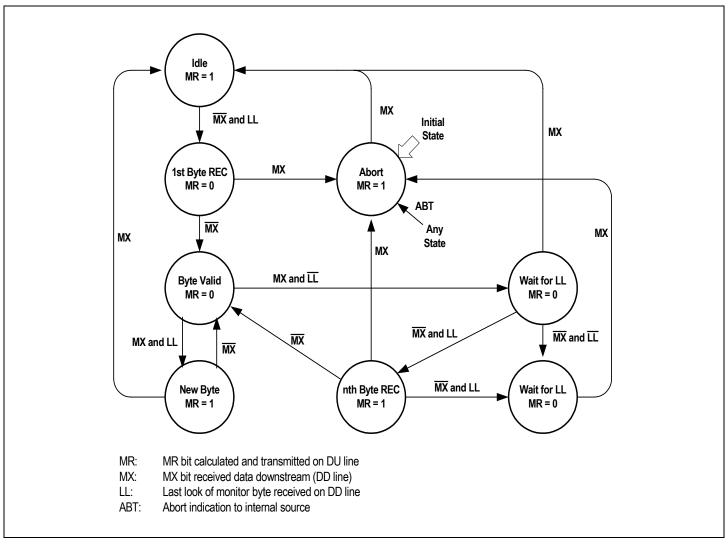

| Figure - 32 | Monitor Channel Operation                                   | 55  |

| Figure - 33 | State Diagram of the Monitor Transmitter                    | 56  |

| Figure - 34 | State Diagram of the Monitor Receiver                       |     |

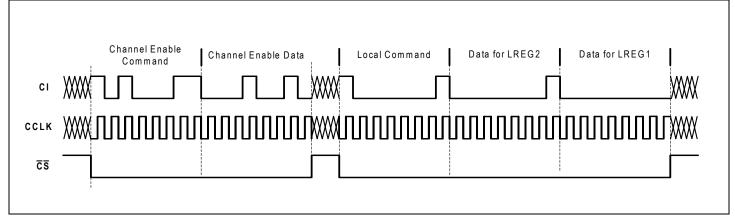

| Figure - 35 | Waveform of Programming Example: Writing to Local Registers |     |

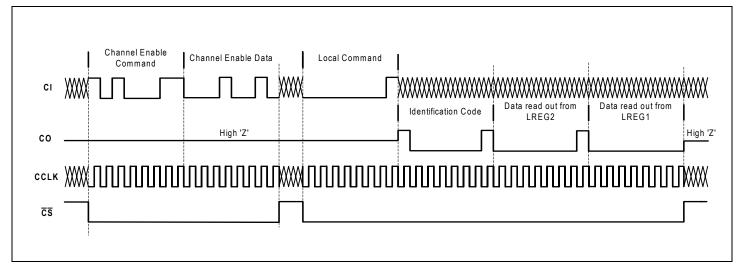

| Figure - 36 | Waveform of Programming Example: Reading Local Registers    |     |

| Figure - 37 | RSLIC Mode Control Signaling                                | 86  |

| Figure - 38 |                                                             | 87  |

| Figure - 39 | RSLIC Internal Test Circuit                                 |     |

| Figure - 40 | IO Debounce Filter                                          |     |

| Figure - 41 | AC/DC Signal Path and Test Loopbacks                        |     |

| Figure - 42 | Clock Timing                                                |     |

| Figure - 43 | MPI Input Timing                                            |     |

| Figure - 44 | MPI Output Timing                                           |     |

| Figure - 45 | PCM Interface Timing (Single Clock Mode)                    |     |

| Figure - 46 | PCM Interface Timing (Double Clock Mode)                    |     |

| Figure - 47 | GCI Interface Timing                                        |     |

| Figure - 48 | Application Circuit for the Internal Ringing Mode           |     |

| Figure - 49 | Application Circuit for the External Ringing Mode           | 104 |

|             |                                                             |     |

# **LIST OF TABLES**

| Table - 1  | Registers and Coe-RAM Locations Used for DC Feeding Configuration | 18  |

|------------|-------------------------------------------------------------------|-----|

| Table - 2  | Registers and Coe-RAM Locations Used for Internal Ringing Mode    | 23  |

| Table - 3  | Registers and Coe-RAM Locations Used for External Ringing Mode    | 25  |

| Table - 4  | Off-hook Detection in Different Modes                             | 26  |

| Table - 5  | Registers and Coe-RAM Locations Used for Off-hook Detection       | 27  |

| Table - 6  | Registers Used for Ground-key Detection                           | 28  |

| Table - 7  | Registers and Coe-RAM Locations Used for Tone Generation          | 29  |

| Table - 8  | FSK Modulation Characteristics                                    | 30  |

| Table - 9  | Registers and FSK-RAM Used for the FSK Generator                  | 31  |

| Table - 10 | Registers and Coe-RAM Locations Used for UTD                      | 35  |

| Table - 11 | Conference Mode                                                   | 37  |

| Table - 12 | Active PCM Channel Configuration Bits                             | 37  |

| Table - 13 | Level Meter Source Selection                                      | 39  |

| Table - 14 | Level Meter Result Value Range                                    | 42  |

| Table - 15 | Shift Factor Selection                                            | 42  |

| Table - 16 | Level Meter Threshold Setting                                     | 42  |

| Table - 17 | Registers and Coe-RAM Locations Used for the Level Meter          | 43  |

| Table - 18 | Registers and Coe-RAM Locations Used for Ramp Generator           | 47  |

| Table - 19 | Time Slot Selection For Compressed GCI                            | 52  |

| Table - 20 | Time Slot Selection For Linear GCI                                | 53  |

| Table - 21 | Local Register Addressing in MPI Mode                             | 59  |

| Table - 22 | Local Register Addressing in GCI Mode                             | 59  |

| Table - 23 | Coefficient RAM Mapping                                           | 61  |

| Table - 24 | Global Registers Mapping                                          | 62  |

| Table - 25 | Local Registers Mapping                                           | 63  |

| Table - 26 | RSLIC Operating Mode                                              | 88  |

| Table - 27 | Interrupt Source and Interrupt Mask                               | 90  |

| Table - 28 | External Components in Application Circuits                       | 104 |

|            |                                                                   |     |

## 1 PIN CONFIGURATIONS

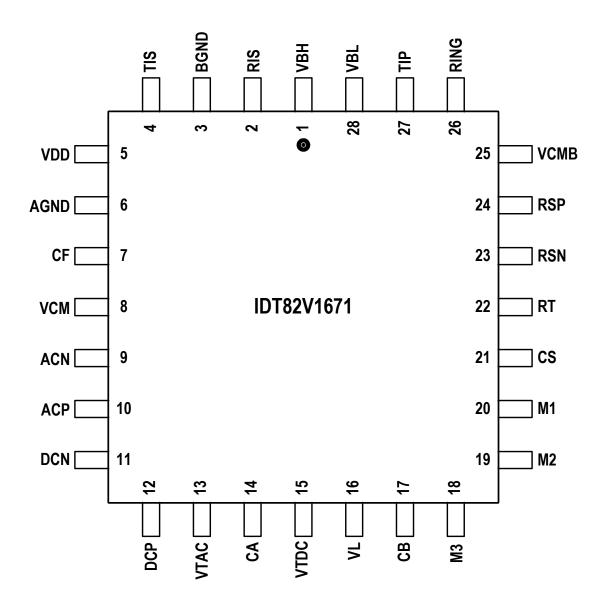

## 1.1 RSLIC PIN CONFIGURATION

## 1.2 CODEC PIN CONFIGURATION

# 2 PIN DESCRIPTIONS

# 2.1 RSLIC PIN DESCRIPTION

| Name Type Pin Number                                                                |                                                        | Pin Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------|--------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>VBH</b> Power 1 Negative battery supply $(-70 \text{ V} \le \text{VBH} \le -52)$ |                                                        | 1          | Negative battery supply $(-70 \text{ V} \le \text{VBH} \le -52 \text{ V})$                                                                                                                                                                                                                                                                                                                                                                                               |

| RIS                                                                                 | <ul> <li>Ring sense, connected for details.</li> </ul> |            | Ring sense, connected to the RING pin through an external resistor Rs. Refer to "8 Application Circuits" on page 103 for details.                                                                                                                                                                                                                                                                                                                                        |

| BGND                                                                                | Power                                                  | 3          | Battery ground. This pin should be externally connected to AGND.                                                                                                                                                                                                                                                                                                                                                                                                         |

| TIS                                                                                 | _                                                      | 4          | Tip sense, connected to the TIP pin through an external resistor RS.                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDD                                                                                 | Power                                                  | 5          | +3.3 V power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AGND                                                                                | Power                                                  | 6          | Analog ground. This pin should be externally connected to BGND.                                                                                                                                                                                                                                                                                                                                                                                                          |

| CF                                                                                  | О                                                      | 7          | Output voltage of VBAT/2 (VBAT represents the selected battery voltage VBH or VBL). An external capacitor is connected between this pin and the ground for filtering.                                                                                                                                                                                                                                                                                                    |

| VCM                                                                                 | I                                                      | 8          | Reference voltage input, typical 1.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ACN                                                                                 | I                                                      | 9          | Differential AC voltage, negative.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ACP                                                                                 | I                                                      | 10         | Differential AC voltage, positive.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DCN                                                                                 | I                                                      | 11         | Differential DC voltage, negative.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DCP                                                                                 | I                                                      | 12         | Differential DC voltage, positive.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VTAC                                                                                | 0                                                      | 13         | Sense transversal AC voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CA                                                                                  |                                                        |            | External capacitor connection. An external capacitor is connected between this pin and the CB pin to separate the DC component from the sense transversal voltage.                                                                                                                                                                                                                                                                                                       |

| VTDC O 15 Sense transversal DC voltage.                                             |                                                        | 15         | Sense transversal DC voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                     |                                                        | 16         | Sense longitudinal voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| СВ                                                                                  | _                                                      | 17         | External capacitor connection. An external capacitor is connected between this pin and the CA pin to separate the DC component from the sense transversal voltage.                                                                                                                                                                                                                                                                                                       |

| М3                                                                                  | I/O                                                    | 18         | Mode control input 3 or temperature information output.  The logic level of the CS pin determines the direction of the M3 pin. See the description of the CS pin for details.                                                                                                                                                                                                                                                                                            |

| M2                                                                                  | ı                                                      | 19         | Mode control input 2. This is a binary logic pin, together with M1 and M3, controlling the operating mode of the RSLIC.                                                                                                                                                                                                                                                                                                                                                  |

| M1                                                                                  | 1                                                      | 20         | Mode control input 1. This is a binary logic pin, together with M2 and M3, controlling the operating mode of the RSLIC.                                                                                                                                                                                                                                                                                                                                                  |

| cs                                                                                  | ı                                                      | 21         | Chip select input. It is a ternary logic pin. When the CS pin is logic 0 (0 V< CS < 0.8 V), the RSLIC receives the mode control data from the CODEC through the M1 to M3 pins. When the CS pin is logic 1 (2.2 V< CS < 3.3 V), the RSLIC sends the temperature information of itself to the CODEC through the M3 pin. When the CS pin is 1.5 V (with $\pm 0.5$ V tolerance), the RSLIC neither receives the data from the CODEC nor sends temperature information to it. |

| RT                                                                                  | 0                                                      | 22         | Ring trip operational amplifier output.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RSN                                                                                 | I                                                      | 23         | Negative ring trip operational amplifier input.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RSP                                                                                 | I                                                      | 24         | Positive ring trip operational amplifier input.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VCMB                                                                                | 0                                                      | 25         | VCM buffer output, 1.5 V, used for external ringing mode.                                                                                                                                                                                                                                                                                                                                                                                                                |

| RING                                                                                | I/O                                                    | 26         | Subscriber loop connection Ring.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TIP                                                                                 | I/O                                                    | 27         | Subscriber loop connection Tip.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VBL                                                                                 | Power                                                  | 28         | Negative battery supply ( $-52 \text{ V} \le \text{VBL} \le -20 \text{ V}$ ).                                                                                                                                                                                                                                                                                                                                                                                            |

## 2.2 CODEC PIN DESCRIPTION

| Name  | Туре | Pin Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-------|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VTDC1 | I    | 33         | DC component of the transversal voltage (Channel 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| VTAC1 | I    | 34         | AC component of transversal voltage (Channel 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| VL1   | I    | 32         | Longitudinal voltage (Channel 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| RTIN1 | I    | 31         | Analog voltage that can be used for external ring trip detection (channel 1).                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| ACP1  | 0    | 40         | Differential AC voltage, positive (Channel 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| ACN1  | 0    | 41         | Differential AC voltage, negative (Channel 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| DCP1  | 0    | 36         | Differential DC voltage, positive (Channel 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| DCN1  | 0    | 39         | Differential DC voltage, negative (Channel 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CS1   | 0    | 52         | Ternary logic output 1, controlling the operating mode of the RSLIC1 (Channel 1).  When the CS1 pin is logic 0 (0 V< CS1 < 0.8 V), the CODEC sends mode control data to the RSLIC1 through the M1 to M3 pins.  When the CS1 pin is logic 1 (2.2 V< CS1 < 3.3 V), the CODEC receives the temperature information of the RSLIC1 through the M3 pin.  When the CS1 pin is 1.5 V (with ±0.5 V tolerance), no mode control data or temperature information is transferred between the CODEC and the RSLIC1. |  |

| IO1_1 | I/O  | 50         | Programmable IO pin with relay-driving capability (Channel 1). In external ringing mode, the IO1_1 pin can be used to control the external ring relay.                                                                                                                                                                                                                                                                                                                                                 |  |

| IO2_1 | I/O  | 49         | Programmable IO pin with relay-driving capability (Channel 1).                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| IO3_1 | I/O  | 48         | Programmable IO pin with analog input functionality (Channel 1).                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| IO4_1 | I/O  | 47         | Programmable IO pin with analog input functionality (Channel 1).                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| CA1_1 | I/O  | 37         | External capacitor connection. An external capacitor is connected between this pin and the DCP1 pin for filtering (Channel 1).                                                                                                                                                                                                                                                                                                                                                                         |  |

| CA2_1 | I/O  | 38         | External capacitor connection. An external capacitor is connected between this pin and the DCN1 pin for filtering (Channel 1).                                                                                                                                                                                                                                                                                                                                                                         |  |

| VTDC2 | I    | 21         | DC component of the transversal voltage (Channel 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| VTAC2 | I    | 22         | AC component of the transversal voltage (Channel 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| VL2   | I    | 20         | Longitudinal voltage (Channel 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| RTIN2 | I    | 19         | Analog voltage that can be used for external ring trip detection (channel 2).                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| ACP2  | 0    | 28         | Differential AC voltage, positive (Channel 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| ACN2  | 0    | 29         | Differential AC voltage, negative (Channel 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| DCP2  | 0    | 24         | Differential DC voltage, positive (Channel 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| DCN2  | 0    | 27         | Differential DC voltage, negative (Channel 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CS2   | 0    | 51         | Ternary logic output 2, controlling the operating mode of the RSLIC2 (Channel 2). When the CS2 pin is logic 0 (0 V< CS2 < 0.8 V), the CODEC sends mode control data to the RSLIC2 through the M1 to M3 pins. When the CS2 pin is logic 1 (2.2 V< CS2 < 3.3 V), the CODEC receives the temperature information of the RSLIC2 through the M3 pin. When the CS2 pin is 1.5 V (with ±0.5 V tolerance), no mode control data or temperature information is transferred between the CODEC and the RSLIC2.    |  |

| IO1_2 | I/O  | 45         | Programmable IO pin with relay-driving capability (Channel 2). In external ringing mode, the IO1_2 pin can be used to control the external ring relay.                                                                                                                                                                                                                                                                                                                                                 |  |

| IO2_2 | I/O  | 44         | Programmable IO pin with relay-driving capability (Channel 2).                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| IO3_2 | I/O  | 43         | Programmable IO pin with analog input functionality (Channel 2).                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| IO4_2 | I/O  | 42         | Programmable IO pin with analog input functionality (Channel 2).                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| CA1_2 | I/O  | 25         | External capacitor connection. An external capacitor is connected between this pin and the DCP2 pin for filtering (Channel 2).                                                                                                                                                                                                                                                                                                                                                                         |  |

| CA2_2 | I/O  | 26         | External capacitor connection. An external capacitor is connected between this pin and the DCN2 pin for filtering (Channel 2).                                                                                                                                                                                                                                                                                                                                                                         |  |

| Name  | Туре | Pin Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-------|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VTDC3 | I    | 5          | OC component of the transversal voltage (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| VTAC3 | Ι    | 6          | AC component of the transversal voltage (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| VL3   | Ι    | 4          | Longitudinal voltage (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| RTIN3 | I    | 3          | Analog voltage that can be used for external ring trip (channel 3).                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| ACP3  | 0    | 12         | Differential AC voltage, positive (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| ACN3  | 0    | 13         | Differential AC voltage, negative (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| DCP3  | 0    | 8          | Differential DC voltage, positive (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| DCN3  | 0    | 11         | Differential DC voltage, negative (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| CS3   | 0    | 80         | Ternary logic output 3, controlling the operating mode of the RSLIC3 (Channel 3). When the CS3 pin is logic 0 (0 V< CS3 < 0.8 V), the CODEC sends mode control data to the RSLIC3 through the M1 to M3 pins. When the CS3 pin is logic 1 (2.2 V< CS3 < 3.3 V), the CODEC receives the temperature information of the RSLIC3 through the M3 pin. When the CS3 pin is 1.5 V (with $\pm 0.5$ V tolerance), no mode control data or temperature information is transferred between the CODEC and the RSLIC3.          |  |  |

| IO1_3 | I/O  | 86         | Programmable IO pin with relay-driving capability (Channel 3). In external ringing mode, the IO1_3 pin can be used to control the external ring relay.                                                                                                                                                                                                                                                                                                                                                            |  |  |

| IO2_3 | I/O  | 87         | Programmable IO pin with relay-driving capability (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| IO3_3 | I/O  | 88         | Programmable IO pin with analog input functionality (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| IO4_3 | I/O  | 89         | Programmable IO pin with analog input functionality (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| CA1_3 | I/O  | 9          | External capacitor connection. An external capacitor is connected between this pin and the DCP3 pin for filtering (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| CA2_3 | I/O  | 10         | External capacitor connection. An external capacitor is connected between this pin and the DCN3 pin for filtering (Channel 3).                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| VTDC4 | _    | 93         | DC component of the transversal voltage (Channel 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| VTAC4 | Ι    | 94         | AC component of the transversal voltage (Channel 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| VL4   | _    | 92         | ongitudinal voltage (Channel 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RTIN4 | Ι    | 91         | Analog voltage that can be used for external ring trip (Channel 4).                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| ACP4  | 0    | 100        | Differential AC voltage, positive (Channel 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

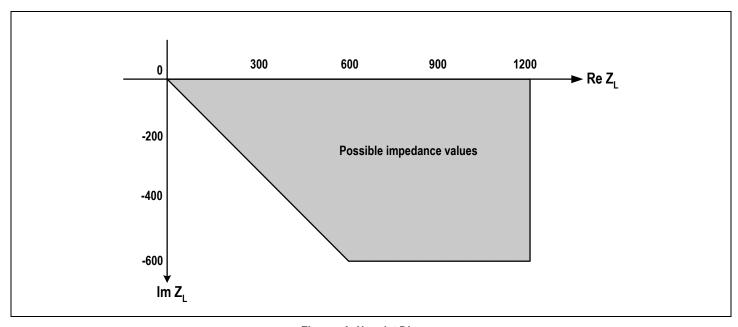

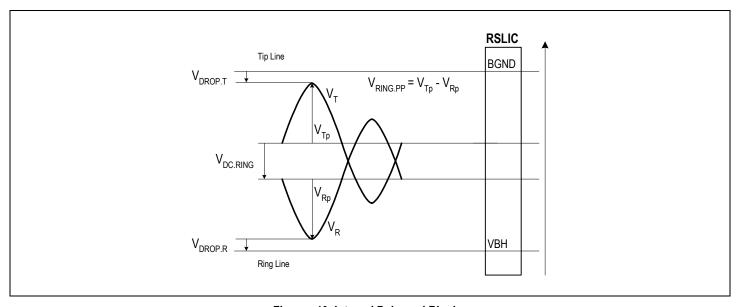

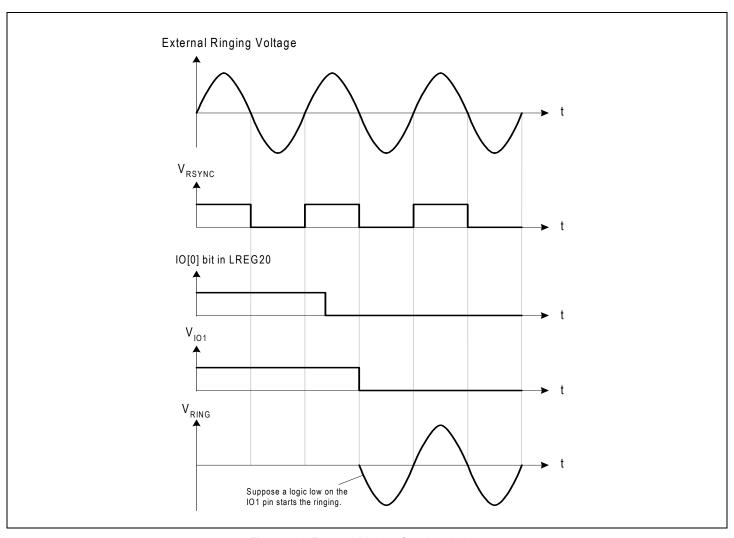

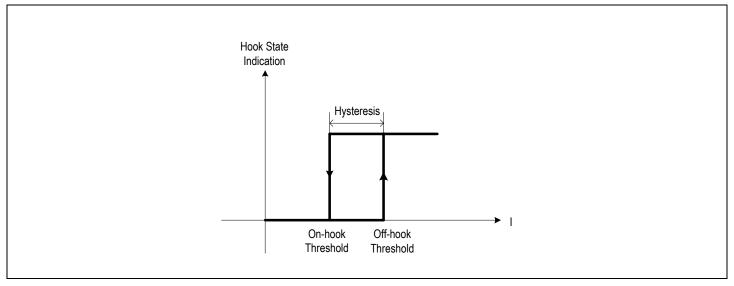

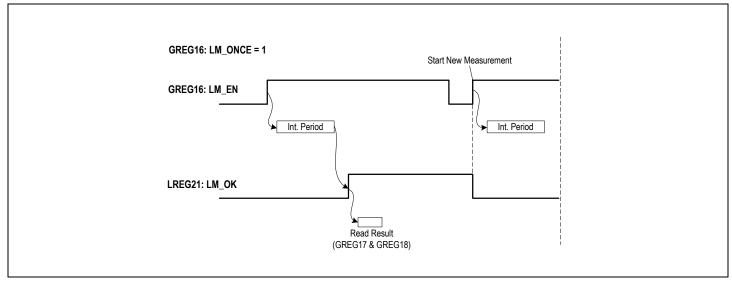

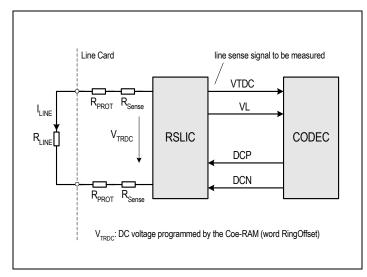

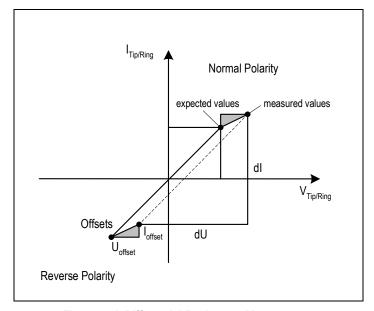

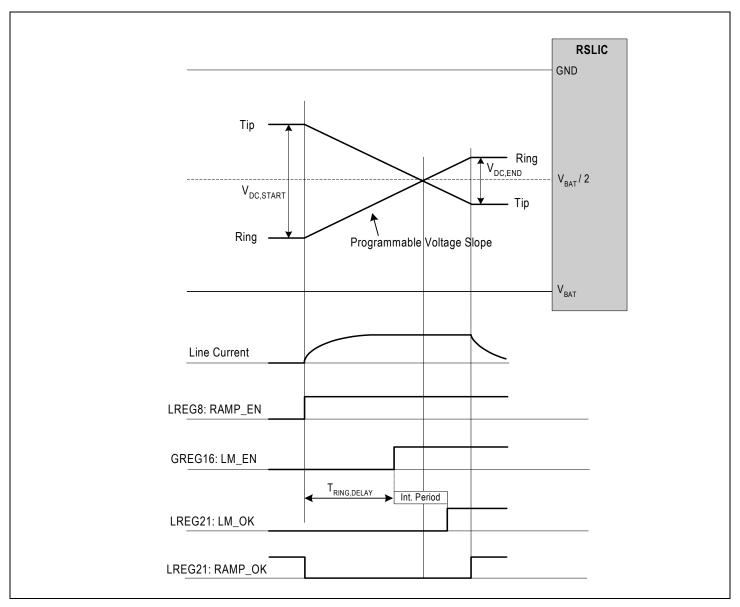

| ACN4  | 0    | 1          | Differential AC voltage, negative (Channel 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |