# Linear Single Cell Li-Ion Battery Charger IC for Portable Applications

## **General Description**

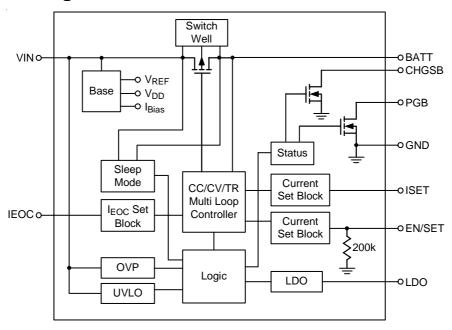

The RT9524 is a fully integrated single cell Li-ion battery charger IC ideal for portable applications. The RT9524 optimizes the charging task by using a control algorithm including pre-charge mode, fast charge mode and constant voltage mode. the input voltage range of the VIN pin can be as high as 28V. When the input voltage exceeds the OVP threshold, it will turn off the charging MOSFET to avoid overheating of the chip.

In RT9524, the maximum charging current can be programmed with an external resistor. For USB application, the user can set the current to 100mA/500mA through the EN/SET pin. For the factory mode, the RT9524 can allow 4.2V/2.3A power pass through to support system operation. It also provides a 50mA LDO to support the power of peripheral circuit. The internal thermal feedback circuit regulates the die temperature to optimize the charge rate for all ambient temperatures. The RT9524 provides protection functions such as under voltage protection, over voltage protection for VIN supply and thermal protection for battery temperature.

The RT9524 is available in a WDFN-10L 3x2 package to achieve optimized solution for PCB space and thermal considerations.

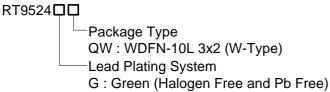

# **Ordering Information**

#### Note:

Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

## **Features**

- 28V Maximum Rating for DC Adapter

- Internal Integrated Power MOSFETs

- Support 4.2V/2.3A Factory Mode

- 50mA Low Dropout Voltage Regulator

- Status Pin Indicator

- Programmed Charging Current

- Under Voltage Lockout

- Over Voltage Protection

- Thermal Feedback Optimized Charge Rate

- RoHS Compliant and Halogen Free

# **Applications**

- Cellular Phones

- Digital Cameras

- PDAs and Smart Phones

- Protable Instruments

# **Pin Configurations**

(TOP VIEW)

WDFN-10L 3x2

# **Marking Information**

A0 : Product Code

W : Date Code

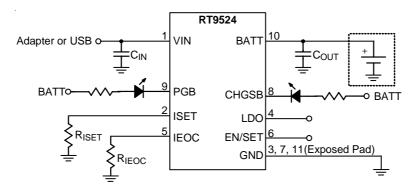

# **Typical Application Circuit**

# **Functional Pin Description**

| Pin No.                   | Pin Name | Pin Function                                                                                                      |

|---------------------------|----------|-------------------------------------------------------------------------------------------------------------------|

| 1                         | VIN      | The Input Power Source.                                                                                           |

| 2                         | ISET     | Charging Current Setting.                                                                                         |

| 3, 7,<br>11 (Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.       |

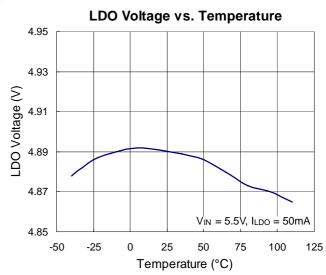

| 4                         | LDO      | LDO Output (4.9V). This pin provides 50mA output current.                                                         |

| 5                         | IEOC     | End-of-Charge Current Setting. The $I_{\rm EOC}$ is from 5% to 50% Ichg-fast which is programmed by the ISET pin. |

| 6                         | EN/SET   | Enable and Operation Mode Setting.                                                                                |

| 8                         | CHGSB    | Indicator Output for Charging Status.                                                                             |

| 9                         | PGB      | Indicator Output for Power Status.                                                                                |

| 10                        | BATT     | Battery Charge Current Output.                                                                                    |

# **Function Block Diagram**

# Absolute Maximum Ratings (Note 1)

| • Supply Input Voltage, V <sub>IN</sub>                                     | - −0.3V to 28V   |

|-----------------------------------------------------------------------------|------------------|

| • Other Pins                                                                | 0.3V to 6V       |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                  |

| WDFN-10L 3x2                                                                | - 1.111W         |

| Package Thermal Resistance (Note 2)                                         |                  |

| WDFN-10L 3x2, $\theta_{JA}$                                                 | - 90°C/W         |

| WDFN-10L 3x2, $\theta_{JC}$                                                 | - 15°C/W         |

| • Lead Temperature (Soldering, 10 sec.)                                     | - 260°C          |

| • Junction Temperature                                                      | - 150°C          |

| Storage Temperature Range                                                   | - −65°C to 150°C |

| Recommended Operating Conditions (Note 3)                                   |                  |

| Supply Input Voltage, V <sub>IN</sub>                                       | - 4.3V to 5.5V   |

| Junction Temperature Range                                                  | 40°C to 125°C    |

| Ambient Temperature Range                                                   | - −20°C to 85°C  |

# **Electrical Characteristics**

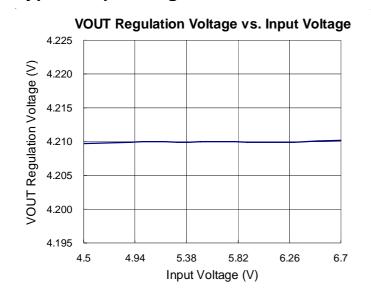

( $V_{IN}$  = 5V,  $V_{BATT}$  = 4V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter                               | Symbol              | Test Conditions                                        | Min   | Тур                                | Max   | Unit |

|-----------------------------------------|---------------------|--------------------------------------------------------|-------|------------------------------------|-------|------|

| VIN POR Rising Threshold Voltage        | V <sub>POR</sub>    |                                                        | 3.15  | 3.3                                | 3.45  | V    |

| VIN POR Threshold Voltage Hysteresis    |                     |                                                        |       | 200                                | 300   | mV   |

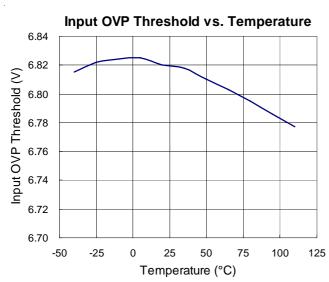

| VIN OVP Threshold Voltage               | V <sub>OVP</sub>    |                                                        | 6.7   | 6.9                                | 7.1   | V    |

| VIN OVP Threshold Voltage<br>Hysteresis |                     |                                                        |       | 200                                | 300   | mV   |

| VIN – VOUT VOS Rising                   |                     |                                                        |       | 75                                 | 150   | mV   |

| VIN – VOUT VOS Falling                  |                     |                                                        | 18    | 32                                 |       | mV   |

| VIN Standby Current                     |                     | V <sub>BATT</sub> = 4.5V, EN/SET = High                |       | 250                                | 300   | μΑ   |

| VIN Supply Current                      |                     | V <sub>BATT</sub> = 4.5V, EN/SET = Low                 |       | 1                                  | 2     | mA   |

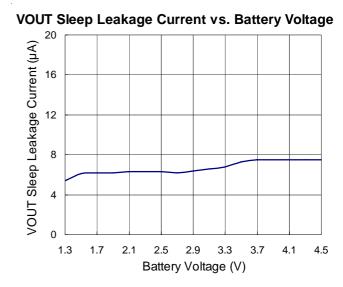

| VOUT Sleep Leakage<br>Current           |                     |                                                        |       | 1                                  | 10    | μΑ   |

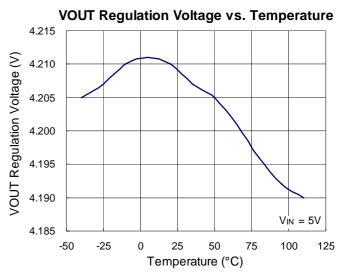

| VOUT Regulation                         |                     | 0°C to 85°C, I <sub>LOAD</sub> = 0mA                   | 4.158 | 4.2                                | 4.242 | V    |

| Thermal Regulation                      |                     |                                                        |       | 125                                |       | °C   |

| OTP                                     |                     |                                                        |       | 155                                |       | °C   |

| OTP Hysteresis                          |                     |                                                        |       | 20                                 |       | °C   |

| PGB/CHGSB Sink Current                  |                     |                                                        | 20    |                                    |       | mA   |

| Pre-Charge Threshold                    |                     | V <sub>OUT</sub> Rising                                | 2.4   | 2.5                                | 2.6   | V    |

| Fast-Charge to Pre-Charge Deglitch Time |                     |                                                        |       | 25                                 |       | ms   |

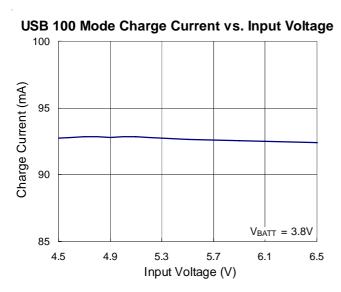

|                                         | I <sub>PRECHG</sub> | USB100 Mode                                            | 90    | 95                                 | 100   | mA   |

| Pre-Charge Current                      |                     | USB500 Mode or ISET Mode, ratio of fast-charge current | 15    | 20                                 | 25    | %    |

| End of Charge Current (EOC)             |                     |                                                        |       | R <sub>EOC</sub> /K <sub>EOC</sub> |       | %    |

To be continued

| Parameter                           |                           | Symbol              | Test Conditions                       | Min   | Тур | Max   | Unit |

|-------------------------------------|---------------------------|---------------------|---------------------------------------|-------|-----|-------|------|

| IEOC Setting Current                |                           | I <sub>EOC</sub>    |                                       | 70    | 75  | 80    | μА   |

| IEOC Sett                           | ting K <sub>EOC</sub>     |                     |                                       | 180   | 200 | 220   | Ω/%  |

| VIN Powe                            | r FET R <sub>DS(ON)</sub> |                     | I <sub>OUT</sub> = 1A                 |       | 280 | 512   | mV   |

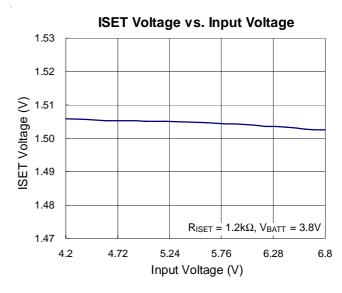

| ISET Set '                          | Voltage                   | VISET               |                                       |       | 1.5 |       | V    |

| ISET Shor                           | rt Protect Threshold      |                     |                                       | 320   |     | 460   | Ω    |

| ISET Shor                           | rt Protect Deglitch       |                     |                                       |       | 1.5 |       | ms   |

| ISET Shor                           | rt Protect Maximum        |                     |                                       |       | 2   |       | Α    |

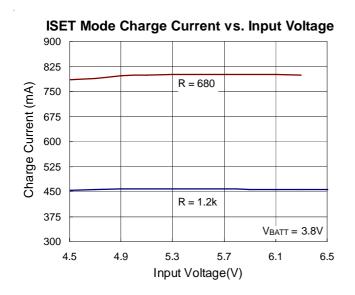

|                                     |                           |                     | As ISET Mode, R <sub>ISET</sub> = 530 | 0.9   | 1   | 1.1   | Α    |

| VIN Charg                           | ge Current                | I <sub>CHRG</sub>   | As USB100 Mode                        | 90    | 95  | 100   | mA   |

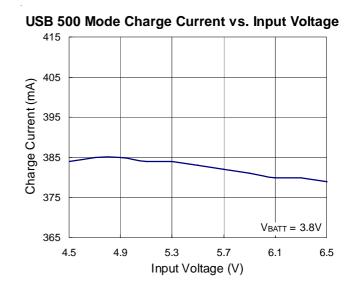

|                                     |                           |                     | As USB500 Mode                        | 380   | 395 | 415   | mA   |

| EN/SET P                            | Pull Low Resistor         |                     |                                       |       | 200 |       | kΩ   |

| EN/SET                              | Logic-High                | V <sub>IH</sub>     |                                       | 1.4   |     |       | V    |

| Voltage                             | Logic-Low                 | V <sub>IL</sub>     |                                       |       |     | 0.4   | V    |

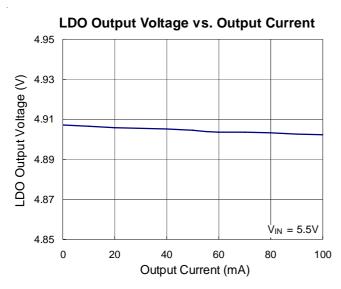

| LDO On-F                            | Resistance                | R <sub>DS(ON)</sub> |                                       |       | 3   | 6     | Ω    |

| LDO Outp                            | LDO Output Voltage        |                     |                                       | 4.75  | 4.9 | 5.05  | V    |

| LDO Maximum Output<br>Current       |                           |                     |                                       | 60    | 120 | 180   | mA   |

| Factory Mode V <sub>OUT</sub>       |                           |                     |                                       | 4.116 | 4.2 | 4.284 | V    |

| Factory Mode Maximum Output Current |                           |                     |                                       | 2.3   |     |       | Α    |

| EN/SET Off Time                     |                           |                     | Timer to disable chip                 | 1.5   |     |       | ms   |

| EN/SET Lock Time                    |                           | _                   | Timer to lock pulse count             | 1.5   |     |       | ms   |

| Logic-High Duration                 |                           |                     |                                       | 100   |     | 700   | μS   |

| Logic-Low Duration                  |                           |                     |                                       | 100   |     | 700   | μS   |

**Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board of JEDEC 51-7 thermal measurement standard. The measurement case position of  $\theta_{JC}$  is on the exposed pad of the package.

Note 3. The device is not guaranteed to function outside its operating conditions.

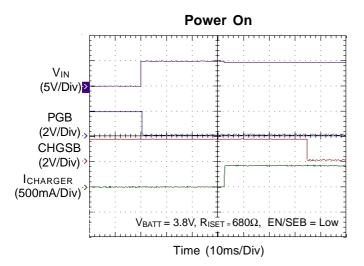

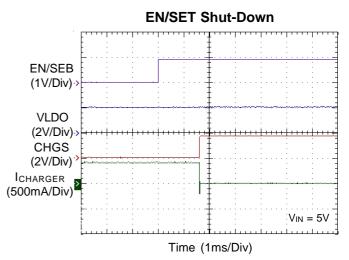

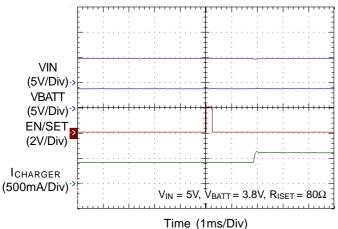

# **Typical Operating Characteristics**

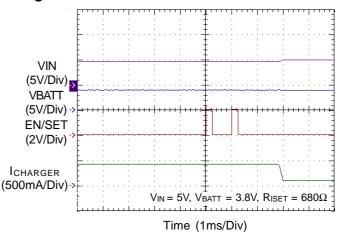

## Charger Current--USB500 mode to ISET mode

#### Charger Current--USB500 mode to USB100 mode

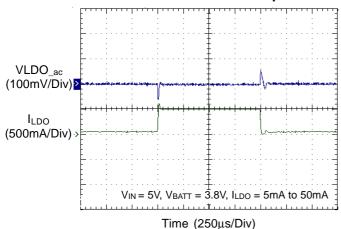

#### **LDO Load Transient Response**

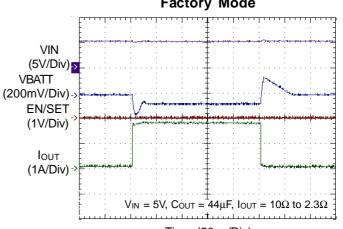

## **Factory Mode**

Time (50µs/Div)

DS9524-01 April 2011 www.richtek.com

7

# **Application Information**

#### **Description**

The RT9524 is a fully integrated low cost single-cell Lilon battery charger IC with a constant current mode (CC mode) or a constant voltage mode (CV mode). The charge current is programmable to USB100, USB500 or ISET mode and the CV mode voltage is fixed at 4.2V. The precharge threshold is fixed at 2.5V. If the battery voltage is below the pre-charge threshold, the RT9524 charges the battery with a trickle current until the battery voltage rises above the pre-charge threshold. The RT9524 is capable of being powered up from AC adapter and USB (Universal Serial Bus) port inputs. Moreover, the RT9524 include a linear regulator (LDO 4.9V, 50mA) for supplying low power external circuitry.

#### **ACIN Over Voltage Protection**

The input voltage is monitored by the internal comparator and the input over voltage protection threshold is set to 6.9V. However, input voltage over 28V will still cause damage to the RT9524. When the input voltage exceeds the threshold, the comparator outputs a logic signal to turn off the power P-MOSFET to prevent the high input voltage from damaging the electronics in the handheld system. When the input over voltage condition is removed, the comparator re-enables the output by running through the soft-start.

#### **Charger Enable and mode Setting**

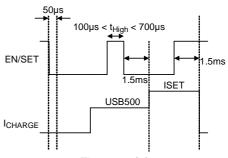

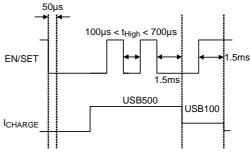

EN/SET is used to enable or disable the charger as well as to select the charge current limit. Drive the EN pin to low or leave it floating to enable the charger. The EN/SET pin has a 200kΩ internal pull down resistor. So, when left floating, the input is equivalent to logic low. Drive this pin to high to disable the charger. After the EN/SET pin pulls low for 50μs, the RT9524 enters the USB500 mode and wait for the setting current signal. EN/SET can be used to program the charge current during this cycle. The RT9524 will change its charge current by sending different pulse to EN/SET pin. If no signal is sent to EN/SET, the RT9524 will remain in USB500 mode. A correct period of time for high pulse is between 100μs and 700μs and the period of pulse to pulse must be between 100μs and 700μs to be properly read. Once EN/SET is held low for 1.5ms,

the number of pulses is locked and sent to the control logic and then the mode changes. The RT9524 needs to be restarted to reset the charge current. Once the EN/ SET input is held high for more than 1.5ms, the RT9524 is disabled.

Table 1. Pulse Counting Map for EN/SET Interface

| Pulses | Charge Condition | MODE Control         |

|--------|------------------|----------------------|

| 0      | USB500 Mode      | Charge Current Limit |

| 1      | ISET Mode        | Charge Current Limit |

| 2      | USB100 Mode      | Charge Current Limit |

| 3      | Factory Mode     | Enabled              |

| ≥4     | USB100 Mode      | Charge Current Limit |

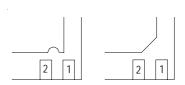

Figure .1 (a)

Figure .1 (b)

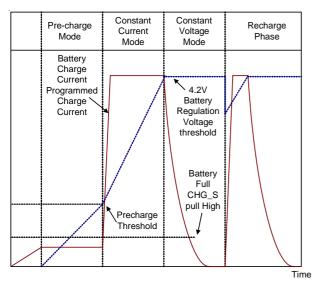

#### **Battery Charge Profile**

The RT9524 charges a Li-Ion battery with a constant current (CC) or a constant voltage (CV).

The constant current is decided by the operation mode of USB100, USB500 or ISET mode. The constant current is set with the external resistor R<sub>ISET</sub> and the constant voltage is fixed at 4.2V. If the battery voltage is below the Pre-Charge Threshold, the RT9524 charges the battery with a trickle current until the battery voltage rises above the trickle charge threshold. When the battery voltage reaches 4.2V, the charger enters CV mode and regulates the battery voltage at 4.2V to fully charge the battery without the risk of over charging

www.richtek.com DS9524-01 April 2011

Figure 2

#### **Battery Pre-Charge Current**

During a charge cycle, if the battery voltage is below the pre-charge threshold, the RT9524 enters the pre-charge mode. This feature revives deeply discharged cells and protects battery. Under USB100 Mode, the pre-charge current is internally set to 95mA. When the RT9524 is under USB500 and ISET Mode, the pre-charge current is 20% of fast-charge current set by external resistor R<sub>ISET</sub>.

#### **Battery Fast-Charge Current**

#### **ISET Mode**

The RT9524 offers ISET pin to program the charge current. The resistor  $R_{\mathsf{ISET}}$  is connected to ISET and GND. The parameter  $K_{\mathsf{ISET}}$  is specified in the specification table.

#### USB500 and USB100 Mode

The fast-charge current is 95mA in USB100 mode and 395mA in USB500 mode. Note that if the fast-charge current set by external resistor is smaller than that in USB500 mode (395mA), the RT9524 charges the battery in ISET mode.

#### **Battery Voltage Regulation (CV Mode)**

The battery voltage regulation feedback is through the BATT pin. The RT9524 monitors the battery voltage between BATT and GND pins. When the battery voltage closes in on the battery regulation voltage threshold, the voltage regulation phase begins and the charging current begins to taper down. When the charging current falls below the programmed end-of-charge current threshold, the CHGSB pin goes high to indicate the termination of charge cycle.

The end-of-charge current threshold is set by the IEOC pin. The resistor  $R_{EOC}$  is connected to IEOC and GND. The parameters  $K_{EOC}$  and IEOC are specified in the specification table.

$$I_{EOC}(\%) = \frac{R_{EOC}}{K_{EOC}}$$

;  $K_{EOC} = 200$

The current threshold of IEOC (%) is defined as the percentage of fast-charge current set by  $R_{\rm ISET}$ . After the CHGSB pin is pulled high, the RT9524 still monitors the battery voltage. Charge current is resumed when the battery voltage goes to lower than the battery regulation voltage threshold.

#### **Factory Mode**

The RT9524 provides factory mode for supplies up to 2.3A for powering external loads with no battery installed and BATT is regulated to 4.2V. The factory mode allows the user to supply system power with no battery connected. In factory mode, thermal regulation is disabled but thermal protection (155°C) is still active. When using currents greater than 1.5A in factory mode, the user must limit the duty cycle at the maximum current to 20% with a maximum period of 10ms.

#### LDO

The RT9524 integrates one low dropout linear regulator (LDO) that supplies up to 50mA. The LDO is active whenever the input voltage is between POR threshold and

OVP threshold. It is not affected by the EN/SET input. Note that the LDO current is independence and not monitored by the charge current limit.

#### **Charge Status Outputs (CHGSB and PGB)**

The open-drain CHGSB and PGB outputs indicate various charger operations as shown in the following table. These status pins can be used to drive LEDs or communicate to the host processor. Note that ON indicates the open-drain transistor is turned on and LED is bright.

Table 2

| Condition                    | CHGSB | PGB |

|------------------------------|-------|-----|

| Input OVP                    | OFF   | OFF |

| Input UVLO                   | OFF   | OFF |

| Charge (CC Mode and CV Mode) | ON    | ON  |

| Charge Done (IFULL)          | OFF   | ON  |

|                                                 | PGB Deglitches Time |                  |  |  |

|-------------------------------------------------|---------------------|------------------|--|--|

| Condition                                       | EN/SET is<br>High   | EN/SET is<br>Low |  |  |

| Entering OVP<br>(V <sub>IN</sub> = 5.5V→10V)    | 0                   | 100μs            |  |  |

| Leaving OVP<br>(V <sub>IN</sub> = 10V→5.5V)     | 500μs               | 450μs            |  |  |

| Entering SLEEP<br>(V <sub>IN</sub> = 5.5V→3.6V) | 0                   | 32ms             |  |  |

| Leaving SLEEP (V <sub>IN</sub> = 3.6V→5.5V)     | 500μs               | 500μs            |  |  |

| Entering UVLO<br>(V <sub>IN</sub> = 5.5V→2.5V)  | 0                   | 0                |  |  |

| Leaving UVLO<br>(V <sub>IN</sub> = 2.5V→5.5V)   | 230μs               | 230μs            |  |  |

#### Sleep Mode

The RT9524 enters sleep mode if the power is removed from the input. This feature prevents draining the battery during the absence of input supply.

#### **Temperature Regulation and Thermal Protection**

In order to maximize charge rate, the RT9524 features a junction temperature regulation loop. If the power dissipation of the IC results in a junction temperature greater than the thermal regulation threshold (125°C), the RT9524 limits the charge current in order to maintain a junction temperature around the thermal regulation threshold (125°C). The RT9524 monitors the junction

temperature,  $T_J$ , of the die and disconnects the battery from the input if  $T_J$  exceeds 125°C. This operation continues until junction temperature falls below thermal regulation threshold (125°C) by the hysteresis level. This feature prevents maximum power dissipation from exceeding typical design conditions.

#### **Selecting the Input and Output Capacitors**

In most applications, all that is needed is a high-frequency decoupling capacitor on the input. A  $1\mu F$  ceramic capacitor, placed in close proximity to input to GND, works well. In some applications depending on the power supply characteristics and cable length, it may be necessary to add an additional  $10\mu F$  ceramic capacitor to the input. The RT9524 requires a small output capacitor for loop stability. A typical  $1\mu F$  ceramic capacitor placed between the BATT pin and GND is sufficient.

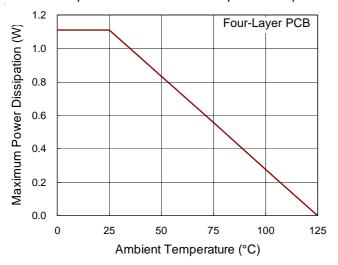

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum operation junction temperature. The maximum power dissipation depends on thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum operation junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating conditions specification of RT9524, the maximum junction temperature is 125°C and  $T_A$  is the maximum ambient temperature. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WDFN-10L 3x2 packages, the thermal resistance,  $\theta_{JA}$ , is 90°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated by the following formula :

$$P_{D(MAX)}$$

= (125°C  $-$  25°C) / (90°C/W) = 1.111W for WDFN-10L3x2 package

The maximum power dissipation depends on operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . For RT9524 package, the derating curve

www.richtek.com DS9524-01 April 2011

in Figure 4 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 4. Derating Curve for RT9524 Package

#### **Layout Consideration**

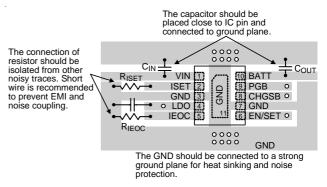

The RT9524 is a fully integrated low cost single-cell Lilon battery charger IC ideal for portable applications. Careful PCB layout is necessary. For best performance, place all peripheral components as close to the IC as possible. A short connection is highly recommended. The following guidelines should be strictly followed when designing a PCB layout for the RT9524.

- Input capacitor should be placed close to the IC and connected to ground plane. The trace of input in the PCB should be placed far away from the sensitive devices or shielded by the ground.

- ➤ The GND should be connected to a strong ground plane for heat sinking and noise protection.

- The connection of R<sub>ISET</sub> and R<sub>IEOC</sub> should be isolated from other noisy traces. The short wire is recommended to prevent EMI and noise coupling.

- Output capacitor should be placed close to the IC and connected to ground plane to reduce noise coupling.

Figure 5. PCB Layout Guide

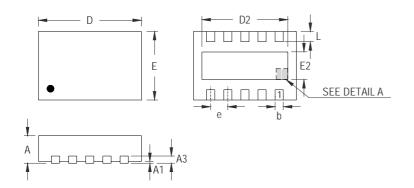

## **Outline Dimension**

**DETAIL A**

Pin #1 ID and Tie Bar Mark Options

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

|        | Min          | Max           | Min                  | Max   |  |

| А      | 0.700        | 0.800         | 0.028                | 0.031 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002 |  |

| A3     | 0.175        | 0.250         | 0.007                | 0.010 |  |

| b      | 0.180        | 0.300         | 0.007                | 0.012 |  |

| D      | 2.900        | 3.100         | 0.114                | 0.122 |  |

| D2     | 2.450        | 2.550         | 0.096                | 0.100 |  |

| Е      | 1.900        | 2.100         | 0.075                | 0.083 |  |

| E2     | 0.750        | 0.850         | 0.030                | 0.033 |  |

| е      | 0.500        |               | 0.0                  | )20   |  |

| L      | 0.250        | 0.350         | 0.010                | 0.014 |  |

W-Type 10L DFN 3x2 Package

## **Richtek Technology Corporation**

Headquarter

5F, No. 20, Taiyuen Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789 Fax: (8863)5526611

## **Richtek Technology Corporation**

Taipei Office (Marketing)

5F, No. 95, Minchiuan Road, Hsintien City

Taipei County, Taiwan, R.O.C.

Tel: (8862)86672399 Fax: (8862)86672377

Email: marketing@richtek.com

Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.