## LM97593 Dual ADC / Digital Tuner / AGC

Check for Samples: [LM97593](#)

### FEATURES

- 100% Software Compatible with the CLC5903

- Pin Compatible with the CLC5903 Except for the Analog Input and Reference Section

- 123 dB Dynamic Range with CLC5526 DVGA (200kHz)

- On-chip Precision Reference

- User Programmable AGC with Enhanced Power Detector

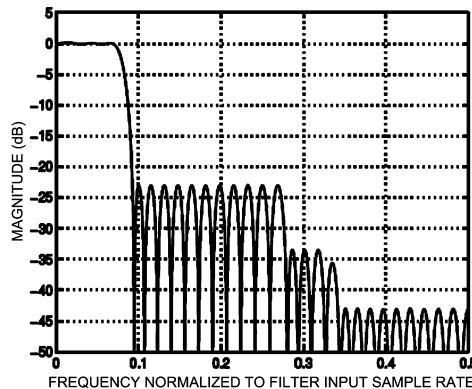

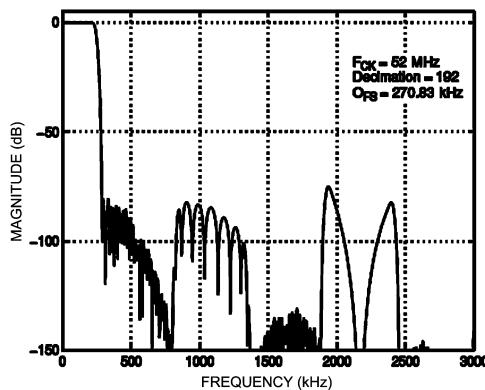

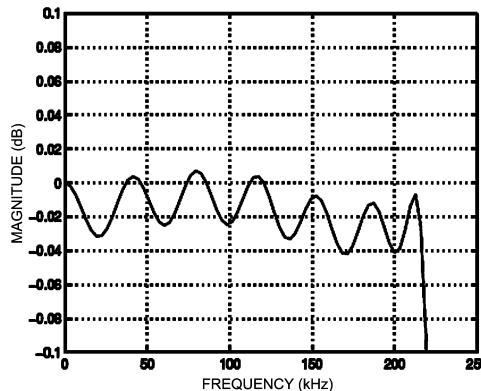

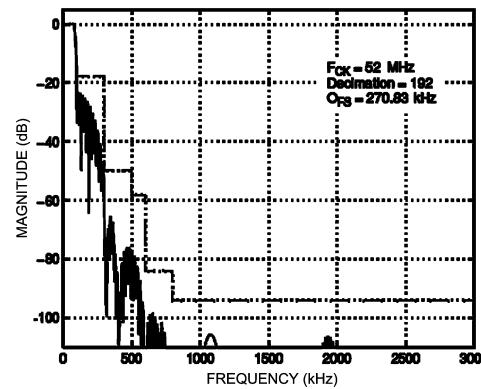

- Channel Filters Include a Fourth Order CIC Followed by 21-tap and 63-tap Symmetric FIRs

- Flexible Output Formats

- Serial and Parallel Output Ports

- JTAG Boundary Scan

- 8-bit Microprocessor Interface

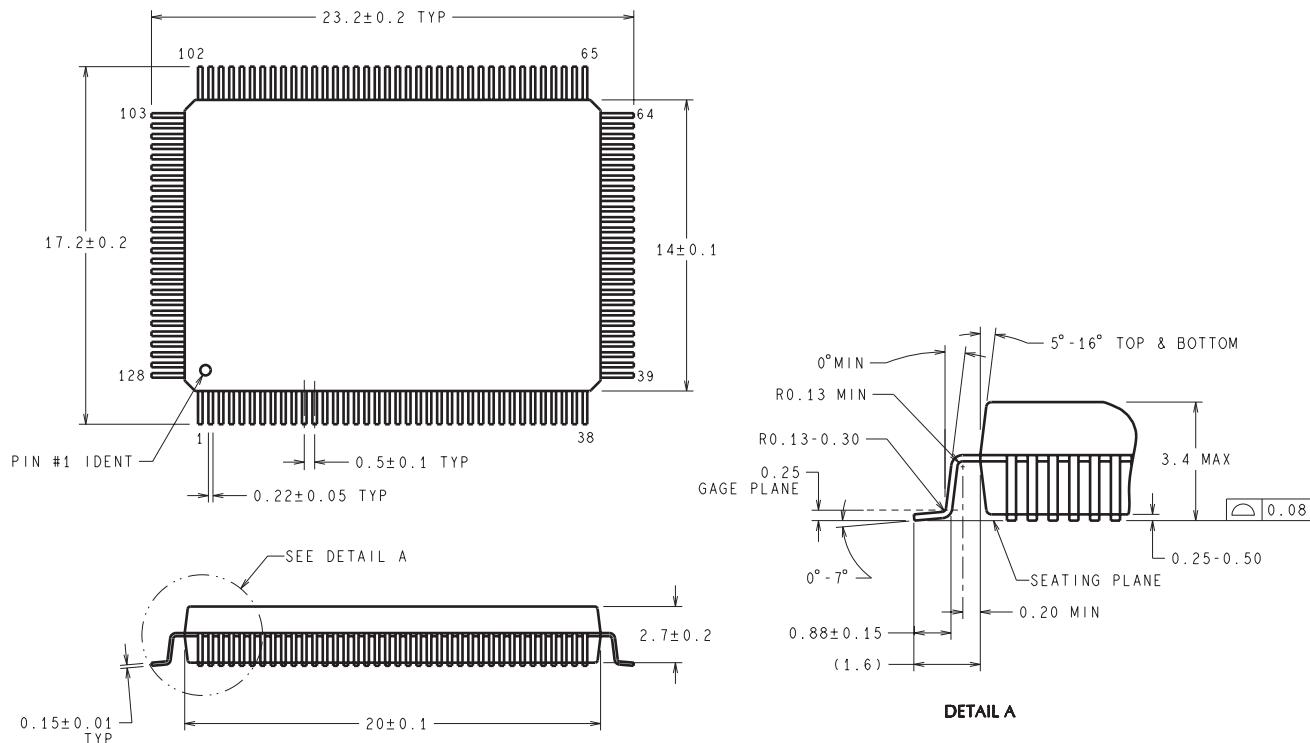

- 128 pin PQFP

### APPLICATIONS

- Cellular Basestations

- GSM / GPRS / EDGE / GSM Phase 2 Receivers

- Satellite Receivers

- Wireless Local Loop Receivers

- Digital Communications

### KEY SPECIFICATIONS

- Internal ADC Resolution: 12 Bits

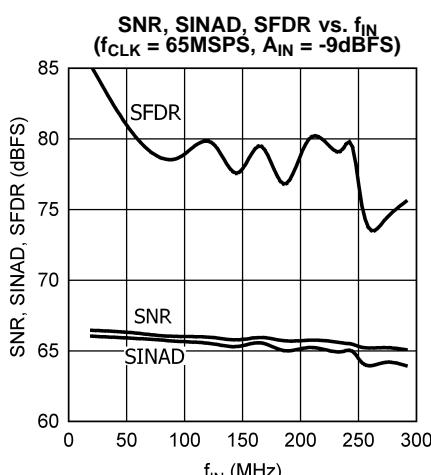

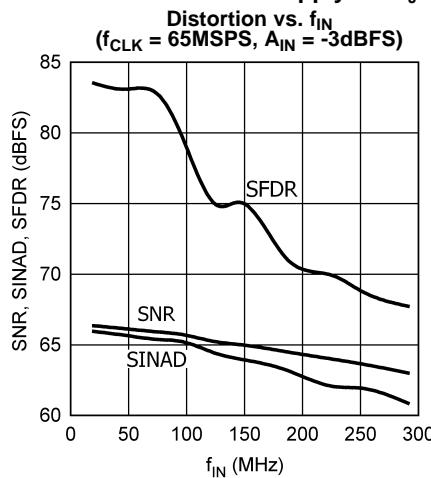

- Sample Rate: 65 MSPS

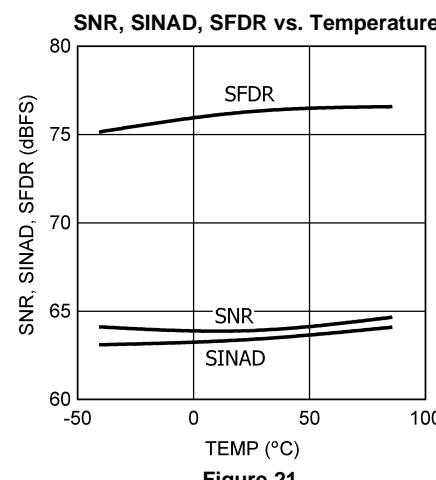

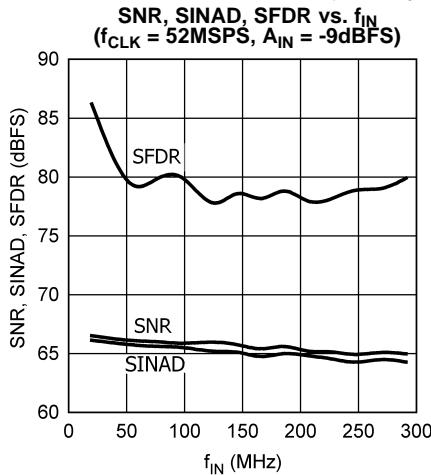

- SNR ( $f_{IN} = 250\text{MHz}$ , 11-bit, Nyquist): 62 dBFS (typ)

- SNR ( $f_{IN} = 250\text{MHz}$ , 200kHz): 83 dBFS (typ)

- SFDR ( $f_{IN} = 250\text{MHz}$ , 11-bit, Nyquist): 68 dBFS (typ)

- Full Power Bandwidth: 650 MHz (typ)

- Power Consumption: (65MSPS) 560 mW (typ)

### DESCRIPTION

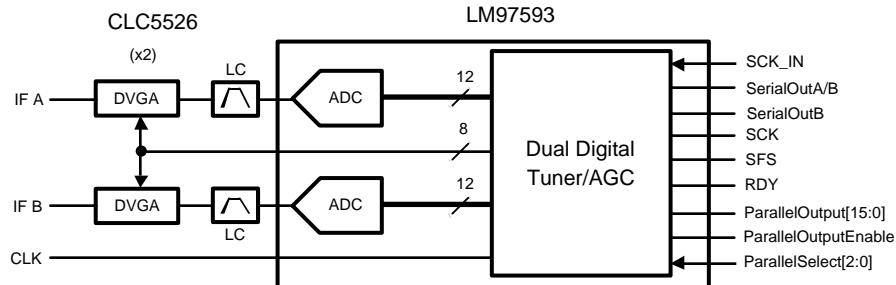

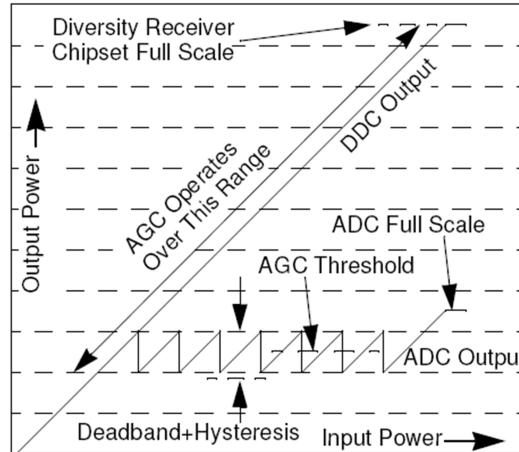

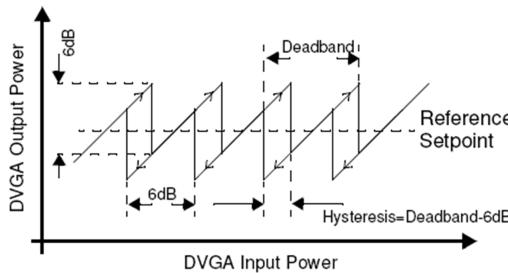

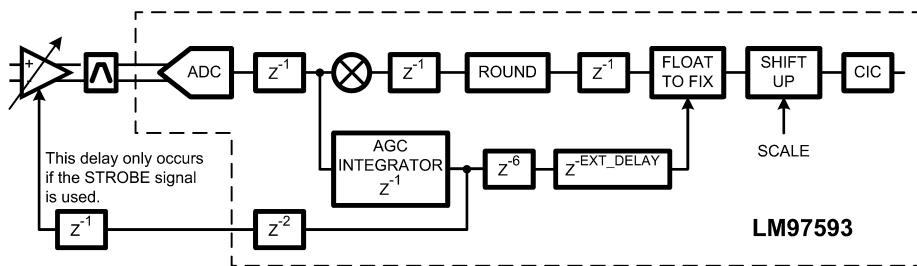

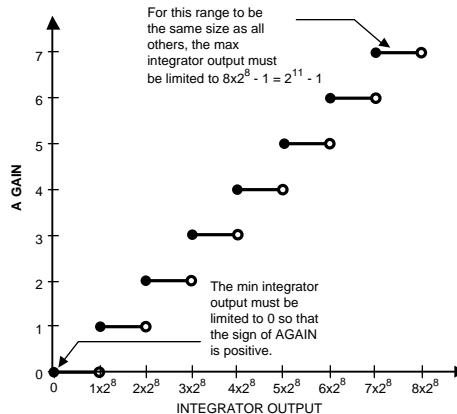

The LM97593 Dual ADC / Digital Tuner / AGC IC is a two channel digital downconverter (DDC) with integrated 12-bit analog-to-digital converters (ADCs) and automatic gain control (AGC). The LM97593 further enhances TI's Diversity Receiver Chipset (DRCS) by integrating a wide-bandwidth dual ADC core with the DDC. The complete DRCS includes one LM97593 Dual ADC / Digital Tuner / AGC and two CLC5526 digitally controlled variable gain amplifiers (DVGAs). This system allows direct IF sampling of signals up to 300MHz for enhanced receiver performance and reduced system costs. A block diagram for a DRCS-based narrowband communications system is shown in [Figure 1](#).

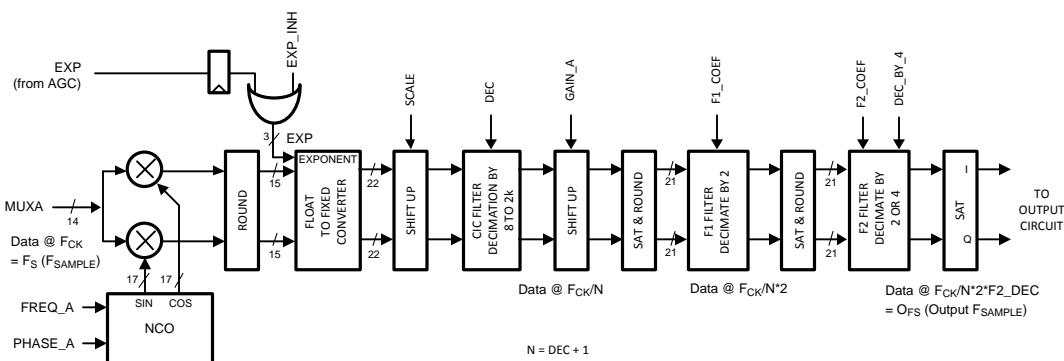

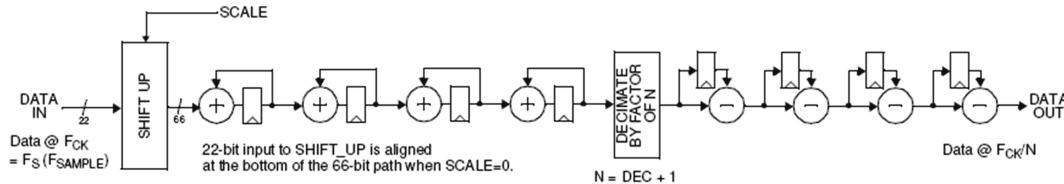

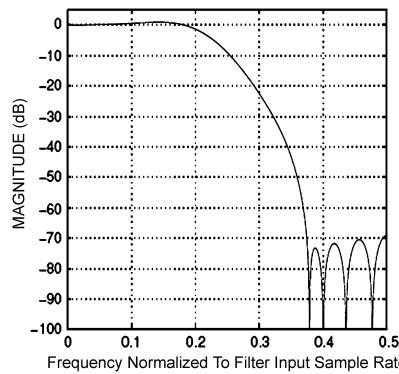

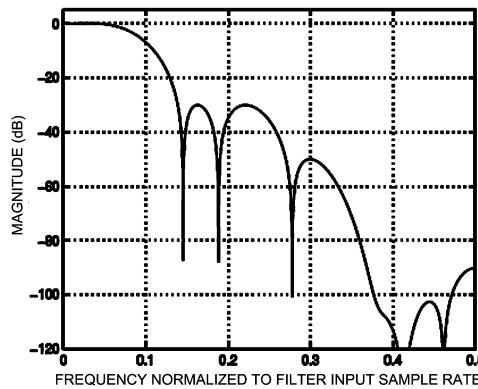

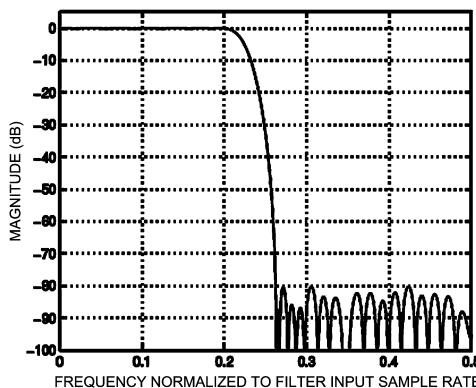

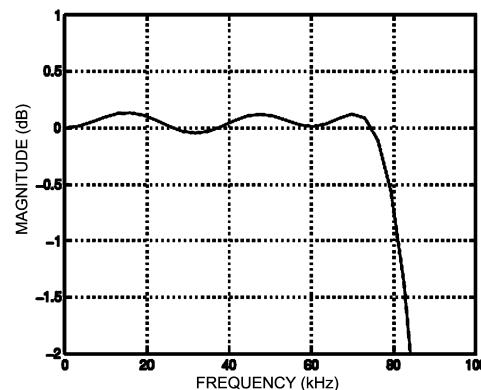

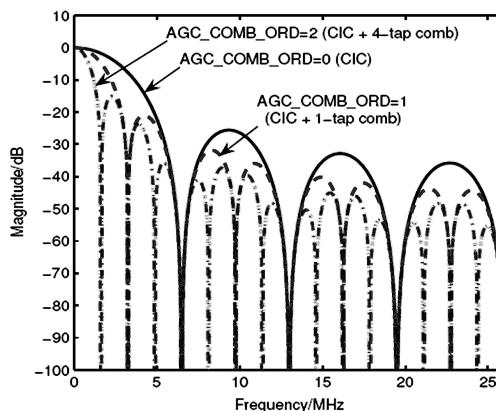

The LM97593 offers high dynamic range digital tuning and filtering based on hard-wired digital signal processing (DSP) technology. Each channel has independent tuning, phase offset, filter coefficients, and gain settings. Channel filtering is performed by a series of three filters. The first is a 4-stage Cascaded Integrator Comb (CIC) filter with a programmable decimation ratio from 8 to 2048. Next there are two symmetric FIR filters, a 21-tap and a 63-tap, both with independent programmable coefficients. The first FIR filter decimates the data by 2, the second FIR decimates by either 2 or 4. Channel filter bandwidth at 52MSPS ranges from  $\pm 650\text{kHz}$  down to  $\pm 1.3\text{kHz}$ . At 65MSPS, the maximum bandwidth increases to  $\pm 12\text{kHz}$ .

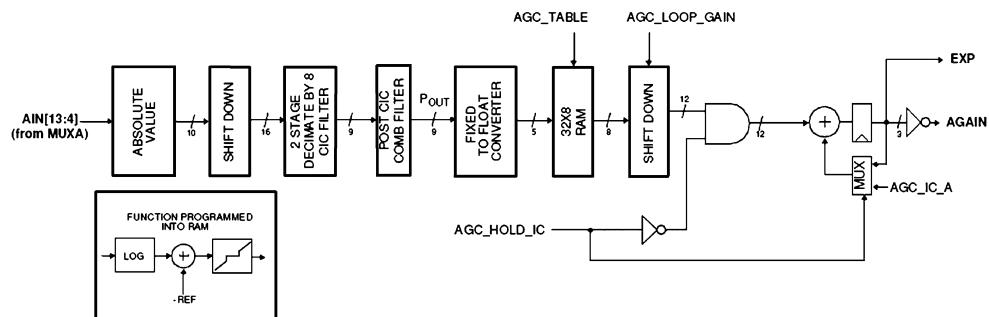

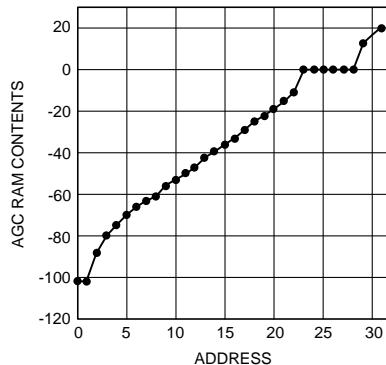

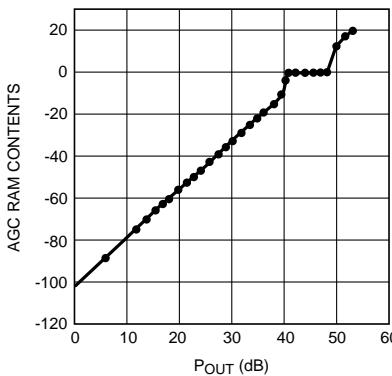

The LM97593's AGC controller monitors the ADC output and controls the ADC input signal level by adjusting the DVGA setting. AGC threshold, deadband+hysteresis, and the loop time constant are user defined. Total dynamic range of greater than 123dB full-scale signal to noise in a 200kHz bandwidth can be achieved with the Diversity Receiver Chipset.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

## Block Diagram 1

Figure 1. Diversity Receiver Chipset Block Diagram

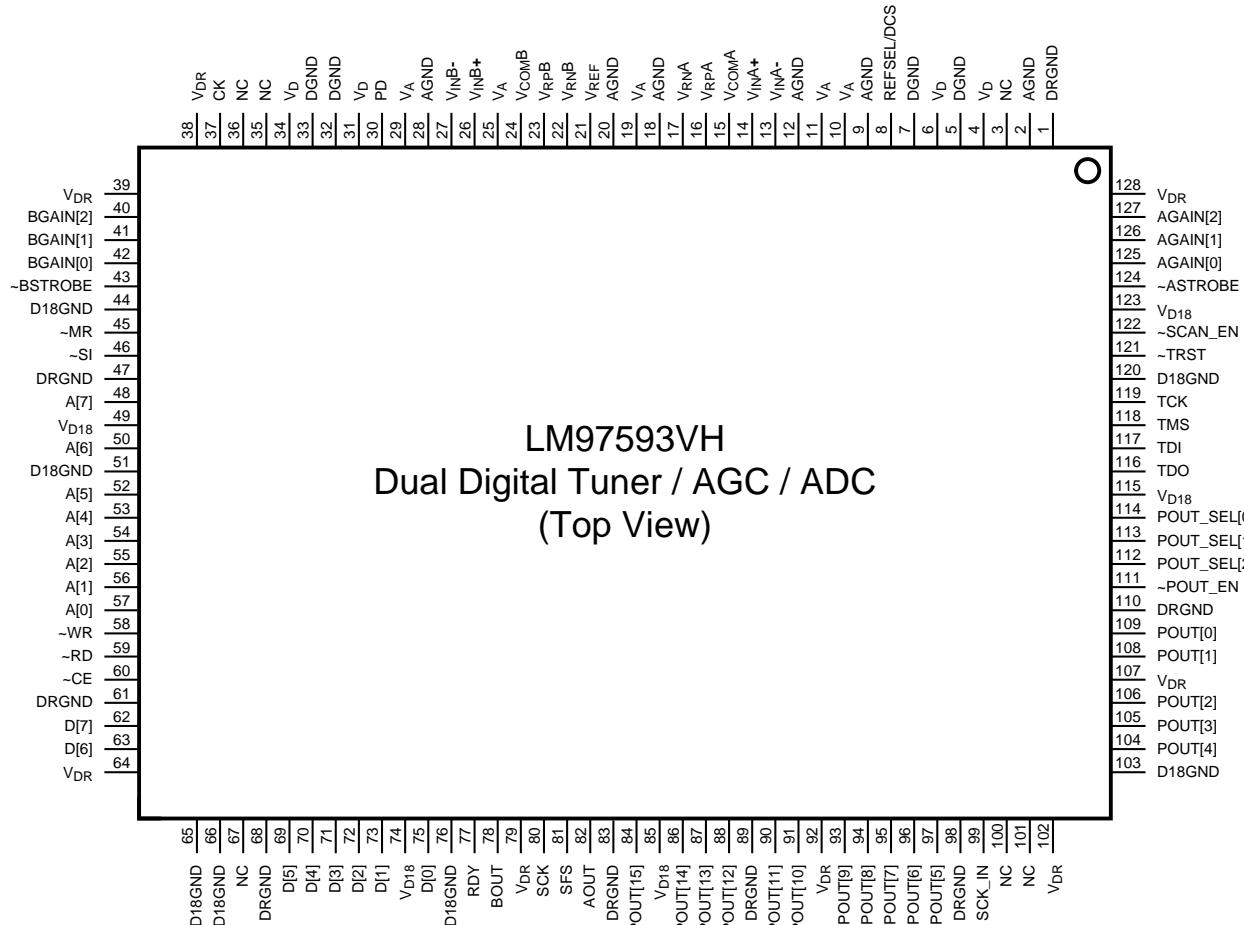

## Connection Diagram

Figure 2. LM97593VH PQFP Pinout

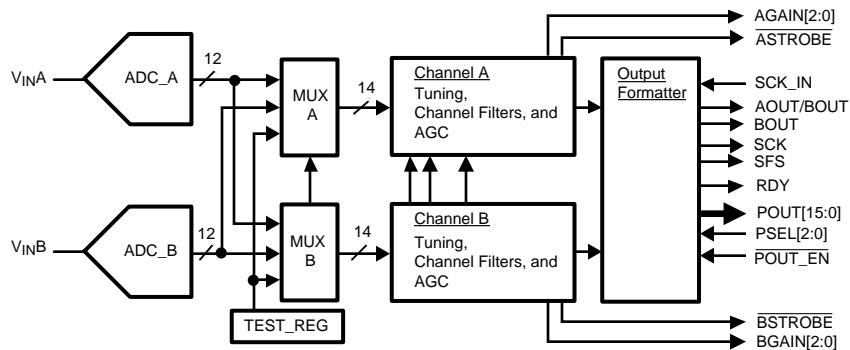

## Block Diagram 2

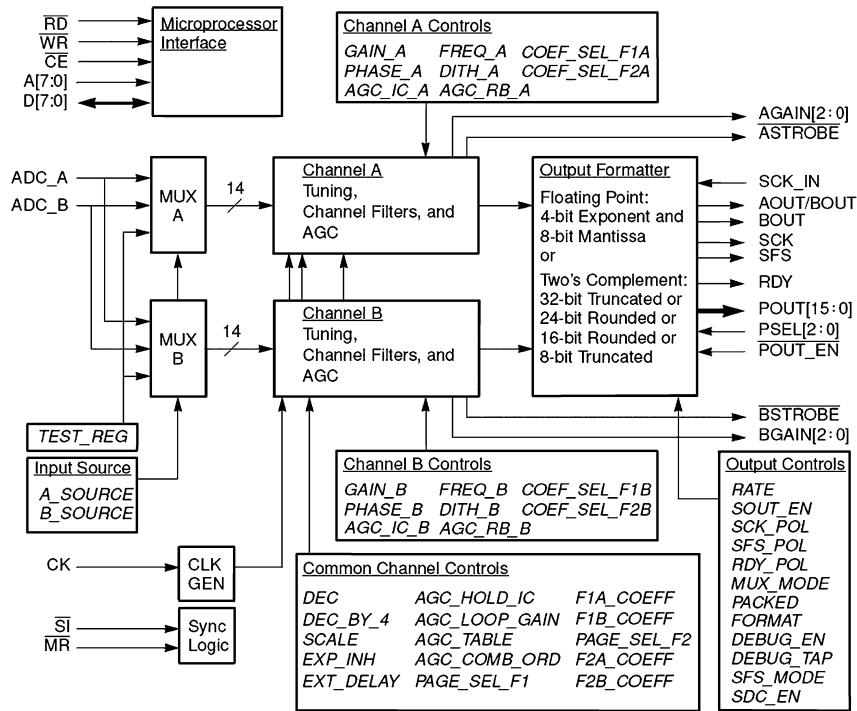

**Figure 3. LM97593 Block Diagram**

## PIN DESCRIPTIONS AND EQUIVALENT CIRCUITS

| Pin No.            | Symbol                                   | Equivalent Circuit     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>ANALOG I/O</b>  |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

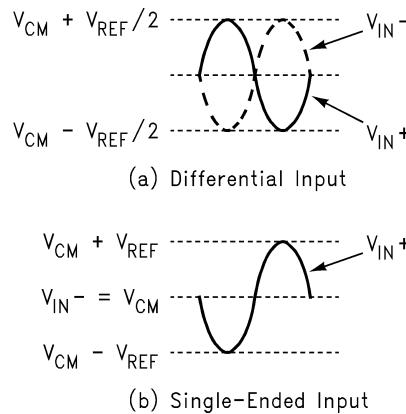

| 13<br>27           | V <sub>IN</sub> A–<br>V <sub>IN</sub> B– | Analog Input           | Negative differential input signal for the 'A' channel<br>Negative differential input signal for the 'B' channel                                                                                                                                                                                                                                                                                                                                                                                             |

| 14<br>26           | V <sub>IN</sub> A+<br>V <sub>IN</sub> B+ | Analog Input           | Positive differential input signal for the 'A' channel<br>Positive differential input signal for the 'B' channel                                                                                                                                                                                                                                                                                                                                                                                             |

| 21                 | V <sub>REF</sub>                         | Control / Analog Input | Reference Select Pin / External Reference Voltage Input<br>Input differential full scale swing = 2 * V <sub>REF</sub><br>V <sub>REF</sub> = V <sub>A</sub> to V <sub>A</sub> - 0.3V: Reference Voltage = 1.0 V (Internal)<br>V <sub>REF</sub> = 0.8V to 1.5V: Reference Voltage = V <sub>REF</sub> (External)                                                                                                                                                                                                |

| 15<br>24           | V <sub>COM</sub> A<br>V <sub>COM</sub> B | Analog Output          | Common Mode reference voltage for the 'A' channel<br>Common Mode reference voltage for the 'B' channel<br>These pins may be loaded to 1 mA for use as temperature stable 1.5V references.                                                                                                                                                                                                                                                                                                                    |

| 16<br>23           | V <sub>RP</sub> A<br>V <sub>RP</sub> B   | Analog Output          | Upper reference voltage for the 'A' channel<br>Upper reference voltage for the 'B' channel                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 17<br>22           | V <sub>RNA</sub><br>V <sub>RNB</sub>     | Analog Output          | Lower reference voltage for the 'A' channel<br>Lower reference voltage for the 'B' channel                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8                  | REFSEL/DCS                               | Control Input          | This is a three-state pin. V <sub>COM</sub> = V <sub>COM</sub> A or V <sub>COM</sub> B.<br>REFSEL/DCS = AGND: the internal reference is enabled and duty cycle correction is applied to the ADC input clock (CK).<br>REFSEL/DCS = V <sub>COM</sub> : the internal reference is enabled and no duty cycle correction is applied to the ADC input clock (CK).<br>REFSEL/DCS = V <sub>A</sub> : DCS is on, the internal reference is disabled. Apply a 0.8-1.2V external reference to the V <sub>REF</sub> pin. |

| <b>DIGITAL I/O</b> |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 30                 | PD                                       | Input                  | POWER DOWN, when high both ADCs are powered down, when low, both ADCs are enabled                                                                                                                                                                                                                                                                                                                                                                                                                            |

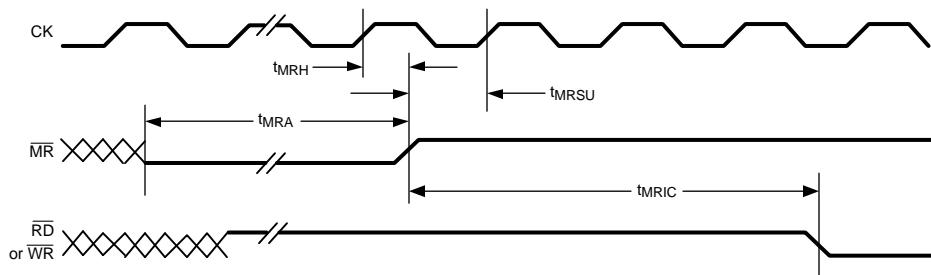

| 45                 | MR                                       | Input                  | MASTER RESET, Active low<br>Resets all registers within the chip. ASTROBE and BSTROBE are asserted during MR.                                                                                                                                                                                                                                                                                                                                                                                                |

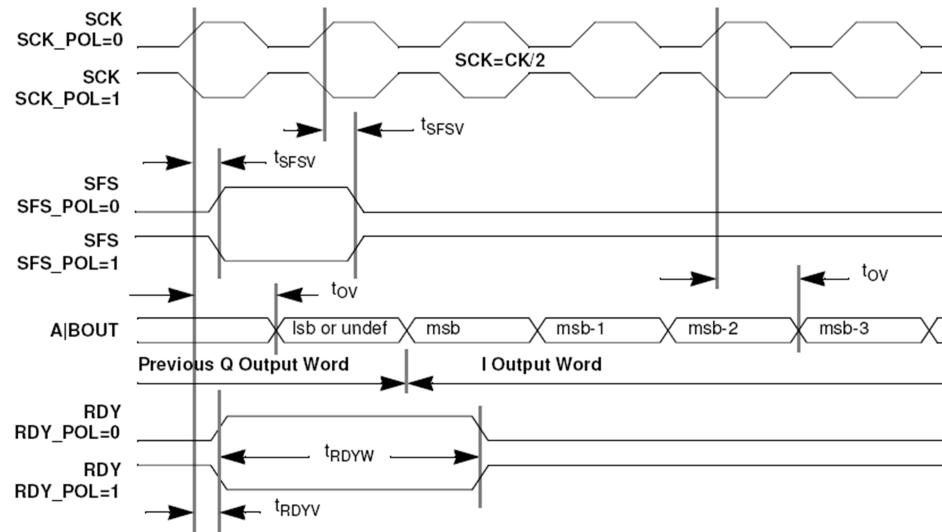

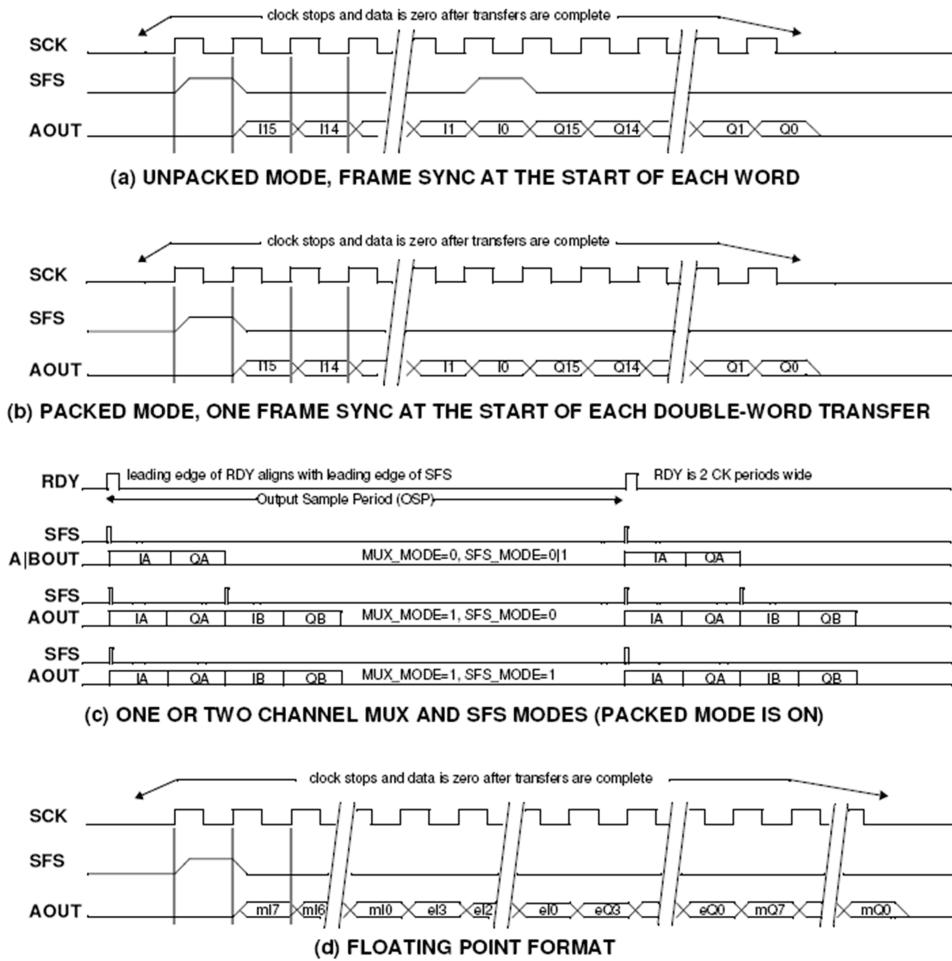

| 82<br>78           | AOUT<br>BOUT                             | Output                 | SERIAL OUTPUT DATA, Active high<br>The 2's complement serial output data is transmitted on these pins, MSB first. The output bits change on the rising edge of SCK (falling edge if SCK_POL=1) and should be captured on the falling edge of SCK (rising edge if SCK_POL=1). These pins are tri-stated at power up and are enabled by the SOUT_EN control register bit. See Figure 13 and Figure 75 timing diagrams. In Debug Mode AOUT=DEBUG[1], BOUT=DEBUG[0].                                             |

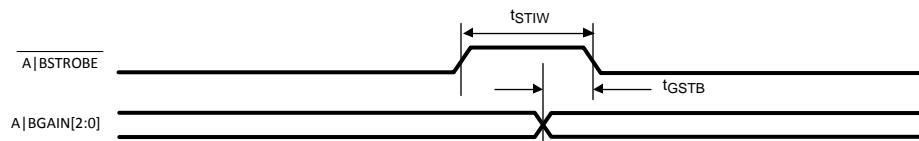

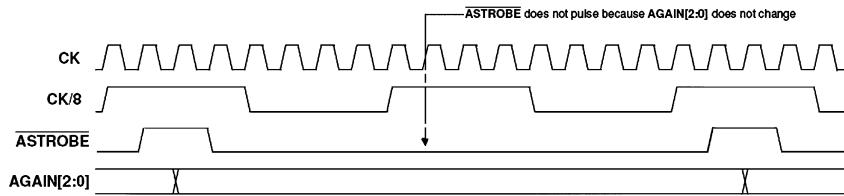

| 127:125<br>40:42   | AGAIN[2:0]<br>BGAIN[2:0]                 | Output                 | OUTPUT DATA TO DVGA, Active high<br>3 bit bus that sets the gain of the DVGA determined by the AGC circuit.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 124<br>43          | ASTROBE<br>BSTROBE                       | Output                 | DVGA STROBE, Active low<br>Strobes the data into the DVGA. See Figure 7 and Figure 82 timing diagrams.                                                                                                                                                                                                                                                                                                                                                                                                       |

## PIN DESCRIPTIONS AND EQUIVALENT CIRCUITS (continued)

| Pin No.                                                 | Symbol        | Equivalent Circuit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------|---------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80                                                      | SCK           | Output             | SERIAL DATA CLOCK, <i>Active high or low</i><br>The serial data is clocked out of the chip by this clock. The active edge of the clock is user programmable. This pin is tri-stated at power up and is enabled by the SOUT_EN control register bit. See <a href="#">Figure 13</a> and <a href="#">Figure 75</a> timing diagrams. In Debug Mode outputs an appropriate clock for the debug data. If RATE=0 the input <b>CK</b> duty cycle will be reflected to <b>SCK</b> .                                             |

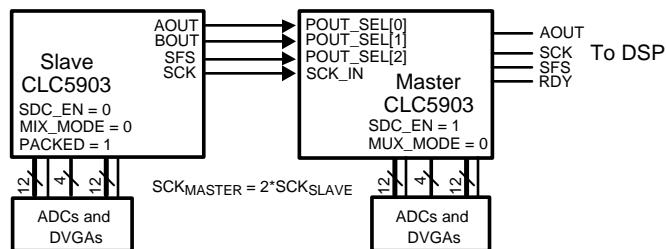

| 99                                                      | SCK_IN        | Input              | SERIAL DATA CLOCK INPUT, <i>Active high or low</i><br>Data bits from a serial daisy-chain slave are clocked into a serial daisy-chain master on the falling edge of SCK_IN (rising if SCK_POL=1 on the slave). Tie low if not used.                                                                                                                                                                                                                                                                                    |

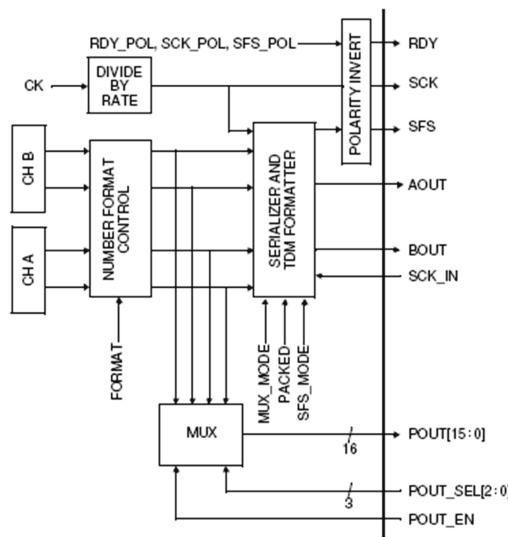

| 81                                                      | SFS           | Output             | SERIAL FRAME STROBE, <i>Active high or low</i><br>The serial word strobe. This strobe delineates the words within the serial output streams. This strobe is a pulse at the beginning of each serial word (PACKED=0) or each serial word I/Q pair (PACKED=1). The polarity of this signal is user programmable. This pin is tri-stated at power up and is enabled by the SOUT_EN control register bit. See <a href="#">Figure 13</a> and <a href="#">Figure 75</a> timing diagrams. In Debug Mode <b>SFS=DEBUG[2]</b> . |

| 84, 86:88,<br>90, 91,<br>93:97,<br>104:106,<br>108, 109 | POUT[15:0]    | Output             | PARALLEL OUTPUT DATA, <i>Active high</i><br>The output data is transmitted on these pins in parallel format. The <b>POUT_SEL[2:0]</b> pins select one of eight 16-bit output words. The <b>POUT_EN</b> pin enables these outputs. <b>POUT[15]</b> is the MSB. In Debug Mode <b>POUT[15:0]=DEBUG[19:4]</b> .                                                                                                                                                                                                            |

| 112:114                                                 | POUT_SEL[2:0] | Input              | PARALLEL OUTPUT DATA SELECT, <i>Active high</i><br>The 16-bit output word is selected with these 3 pins. Not used in Debug Mode. For a serial daisy-chain master, <b>POUT_SEL[2:0]</b> become inputs from the slave: <b>POUT_SEL[2]=SFS<sub>SLAVE</sub></b> , <b>POUT_SEL[1]=BOUT<sub>SLAVE</sub></b> , and <b>POUT_SEL[0]=AOUT<sub>SLAVE</sub></b> . Tie low if not used.                                                                                                                                             |

| 111                                                     | POUT_EN       | Input              | PARALLEL OUTPUT ENABLE. <i>Active low</i><br>This pin enables the chip to output the selected output word on the <b>POUT[15:0]</b> pins. Not used in Debug Mode. Tie high if not used.                                                                                                                                                                                                                                                                                                                                 |

| 77                                                      | RDY           | Output             | READY FLAG, <i>Active high or low</i><br>The chip asserts this signal to identify the beginning of an output sample period (OSP). The polarity of this signal is user programmable. This signal is typically used as an interrupt to a DSP chip, but can also be used as a start pulse to dedicated circuitry. This pin is active regardless of the state of SOUT_EN. In Debug Mode <b>RDY=DEBUG[3]</b> .                                                                                                              |

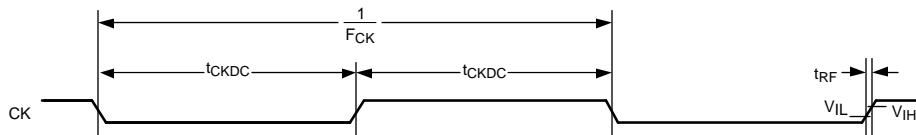

| 37                                                      | CK            | Input              | INPUT CLOCK. <i>Active high</i><br>The clock input to the chip. The The <b>V<sub>IN</sub>A</b> and <b>V<sub>IN</sub>B</b> analog input signals are sampled on the rising edge of this signal. <b>SI</b> is clocked into the chip on the rising edge of <b>CK</b> .                                                                                                                                                                                                                                                     |

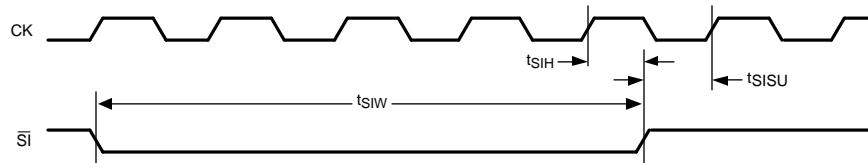

| 46                                                      | SI            | Input              | SYNC IN. <i>Active low</i><br>The sync input to the chip. The decimation counters, dither, and NCO phase can be synchronized by <b>SI</b> . This sync is clocked into the chip on the rising edge of <b>CK</b> . Tie this pin high if external sync is not required. All sample data is flushed by <b>SI</b> . To properly initialize the DVGA <b>ASTROBE</b> and <b>BSTROBE</b> are asserted during <b>SI</b> .                                                                                                       |

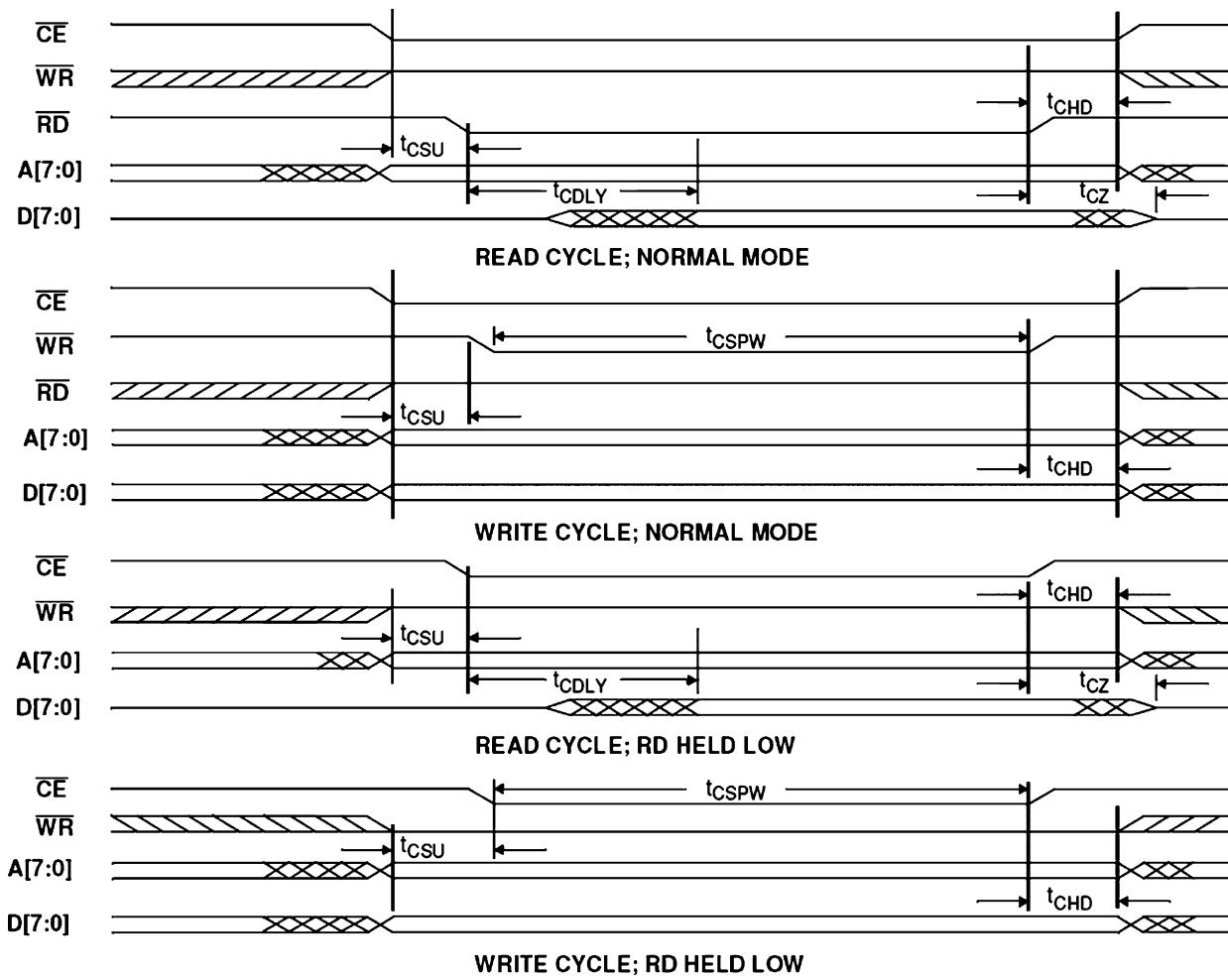

| 62, 63,<br>69:73, 75                                    | D[7:0]        | Input/Output       | DATA BUS. <i>Active high</i><br>This is the 8 bit control data I/O bus. Control register data is loaded into the chip or read from the chip through these pins. The chip will only drive output data on these pins when <b>CE</b> is low, <b>RD</b> is low, and <b>WR</b> is high.                                                                                                                                                                                                                                     |

| 48, 50, 52:57                                           | A[7:0]        | Input              | ADDRESS BUS. <i>Active high</i><br>These pins are used to address the control registers within the chip. Each of the control registers within the chip are assigned a unique address. A control register can be written to or read from by setting <b>A[7:0]</b> to the register's address and setting <b>CE</b> , <b>RD</b> , and <b>WR</b> appropriately.                                                                                                                                                            |

| 59                                                      | RD            | Input              | READ ENABLE. <i>Active low</i><br>This pin enables the chip to output the contents of the selected register on the <b>D[7:0]</b> pins when <b>CE</b> is also low.                                                                                                                                                                                                                                                                                                                                                      |

| 58                                                      | WR            | Input              | WRITE ENABLE. <i>Active low</i><br>This pin enables the chip to write the value on the <b>D[7:0]</b> pins into the selected register when <b>CE</b> is also low. This pin can also function as <b>RD</b> / <b>CE</b> if <b>RD</b> is held low. See <a href="#">Figure 15</a> for details.                                                                                                                                                                                                                              |

**PIN DESCRIPTIONS AND EQUIVALENT CIRCUITS (continued)**

| Pin No.                                 | Symbol                | Equivalent Circuit       | Description                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------|-----------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60                                      | $\overline{CE}$       | Input                    | CHIP ENABLE. <i>Active low</i><br>This control strobe enables the read or write operation. The contents of the register selected by $A[7:0]$ will be output on $D[7:0]$ when $\overline{RD}$ is low and $\overline{CE}$ is low. If $\overline{WR}$ is low and $\overline{CE}$ is low, then the selected register will be loaded with the contents of $D[7:0]$ . |

| 116                                     | TDO                   | Output                   | TEST DATA OUT. <i>Active high</i>                                                                                                                                                                                                                                                                                                                               |

| 117                                     | TDI                   | Input                    | TEST DATA IN. <i>Active high with pull-up</i>                                                                                                                                                                                                                                                                                                                   |

| 118                                     | TMS                   | Input                    | TEST MODE SELECT. <i>Active high with pull-up</i>                                                                                                                                                                                                                                                                                                               |

| 119                                     | TCK                   | Input                    | TEST CLOCK. <i>Active high</i> . Tie low if JTAG is not used.                                                                                                                                                                                                                                                                                                   |

| 121                                     | $\overline{TRST}$     | Input                    | TEST RESET. <i>Active low with pull-up</i><br>Asynchronous reset for TAP controller. Tie low or to $\overline{MR}$ if JTAG is not used.                                                                                                                                                                                                                         |

| 122                                     | $\overline{SCAN\_EN}$ | Input                    | SCAN ENABLE. <i>Active low with pull-up</i><br>Enables access to internal scan registers. Tie high. Used for manufacturing test only!                                                                                                                                                                                                                           |

| <b>Digital Power Supplies</b>           |                       |                          |                                                                                                                                                                                                                                                                                                                                                                 |

| 38, 39, 64,<br>79, 92, 102,<br>107, 128 | $V_{DR}$              | DDC Output Driver Power  | I/O Power Supply, 3.3V nominal. Quantity 8.                                                                                                                                                                                                                                                                                                                     |

| 1, 47, 61, 68,<br>83, 89, 98,<br>110    | DRGND                 | DDC Output Driver Ground | I/O Ground Return. Quantity 8.                                                                                                                                                                                                                                                                                                                                  |

| 49, 74, 85,<br>115, 123                 | $V_{D18}$             | DDC Core Power           | DSP Digital Core Power Supply, 1.8V nominal. Quantity 5.                                                                                                                                                                                                                                                                                                        |

| 49, 74, 85,<br>115, 123                 | $V_{D18}$             | DDC Core Power           | DSP Digital Core Power Supply, 1.8V nominal. Quantity 5.                                                                                                                                                                                                                                                                                                        |

| 44, 51, 65,<br>66, 76, 103,<br>120      | D18GND                | DDC Core Ground          | DSP Digital Core Ground Return. Quantity 7.                                                                                                                                                                                                                                                                                                                     |

| 4, 6, 31, 34                            | $V_D$                 | ADC Digital Power        | ADC Digital Logic Power Supply, 3.3V nominal. Quantity 4.                                                                                                                                                                                                                                                                                                       |

| 5, 7, 32, 33                            | DGND                  | ADC Digital Ground       | ADC Digital Logic Ground Return. Quantity 4.                                                                                                                                                                                                                                                                                                                    |

| <b>Analog Power Supplies</b>            |                       |                          |                                                                                                                                                                                                                                                                                                                                                                 |

| 10, 11, 19,<br>25, 29                   | $V_A$                 | ADC Analog Power         | ADC Analog Power Supply, 3.3V nominal. Quantity 5.                                                                                                                                                                                                                                                                                                              |

| 2, 9, 12, 18,<br>20, 28                 | AGND                  | ADC Analog Ground        | ADC Analog Ground Return. Quantity 6.                                                                                                                                                                                                                                                                                                                           |

| <b>Unconnected Pins</b>                 |                       |                          |                                                                                                                                                                                                                                                                                                                                                                 |

| 3, 35, 36, 67,<br>100, 101              | NC                    | NC                       | Not Connected. These pins should be left floating.                                                                                                                                                                                                                                                                                                              |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## Absolute Maximum Ratings<sup>(1)(2)(3)</sup>

|                                                                           |                                 |        |

|---------------------------------------------------------------------------|---------------------------------|--------|

| ADC Analog, Digital and IO Supply Voltages ( $V_A$ , $V_D$ and $V_{DR}$ ) | -0.3V to 4.2V                   |        |

| Difference between $V_A$ , $V_D$ , and $V_{DR}$                           | $\leq 100$ mV                   |        |

| Positive Core Supply Voltage ( $V_{D18}$ )                                | -0.3V to 2.35V                  |        |

| Voltage on Any Input or Output Pin<br>(Not to exceed 4.2V)                | -0.3V to ( $V_{DR}$ + 0.3V)     |        |

| Input Current at Any Pin other than Supply Pins <sup>(4)</sup>            | $\pm 5$ mA                      |        |

| Package Input Current <sup>(4)</sup>                                      | $\pm 50$ mA                     |        |

| Max Junction Temp ( $T_J$ )                                               | +125°C                          |        |

| Thermal Resistance ( $\theta_{JA}$ )                                      | 39°C/W                          |        |

| Package Dissipation at $T_A = 25^\circ\text{C}$ <sup>(5)</sup>            | 3.2W                            |        |

| ESD Susceptibility <sup>(6)</sup>                                         | Human Body Model (1.5kΩ, 100pF) | 2000 V |

|                                                                           | Machine Model (0Ω, 200pF)       | 200 V  |

| Charge Device Model                                                       | 750 V                           |        |

| Storage Temperature                                                       | -65°C to +150°C                 |        |

- (1) All voltages are measured with respect to GND = AGND = DGND = DRGND = 0V, unless otherwise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is ensured to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (4) When the input voltage at any pin exceeds the power supplies (that is,  $V_{IN} < AGND$ , or  $V_{IN} > V_A$ ), the current at that pin should be limited to  $\pm 25$  mA. The  $\pm 50$  mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of  $\pm 25$  mA to two.

- (5) The maximum allowable power dissipation is dictated by  $T_{J,max}$ , the junction-to-ambient thermal resistance, ( $\theta_{JA}$ ), and the ambient temperature, ( $T_A$ ), and can be calculated using the formula  $P_{D,max} = (T_{J,max} - T_A)/\theta_{JA}$ . The values for maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Such conditions should always be avoided.

- (6) Human Body Model is 100 pF discharged through a 1.5 kΩ resistor. Machine Model is 220 pF discharged through 0 Ω.

## Operating Ratings<sup>(1)(2)</sup>

|                                                                                                                                                                                                |                                                     |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| Soldering process must comply with Texas Instrument's Reflow Temperature Profile specifications. Refer to <a href="http://www.ti.com/packaging">http://www.ti.com/packaging</a> <sup>(3)</sup> |                                                     |  |

| Operating Temperature Range                                                                                                                                                                    | $-40^\circ\text{C} \leq T_A \leq +85^\circ\text{C}$ |  |

| ADC Analog, Digital and IO Supply Voltages ( $V_A$ , $V_D$ and $V_{DR}$ )                                                                                                                      | +3.0V to +3.6V                                      |  |

| Digital Core Supply Voltage ( $V_{D18}$ )                                                                                                                                                      | +1.6V to +2.0V                                      |  |

| Difference Between AGND, DGND, DRGND and D18GND                                                                                                                                                | $\leq 100$ mV                                       |  |

| Voltage on Any Input or Output Pin                                                                                                                                                             | 0V to +3.3V                                         |  |

| $V_{CM}$                                                                                                                                                                                       | 1.0V to 2.0V                                        |  |

| Clock Duty Cycle                                                                                                                                                                               | 30% to 70 %                                         |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is ensured to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.

- (2) All voltages are measured with respect to GND = AGND = DGND = DRGND = 0V, unless otherwise specified.

- (3) Reflow temperature profiles are different for lead-free and non-lead-free packages.

## Reliability Information

|                  |             |

|------------------|-------------|

| Transistor Count | 1.3 million |

|------------------|-------------|

## LM97593 Electrical Characteristics

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = D18GND = 0V,  $V_A = V_D = V_{DR} = +3.3V$ ,  $V_{D18} = +1.8V$ , Internal  $V_{REF} = +1.0V$ ,  $f_{CLK} = 65$  MHz,  $V_{CM} = V_{COM}$ ,  $t_R = t_F = 1$  ns,  $C_L = 5$  pF/pin. The ADC's 11 most significant bits observed at the mixer output debug tap with NCO = 0Hz. Typical values are for  $T_A = 25^\circ C$ . **Boldface limits apply for  $T_{MIN} \leq T_A \leq T_{MAX}$** . All other limits apply for  $T_A = 25^\circ C$ .<sup>(1)(2)(3)</sup>

| Symbol                                            | Parameter                                                                                        | Conditions      | Typical <sup>(4)</sup> | Limits     | Units (Limits) |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------|------------------------|------------|----------------|

| <b>STATIC CONVERTER CHARACTERISTICS</b>           |                                                                                                  |                 |                        |            |                |

|                                                   | Resolution with No Missing Codes                                                                 |                 | <b>11</b>              | Bits (min) |                |

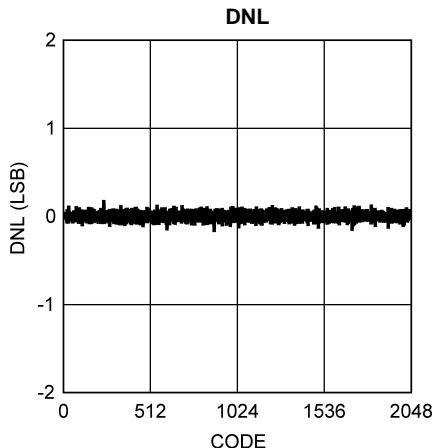

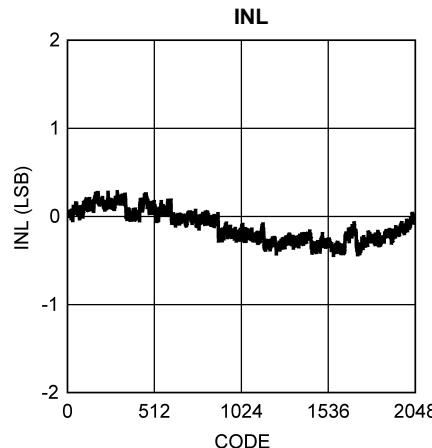

| INL                                               | Integral Non Linearity <sup>(5)</sup>                                                            | Ramp, End Point | <b>2</b>               | LSB (max)  |                |

|                                                   |                                                                                                  |                 | <b>-2</b>              | LSB (min)  |                |

| DNL                                               | Differential Non Linearity                                                                       | Ramp, End Point | <b>0.85</b>            | LSB (max)  |                |

|                                                   |                                                                                                  |                 | <b>-0.85</b>           | LSB (min)  |                |

| $V_{OFF}$                                         | Offset Error                                                                                     | -40°C to +85°C  | -4.1                   |            | LSB            |

| <b>REFERENCE AND ANALOG INPUT CHARACTERISTICS</b> |                                                                                                  |                 |                        |            |                |

| $V_{CM}$                                          | Common Mode Input Voltage                                                                        |                 | 1.5                    | <b>1.0</b> | V (min)        |

|                                                   |                                                                                                  |                 |                        | <b>2.0</b> | V (max)        |

| $V_{COMA}$<br>$V_{COMB}$                          | Reference Output Voltage                                                                         |                 | 1.5                    |            | V              |

| $C_{IN}$                                          | $V_{IN}$ Input Capacitance (each pin to GND)<br>( $V_{IN} = 1.5V_{dc} \pm 0.5V$ ) <sup>(6)</sup> | CK LOW          | 8                      |            | pF             |

|                                                   |                                                                                                  | CK HIGH         | 7                      |            | pF             |

| $V_{REF}$                                         | External Reference Voltage <sup>(7)</sup>                                                        |                 | 1.0                    | 0.8        | V (min)        |

|                                                   |                                                                                                  |                 |                        | 1.2        | V (max)        |

|                                                   | Reference Input Resistance                                                                       |                 | 1                      |            | MΩ             |

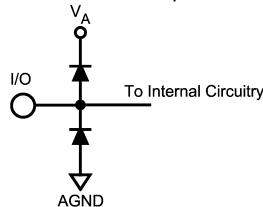

(1) The inputs are protected as shown below. Input voltage magnitudes above  $V_A$  or below GND will not damage this device, provided current is limited per [Note \(4\)](#).

(2) To ensure accuracy, it is required that  $|V_A - V_D| \leq 100$  mV and separate bypass capacitors are used at each power supply pin.

(3) With the test condition for  $V_{REF} = +1.0V$  (2V<sub>P-P</sub> differential input), the 12-Bit LSB is 488  $\mu$ V.

(4) Typical figures are at  $T_A = 25^\circ C$  and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured. Test Limits are specified to TI's AOQL (Average Outgoing Quality Level).

(5) Integral Non Linearity is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive and negative full-scale.

(6) The input capacitance is the sum of the package/pin capacitance and the sample and hold circuit capacitance.

(7) Optimum performance will be obtained by keeping the reference input in the 0.8V to 1.2V range. The LM4051CIM3-ADJ (SOT-23 package) is recommended for external reference applications.

## LM97593 Electrical Characteristics (continued)

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = 0V,  $V_A = V_D = V_{DR} = +3.3V$ ,  $V_{D18} = +1.8V$ , Internal  $V_{REF} = +1.0V$ ,  $f_{CLK} = 65$  MHz,  $V_{CM} = V_{COM}$ ,  $t_R = t_F = 1$  ns,  $C_L = 5$  pF/pin. The ADC's 11 most significant bits observed at the mixer output debug tap with NCO = 0Hz. Typical values are for  $T_A = 25^\circ C$ . **Boldface limits apply for  $T_{MIN} \leq T_A \leq T_{MAX}$** . All other limits apply for  $T_A = 25^\circ C$ .<sup>(1)(2)(3)</sup>

| Symbol                                   | Parameter                                                                                      | Conditions                                                                                                                                 | Typical <sup>(4)</sup> | Limits       | Units (Limits) |

|------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------|----------------|

| <b>DYNAMIC CONVERTER CHARACTERISTICS</b> |                                                                                                |                                                                                                                                            |                        |              |                |

| FPBW                                     | Full Power Bandwidth                                                                           |                                                                                                                                            | 650                    |              | MHz            |

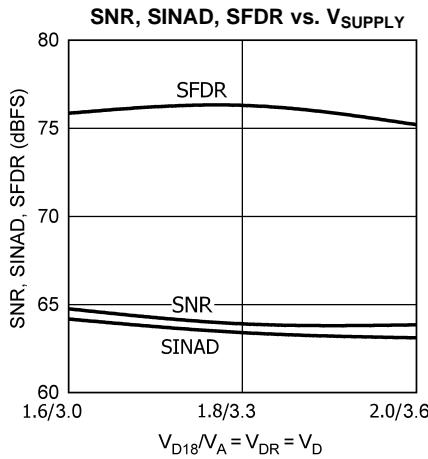

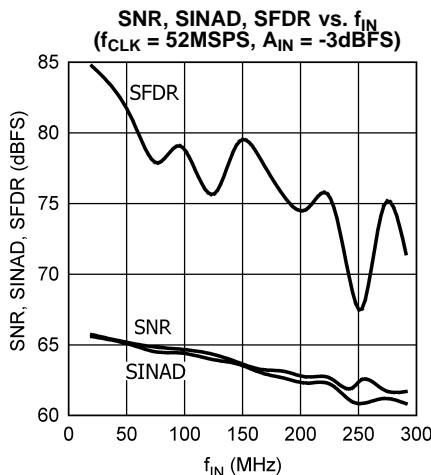

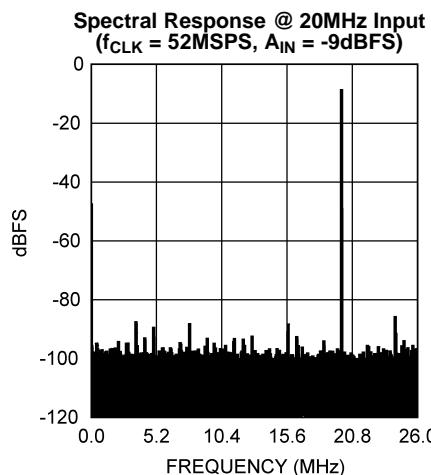

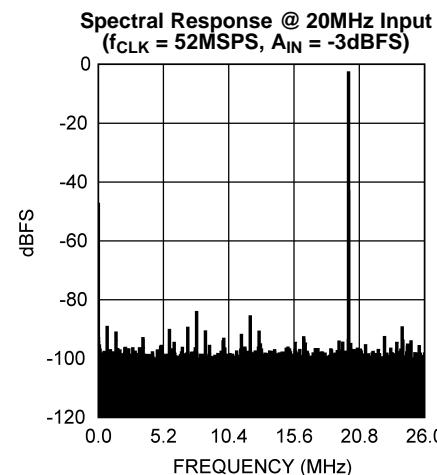

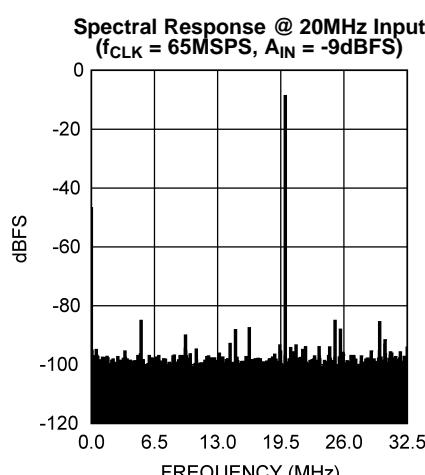

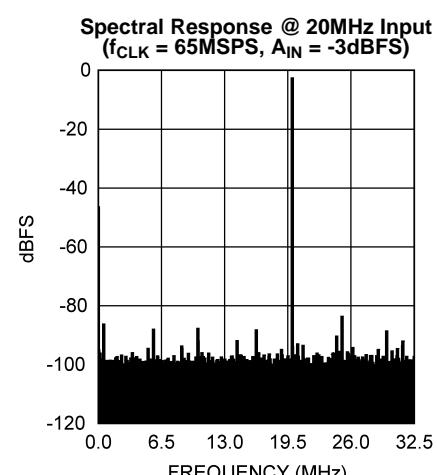

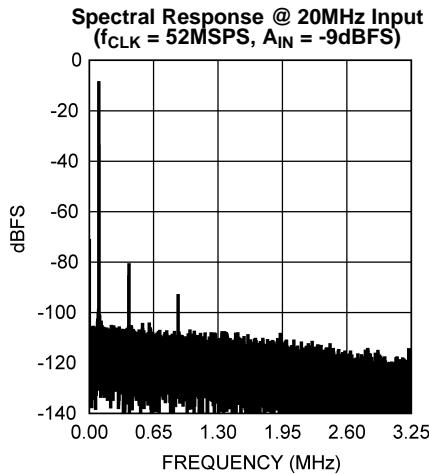

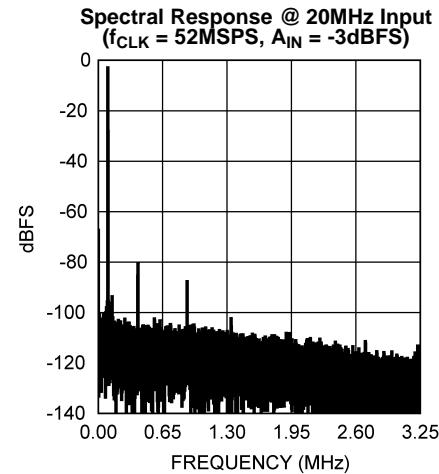

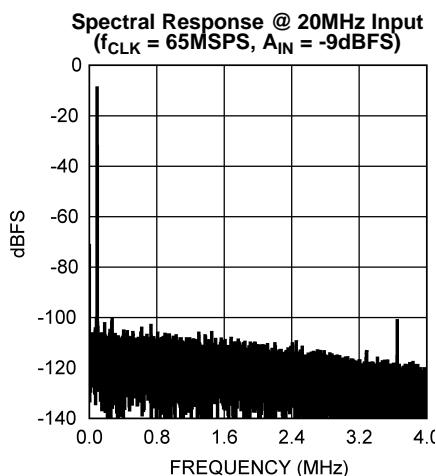

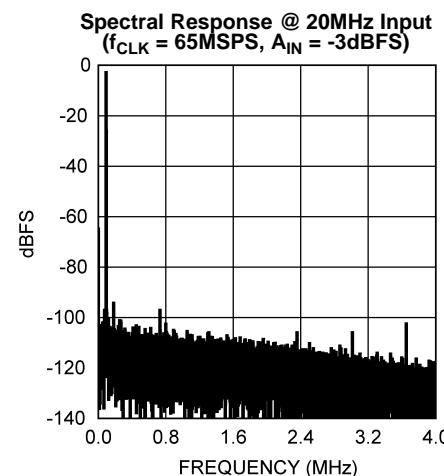

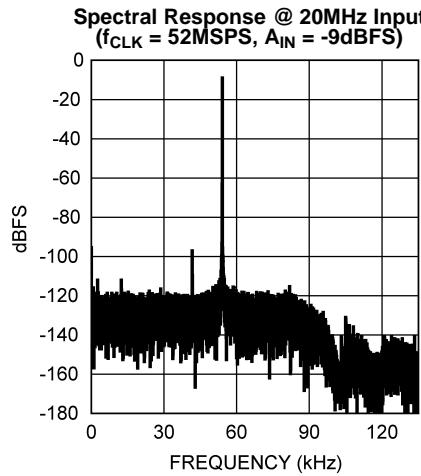

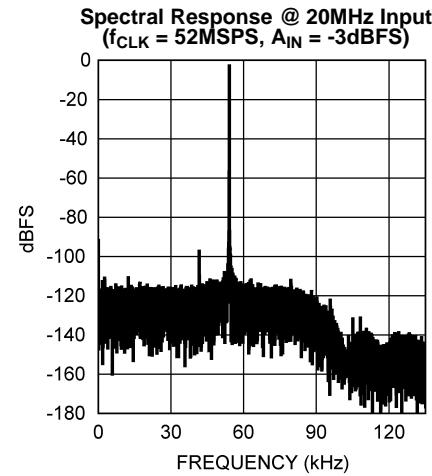

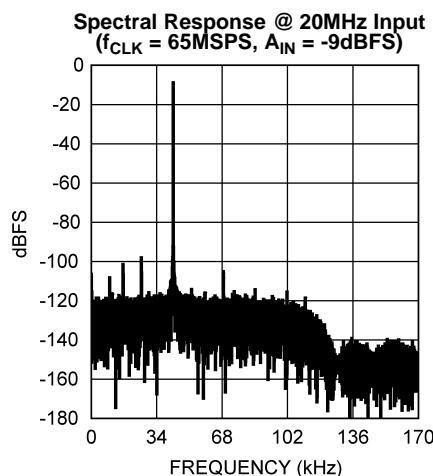

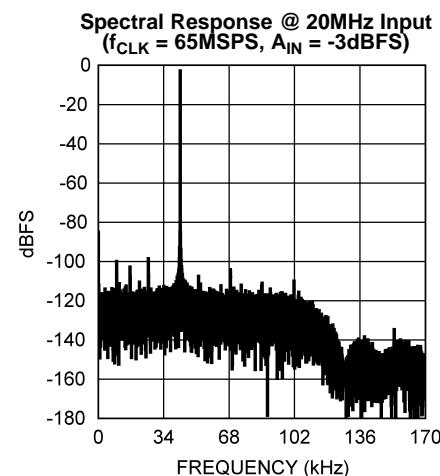

| SNR                                      | Signal-to-Noise Ratio                                                                          | $f_{IN} = 20$ MHz, $V_{IN} = -3$ dBFS                                                                                                      | 66.2                   |              | dBFS           |

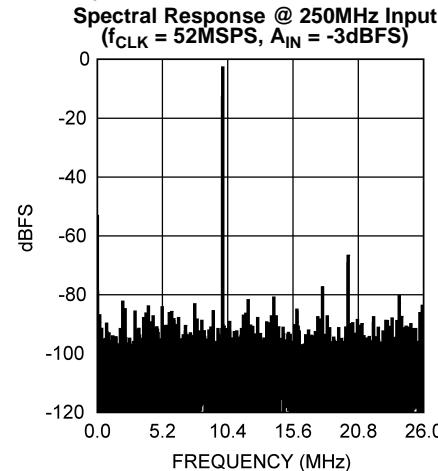

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -3$ dBFS                                                                                                     | 63.7                   |              | dBFS           |

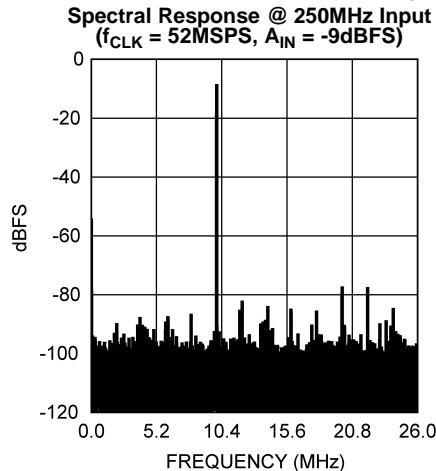

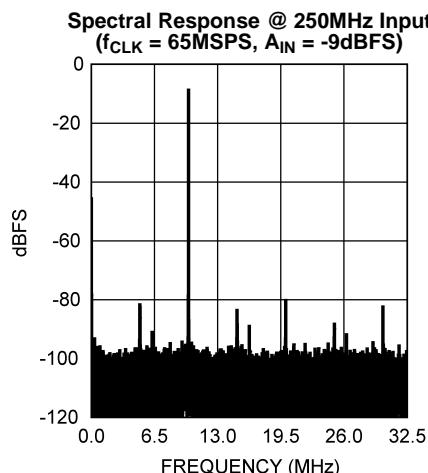

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -9$ dBFS                                                                                                     | 63.9                   | <b>62.2</b>  | dBFS (min)     |

| SINAD                                    | Signal-to-Noise and Distortion                                                                 | $f_{IN} = 20$ MHz, $V_{IN} = -3$ dBFS                                                                                                      | 62.8                   |              | dB             |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -3$ dBFS                                                                                                     | 62.0                   |              | dBFS           |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -9$ dBFS                                                                                                     | 63.4                   | <b>60.4</b>  | dBFS (min)     |

| ENOB                                     | Effective Number of Bits (Relative to Full Scale)                                              | $f_{IN} = 20$ MHz, $V_{IN} = -3$ dBFS                                                                                                      | 10.6                   |              | Bits           |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -3$ dBFS                                                                                                     | 10.0                   |              | Bits           |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -9$ dBFS                                                                                                     | 10.3                   |              | Bits (min)     |

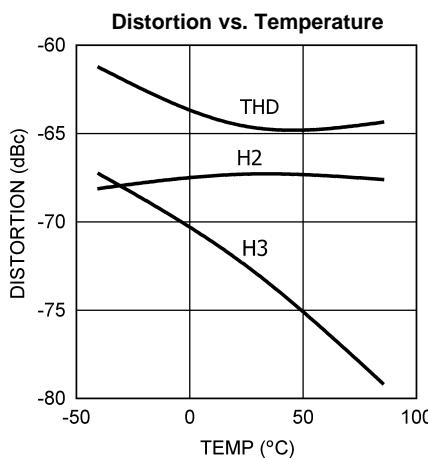

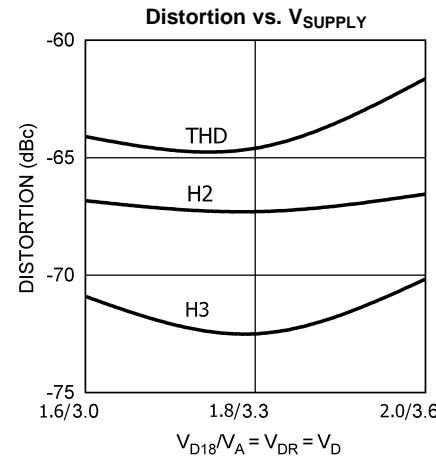

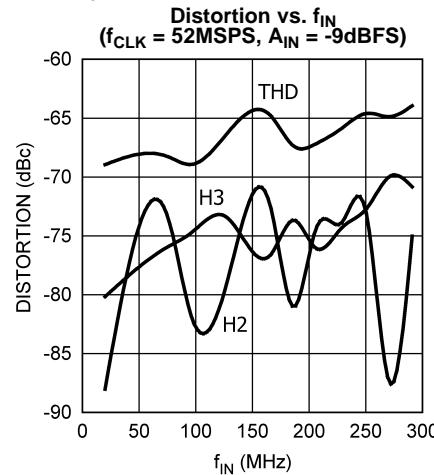

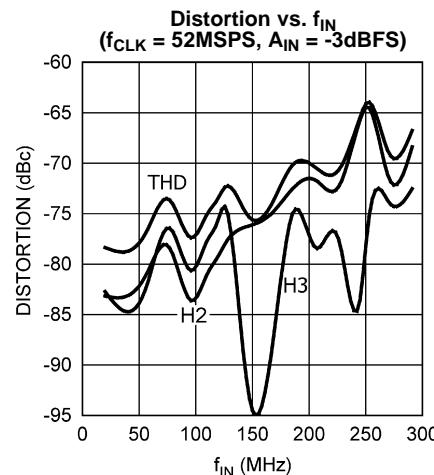

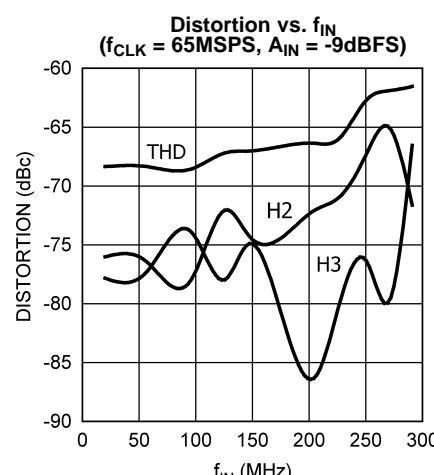

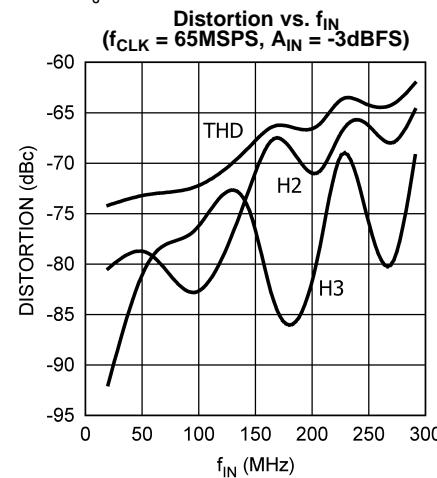

| THD                                      | Total Harmonic Distortion                                                                      | $f_{IN} = 20$ MHz, $V_{IN} = -3$ dBFS                                                                                                      | -77.1                  |              | dB             |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -3$ dBFS                                                                                                     | -57.9                  |              | dB             |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -9$ dBFS                                                                                                     | -64.6                  | <b>-54.1</b> | dB (max)       |

| H2                                       | Second Harmonic Distortion                                                                     | $f_{IN} = 20$ MHz, $V_{IN} = -3$ dBFS                                                                                                      | -82.7                  |              | dB             |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -3$ dBFS                                                                                                     | -59.9                  |              | dB             |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -9$ dBFS                                                                                                     | -67.3                  | -59.3        | dB (max)       |

| H3                                       | Third Harmonic Distortion                                                                      | $f_{IN} = 20$ MHz, $V_{IN} = -3$ dBFS                                                                                                      | -91.7                  |              | dB             |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -3$ dBFS                                                                                                     | -69.0                  |              | dB             |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -9$ dBFS                                                                                                     | -72.5                  | <b>-56.8</b> | dB (min)       |

| SFDR                                     | Spurious Free Dynamic Range                                                                    | $f_{IN} = 20$ MHz, $V_{IN} = -3$ dBFS                                                                                                      | 79.7                   |              | dBFS           |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -3$ dBFS                                                                                                     | 68.0                   |              | dBFS (min)     |

|                                          |                                                                                                | $f_{IN} = 249$ MHz, $V_{IN} = -9$ dBFS                                                                                                     | 76.3                   | <b>67.0</b>  | dBFS           |

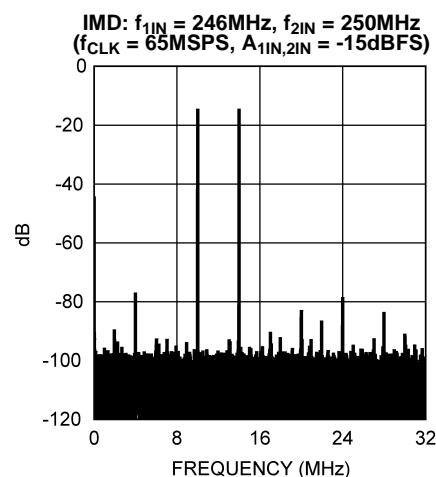

| IMD                                      | Intermodulation Distortion                                                                     | $f_{1IN} = 246$ MHz, $V_{IN} = -15$ dBFS                                                                                                   |                        |              |                |

|                                          |                                                                                                | $f_{2IN} = 250$ MHz, $V_{IN} = -15$ dBFS<br>( $f_{1IN} + f_{2IN} = -9$ dBFS)                                                               | -77.5                  |              | dBFS           |

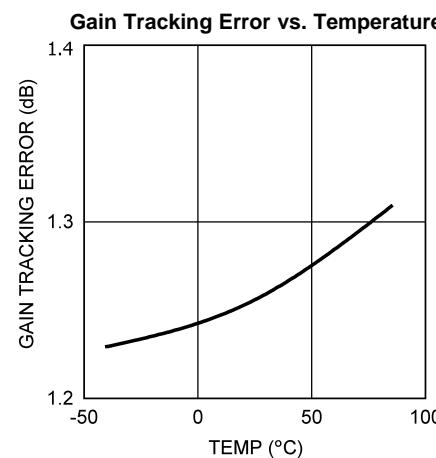

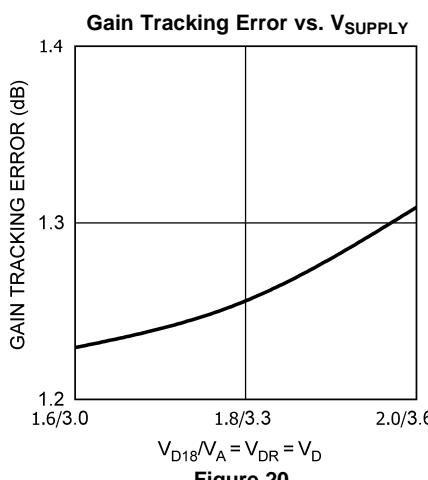

|                                          | Dynamic Gain Error                                                                             | -3 dBFS reference, -50dBFS target                                                                                                          | $\pm 1.3$              | $\pm 2$      | dB             |

| <b>INTERCHANNEL CHARACTERISTICS</b>      |                                                                                                |                                                                                                                                            |                        |              |                |

|                                          | Channel - Channel Offset Match                                                                 | 10 MHz -1dBFS driven                                                                                                                       | $\pm 0.2$              |              | %FS            |

|                                          | Channel - Channel Gain Match                                                                   | 10 MHz -1dBFS driven                                                                                                                       | $\pm 0.4$              |              | %FS            |

|                                          | Crosstalk (AGC fixed at 0dB gain, with AGC operating the crosstalk will improve at the output) | 249MHz -3dBFS driven channel, 50Ω termination measured channel                                                                             | 60(+42)<br>(8)         |              | dB             |

| <b>CIC OUTPUT CHARACTERISTICS</b>        |                                                                                                |                                                                                                                                            |                        |              |                |

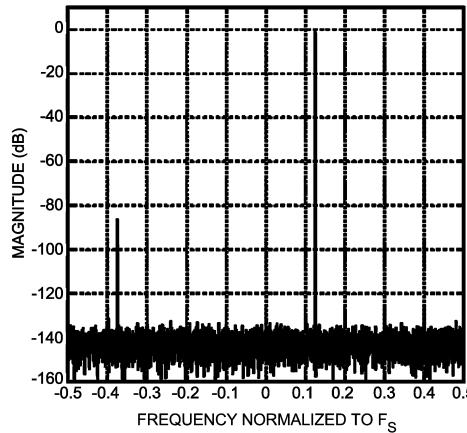

| SNR                                      | Signal-to-Noise Ratio                                                                          | CIC Decimation = 8, NCO = 11.1MHz (248.9MHz @65MSPS aliases to 11.1 MHz), $f_{IN} = 249$ MHz at -3dBFS, signal observed at F1 In Debug tap | 68.6                   | <b>66.1</b>  | dBFS           |

| SINAD                                    | Signal-to-Noise and Distortion                                                                 |                                                                                                                                            | 68.5                   | <b>66.1</b>  | dBFS           |

| SFDR                                     | Spurious Free Dynamic Range                                                                    |                                                                                                                                            | 75.1                   | <b>70.3</b>  | dB             |

| <b>DDC OUTPUT CHARACTERISTICS</b>        |                                                                                                |                                                                                                                                            |                        |              |                |

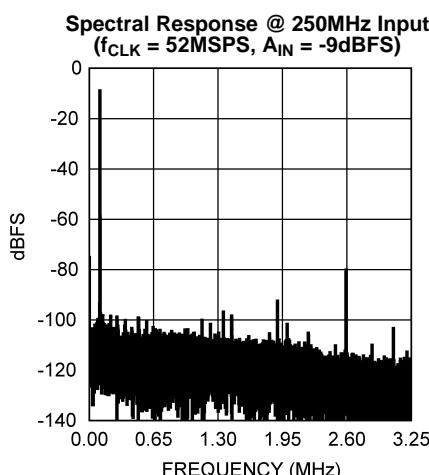

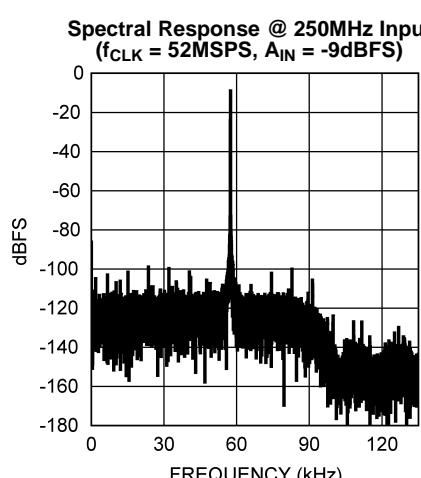

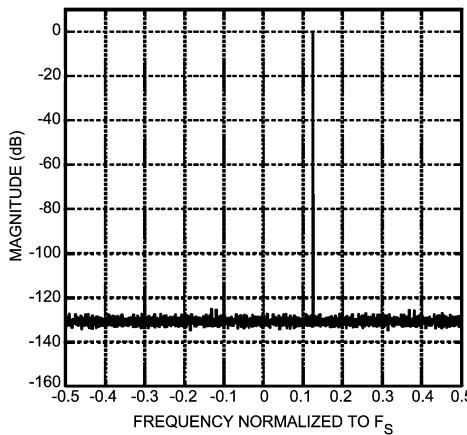

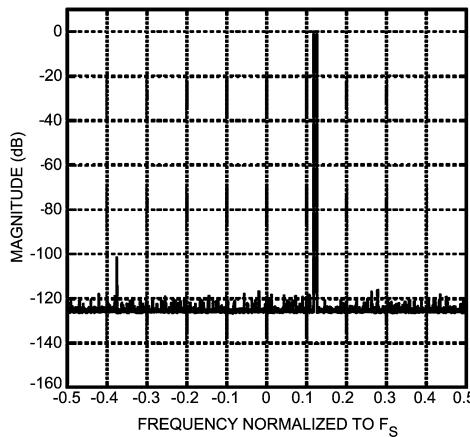

| SNR                                      | Signal-to-Noise Ratio                                                                          | GSM Filter set, 200kHz channel BW, NCO = 11.1MHz (248.9MHz @52MSPS aliases to 11.1 MHz), $f_S = 52$ MSPS, $f_{IN} = 249$ MHz at -9dBFS     | 82 (+42)<br>(8)        |              | dBFS           |

| SINAD                                    | Signal-to-Noise and Distortion                                                                 |                                                                                                                                            | 73                     |              | dB             |

| SFDR                                     | Spurious Free Dynamic Range                                                                    |                                                                                                                                            | 90                     |              | dB             |

(8) (+x) indicates the additional dynamic range provided by the AGC. The DVGA in front of the LM97593 provides 42 dB of gain adjustment.

## LM97593 Electrical Characteristics (continued)

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = D18GND = 0V,  $V_A = V_D = V_{DR} = +3.3V$ ,  $V_{D18} = +1.8V$ , Internal  $V_{REF} = +1.0V$ ,  $f_{CLK} = 65$  MHz,  $V_{CM} = V_{COM}$ ,  $t_R = t_F = 1$  ns,  $C_L = 5$  pF/pin. The ADC's 11 most significant bits observed at the mixer output debug tap with NCO = 0Hz. Typical values are for  $T_A = 25^\circ C$ . **Boldface limits apply for  $T_{MIN} \leq T_A \leq T_{MAX}$** . All other limits apply for  $T_A = 25^\circ C$ .<sup>(1)(2)(3)</sup>

| Symbol | Parameter                      | Conditions                                                                                                                             | Typical <sup>(4)</sup> | Limits | Units (Limits) |

|--------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------|----------------|

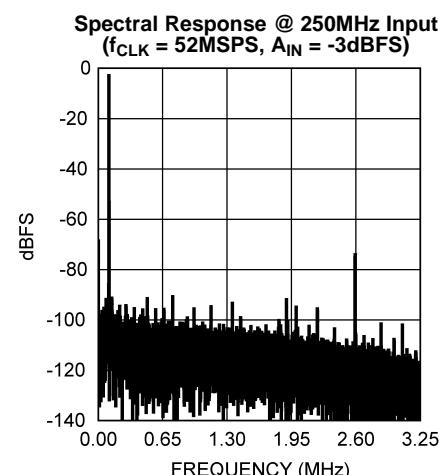

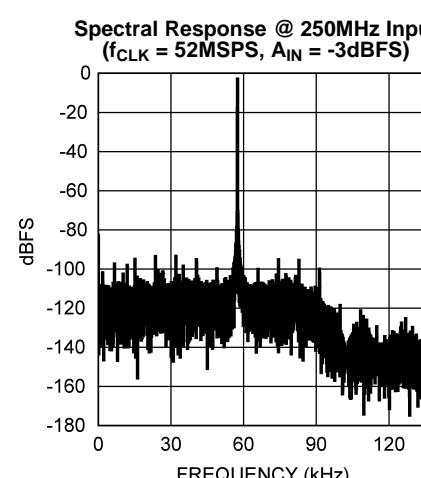

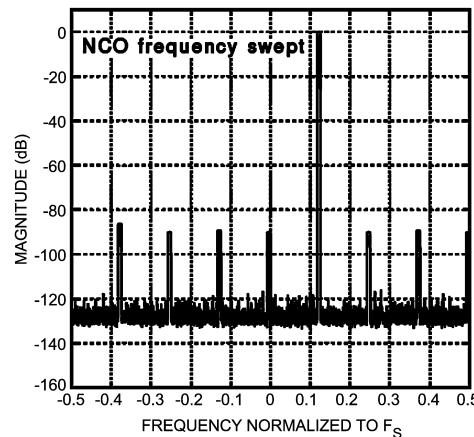

| SNR    | Signal-to-Noise Ratio          | GSM Filter set, 200kHz channel BW, NCO = 11.1MHz (248.9MHz @52MSPS aliases to 11.1 MHz), $f_S = 52$ MSPS, $f_{IN} = 249$ MHz at -3dBFS | 76 (+42)<br>(9)        |        | dBFS           |

| SINAD  | Signal-to-Noise and Distortion |                                                                                                                                        | 74                     |        | dBc            |

| SFDR   | Spurious Free Dynamic Range    |                                                                                                                                        | 90                     |        | dBc            |

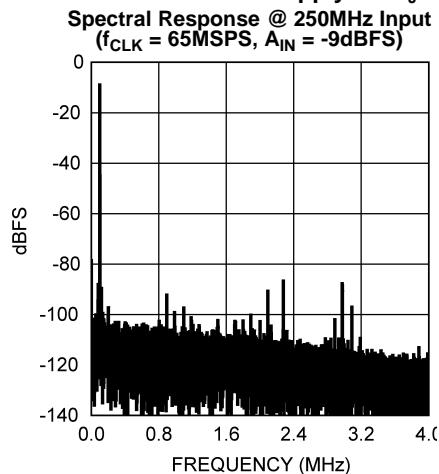

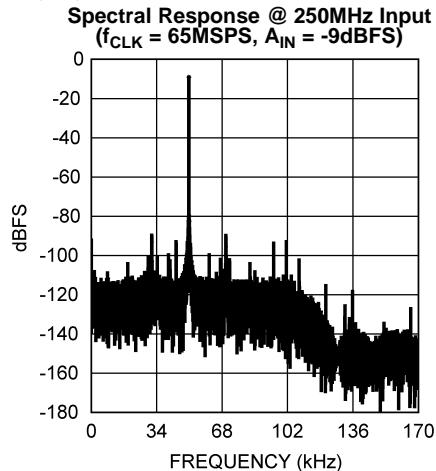

| SNR    | Signal-to-Noise Ratio          | GSM Filter set, 200kHz channel BW, NCO = 11.1MHz (248.9MHz @65MSPS aliases to 11.1 MHz), $f_S = 65$ MSPS, $f_{IN} = 249$ MHz at -9dBFS | 79 (+42)<br>(9)        |        | dBFS           |

| SINAD  | Signal-to-Noise and Distortion |                                                                                                                                        | 71                     |        | dBc            |

| SFDR   | Spurious Free Dynamic Range    |                                                                                                                                        | 81                     |        | dBc            |

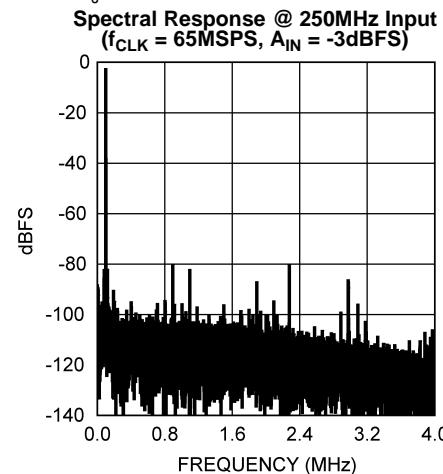

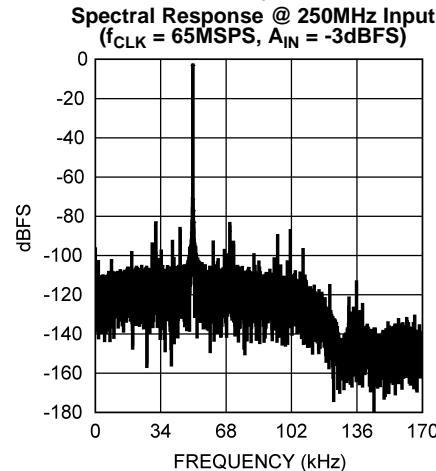

| SNR    | Signal-to-Noise Ratio          | GSM Filter set, 200kHz channel BW, NCO = 11.1MHz (248.9MHz @65MSPS aliases to 11.1 MHz), $f_S = 65$ MSPS, $f_{IN} = 249$ MHz at -3dBFS | 74 (+42)<br>(9)        |        | dBFS           |

| SINAD  | Signal-to-Noise and Distortion |                                                                                                                                        | 71                     |        | dBc            |

| SFDR   | Spurious Free Dynamic Range    |                                                                                                                                        | 80                     |        | dBc            |

(9) (+x) indicates the additional dynamic range provided by the AGC. The DVGA in front of the LM97593 provides 42 dB of gain adjustment.

## DC and Logic Electrical Characteristics

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = D18GND = 0V,  $V_A = V_D = V_{DR} = +3.3V$ ,  $V_{D18} = +1.8V$ , Internal  $V_{REF} = +1.0V$ ,  $f_{CLK} = 65$  MHz,  $V_{CM} = V_{COM}$ ,  $t_R = t_F = \text{TBD}$  ns,  $C_L = 5$  pF/pin. CIC Decimation = 48, F2 Decimation = 2. Typical values are for  $T_A = 25^\circ C$ . **Boldface limits apply for  $T_{MIN} \leq T_A \leq T_{MAX}$** . All other limits apply for  $T_A = 25^\circ C$ .

| Symbol                              | Parameter                                    | Conditions                                              | Typical <sup>(1)</sup> | Limits     | Units (Limits) |

|-------------------------------------|----------------------------------------------|---------------------------------------------------------|------------------------|------------|----------------|

| $V_{IL}$                            | Voltage input low                            |                                                         |                        | <b>0.7</b> | V (max)        |

| $V_{IH}$                            | Voltage input high                           |                                                         |                        | <b>2.3</b> | V (min)        |

| $I_{OZ}$                            | Input current                                |                                                         |                        | <b>20</b>  | $\mu A$        |

| $V_{OL}$                            | Voltage output low ( $I_{OL} = 7$ mA)        |                                                         |                        | <b>0.4</b> | V (max)        |

| $V_{OH}$                            | Voltage output high ( $I_{OH} = -7$ mA)      |                                                         |                        | <b>2.4</b> | V (min)        |

| $C_{IN}$                            | Input capacitance                            |                                                         |                        | <b>5.0</b> | pF             |

| <b>POWER SUPPLY CHARACTERISTICS</b> |                                              |                                                         |                        |            |                |

| $I_A$                               | ADC Analog Supply Current                    | 65MSPS                                                  | 96                     | <b>121</b> | mA (max)       |

| $I_A$                               | ADC Analog Supply Current                    | 52MSPS                                                  | 84                     |            | mA             |

| $I_D$                               | ADC Digital Supply Current                   | 65MSPS                                                  | 24                     | <b>28</b>  | mA (max)       |

| $I_D$                               | ADC Digital Supply Current                   | 52MSPS                                                  | 20                     |            | mA             |

| $I_{DR}$                            | Digital Output Supply Current <sup>(2)</sup> | 65MSPS                                                  | 14                     | <b>18</b>  | mA (max)       |

| $I_{DR}$                            | Digital Output Supply Current <sup>(2)</sup> | 52MSPS                                                  | 10                     |            | mA             |

| $I_{D18}$                           | Digital Core Supply Current                  | 65MSPS                                                  | 67                     | <b>78</b>  | mA (max)       |

| $I_{D18}$                           | Digital Core Supply Current                  | 52MSPS                                                  | 53                     |            | mA             |

| $P_{D65}$                           | Total Power Dissipation                      | GSM Set, 65MSPS                                         | 560                    | <b>793</b> | mW (max)       |

| $P_{D52}$                           | Total Power Dissipation                      | GSM Set, 52MSPS                                         | 485                    |            | mW             |

| PSRR                                | Power Supply Rejection Ratio                 | Rejection of Full-Scale Error with $V_A = 3.0$ vs. 3.6V |                        |            | dB             |

- (1) Typical figures are at  $T_A = 25^\circ C$  and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured. Test Limits are specified to TI's AOQL (Average Outgoing Quality Level).

- (2)  $I_{DR}$  is the current consumed by the switching of the output drivers and is primarily determined by load capacitance on the output pins, the supply voltage,  $V_{DR}$ , and the rate at which the outputs are switching (which is signal dependent).  $I_{DR} = V_{DR}(C_0 \times f_0 + C_1 \times f_1 + \dots + C_{11} \times f_{11})$  where  $V_{DR}$  is the output driver power supply voltage,  $C_n$  is total capacitance on the output pin, and  $f_n$  is the average frequency at which that pin is toggling.

## AC Electrical Characteristics

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = D18GND = 0V,  $V_A = V_D = V_{DR} = +3.3V$  ( $\pm 10\%$ ),  $V_{D18} = +1.8V$  ( $\pm 10\%$ ), Internal  $V_{REF} = +1.0V$ ,  $f_{CLK} = 65$  MHz,  $V_{CM} = V_{COM}$ ,  $t_R = t_F = 1$  ns,  $C_L = 5$  pF/pin. CIC Decimation = 48, F2 Decimation = 2. Typical values are for  $T_A = 25^\circ C$ . **Boldface limits apply for  $T_{MIN} \leq T_A \leq T_{MAX}$** . All other limits apply for  $T_A = 25^\circ C$ .<sup>(1)</sup>

| Symbol                           | Parameter ( $C_L=50pF$ )                                                                                | Min | Typical <sup>(2)</sup> | Max | Units             |

|----------------------------------|---------------------------------------------------------------------------------------------------------|-----|------------------------|-----|-------------------|

| <b>Clock Input</b>               |                                                                                                         |     |                        |     |                   |

| $F_{CK}$                         | Clock ( <b>CK</b> ) Frequency (Figure 6)                                                                | 20  |                        | 65  | MHz               |

| $t_{CKDC}$                       | <b>CK</b> duty cycle, DCS off (Figure 6)                                                                | 40  |                        | 60  | %                 |

| $t_{RF}$                         | CK rise and fall times ( $V_{IL}$ to $V_{IH}$ ) (Figure 6)                                              |     |                        | 2   | ns                |

|                                  | NCO Tuning Resolution                                                                                   |     | 0.02                   |     | Hz                |

|                                  | NCO Phase Resolution                                                                                    |     | 0.005                  |     | o                 |

| <b>Control Interface</b>         |                                                                                                         |     |                        |     |                   |

| $t_{MRA}$                        | <b>MR</b> Active Time (Figure 4)                                                                        | 4   |                        |     | <b>CK</b> periods |

| $t_{MRIC}$                       | <b>MR</b> Inactive to first Control Port Access (Figure 4)                                              | 10  |                        |     | <b>CK</b> periods |

| $t_{MRSU}$                       | <b>MR</b> Setup Time to CK (Figure 4)                                                                   | 6   |                        |     | ns                |

| $t_{MRH}$                        | <b>MR</b> Hold Time from CK (Figure 4)                                                                  | 2   |                        |     | ns                |

| $t_{SISU}$                       | <b>SI</b> Setup Time to CK (Figure 5)                                                                   | 6   |                        |     | ns                |

| $t_{SIH}$                        | <b>SI</b> Hold Time from CK (Figure 5)                                                                  | 2   |                        |     | ns                |

| $t_{SIW}$                        | <b>SI</b> Pulse Width (Figure 5)                                                                        | 4   |                        |     | <b>CK</b> periods |

| <b>DVGA Interface</b>            |                                                                                                         |     |                        |     |                   |

| $t_{STIW}$                       | <b>A BSTROBE</b> Inactive Pulse Width (Figure 7)                                                        |     | 2                      |     | <b>CK</b> periods |

| $t_{GSTB}$                       | <b>A BGAIN</b> setup before <b>A BSTROBE</b> (Figure 7)                                                 | 6   |                        |     | ns                |

| <b>Parallel Output Interface</b> |                                                                                                         |     |                        |     |                   |

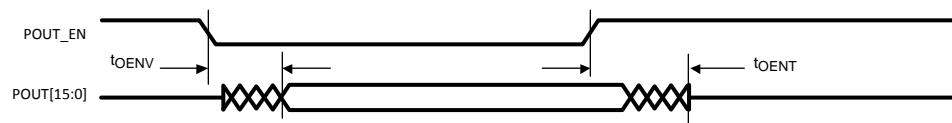

| $t_{OENV}$                       | <b>POUT_EN</b> Active to <b>POUT[15:0]</b> Valid (Figure 9)                                             |     |                        | 12  | ns                |

| $t_{OENT}$                       | <b>POUT_EN</b> Inactive to <b>POUT[15:0]</b> Tri-State (Figure 9)                                       |     |                        | 10  | ns                |

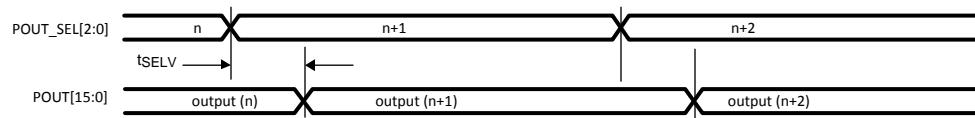

| $t_{SELV}$                       | <b>PSEL[2:0]</b> to <b>POUT[15:0]</b> Valid (Figure 10)                                                 |     |                        | 13  | ns                |

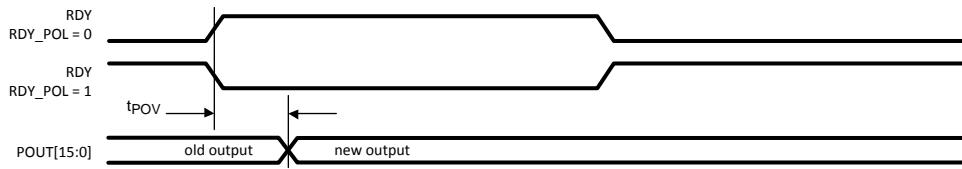

| $t_{POV}$                        | <b>RDY</b> to <b>POUT[15:0]</b> New Value Valid (Note 5) (Figure 11)                                    |     |                        | 7   | ns                |

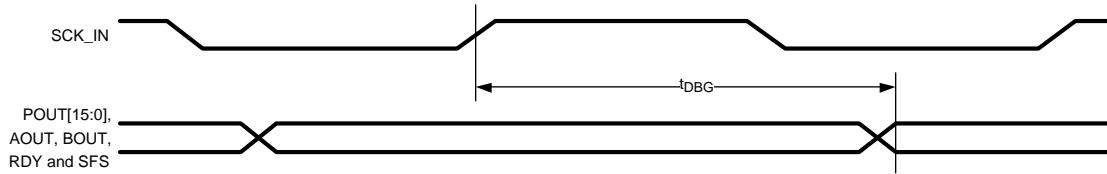

| $t_{DBG}$                        | <b>SCK</b> to <b>POUT[15:0]</b> , <b>RDY</b> , <b>SFS</b> , <b>AOUT</b> , <b>BOUT</b> Valid (Figure 12) |     |                        | 4   | ns                |

| <b>Serial Interface</b>          |                                                                                                         |     |                        |     |                   |

| $t_{SFSV}$                       | <b>SCK</b> to <b>SFS</b> Valid (Note 3) (Figure 13)                                                     | -2  | 1.6                    | 3.5 | ns                |

| $t_{OV}$                         | <b>SCK</b> to <b>A BOUT</b> Valid (Note 4) (Figure 13)                                                  | -2  | 1.7                    | 3.5 | ns                |

| $t_{RDYW}$                       | <b>RDY</b> Pulse Width (Figure 13)                                                                      |     | 2                      |     | <b>CK</b> periods |

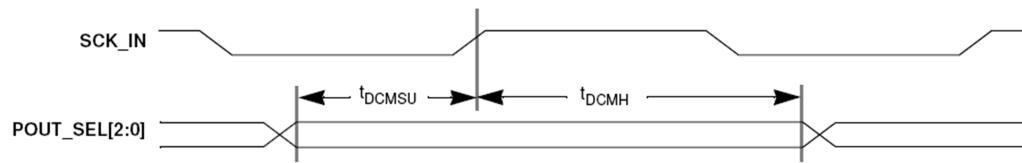

| $t_{DCMSU}$                      | <b>PSEL[2:0]</b> Setup Time to <b>SCK_IN</b> (Figure 8)                                                 | 3   | 1.4                    |     | ns                |

| $t_{DCMH}$                       | <b>PSEL[2:0]</b> Hold Time from <b>SCK_IN</b> (Figure 8)                                                | 0.5 | -0.9                   |     | ns                |

| $t_{RDYV}$                       | <b>SCK</b> to <b>RDY</b> valid (Figure 13)                                                              | -3  | 1.8                    | 4   | ns                |

| <b>JTAG Interface</b>            |                                                                                                         |     |                        |     |                   |

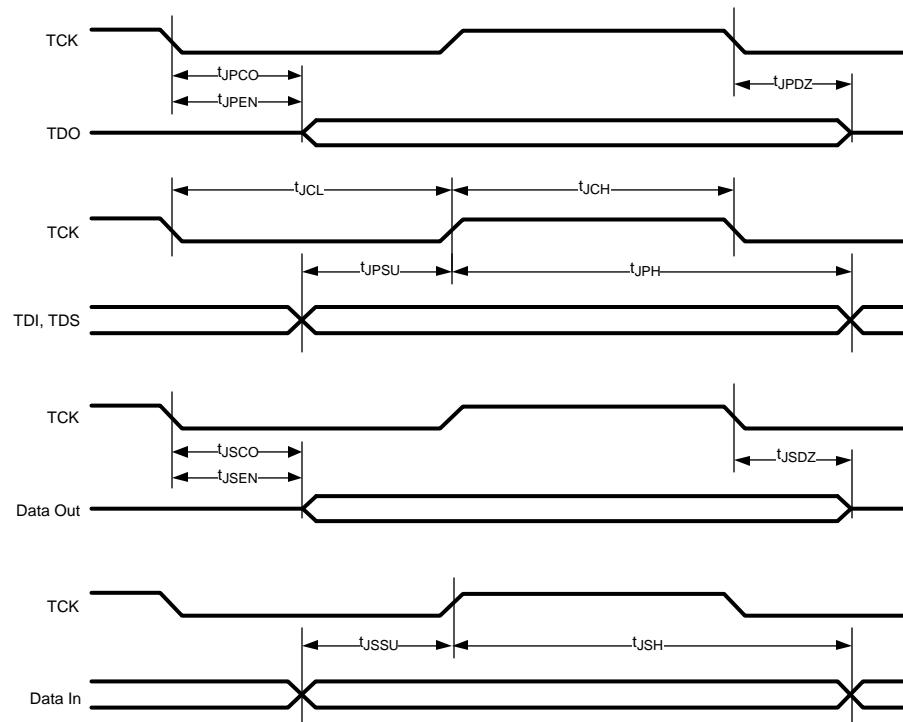

| $t_{JPCO}$                       | Propagation Delay <b>TCK</b> to <b>TDO</b> (Figure 14)                                                  |     |                        | 25  | ns                |

| $t_{JSCE}$                       | Propagation Delay <b>TCK</b> to Data Out (Figure 14)                                                    |     |                        | 35  | ns                |

| $t_{JPDZ}$                       | Disable Time <b>TCK</b> to <b>TDO</b> (Figure 14)                                                       |     |                        | 25  | ns                |

| $t_{JSDZ}$                       | Disable Time <b>TCK</b> to Data Out (Figure 14)                                                         |     |                        | 35  | ns                |

| $t_{JOPEN}$                      | Enable Time <b>TCK</b> to <b>TDO</b> (Figure 14)                                                        | 0   |                        | 25  | ns                |

| $t_{JSEN}$                       | Enable Time <b>TCK</b> to Data Out (Figure 14)                                                          | 0   |                        | 35  | ns                |

| $t_{JSSU}$                       | Setup Time Data to <b>TCK</b> (Figure 14)                                                               | 10  |                        |     | ns                |

| $t_{JPSU}$                       | Setup Time <b>TDI, TMS</b> to <b>TCK</b> (Figure 14)                                                    | 10  |                        |     | ns                |

| $t_{JSH}$                        | Hold Time Data to <b>TCK</b> (Figure 14)                                                                | 45  |                        |     | ns                |

| $t_{JPH}$                        | Hold Time <b>TCK</b> to <b>TDI, TMS</b> (Figure 14)                                                     | 45  |                        |     | ns                |

(1) Timing specifications are tested at TTL logic levels,  $V_{IL} = 0.4V$  for a falling edge and  $V_{IH} = 2.4V$  for a rising edge.

(2) Typical figures are at  $T_A = 25^\circ C$  and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured. Test Limits are specified to TI's AOQL (Average Outgoing Quality Level).

## AC Electrical Characteristics (continued)

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = D18GND = 0V,  $V_A = V_D = V_{DR} = +3.3V$  ( $\pm 10\%$ ),  $V_{D18} = +1.8V$  ( $\pm 10\%$ ), Internal  $V_{REF} = +1.0V$ ,  $f_{CLK} = 65$  MHz,  $V_{CM} = V_{COM}$ ,  $t_R = t_F = 1$  ns,  $C_L = 5$  pF/pin. CIC Decimation = 48, F2 Decimation = 2. Typical values are for  $T_A = 25^\circ C$ . **Boldface limits apply for  $T_{MIN} \leq T_A \leq T_{MAX}$** . All other limits apply for  $T_A = 25^\circ C$ .<sup>(1)</sup>

| Symbol                          | Parameter ( $C_L=50pF$ )                                            | Min       | Typical <sup>(2)</sup> | Max       | Units |

|---------------------------------|---------------------------------------------------------------------|-----------|------------------------|-----------|-------|