**TENTATIVE**

TOSHIBA BIPOLAR LINEAR INTEGRATED CIRCUIT SILICON MONOLITHIC

# **TA8772AN**

PAL / SECAM / NTSC BASE BAND 1H DELAY SYSTEM FOR COLOR TV OR VCR

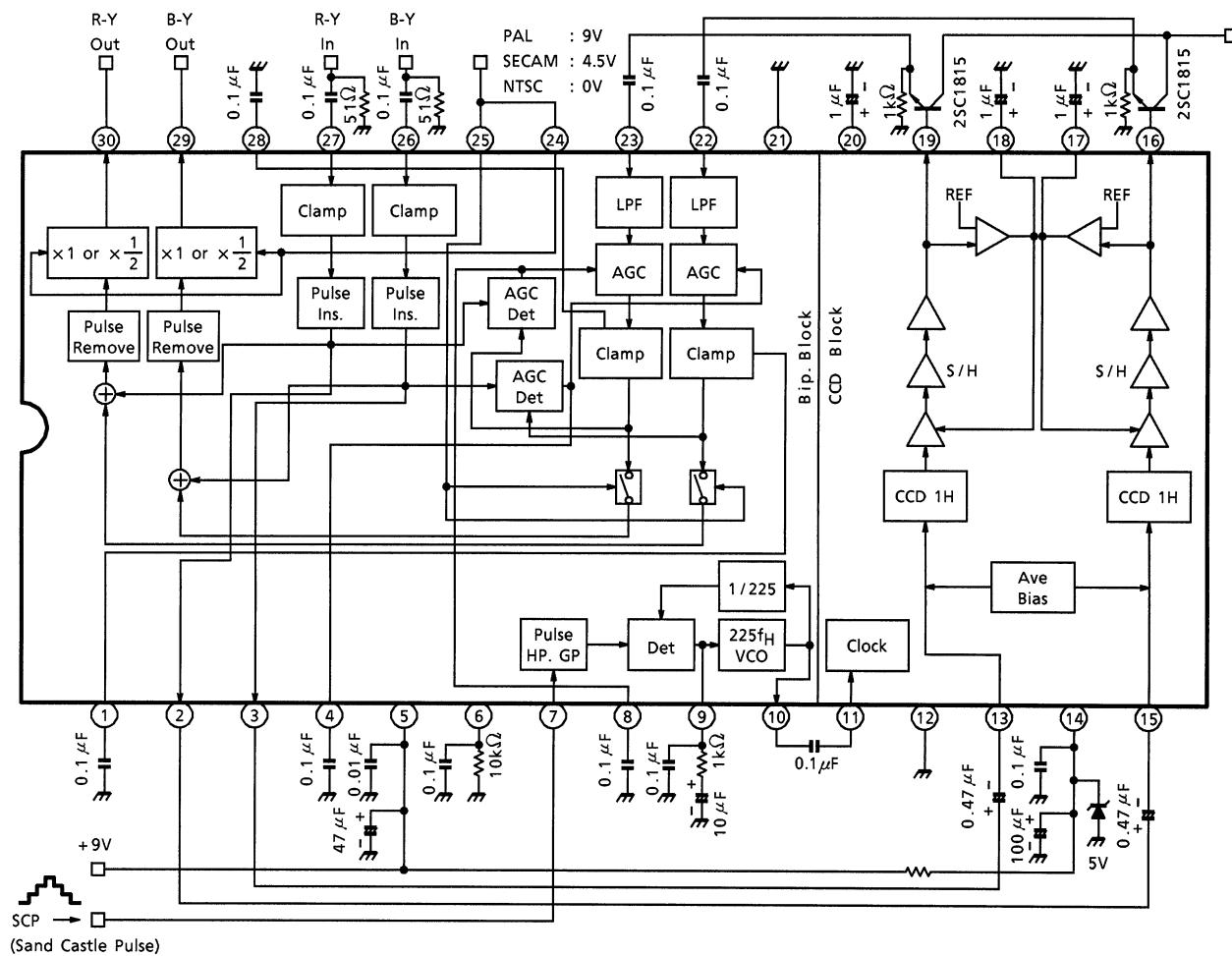

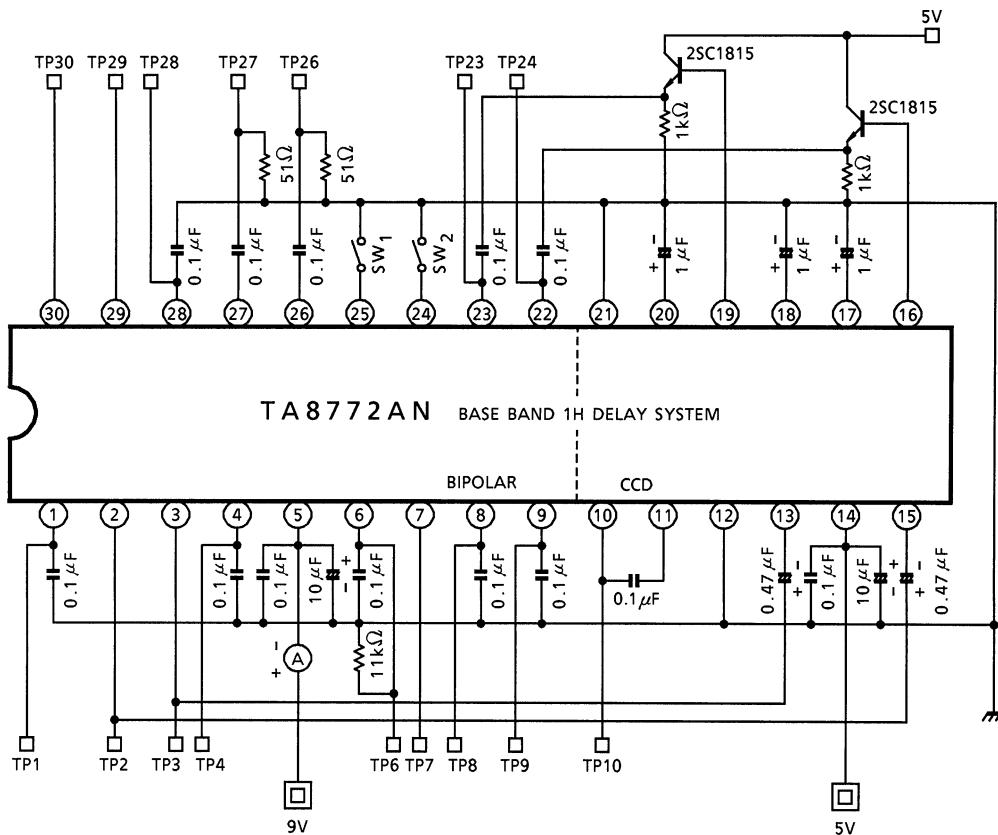

The TA8772AN has two chips, a bipolar chip and a CCD chip, in a package.

CCD chip consist of two delaylines which operate to delay R-Y and B-Y signal. Bipolar chip operate to control the signals which is processed by CCD stage.

## **FEATURES**

### **Bipolar stage**

- AGC circuit (For correcting output level)

- L.P.F. (For reducing CCD clock)

- DC clamp circuit (For reducing the difference of DC level between delay signal and direct signal.)

- Mode SW (For control output signal by PAL, NTSC or SECAM ident)

- 225fH VCO circuit (For making CCD clock)

### **CCD stage**

- CCD drive circuit

- Sample & Hold circuit

- Input bias circuit

- Sync tip clamp circuit (This device's dynamic range bear no relation to change of APL on adopt this circuit)

- Delay time of 1H consist of supply 225fH clock.

## **TOTAL**

- This device can operate by the smallest external parts because of include CCD drive circuit, bias generator circuit and output amplifier for support CCD circuit.

Weight: 1.99g (Typ.)

000707EBA1

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.

## BLOCK DIAGRAM

(Sand Castle Pulse)

## TERMINAL FUNCTION

| PIN No. | PIN NAME        | FUNCTION                                                                                    | INTERFACE CIRCUIT                                                                    | TERMINAL SIGNAL                                                                                                                       |

|---------|-----------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

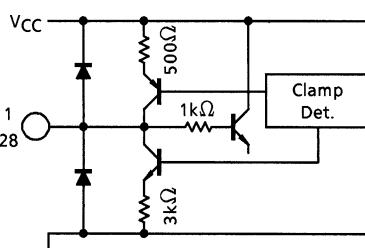

| 1       | R-Y Clamp Det.  | This is a terminal for detecting DC clamp level of R-Y signal.                              |    | DC 4.5V                                                                                                                               |

| 28      | B-Y Clamp Det.  | This is a terminal for detecting DC clamp level of R-Y signal.                              |                                                                                      |                                                                                                                                       |

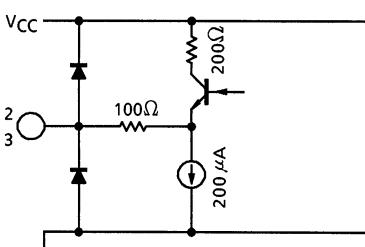

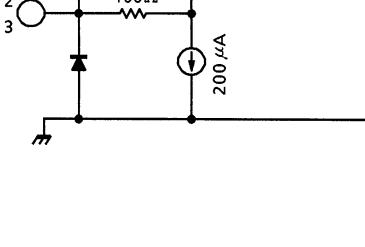

| 2       | R-Y to CCD      | This is output terminal of R-Y signal.<br>This terminal connects to pin 15 of CCD circuit.  |    | <br>160mV <sub>p-p</sub><br>A : 4.30V<br>B : 4.55V |

| 3       | B-Y to CCD      | This is output terminal of B-Y signal.<br>This terminal connects to pin 13 of CCD circuit.  |   | <br>180mV <sub>p-p</sub><br>A : 4.30V<br>B : 4.55V |

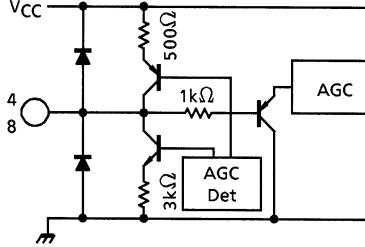

| 4       | R-Y AGC Det.    | This is terminal for detecting AGC.                                                         |  | DC 3.9V                                                                                                                               |

| 8       | B-Y AGC Det.    | This is terminal for detecting AGC.                                                         |  |                                                                                                                                       |

| 5       | V <sub>CC</sub> | This is power supply terminal for supplying 9V (Typ.) to bipolar circuit.                   | —                                                                                    | —                                                                                                                                     |

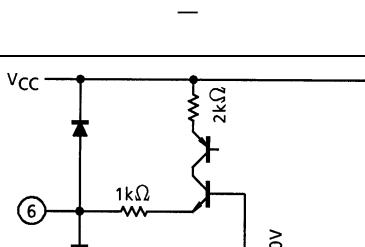

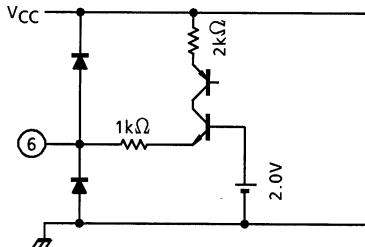

| 6       | Filter Adj.     | This terminal is connected to GND via 10kΩ. This is terminal for adjusting internal filter. |  | DC 1.3V                                                                                                                               |

| PIN No. | PIN NAME         | FUNCTION                                                                                           | INTERFACE CIRCUIT | TERMINAL SIGNAL                                    |

|---------|------------------|----------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------|

| 7       | S.C.P. In        | This is input terminal for S.C.P.                                                                  |                   | <br>A : 7.80V<br>B : 4.45V<br>C : 0.40V            |

| 9       | PLL Det.         | This terminal outputs result of phase comparison between internal VCO and horizontal input signal. |                   | DC 4.2V                                            |

| 10      | Clock            | This terminal outputs clock pulse which is used by CCD circuit.                                    |                   | <br>0.4V <sub>p-p</sub><br>DC 2.3V                 |

| 11      | Clock In         | This terminal receives clock pulse for CCD circuit.                                                |                   | <br>0.4V <sub>p-p</sub><br>DC 2.3V                 |

| 12      | V <sub>SS</sub>  | This terminal is V <sub>SS</sub> terminal for CCD circuit. Connect this terminal to GND.           | —                 | —                                                  |

| 13      | V <sub>IN1</sub> | This is input terminal of B-Y signal for CCD circuit                                               |                   | <br>180mV <sub>p-p</sub><br>A : 2.50V<br>B : 2.25V |

| 15      | V <sub>IN2</sub> | This is input terminal of B-Y signal for CCD circuit                                               |                   | <br>160mV <sub>p-p</sub><br>A : 2.50V<br>B : 2.25V |

| PIN No. | PIN NAME          | FUNCTION                                                                         | INTERFACE CIRCUIT | TERMINAL SIGNAL |

|---------|-------------------|----------------------------------------------------------------------------------|-------------------|-----------------|

| 14      | V <sub>DD</sub>   | This terminal is power supply terminal for supplying 5V (Typ.) to CCD circuit.   | —                 | —               |

| 16      | V <sub>OUT2</sub> | This terminal outputs delayed signal of R-Y.                                     |                   |                 |

| 19      | V <sub>OUT1</sub> | This terminal outputs delayed signal of B-Y.                                     |                   |                 |

| 17      | V <sub>OB2</sub>  | This terminal controls output DC level of pin 16.                                |                   | DC 1.5V         |

| 18      | V <sub>OB1</sub>  | This terminal controls output DC level of pin 19.                                |                   | DC 1.5V         |

| 20      | V <sub>GG</sub>   | This terminal is applied V <sub>CC</sub> ×2 voltage by internal voltage booster. | —                 | DC 10.5V        |

| 21      | GND               | This terminal is GND terminal for bipolar circuit.                               | —                 | —               |

| 22      | R-Y from CCD      | This is input terminal of delayed R-Y signal.                                    |                   |                 |

| 23      | B-Y from CCD      | This is input terminal of delayed B-Y signal.                                    |                   |                 |

| PIN No. | PIN NAME             | FUNCTION                                                                                                       | INTERFACE CIRCUIT                                                                    | TERMINAL SIGNAL                                                                                                              |

|---------|----------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

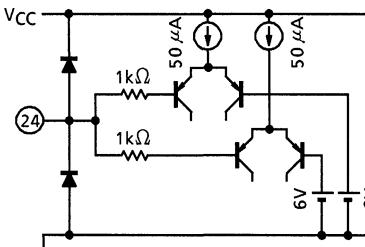

| 24      | MODE SW <sub>1</sub> | This terminal controls the gain of internal circuit for PAL, SECAM or NTSC.<br>Threshold level is 6V (Typ.).   |    | DC<br>PAL : 8.3V<br>SECAM : 4.6V<br>NTSC : 0.0V                                                                              |

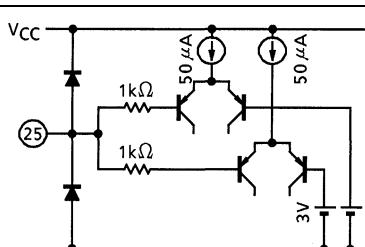

| 25      | MODE SW <sub>2</sub> | This terminal controls sw of calculator for delayed signal and direct signal.<br>Threshold level is 3V (Typ.). |    | DC<br>PAL : 8.3V<br>SECAM : 4.6V<br>NTSC : 0.0V                                                                              |

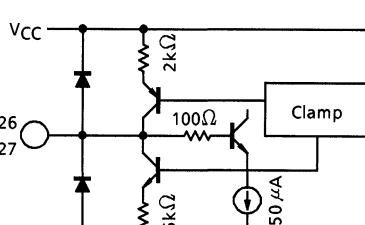

| 26      | B-Y In               | This is input terminal of B-Y signal.                                                                          |   | <br>350mV <sub>p-p</sub><br>DC : 5.25 V   |

| 27      | R-Y In               | This is input terminal of R-Y signal.                                                                          |  | <br>320mV <sub>p-p</sub><br>DC : 5.25 V |

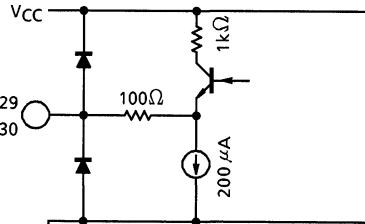

| 29      | B-Y Out              | This is output terminal of B-Y signal.                                                                         |  | <br>350mV <sub>p-p</sub><br>DC : 4.55 V |

| 30      | R-Y Out              | This is output terminal of R-Y signal.                                                                         |  | <br>320mV <sub>p-p</sub><br>DC : 4.55 V |

## MAXIMUM RATINGS (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL                            | RATING                                                            | UNIT             |

|-----------------------|-----------------------------------|-------------------------------------------------------------------|------------------|

| Power Supply Voltage  | V <sub>CC</sub> / V <sub>DD</sub> | 12 / 6                                                            | V                |

| Power Dissipation     | P <sub>D</sub> (Note)             | 1.6                                                               | W                |

| Operating Temperature | T <sub>opr</sub>                  | -20~65                                                            | °C               |

| Storage Temperature   | T <sub>stg</sub>                  | -55~150                                                           | °C               |

| Input Signal Voltage  | e <sub>in</sub>                   | 0.8                                                               | V <sub>p-p</sub> |

| Terminal Voltage      | V <sub>in</sub> / CCD             | GND - 0.3~V <sub>CC</sub> + 0.3 / GND - 0.3~V <sub>DD</sub> + 0.3 | V                |

Note: When using the device at above Ta = 25°C, decrease the power dissipation by 12.8mW for each increase of 1°C.

## RECOMMENDED OPERATING CONDITION

| PIN No. | PIN NAME               | MIN  | TYP. | MAX  | UNIT |

|---------|------------------------|------|------|------|------|

| 5       | V <sub>CC</sub> (Bip.) | 8.1  | 9.0  | 9.9  | V    |

| 14      | V <sub>DD</sub> (CCD)  | 4.75 | 5.0  | 5.25 | V    |

## ELECTRICAL CHARACTERISTICS

## DC characteristics

Bipolar electrical characteristics (Unless otherwise specified, V<sub>CC</sub> = 9V, Ta = 25°C)

| CHARACTERISTIC       | SYMBOL            | TEST CIR-CUIT    | TEST CONDITION | MIN    | TYP.  | MAX   | UNIT |

|----------------------|-------------------|------------------|----------------|--------|-------|-------|------|

| Power Supply Current | I <sub>CC</sub>   | —                | (Note B1)      | 17.7   | 25.0  | 32.3  | mA   |

| Terminal Voltage     | Pin 1             | V <sub>1</sub>   | (Note B2)      | 3.95   | 4.50  | 5.05  | V    |

|                      | Pin 2             | V <sub>2</sub>   | (Note B2)      | 4.28   | 4.50  | 4.72  |      |

|                      | Pin 3             | V <sub>3</sub>   | (Note B2)      | 4.28   | 4.50  | 4.72  |      |

|                      | Pin 4             | V <sub>4</sub>   | (Note B3)      | 2.85   | 4.50  | 6.15  |      |

|                      | Pin 6             | V <sub>6</sub>   | (Note B4)      | 1.157  | 1.300 | 1.443 |      |

|                      | Pin 8             | V <sub>8</sub>   | (Note B3)      | 2.85   | 4.50  | 6.15  |      |

|                      | Pin 9             | V <sub>9</sub>   | (Note B4)      | 1.82   | 2.15  | 2.48  |      |

|                      | Pin 10            | V <sub>10</sub>  | (Note B4)      | 1.82   | 2.15  | 2.48  |      |

|                      | Pin 22            | V <sub>22</sub>  | (Note B5)      | 4.28   | 4.50  | 4.72  |      |

|                      | Pin 23            | V <sub>23</sub>  | (Note B5)      | 4.28   | 4.50  | 4.72  |      |

|                      | Pin 26            | V <sub>26</sub>  | (Note B2)      | 4.98   | 5.20  | 5.42  |      |

|                      | Pin 27            | V <sub>27</sub>  | (Note B2)      | 4.98   | 5.20  | 5.42  |      |

|                      | Pin 28            | V <sub>28</sub>  | (Note B2)      | 3.95   | 4.50  | 5.05  |      |

|                      | Pin 29            | V <sub>29</sub>  | (Note B6)      | 4.28   | 4.50  | 4.72  |      |

|                      | Pin 29 Difference | dV <sub>29</sub> | (Note B6)      | -0.005 | 0     | 0.005 |      |

|                      | Pin 30            | V <sub>30</sub>  | (Note B7)      | 4.28   | 4.50  | 4.72  |      |

|                      | Pin 30 Difference | dV <sub>30</sub> | (Note B7)      | -0.005 | 0     | 0.005 |      |

CCD DC electrical characteristics (Unless otherwise specified,  $V_{DD} = 5V$ ,  $T_a = 25^\circ C$ )

| CHARACTERISTIC       | SYMBOL   | TEST CIR-CUIT | TEST CONDITION | MIN | TYP. | MAX  | UNIT |

|----------------------|----------|---------------|----------------|-----|------|------|------|

| Power Supply Current | $I_{CC}$ | —             | (Note C1)      | 4.0 | 12.0 | 24.0 | mA   |

| Terminal Voltage     | Pin 11   | $V_{11}$      | (Note C2)      | 1.8 | 2.5  | 3.3  | V    |

|                      | Pin 13   | $V_{13}$      | (Note C2)      | 1.4 | 2.4  | 3.4  |      |

|                      | Pin 15   | $V_{15}$      | (Note C2)      | 1.4 | 2.4  | 3.4  |      |

|                      | Pin 16   | $V_{16}$      | (Note C2)      | 2.4 | 3.1  | 4.1  |      |

|                      | Pin 17   | $V_{17}$      | (Note C2)      | 0.5 | 1.3  | 2.1  |      |

|                      | Pin 18   | $V_{18}$      | (Note C2)      | 0.5 | 1.3  | 2.1  |      |

|                      | Pin 19   | $V_{19}$      | (Note C2)      | 2.4 | 3.1  | 4.1  |      |

|                      | Pin 20   | $V_{20}$      | (Note C2)      | 9.0 | 10.5 | 12.0 |      |

## AC characteristics

Bipolar electrical characteristics (Unless otherwise specified,  $V_{CC} = 9V$ ,  $T_a = 25^\circ C$ )

| CHARACTERISTIC                    | SYMBOL      | TEST CIR-CUIT | TEST CONDITION | MIN  | TYP.  | MAX  | UNIT      |

|-----------------------------------|-------------|---------------|----------------|------|-------|------|-----------|

| Input Dynamic Range               | B-Y in (26) | $D_{R1}$      | (Note B8)      | 1.3  | 1.4   | 1.5  | $V_{p-p}$ |

|                                   | R-Y in (27) | $D_{R2}$      |                |      |       |      |           |

| Linearity                         | B-Y in (26) | $L_{ty1}$     | (Note B10)     | 1    | -2.0  | 0.0  | 2.0       |

|                                   | R-Y in (27) | $L_{ty2}$     |                |      |       |      |           |

| Output Level                      | pin 2       | $V_{o1}$      | (Note B12)     | 1    | 0.39  | 0.40 | 0.41      |

|                                   | pin 3       | $V_{o2}$      |                |      |       |      |           |

| Pulse Insert Level                | pin 2       | $P_{IL1}$     | (Note B14)     | 1    | 0.225 | 0.25 | 0.275     |

|                                   | pin 3       | $P_{IL2}$     |                |      |       |      |           |

| RP Pulse Delay Time               | $R_{PD}$    | 1             | (Note B16)     | 0.00 | 0.70  | 1.00 | $\mu s$   |

| L.P.F. $f_0$ (1)                  | $F_{f01}$   | 1             | (Note B17)     | 1.50 | 1.60  | 1.70 | MHz       |

| L.P.F. $f_0$ (2)                  | $F_{f02}$   | 1             | (Note B18)     | 1.50 | 1.60  | 1.70 | MHz       |

| TRAP $f_0$ (1)                    | $T_{f01}$   | 1             | (Note B19)     | 3.20 | 3.40  | 3.55 | MHz       |

| TRAP $f_0$ (2)                    | $T_{f02}$   | 1             | (Note B20)     | 3.20 | 3.40  | 3.55 | MHz       |

| TRAP Attenuation Value 1          | $T_{at1}$   | 1             | (Note B21)     | —    | -40   | -30  | dB        |

| TRAP Attenuation Value 2          | $T_{at2}$   | 1             | (Note B22)     | —    | -40   | -30  | dB        |

| Input Impedance                   | Pin 22      | $Z_{i1}$      | (Note B23)     | 1    | 34.0  | 50.5 | 67.0      |

|                                   | Pin 23      | $Z_{i2}$      |                |      |       |      |           |

| SW <sub>1</sub> Threshold Voltage | $V_{th1}$   | 1             | (Note B25)     | 5.9  | 6.0   | 6.1  | V         |

| SW <sub>2</sub> Threshold Voltage | $V_{th2}$   | 1             | (Note B26)     | 2.9  | 3.0   | 3.1  | V         |

| VCO Center Frequency              | $f_{cen}$   | 1             | (Note B27)     | 2.45 | 3.50  | 4.60 | MHz       |

| VCO Max Oscillation Frequency     | $f_{max}$   | 1             | (Note B28)     | 3.75 | 4.80  | 6.00 | MHz       |

| VCO Min Oscillation Frequency     | $f_{min}$   | 1             | (Note B29)     | 1.00 | 2.20  | 3.30 | MHz       |

| CHARACTERISTIC                | SYMBOL                     | TEST CIR-CUIT | TEST CONDITION | MIN  | TYP. | MAX  | UNIT             |

|-------------------------------|----------------------------|---------------|----------------|------|------|------|------------------|

| VCO Freq. Control Sensitivity | $f_{\text{sen}}$           | 1             | (Note B30)     | 1.40 | 1.80 | 2.30 | kHz / V          |

| APC Pull in Range (+)         | $F_{\text{pp}}$            | 1             | (Note B31)     | 4.6  | 5.3  | —    | kHz              |

| APC Pull in Range (-)         | $F_{\text{pm}}$            | 1             | (Note B32)     | -4.6 | -5.3 | —    | kHz              |

| VCO Output Level              | $F_{\text{L}_{\text{ev}}}$ | 1             | (Note B33)     | 0.22 | 0.35 | 0.45 | V <sub>p-p</sub> |

| AGC Max Gain                  | $G_{\text{max}}$           | 1             | (Note B34)     | 6.5  | 7.5  | 9.5  | dB               |

| AGC Min Gain                  | $G_{\text{min}}$           | 1             | (Note B35)     | -5.5 | -3.5 | -2.5 | dB               |

| AGC Knee Level (+)            | $G_{\text{k}+}$            | 1             | (Note B36)     | 5.5  | 6.5  | —    | dB               |

| AGC Knee Level (-)            | $G_{\text{k}-}$            | 1             | (Note B37)     | —    | -6.5 | -5.5 | dB               |

| CLAMP DET (+)                 | $C_{\text{d}+}$            | 1             | (Note B38)     | -10  | 0    | 10   | mV               |

| CLAMP DET (-)                 | $C_{\text{d}-}$            | 1             | (Note B39)     | -10  | 0    | 10   | mV               |

| HP PULSE Threshold Voltage    | $H_{\text{Pth}}$           | 1             | (Note B40)     | 3.3  | 3.5  | 3.7  | V                |

| GP PULSE Threshold Voltage    | $G_{\text{Pth}}$           | 1             | (Note B41)     | 6.8  | 7.0  | 7.2  | V                |

CCD electrical characteristics (Unless otherwise specified, V<sub>DD</sub> = 5V, Ta = 25°C)

| CHARACTERISTIC           | SYMBOL                             | TEST CIR-CUIT     | TEST CONDITION | MIN       | TYP. | MAX  | UNIT |                   |  |

|--------------------------|------------------------------------|-------------------|----------------|-----------|------|------|------|-------------------|--|

| Input-Output Gain (*)    | $V_{\text{OUT1}} / V_{\text{IN1}}$ | $G_1$             | —              | (Note C3) | 1.8  | 4.0  | 6.2  | dB                |  |

|                          | $V_{\text{OUT2}} / V_{\text{IN2}}$ | $G_2$             |                |           |      |      |      |                   |  |

| Freq. Characteristic (*) | Pin 19                             | $f_{\text{ch1}}$  | —              | (Note C4) | -3.0 | -2.0 | -1.0 | dB                |  |

|                          | Pin 16                             | $f_{\text{ch2}}$  |                |           |      |      |      |                   |  |

| Output Impedance (*)     | Pin 19                             | $Z_{\text{o}1}$   | —              | (Note C5) | 150  | 300  | 450  | Ω                 |  |

|                          | Pin 16                             | $Z_{\text{o}2}$   |                |           |      |      |      |                   |  |

| Linearity                | REF Pulse Level                    | Pin 19            | —              | (Note C6) | 120  | 125  | 130  | %                 |  |

|                          |                                    | Pin 16            |                |           |      |      |      |                   |  |

|                          | LOW Pulse Level                    | Pin 19            | —              | (Note C6) | 95   | 100  | 105  |                   |  |

|                          |                                    | Pin 16            |                |           |      |      |      |                   |  |

|                          | HIGH Level                         | Pin 19            | —              | (Note C6) | 95   | 100  | 105  |                   |  |

|                          |                                    | Pin 16            |                |           |      |      |      |                   |  |

| Clock LeakageLevel       | Pin 19                             | $L_{\text{CLK1}}$ | —              | (Note C7) | —    | —    | 70.0 | mV <sub>rms</sub> |  |

|                          | Pin 16                             | $L_{\text{CHK2}}$ |                |           |      |      |      |                   |  |

\*: It is necessary that external bias voltage is added to input circuit when sine-wave is input. Please control external bias voltage so that input terminal voltage is 0.2V higher than no signal level.

## TEST CONDITION

Note: GP PULSE ON : Firstly, Apply SAND CASTLE PULSE to pin 7.

Then, Apply the voltage equal to GATE-PULSE level to pin 7.

RP PULSE ON : Firstly, Apply SAND CASTLE PULSE to pin 7.

Then, Apply the voltage equal to H-PULSE level to pin 7.

PULSE OFF : Firstly, Apply SAND CASTLE PULSE to pin 7. Then, Apply the voltage equal to LOW level to pin 7.

Note B1: Power Supply Current.

(1) Pin 7 : Pulse OFF.

(2) Measure the current that flow into IC.

Note B2: Pin 1~3, 26~28 Terminal Voltage.

(1) Pin 7 : GP Pulse ON.

(2) Measure the voltage of each terminals.

Note B3: Pin 4, 8 Terminal Voltage.

(1) Pin 7 : RP Pulse ON.

(2) Measure the voltage of each terminals.

Note B4: Pin 6, 9, 10 Terminal Voltage.

(1) Pin 7 : Pulse OFF.

(2) Measure the voltage of each terminals.

Note B5: Pin 22, 23 Terminal Voltage.

(1) Pin 7 : OPEN.

(2) Measure the voltage of each terminals.

Note B6: Pin 29 Terminal Voltage and Change.

(1) Pin7 : GP Pulse ON.

(2) Apply 0V to pin 24 (SW2 on).

(3) Apply 0V to pin 25 (SW1 on).

(4) Measure the voltage pin 29 (V<sub>29</sub>).

(5) Apply 0V to pin 24 (SW2 on).

(6) Apply 9V to pin 25 (SW2 off).

(7) Measure the voltage pin 29 (V<sub>29a</sub>).

(8) The voltage of pin 29 is V<sub>29</sub>.

(9) The voltage change at pin 29 is V<sub>29</sub> – V<sub>29a</sub>.

Note B7: Pin 30 terminal voltage and change.

(1) Pin 7 : GP Pulse ON.

(2) Apply 0V to pin 24 (SW2 on).

(3) Apply 0V to pin 25 (SW1 on).

(4) Measure the voltage pin 30 (V<sub>30</sub>).

(5) Apply 0V to pin 24 (SW2 on).

(6) Apply 9V to pin 25 (SW2 off).

(7) Measure the voltage pin 30 (V<sub>30a</sub>).

(8) The voltage of pin 29 is V<sub>30</sub>.

(9) The voltage change at pin 30 is V<sub>30</sub> – V<sub>30a</sub>.

Note B8: Pin 26 Input Dynamic Range.

(1) Pin 7 : Pulse OFF.

(2) Apply 100kHz sin curve signal to pin 26 with, 5.2V bias.

(3) Observe pin 3 with spectrum analyzer measure input signal amplitude when 3rd harmonic is -40dB against fundamental wave.

Note B9: Pin 27 Input Dynamic Range.

- (1) Pin 7 : Pulse OFF.

- (2) Apply 100kHz sin curve signal to pin 27 with, 5.2V bias.

- (3) Observe pin 2 with spectrum analyzer measure input signal amplitude when 3rd harmonic is -40dB against fundamental wave.

Note B10: Pin 26 Linearity

- (1) Pin 7 : Pulse OFF.

- (2) Measure  $V_{3a} - V_{3f}$  at condition mentioned in below table.

| Applied voltage to pin 26 | 4.70V    | 5.00V    | 5.05V    | 5.35V    | 5.50V    | 5.80V    |

|---------------------------|----------|----------|----------|----------|----------|----------|

| Measured voltage at pin 3 | $V_{3a}$ | $V_{3b}$ | $V_{3c}$ | $V_{3d}$ | $V_{3e}$ | $V_{3f}$ |

(3) Calculate followings.

- 1) Get the slopes.

$$G_1 = (V_{3b} - V_{3a}) \div 0.3$$

$$G_2 = (V_{3d} - V_{3c}) \div 0.3$$

$$G_3 = (V_{3f} - V_{3e}) \div 0.3$$

- 2) Get the linearity.

$$LN1 = 100 \times (G_1 - G_2) \div G_2$$

$$LN2 = 100 \times (G_2 - G_3) \div G_3$$

$$LN3 = 100 \times (G_3 - G_1) \div G_1$$

Note B11: Pin 27 Linearity.

- (1) Pin 7 : Pulse OFF.

- (2) Measure  $V_{2a} - V_{2f}$  at condition mentioned in below table.

| Applied voltage to pin 27 | 4.70V    | 5.00V    | 5.05V    | 5.35V    | 5.50V    | 5.80V    |

|---------------------------|----------|----------|----------|----------|----------|----------|

| Measured voltage at pin 2 | $V_{2a}$ | $V_{2b}$ | $V_{2c}$ | $V_{2d}$ | $V_{2e}$ | $V_{2f}$ |

(3) Calculate followings.

- 1) Get the slopes.

$$G_1 = (V_{2b} - V_{2a}) \div 0.3$$

$$G_2 = (V_{2d} - V_{2c}) \div 0.3$$

$$G_3 = (V_{2f} - V_{2e}) \div 0.3$$

- 2) Get the linearity.

$$LN1 = 100 \times (G_1 - G_2) \div G_2$$

$$LN2 = 100 \times (G_2 - G_3) \div G_3$$

$$LN3 = 100 \times (G_3 - G_1) \div G_1$$

Note B12: Pin 2 Output Level.

- (1) Pin 7 : Pulse OFF.

- (2) Apply 100kHz, 0.8V<sub>p-p</sub>, sine signal to pin 27 with, 5.2V bias.

- (3) Measure the output level of pin 2.

Note B13: Pin 3 Output Level.

- (1) Pin 7 : Pulse OFF.

- (2) Apply 100kHz, 0.8V<sub>p-p</sub>, sine signal to pin 26 with, 5.2V bias.

- (3) Measure the output level of pin 3.

Note B14: Pin 2 Pulse Ins. Level.

- (1) Pin 7 : Input Sand Castle Pulse.

- (2) Observe pin 2, Measure amplitude of pulse.

Note B15: Pin 3 Pulse Ins. Level.

- (1) Pin 7 : Input Sand Castle Pulse.

- (2) Observe pin 3, Measure amplitude of pulse.

Note B16: RP Pulse Delay Time.

- (1) Pin 7 : Input Sand Castle Pulse.

- (2) Observe pin 7 and 3, Measure the period from leading edge at pin 7 to trailing edge at pin 3.

Note B17: L.P.F.  $f_0$  (1)

- (1) Pin 7 : Input Sand Castle Pulse.

- (2) Apply 2.0V to pin 8.

- (3) Apply 4.5V to pin 28.

- (4) Pin 24 : OPEN.

- (5) Apply 9.0V to pin 25.

- (6) Input 0.8V<sub>p-p</sub> sin wave signal to pin 23, Measure frequency response at pin 29.

Note: Get the frequency when amplitude is -3dB against amplitude at 100kHz.

Note B18: L.P.F.  $f_0$  (2)

- (1) Pin 7 : Input Sand Castle Pulse.

- (2) Apply 4.5V to pin 1.

- (3) Apply 2.0V to pin 4.

- (4) Pin 24 : OPEN.

- (5) Apply 9.0V to pin 25.

- (6) Input 0.8V<sub>p-p</sub> sin wave signal to pin 23, Measure frequency response at pin 30.

Note: Get the frequency when amplitude is -3dB against amplitude at 100kHz.

Note B19: TRAP  $f_0$  (1)

- (1) Pin 7 : Input Sand Castle Pulse.

- (2) Apply 2.0V to pin 8.

- (3) Apply 4.5V to pin 28.

- (4) Pin 24 : OPEN.

- (5) Apply 9.0V to pin 25.

- (6) Input 0.8V<sub>p-p</sub> sin wave signal to pin 23, Measure frequency response at pin 29.

Note: Get the frequency at the TRAP.

Note B20: TRAP  $f_0$  (2)

- (1) Pin 7 : Input Sand Castle Pulse.

- (2) Apply 4.5V to pin 1.

- (3) Apply 2.0V to pin 4.

- (4) Pin 24 : OPEN.

- (5) Apply 9.0V to pin 25.

- (6) Input 0.8V<sub>p-p</sub> sin wave signal to pin 22, Measure frequency response at pin 30.

Note: Get the frequency at the TRAP.

## Note B21: TRAP Attenuation Value (1).

- (1) Pin 7 : Input Sand Castle Pulse.

- (2) Apply 2.0V to pin 8.

- (3) Apply 4.5V to pin 28.

- (4) Pin 24 : OPEN.

- (5) Apply 9.0V to pin 25.

- (6) Input 0.8V<sub>p-p</sub> sin wave signal to pin 23, Measure frequency response at pin 29.

Note: Get the level at 3.54MHz against level at 100kHz.

## Note B22: TRAP Attenuation (2)

- (1) Pin 7 : Input Sand Castle Pulse.

- (2) Apply 4.5V to pin 1.

- (3) Apply 2.0V to pin 4.

- (4) Pin 24 : OPEN.

- (5) Apply 9.0V to pin 25.

- (6) Input 0.8V<sub>p-p</sub> sin wave signal to pin 22, Measure frequency response at pin 30.

Note: Get the level at 3.54MHz against level at 100kHz.

## Note B23: Pin 22 Impedance.

- (1) Apply 4.6V to pin 22.

- (2) Measure the current that flows into pin 22. ( $I_{22a}$ )

- (3) Apply 5.0V to pin 22.

- (4) Measure the current that flows into pin 22. ( $I_{22b}$ )

- (5) Calculate impedance.  $400 / (I_{22b} - I_{22a})$

## Note B24: Pin 23 Impedance.

- (1) Apply 4.6V to pin 23.

- (2) Measure the current that flows into pin 23. ( $I_{23a}$ )

- (3) Apply 5.0V to pin 23.

- (4) Measure the current that flows into pin 23. ( $I_{23b}$ )

- (5) Calculate impedance.  $400 / (I_{23b} - I_{23a})$

Note B25:  $SW_1$  Threshold Voltage.

- (1) Pin 7 : Pulse OFF.

- (2) Pin 25 : OPEN.

- (3) Input 100kHz, 0.8V<sub>p-p</sub>, sine wave to pin 26 with, 5.2V bias.

- (4) Connect external voltage supply to pin 24 observe pin 29 with changing supply voltage, Measure the voltage of when output level is changed supply voltage to pin 24.

Note B26:  $SW_2$  Threshold Voltage.

- (1) Pin 7 : Pulse OFF.

- (2) Pin 24 : OPEN.

- (3) Input 100kHz, 0.8V<sub>p-p</sub>, sine wave to pin 23.

- (4) Apply 4.5V to pin 28.

- (5) Apply 4.5V to pin 8.

- (6) Connect external voltage supply to pin 25 observe pin 29 with changing supply voltage, Measure the voltage of when the signal appear at pin 29.

Note B27: VCO Free-run Frequency.

- (1) Pin 7 : Pulse OFF.

- (2) Measure the frequency of output signal at pin 10.

Note B28: VCO Max. Frequency.

- (1) Pin 7 : Pulse OFF.

- (2) Apply 3.0V to pin 9.

- (3) Measure the frequency of output signal at pin 10.

Note B29: VCO Min. Frequency.

- (1) Pin 7 : Pulse OFF.

- (2) Apply 3.0V to pin 9.

- (3) Measure the frequency of output signal at pin 10.

Note B30: Frequency Control Sensitivity.

- (1) Pin 7 : Pulse OFF.

- (2) Apply 4.2V to pin 9. ( $f_{10a}$ )

- (3) Measure the frequency of output signal at pin 10.

- (4) Apply 4.8V to pin 9. ( $f_{10b}$ )

- (5) Measure the frequency of output signal at pin 10.

- (6) Calculate frequency control sensitivity.  $(f_{10b} - f_{10a}) / 0.6$

Note B31: APC Pull-in Range (+)

- (1) Input 0.3V, 15.734kHz, 10 $\mu$ s pulse to pin 7.

- (2) Observe pin 9 contain AFC is locked.

- (3) Increase input frequency due to unlock APC. Then decrease input frequency measure the input frequency when APC is locked again. ( $f_{7a}$ )

- (4) Calculate pull-in frequency.  $(f_{7a} - 15.734\text{kHz})$

Note B32: APC Pull-in Range (-)

- (1) Input 0.3V, 15.734kHz, 10 $\mu$ s pulse to pin 7.

- (2) Observe pin 9 contain AFC is locked.

- (3) Increase input frequency due to unlock APC. Then decrease input frequency measure the input frequency when APC is locked again. ( $f_{7b}$ )

- (4) Calculate pull-in frequency.  $(f_{7b} - 15.734\text{kHz})$

Note B33: VCO Output Level.

- (1) Input Sand Castle Pulse to pin 7.

- (2) Measure amplitude of output signal at pin 10.

## Note B34: AGC Max. Gain.

- (1) Input Sand Castle Pulse to pin 7.

- (2) Pin 24 : OPEN.

- (3) Apply 9.0V to pin 25.

- (4) Apply 2.0V to pin 8.

- (5) Input 100kHz, sine wave signal, which is synchronized with  $f_H$ , to pin 23.

- (6) Observe pin 29, Measure input signal amplitude. At pin 23 when output signal amplitude is 0.8V<sub>p-p</sub> at pin 29. (V<sub>23a</sub>)

- (7) Calculate gain.  $G = 20\log(0.8 / V_{23a})$

## Note B35: AGC Min. Gain.

- (1) Input Sand Castle Pulse to pin 7.

- (2) Pin 24 : OPEN.

- (3) Apply 9.0V to pin 25.

- (4) Apply 7.0V to pin 8.

- (5) Input 100kHz, sine wave signal, which is synchronized with  $f_H$ , to pin 23.

- (6) Observe pin 29, Measure input signal amplitude. At pin 23 when output signal amplitude is 0.8V<sub>p-p</sub> at pin 29. (V<sub>23b</sub>)

- (7) Calculate gain.  $G = 20\log(0.8 / V_{23b})$

## Note B36: AGC Knee Level (+)

- (1) Input Sand Castle Pulse to pin 7.

- (2) Apply 9.0V to pin 24.

- (3) Apply 9.0V to pin 25.

- (4) Input 100kHz, sine wave signal, which is synchronized with  $f_H$ , to pin 26.

- (5) Connect pin 3 to pin 23 via amplifier.

- (6) Set the input level at pin 23 is 0.8V<sub>p-p</sub> by adjusting gain of amplifier.

- (7) Measure output signal at pin 29. (V<sub>29</sub>)

- (8) Measure input signal amplitude at pin 23 when the output signal amplitude at pin 29 is 0.5dB bigger than V<sub>29</sub> with adjusting gain of amplifier. (V<sub>23a</sub>)

- (9) Calculate knee level.  $20\log(V_{23a} / 0.8)$

## Note B37: AGC Knee Level (-)

- (1) Input Sand Castle Pulse to pin 7.

- (2) Apply 9.0V to pin 24.

- (3) Apply 9.0V to pin 25.

- (4) Input 100kHz, sine wave signal, which is synchronized with  $f_H$ , to pin 26.

- (5) Connect pin 3 to pin 23 via amplifier.

- (6) Set the input level at pin 23 is 0.8V<sub>p-p</sub> by adjusting gain of amplifier.

- (7) Measure output signal at pin 29. (V<sub>29</sub>)

- (8) Measure input signal amplitude at pin 23 when the output signal amplitude at pin 29 is -0.5dB bigger than V<sub>29</sub> with adjusting gain of amplifier. (V<sub>23b</sub>)

- (9) Calculate knee level.  $20\log(V_{23b} / 0.8)$

## Note B38: Clamp Det (+)

- (1) Pin 7 : GP Pulse ON.

- (2) Apply 2.0V to pin 8.

- (3) Apply 9.0V to pin 25.

- (4) Pin 24 : OPEN.

- (5) Apply 4.5V to pin 23.

- (6) Measure voltage at pin 29. (V<sub>29</sub>)

- (7) Apply 5.0V to pin 23.

- (8) Measure voltage at pin 29. (V<sub>29a</sub>)

- (9) Calculate voltage change.  $(V_{29a} - V_{29})$

## Note B39: Clamp Det (-)

- (1) Pin 7 : GP Pulse ON.

- (2) Apply 2.0V to pin 8.

- (3) Apply 9.0V to pin 25.

- (4) Pin 24 : OPEN.

- (5) Apply 4.5V to pin 23.

- (6) Measure voltage at pin 29. (V29)

- (7) Apply 4.0V to pin 23.

- (8) Measure voltage at pin 29. (V29b)

- (9) Calculate voltage change. (V29b – V29)

## Note B40: HP Pulse Threshold Voltage.

- (1) Input Sand Castle Pulse to pin 7.

- (2) Decrease H.BLK level until disappear normal pulse at pin 3. Then, Increase H.BLK level. Measure H.BLK level when normal pulse appear at pin 3.

## Note B41: GP Pulse Threshold Voltage.

- (1) Input Sand Castle Pulse to pin 7.

- (2) Decrease Gate-Pulse level until voltage at pin 26 isn't clamped to 5.2V, Then increase Gate-Pulse level. Measure Gate-Pulse level when voltage at pin 26 is clamped to 5.2V.

## Note C1: Power Supply Current.

- (1) Input  $f = 225f_H$ , Lev = 0.3V<sub>p-p</sub> signal to pin 11.

- (2) Pin 13 and 15 are no input. (S<sub>1</sub>, S<sub>2</sub> = b)

- (3) After 20s from (1), Measure the current from power supply.

## Note C2: Pin 11~20 Terminal Voltage.

- (1) Input  $f = 225f_H$ , Lev = 0.3V<sub>p-p</sub> signal to pin 11.

- (2) Pin 13 and 15 are no input. (S<sub>1</sub>, S<sub>2</sub> = b)

- (3) Measure the voltage at each pin.

## Note C3: Input-Output Gain.

- (1) Input  $f = 225f_H$ , Lev = 0.3V<sub>p-p</sub> signal to pin 11.

- (2) Apply external bias voltage to pin 13 and 15 so that the voltage at pin 13 and 15 are 0.2V higher than voltage when no input.

- (3) Input  $f = 15\text{kHz}$ , Lev = 0.3V<sub>p-p</sub> signal to pin 13 and 15. (S<sub>1</sub>, S<sub>2</sub> = c) (V<sub>IN</sub>)

- (4) Measure output signal amplitude at pin 16 and 19. (V<sub>OUT</sub>)

- (5) Calculate gain.

$$G_1 (G_2) = 20\log (V_{OUT} / V_{IN}) [\text{dB}]$$

## Note C4: Frequency Response

- (1) Input  $f = 225f_H$ , Lev = 0.3V<sub>p-p</sub> signal to pin 11.

- (2) Apply external bias voltage to pin 13 and 15 so that the voltage at pin 13 and 15 are 0.2V higher than voltage when no input.

- (3) Input  $f = 1.17\text{MHz}$ , Lev = 0.3V<sub>p-p</sub> signal to pin 13 and 15. (S<sub>1</sub>, S<sub>2</sub> = c) (V<sub>IN</sub>)

- (4) Measure output signal amplitude at pin 16 and 19. (V<sub>OUT</sub>)

- (5) Calculate gain.

$$G = 20\log (V_{OUT} / V_{IN}) [\text{dB}]$$

Calculate frequency response.

$$f_{ch1} (f_{ch2}) = G_1 (G_2) - G [\text{dB}]$$

## Note C5: Output Impedance.

- (1) Input  $f = 225f_H$ , Lev = 0.3V<sub>p-p</sub> signal to pin 11.

- (2) Apply external bias voltage to pin 13 and 15 so that the voltage at pin 13 and 15 are 0.2V higher than voltage when no input.

- (3) Input  $f = 15\text{kHz}$ , Lev = 0.3V<sub>p-p</sub> signal to pin 13 and 15. (S<sub>1</sub>, S<sub>2</sub> = c)

- (4) Measure output level (15KHz component) at pin 16 and 19. (V<sub>outa</sub>)

- (5) Measure output level (15KHz component) with load at pin 16 and 19. (V<sub>outb</sub>)

- (6) Calculate output impedance.

$$Z_{o1} (Z_{o2}) = (10 \frac{V_{outa} - V_{outb}}{20} - 1) \times 300 [\Omega]$$

## Note C6: Linearity

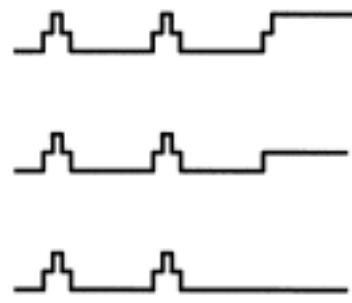

- (1) Input  $f = 225fH$ , Lev = 0.3V<sub>p-p</sub> signal to pin 11.

- (2) Input 4 step signal to pin 13 and 15. (S<sub>1</sub>, S<sub>2</sub> = c)

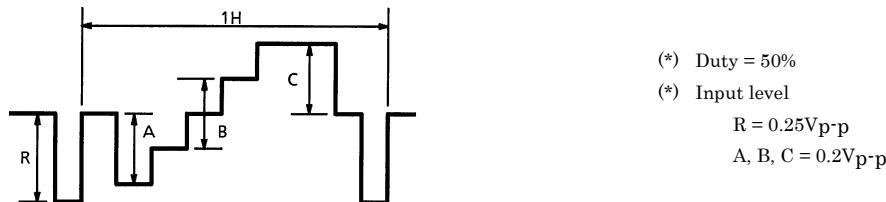

## &lt;Input Signal&gt;

- (3) Measure output signal (R, A, B, C) amplitude at pin 16 and 19.

- (4) Calculate linearity

$$V_{rpl1} (V_{rpl2}) = \frac{R}{A} \times 100 [\%] \quad V_{HL1} (V_{HL2}) = \frac{C}{A} \times 100 [\%]$$

$$V_{LL1} (V_{LL2}) = \frac{B}{A} \times 100 [\%]$$

## Note C7: Clock Leak

- (1) Input  $f = 225fH$ , Lev = 0.3V<sub>p-p</sub> signal to pin 11.

- (2) Pin 13 and 15 are no input. (S<sub>1</sub>, S<sub>2</sub> = b)

- (3) Measure clock level (225fH component) with spectrum analyzer at pin 11. (V<sub>in</sub> [dB])

- (4) Measure clock level (225fH component) with spectrum analyzer at pin 16 and 19. (V<sub>out</sub> [dB])

- (6) Measure clock leak.

$$\text{CLOCK LEAK (Lclk1 / Lclk2)} = 10 \frac{V_{out} - V_{in}}{20} \times 300 \times \frac{1}{2\sqrt{2}} [\text{mVrms}]$$

## TEST CIRCUIT

## ATTENTION FOR HANDLING

The input and output terminal is high impedance when this IC is not mounted. So, It is necessary that you must protect it from external electronical stress.

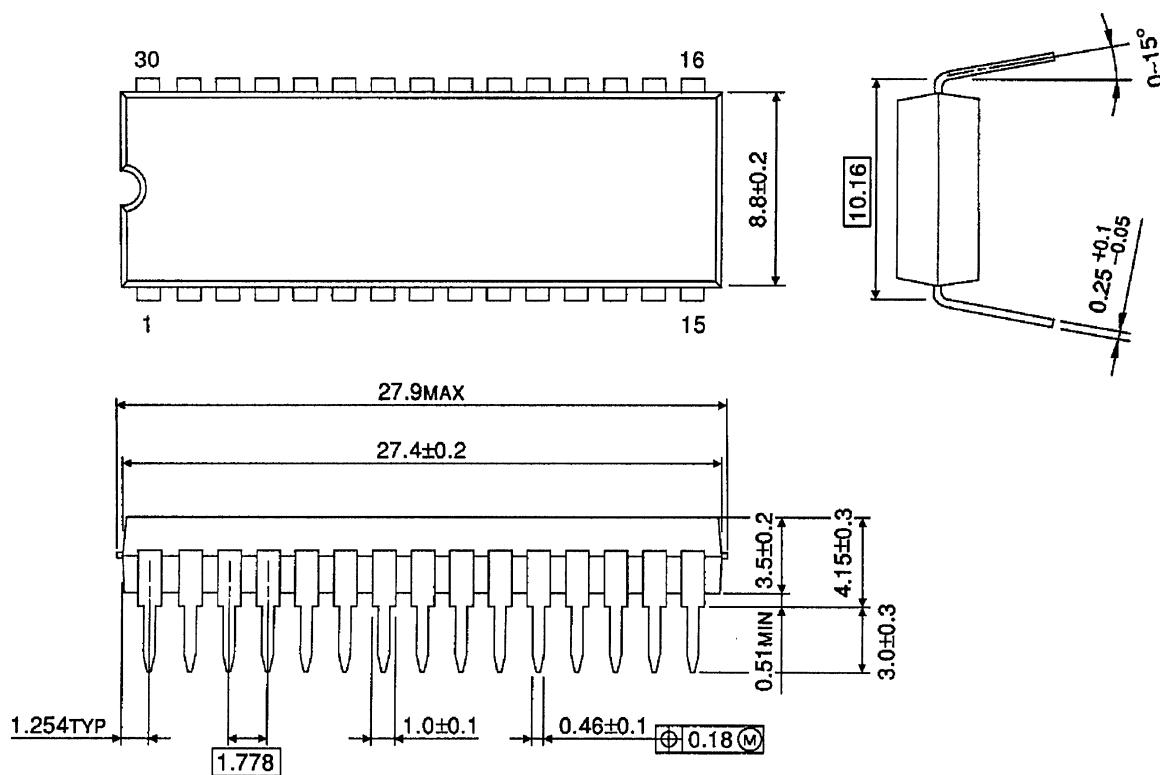

**PACKAGE DIMENSIONS**

SDIP30-P-400-1.78

Unit: mm

Weight: 1.99g (Typ.)