# Automotive Dual Full Bridge Driver

## **Features and Benefits**

- Two full bridge power outputs

- Typical application up to  $\pm 800$  mA, 28 V

- Adjustable peak current limit control

- Minimum overcurrent shutdown at 1.4 A

- Continuous operation at high ambient temperature

- Synchronous rectification for low power dissipation

- Simple parallel interface control

- · Inverted and non-inverted inputs

- No crossover current

- Low current consumption in sleep mode

- Error flag diagnostics

- Open load diagnostic during on-state for all outputs

- Outputs protected against overcurrent

- Overtemperature protection with hysteresis

Continued on the next page...

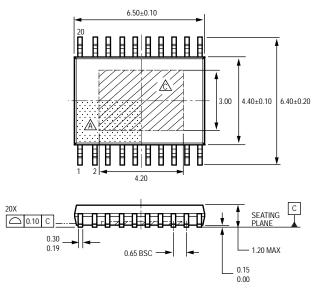

# Package: 20-pin TSSOP with exposed thermal pad (suffix LP)

## **Description**

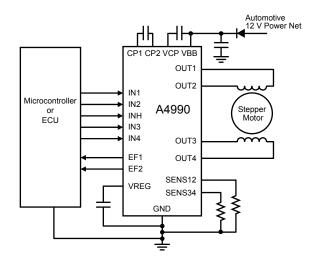

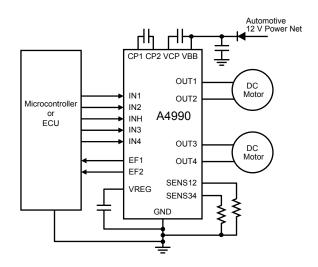

The A4990 is a dual full-bridge driver for stepper motors and small brush DC motors in automotive applications. Each full bridge uses DMOS power devices with integrated freewheeling diodes. Control circuits prevent cross-conduction, or shootthrough, when switching between high-side and low-side drives.

This device drives stepper motors with full current in either direction in each phase, allowing two-phase on, full-step operation. It drives DC motors in both directions and has brake capability. A single input turns-off both bridges, allowing motors to coast. All control modes can easily be achieved using 3, 4, or 5 outputs from a standard parallel interface of a microcontroller.

The peak motor current can be limited by sense resistor selection, providing higher efficiency, reduced motor heating, and longer motor life.

The outputs are protected from short circuits to supply and to ground, and low load-current detection is included. Chip level protection includes: overtemperature shutdown, and overvoltage and undervoltage lockout.

The A4990 is supplied in a 20-lead TSSOP power package with an exposed thermal pad (package type LP). This package is lead (Pb) free with 100% matte-tin lead frame plating.

# **Typical Applications**

## Features and Benefits (continued)

- Overvoltage and undervoltage lockout

- 3.3 V / 5 V compatible inputs with hysteresis

- Thermally enhanced package (exposed pad)

- Fully integrated in a compact TSSOP package for space sensitive applications

#### **Selection Guide**

| ocicotion oaiac |                                |                                                                              |  |  |

|-----------------|--------------------------------|------------------------------------------------------------------------------|--|--|

| Part Number     | Packing                        | Package                                                                      |  |  |

| A4990KLPTR-T    | 4000 pieces per<br>13-in. reel | 4.4 mm × 6.5 mm, 1.2 mm nominal height 20-pin TSSOP with exposed thermal pad |  |  |

## Absolute Maximum Ratings with respect to ground

| Characteristic                | Symbol               | Notes                                                                                                                                      | Rating                      | Unit |

|-------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|

| Load Supply Voltage           | V <sub>BB</sub>      |                                                                                                                                            | -0.3 to 50                  | V    |

| CP1 Pin                       |                      |                                                                                                                                            | –0.3 to V <sub>BB</sub>     | V    |

| CP2, VCP Pin                  |                      |                                                                                                                                            | -0.3 to V <sub>BB</sub> + 8 | V    |

| OUT1, OUT2, OUT3, OUT4 Pins   |                      |                                                                                                                                            | –0.3 to V <sub>BB</sub>     | V    |

| IN1, IN2, IN3, IN4 Pins       |                      |                                                                                                                                            | -0.3 to 6                   | V    |

| VREG Pin                      |                      |                                                                                                                                            | -0.3 to 8.5                 | V    |

| INH Pin                       |                      |                                                                                                                                            | -0.3 to 6                   | V    |

| EF1, EF2 Pins                 |                      |                                                                                                                                            | -0.3 to 6                   | V    |

| SENS12, SENS34 Pins           |                      |                                                                                                                                            | -0.3 to 1                   | V    |

| Operating Ambient Temperature | T <sub>A</sub>       | L temperature range, limited by power dissipation                                                                                          | -40 to 150                  | °C   |

|                               |                      | Continuous                                                                                                                                 | 150                         | °C   |

| laximum Junction Temperature  | T <sub>J</sub> (max) | Single overtemperature event not exceeding 10 s, cumulative lifetime duration not exceeding 10 hours, specified by design characterization | 175                         | °C   |

| Storage Temperature           | T <sub>stg</sub>     |                                                                                                                                            | -55 to 150                  | °C   |

# Thermal Characteristics may require derating at maximum conditions, see application information

| Characteristic                                | Symbol               | Test Conditions*                                                 |    | Unit |

|-----------------------------------------------|----------------------|------------------------------------------------------------------|----|------|

| Package Thermal Resistance                    | $R_{	heta JA}$       | Estimated, on Package LH, on 4-layer PCB based on JEDEC standard | 31 | °C/W |

| Junction to Ambient)                          | $\kappa_{\theta JA}$ | Estimated, on 2-layer PCB with 3.8 in.2 of copper area each side | 38 | °C/W |

| Package Thermal Resistance (Junction to Case) | $R_{	heta JC}$       | Estimated                                                        | 2  | °C/W |

<sup>\*</sup>Additional thermal information available on the Allegro website.

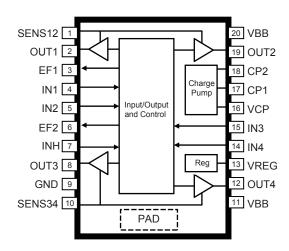

# **Pin-out Diagram**

#### **Terminal List Table**

| Number | Name   | Function                                             |

|--------|--------|------------------------------------------------------|

| CP1    | 17     | Charge pump capacitor                                |

| CP2    | 18     | Charge pump capacitor                                |

| EF1    | 3      | Error flag 1                                         |

| EF2    | 6      | Error flag 2                                         |

| GND    | 9      | Ground                                               |

| IN1    | 4      | Bridge control input 1, phase A                      |

| IN2    | 5      | Bridge control input 2, phase A                      |

| IN3    | 15     | Bridge control input 3, phase B                      |

| IN4    | 14     | Bridge control input 4, phase B                      |

| INH    | 7      | Drive disable input, active low                      |

| OUT1   | 2      | Bridge output 1, phase A                             |

| OUT2   | 19     | Bridge output 2, phase A                             |

| OUT3   | 8      | Bridge output 3, phase B                             |

| OUT4   | 12     | Bridge output 4, phase B                             |

| PAD    | _      | Exposed thermal pad for enhanced thermal dissipation |

| SENS12 | 1      | Current sense node, phase A bridge                   |

| SENS34 | 10     | Current sense node, phase B bridge                   |

| VBB    | 11, 20 | Motor supply voltage                                 |

| VCP    | 16     | Pump storage capacitor                               |

| VREG   | 13     | Regulated voltage                                    |

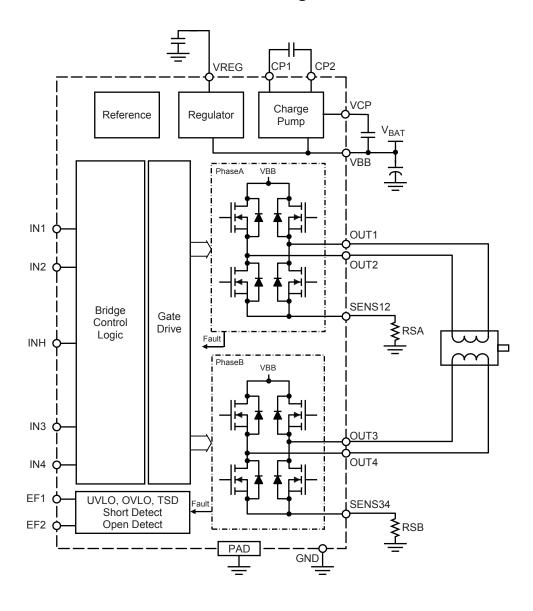

# **Functional Block Diagram**

**ELECTRICAL CHARACTERISTICS** Valid at  $T_J = -40^{\circ}\text{C}$  to 150°C,  $V_{BB} = 7$  to 28 V; unless otherwise specified

| Characteristic                                      | Symbol                | Test Conditions                                                                 | Min. | Тур.                  | Max.              | Unit |

|-----------------------------------------------------|-----------------------|---------------------------------------------------------------------------------|------|-----------------------|-------------------|------|

| Supplies                                            |                       |                                                                                 |      |                       |                   |      |

| Lood Cumply Voltage Dengel                          | V <sub>BB(func)</sub> | Functional, no unsafe states                                                    | 0    | _                     | 50                | V    |

| Load Supply Voltage Range <sup>1</sup>              | V <sub>BB(op)</sub>   | Outputs driving                                                                 | 6    | _                     | V <sub>BBOV</sub> | V    |

| Load Supply Quippont Current                        |                       | INH = high, IN1 = IN3 = low, IN2 = IN4 = high                                   | -    | 7                     | 10                | mA   |

| Load Supply Quiescent Current                       | I <sub>BBQ</sub>      | INH < 0.5 V, sleep mode                                                         | -    | 1                     | 5                 | μA   |

| Charge Pump Voltage                                 | V <sub>CP</sub>       | V <sub>BB</sub> > 7.5 V, INH = high                                             | _    | V <sub>BB</sub> + 6.7 | ı                 | V    |

| Internal Regulator Voltage                          | V <sub>REG</sub>      | INH = high, V <sub>BB</sub> > 7.5 V                                             | _    | 7.2                   | ı                 | V    |

| Internal Regulator Dropout Voltage                  | V <sub>REGDO</sub>    | INH = high, V <sub>BB</sub> > 5.6 V                                             | _    | 100                   | 200               | mV   |

| Motor Bridge Output                                 |                       |                                                                                 |      |                       |                   |      |

|                                                     |                       | $V_{BB} = 13.5 \text{ V}, I_{OUT} = -1 \text{ A}, T_{J} = 25^{\circ}\text{C}$   | _    | 500                   | 600               | mΩ   |

| High-Side On-Resistance <sup>2</sup>                | R <sub>DS(on)H</sub>  | $V_{BB} = 13.5 \text{ V}, I_{OUT} = -1 \text{ A}, T_{J} = 150 ^{\circ}\text{C}$ | _    | 900                   | 1100              | mΩ   |

|                                                     |                       | $V_{BB} = 7 \text{ V}, I_{OUT} = -1 \text{ A}, T_{J} = 25^{\circ}\text{C}$      | _    | 625                   | 750               | mΩ   |

| High-Side Body Diode Forward Voltage                | $V_{fH}$              | I <sub>f</sub> = 1 A                                                            | _    | _                     | 1.4               | V    |

|                                                     | R <sub>DS(on)L</sub>  | V <sub>BB</sub> = 13.5 V, I <sub>OUT</sub> = 1 A, T <sub>J</sub> = 25°C         | _    | 500                   | 600               | mΩ   |

| Low-Side On-Resistance                              |                       | V <sub>BB</sub> = 13.5 V, I <sub>OUT</sub> = 1 A, T <sub>J</sub> = 150°C        | _    | 900                   | 1100              | mΩ   |

|                                                     |                       | V <sub>BB</sub> = 7 V, I <sub>OUT</sub> = 1 A, T <sub>J</sub> = 25°C            | _    | 625                   | 750               | mΩ   |

| Low-Side Body Diode Forward Voltage <sup>2</sup>    | $V_{fL}$              | I <sub>f</sub> = -1 A                                                           | _    | _                     | 1.4               | V    |

| Dead Time                                           | t <sub>DEAD</sub>     |                                                                                 | _    | 500                   | _                 | ns   |

|                                                     |                       | INH = high, V <sub>OUT</sub> = V <sub>BB</sub>                                  | -120 | -65                   | _                 | μΑ   |

| Output Lookaga Current?                             |                       | INH = high, V <sub>OUT</sub> = 0 V                                              | -200 | -120                  | -                 | μA   |

| Output Leakage Current <sup>2</sup>                 | I <sub>OUT(lkg)</sub> | INH = low, V <sub>OUT</sub> = V <sub>BB</sub>                                   | _    | <1.0                  | 20                | μA   |

|                                                     |                       | INH = low, V <sub>OUT</sub> = 0 V                                               | -20  | <1.0                  | ı                 | μA   |

| Current Limit                                       |                       |                                                                                 |      |                       |                   |      |

| Internal Oscillator Frequency                       | f <sub>OSC</sub>      |                                                                                 | 3.2  | 4                     | 4.8               | MHz  |

| Blank Time                                          | t <sub>BLANK</sub>    |                                                                                 | 2800 | 3500                  | 4200              | ns   |

| PWM Frequency                                       | f <sub>PWM</sub>      |                                                                                 | 17.3 | 21.7                  | 26                | kHz  |

| Internal Reference Voltage                          | V <sub>REF</sub>      |                                                                                 | 1.1  | 1.2                   | 1.3               | V    |

| Maximum Sense Voltage                               | V <sub>SMAX</sub>     |                                                                                 | _    | 125                   | _                 | mV   |

| Current Trip Point Error <sup>3</sup>               | Err <sub>ITrip</sub>  |                                                                                 | _    | _                     | ±10               | %    |

| Logic Input and Output                              |                       |                                                                                 |      |                       |                   |      |

| Logic Input Low Voltage                             | V <sub>IL</sub>       |                                                                                 | _    | _                     | 0.8               | V    |

| Logic Input Low Voltage for Sleep<br>Mode (INH pin) | V <sub>ILS</sub>      |                                                                                 | _    | -                     | 0.5               | V    |

| Logic Input High Voltage                            | V <sub>IH</sub>       |                                                                                 | 2.0  | -                     | _                 | V    |

| Logic Input Hysteresis                              | V <sub>Ihys</sub>     |                                                                                 | 100  | 300                   | -                 | mV   |

Continued on the next page...

# **ELECTRICAL CHARACTERISTICS** Valid at $T_J = -40$ °C to 150°C, $V_{BB} = 7$ to 28 V; unless otherwise specified

| Characteristic                                           | Symbol               | Test Conditions                                | Min. | Тур. | Max. | Unit |  |  |  |

|----------------------------------------------------------|----------------------|------------------------------------------------|------|------|------|------|--|--|--|

| Logic Input and Output (continued)                       |                      |                                                |      |      |      |      |  |  |  |

| Logic Input Pull-Down Current (IN1,IN3, INH pins)        | I <sub>PD</sub>      | IN1 = IN3 = INH = 2 V                          | 10   | 25   | 50   | μA   |  |  |  |

| Logic Input Pull-Up Current (IN2, IN4 pins) <sup>2</sup> | I <sub>PU</sub>      | IN2 = IN4 = 0.8 V                              | -10  | -25  | -50  | μΑ   |  |  |  |

| Logic Output Low Voltage (EF1, EF2 pins)                 | V <sub>OL</sub>      | EF1 = EF2 = 2 mA                               | -    | 0.2  | 0.4  | V    |  |  |  |

| Logic Output Leakage <sup>2</sup>                        | I <sub>O(lkg)</sub>  | 0 V < V <sub>O</sub> < V <sub>DD</sub>         | -1   | _    | 1    | μA   |  |  |  |

| Logic Input Pulse Filter Time (IN1, IN2, IN3, IN4 pins)  | t <sub>PIN</sub>     |                                                | _    | 80   | _    | ns   |  |  |  |

| Sleep Mode Delay                                         | t <sub>SLEEP</sub>   | From INH going low until sleep mode            | _    | 300  | -    | μs   |  |  |  |

| Wake-up from Reset                                       | t <sub>EN</sub>      |                                                | _    | _    | 2    | ms   |  |  |  |

| Diagnostics and Protection                               |                      |                                                |      |      |      |      |  |  |  |

| VBB Overvoltage Turn-Off Voltage                         | V <sub>BBOV</sub>    | V <sub>BB</sub> rising                         | 32   | 34   | 36   | V    |  |  |  |

| VBB Overvoltage Hysteresis                               | V <sub>BBOVhys</sub> |                                                | 2    | _    | 4    | V    |  |  |  |

| VBB Undervoltage Threshold                               | V <sub>BBUV</sub>    | V <sub>BB</sub> falling                        | 5.2  | 5.5  | 5.8  | V    |  |  |  |

| VBB Undervoltage Hysteresis                              | V <sub>BBhys</sub>   |                                                | 500  | 760  | -    | mV   |  |  |  |

| VREG Undervoltage Threshold                              | V <sub>REGUV</sub>   | V <sub>REG</sub> falling                       | 4.6  | 4.8  | 4.95 | V    |  |  |  |

| VREG Undervoltage Hysteresis                             | VREGhys              |                                                | 250  | 370  | -    | mV   |  |  |  |

| High-Side Overcurrent Threshold                          | I <sub>OCH</sub>     | Sampled after t <sub>SCT</sub>                 | 1.4  | 2.05 | 2.65 | А    |  |  |  |

| High-Side Current Limit                                  | I <sub>LIMH</sub>    | Active during t <sub>SCT</sub>                 | 3    | 5.5  | 8    | Α    |  |  |  |

| Low-Side Overcurrent Sense Voltage                       | V <sub>OCL</sub>     | Sampled after t <sub>SCT</sub>                 | 210  | 250  | 290  | mV   |  |  |  |

| Overcurrent Fault Delay                                  | t <sub>SCT</sub>     |                                                | 1500 | 2000 | 2700 | ns   |  |  |  |

| Open Load Current                                        | I <sub>OLP</sub>     |                                                | 6    | 12   | 20   | mA   |  |  |  |

| Open Load Fault Delay                                    | t <sub>dOLP</sub>    |                                                | 717  | 896  | 1075 | μs   |  |  |  |

| Overtemperature Shutdown                                 | T <sub>JF</sub>      | Temperature increasing                         | 155  | 170  | -    | °C   |  |  |  |

| Overtemperature Hysteresis                               | T <sub>Jhys</sub>    | Recovery = T <sub>JF</sub> - T <sub>Jhys</sub> | _    | 15   | -    | °C   |  |  |  |

$<sup>^{1}</sup>V_{BB(func)}$  function is correct but parameters may not meet specification when 7 V > V<sub>BB</sub> or V<sub>BB</sub> > 28 V. Outputs not operational above V<sub>BBOV</sub> or below V<sub>REGUVL</sub>.  $^{2}$ For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

$<sup>^3</sup>$ Current Trip Point Error is the difference between the actual current trip point and the target current trip point, referred to maximum full scale (100%) current:  $Err_{Trip} = 100 \times (I_{TripActual} - I_{TripTarget}) / I_{FullScale}$  (%).

**Table 1. Functional Truth Table**

| Input/Output          |         |     |      |      | Functional State        |                         |                              |  |  |  |  |

|-----------------------|---------|-----|------|------|-------------------------|-------------------------|------------------------------|--|--|--|--|

|                       | Phase A |     |      |      |                         |                         |                              |  |  |  |  |

| INH                   | IN1     | IN2 | OUT1 | OUT2 | Mode                    | Stepper Motor Operation | DC Motor Operation           |  |  |  |  |

| L                     | Х       | Х   | Z    | Z    | Sleep                   | Low current consumption | Low current consumption      |  |  |  |  |

| Н                     | Z       | Z   | L    | L    | Brake: low side         | No phase current        | Low-side brake               |  |  |  |  |

| Н                     | L       | L   | L    | Н    | Current driven negative | Negative phase current  | Motor turns counterclockwise |  |  |  |  |

| Н                     | L       | Н   | L    | L    | Low-side recirculation  | No current              | Low-side brake               |  |  |  |  |

| Н                     | Н       | L   | Н    | Н    | High-side recirculation | No current              | High-side brake              |  |  |  |  |

| Н                     | Н       | Н   | Н    | L    | Current driven positive | Positive phase current  | Motor turns clockwise        |  |  |  |  |

|                       |         |     |      |      | Ph                      | ase B                   |                              |  |  |  |  |

| INH IN3 IN4 OUT3 OUT4 |         |     | OUT3 | OUT4 | Mode                    | Stepper Motor Operation | DC Motor Operation           |  |  |  |  |

| L                     | Х       | Х   | Z    | Z    | Sleep                   | Low current consumption | Low current consumption      |  |  |  |  |

| Н                     | Z       | Z   | L    | L    | Brake: low side         | No phase current        | Low-side brake               |  |  |  |  |

| Н                     | L       | L   | L    | Н    | Current driven negative | Negative phase current  | Motor turns counterclockwise |  |  |  |  |

| Н                     | L       | Н   | L    | L    | Low-side recirculation  | No current              | Low-side brake               |  |  |  |  |

| Н                     | Н       | L   | Н    | Н    | High-side recirculation | No current              | High-side brake              |  |  |  |  |

| Н                     | Н       | Н   | Н    | L    | Current driven positive | Positive phase current  | Motor turns clockwise        |  |  |  |  |

X = don't care, Z = high-impedance

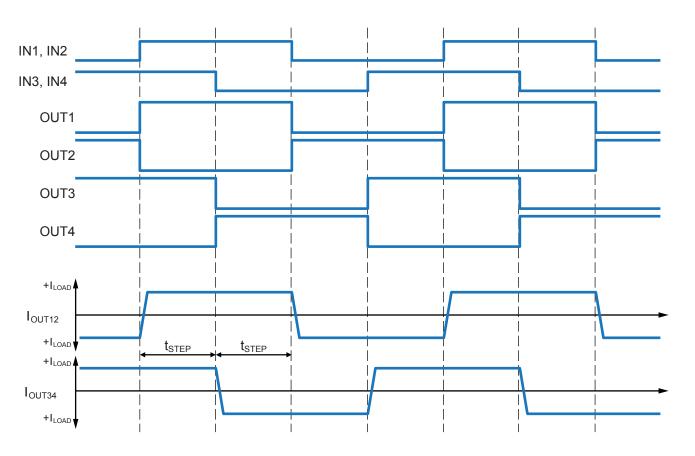

Figure 1. Stepper Motor Input and Output Sequence Timing Diagram

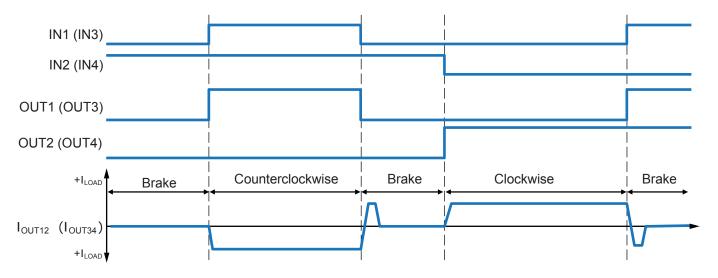

Figure 2. Brush DC Motor Input and Output Sequence Timing Diagram (phase B names shown in parentheses)

# **Functional Description**

The A4990 is an automotive dual full bridge driver suitable for high temperature applications such as headlamp bending and leveling, throttle control, and fuel recirculation control. It is also suitable for other low-current stepper applications, such as air conditioning and venting.

The device provides two full-bridge drivers for stepper motors and small brush DC motors. Each full-bridge uses DMOS power devices with integrated freewheeling diodes and the control circuit prevents cross-conduction, or shoot-through, when switching between high-side and low-side drives.

The A4990 drives stepper motors with full current, in either direction in each phase, allowing two-phase on, full-step operation. It drives DC motors in both directions and has brake capability. A single input turns-off all bridges, allowing all motors to coast. All control modes can easily be achieved using 3, 4 or 5 outputs from a standard parallel interface of a microcontroller.

The current in each phase of the stepper motor is regulated by a fixed frequency, peak detect PWM current regulator. The motor peak current can be limited by the values selected for external sense resistors, providing higher efficiency, reduced motor heating, and longer motor life.

The outputs are protected from short circuits to supply and to ground, and low load-current detection is included. Chip level protection includes: overtemperature shutdown, and overvoltage and undervoltage lockout. Faults are indicated by two error flags.

#### **Pin Functions**

**VBB** Main motor supply and chip supply for internal logic, regulators, and charge pump. Both VBB pins must be connected to the main supply and each decoupled to ground with a ceramic capacitor. A low ESR electrolytic capacitor must be connected between the main supply and ground to provide motor switching currents

$\emph{CP1}$  and  $\emph{CP2}$  Pump capacitor connection for charge pump. Connect a 100 nF / 50 V ceramic capacitor between CP1 and CP2.

$\it VCP$  Above-supply voltage for high-side drive. A 100 nF / 16 V ceramic capacitor should be connected between VCP and VBB to provide the pump storage reservoir.

**VREG** Regulated supply for bridge gate drives. A 470 nF / 10 V ceramic capacitor should be connected between VREG and ground.

**GND** Chip ground. Connect to supply ground.

**OUT1 and OUT2** Motor connection for phase A. Positive motor phase current direction is defined as flowing from OUT1 to OUT2.

**OUT3 and OUT4** Motor connection for phase B. Positive motor phase current direction is defined as flowing from OUT3 to OUT4.

**SENS12** Phase A current sense. Connect sense resistor between SENS12 and GND.

**SENS34** Phase B current sense. Connect sense resistor between SENS34 and GND.

**IN1** Control input for OUT1 with internal pull-down.

**IN2** Inverted control input for OUT2 with internal pull-up.

**IN3** Control input for OUT3 with internal pull-down.

**IN4** Inverted control input for OUT4 with internal pull-up.

**INH** Inhibit control input. Controls activity of bridge outputs. When held low, deactivates the outputs, that is, turns-off all output bridge FETs and the A4990 enters sleep mode.

**EF1** Error flag output 1. Combines with EF2 to indicate active fault status. Open drain output requiring an external pull-up resistor to the logic supply voltage.

**EF2** Error flag output 2. Combines with EF1 to indicate active fault status. Open drain output requiring an external pull-up resistor to the logic supply voltage.

## Operation

The two full-bridges in the A4990 are each controlled by two logic inputs, one input for each half bridge (IN1 for OUT1, and so forth), according to the logic shown in table 1. The two bridges are controlled independently except for the INH input which turns-off all outputs and puts the A4990 into low current sleep mode.

The two bridges in the A4990 can be used to drive a single, two-phase bipolar stepper motor or two bidirectional brush DC motors:

- Stepper Motor A two-phase stepper motor is made to rotate by sequencing the relative currents in each phase using the four inputs as shown in figure 1. In its simplest form, each phase in turn is fully energized by applying a forward or reverse voltage to each winding in sequence.

- Brush DC Motor A brush DC motor can be driven by each full-bridge, in both directions as shown in figure 2. In addition to controlling rotation direction, the two control inputs for each bridge can be used to provide PWM speed control and motor braking.

The operating modes for each motor type are listed in table 1.

Current Limiting The A4990 includes a PWM current control function that can be used to limit the phase current with changes in the operating temperature and voltage. This prevents overheating in the motor at high supply voltage or low temperatures. The PWM current control function in the A4990 can be used to limit the current in each phase independently. The current limit function is only active when other factors, such as motor phase R/L, motor speed, or supply voltage do not limit the phase current.

For each of the two phases, the currents are measured in the full-bridge using a sense resistor, RSx, with voltage feedback to the respective SENSx pin. The target current level,  $I_{PHASEx}$ , is defined as:

$$I_{\text{PHASEx}} = V_{\text{REF}} / (16 \times R_{\text{Sx}})$$

where

V<sub>REF</sub> is the internal reference voltage, and

$R_{Sx}$  is the phase sense resistor value.

**Table 2: Phase Output Current versus Sense Resistor Value**

$V_{REF} = 1.2 V$

| I <sub>PHASE</sub><br>(mA) | R <sub>S</sub><br>(mΩ)            | I <sub>PHASE</sub><br>(mA)                                                             |

|----------------------------|-----------------------------------|----------------------------------------------------------------------------------------|

| 1000                       | 150                               | 500                                                                                    |

| 909                        | 187                               | 401                                                                                    |

| 806                        | 249                               | 301                                                                                    |

| 701                        | 374                               | 201                                                                                    |

| 605                        | 750                               | 100                                                                                    |

|                            | (mA)<br>1000<br>909<br>806<br>701 | (mA)     (mΩ)       1000     150       909     187       806     249       701     374 |

Table 2 provides some typical currents using E96 series resistor values.

The current comparison is ignored at the start of the PWM on-time for a duration referred to as the *blank time*. The blank time is necessary to prevent any capacitive switching currents from causing a peak current detection.

**Cross-Conduction** Each leg (high-side, low-side pair) of a bridge is protected from cross-conduction, or shoot-through, by a fixed dead time, t<sub>DEAD</sub>. This is the time between switching-off one FET and switching-on the complementary FET. Cross-conduction is prevented by lock-out logic in each driver pair.

#### **Diagnostics**

The A4990 integrates a number of diagnostic features to protect the driver and load as far as possible from fault conditions and extreme operating environments. Some of these features automatically disable the current drive to protect the outputs and the load. Others only provide an indication of the likely fault status, by setting the error flags, EF1 and EF2. The full fault table is shown in table 3.

**Overcurrent** An overcurrent fault condition is usually caused when an output is shorted to the supply or to ground, or the motor phase terminals are shorted together. An overcurrent condition must exist for longer than the Overcurrent Fault Delay,  $t_{SCT}$ , before EF2 is set to low and the outputs are disabled. After the outputs have been disabled they remain latched in this state until the power is switched-off or the INH input is taken low.

The timer for the short detection delay,  $t_{SCT}$ , is started when an overcurrent first occurs. If the overcurrent is still present at the end of the short detection delay time, then a short fault will be generated and latched. If the overcurrent goes away before the short detection delay time is complete, then the timer is reset and a fault is generated.

Table 3: Fault Table

| EF1 | EF2 | Fault Condition                       | Latched | Outputs  | Priority |

|-----|-----|---------------------------------------|---------|----------|----------|

| Н   | Н   | No fault                              | _       | Active   | -        |

| Н   | Н   | Undervoltage                          | No      | Disabled | _        |

| Н   | L   | Overcurrent                           | Yes     | Disabled | 3        |

| L   | Н   | Open Load                             | No      | Active   | 2        |

| L   | L   | Overvoltage or<br>Overtemperature     | No      | Disabled | 1        |

|     |     | · · · · · · · · · · · · · · · · · · · |         |          |          |

# Automotive Dual Full Bridge Driver

The overcurrent fault detection functions are described in detail as follows:

Short to Supply – A short from any of the motor connections to the motor supply (VBB) is detected by monitoring the voltage across the low-side current sense resistor for each phase. This gives a direct measurement of the current through the low side of the bridge.

When a low-side FET is in the on-state, the voltage across the sense resistor, under normal operating conditions, should never be more than the Maximum Sense Voltage,  $V_{SMAX}.$  In this state, an overcurrent is determined to exist when the voltage across the sense resistor exceeds the Low-Side Overcurrent Sense Voltage,  $V_{OCL},$  typically 2 times  $V_{SMAX}.$  The actual overcurrent that  $V_{OCL}$  represents is determined by the value of the sense resistor and is typically 2 times  $I_{SMAX}.$

• Short to Ground – A short from any of the motor connections to ground is detected by directly monitoring the current through each of the high-side FETs in each bridge

When a high-side FET is in the on-state, the maximum current is typically always less than 1 A. In this state, an overcurrent is determined to exist when the current through the active high-side FET exceeds the High-Side Overcurrent Threshold,  $I_{\rm OCH}$ . Note that, when a short to ground is present, the current through the high-side FET is limited to the High-Side Current Limit,  $I_{\rm LIMH}$ , during the Overcurrent Fault Delay,  $t_{\rm SCT}$ . This prevents large negative transients at the phase output pins when the outputs are switched-off.

**Open Load** An open load fault condition is detected if the output current remains below the open load current level,  $I_{OLP}$ , for longer than the Open Load Delay,  $t_{dOLP}$ , 896  $\mu s$  (typ).

When an open load fault appears, EF1 will go low indicating the fault but no other action will be taken. If the output current increases above the limit then the fault is removed and EF1 will go high. **Overvoltage** If the motor supply voltage,  $V_{BB}$ , rises above the overvoltage threshold,  $V_{BBOV}$ , the A4990 will disable the outputs and both EF1 and EF2 will go low indicating the fault. (Note that this setting of the EFx flags also can indicate an overtemperature fault condition.) The overvoltage level has a hysteresis voltage,  $V_{BBOVhys}$ . When the motor supply voltage goes below the overvoltage threshold by more than  $V_{BBOVhys}$ , then the outputs will be re-enabled and EF1 and EF2 will go high.

**Overtemperature** If the chip temperature rises above the overtemperature threshold,  $T_{\rm JF}$ , then EF1 and EF2 will go low and the outputs will be disabled. (Note that this setting of the EFx flags also can indicate an overvoltage fault condition.) Disabling the outputs helps to prevent a further increase in the chip temperature. The overtemperature level has a hysteresis temperature,  $T_{\rm Jhys}$ . When the temperature drops below the overtemperature threshold by more than  $T_{\rm Jhys}$ , then the outputs will be re-enabled and EF1 and EF2 will go high. If the temperature is not reduced sufficiently, then the A4990 will cycle in and out of overtemperature protection, depending on the thermal time constants of the circuit assembly and its environment.

**Undervoltage** If the supply voltage,  $V_{BB}$ , goes below its undervoltage threshold,  $V_{BBUV}$ , or if the voltage of the internal regulator,  $V_{REG}$ , goes below its undervoltage threshold,  $V_{REGUV}$ , then the A4990 will disable all the bridge outputs. Note that this fault condition does not affect the fault flag outputs (EF1 and EF2).

The A4990 will re-enable the bridge outputs when both  $V_{BB}$  and  $V_{REG}$  have risen above the respective undervoltage turn-on voltages, after a short delay. Both  $V_{BB}$  and  $V_{REG}$  undervoltage detectors have hysteresis,  $V_{BBhys}$  and  $V_{REGhys}$  respectively, so the turn-on voltage for  $V_{BB}$  is  $V_{BBUV} + V_{BBhys}$ , and for  $V_{REG}$  is  $V_{REGUV} + V_{REGhys}$ .

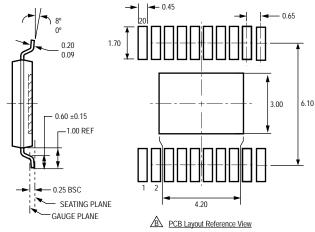

# Package LP, 20-Pin TSSOP with Exposed Thermal Pad

For Reference Only; not for tooling use (reference MO-153 ACT) Dimensions in millimeters

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

Terminal #1 mark area

Reference land pattern layout (reference IPC7351 SOP65P640X110-21M);

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

Exposed thermal pad (bottom surface)

# A4990

# Automotive Dual Full Bridge Driver

Copyright ©2012-2013, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com