# HFC0100 QUASI RESONANT CONTROLLER

#### DESCRIPTION

The HFC0100 is a peak current mode controller with Green Mode Operation. Its high efficiency feature over the entire line and load range meets the stringent world-wide energy efficiency requirements.

The HFC0100 integrated with a high voltage current source, its valley detector ensures minimum Drain-Source voltage switching (Quasi-Resonant operation). When the output power falls below a given level, the controller enters the burst mode.

The HFC0100 features variable protections like Thermal Shutdown (TSD), Vcc Under voltage Lockout (UVLO), Over Load Protection (OLP), Over Voltage Protection (OVP).

The HFC0100 is available in the 8-pin SOIC8 package.

#### **FEATURES**

- Universal Main Input Voltage (85~265VAC)

- Quasi-Resonant Operation

- Valley Switching for high efficiency and EMI

- Active Burst Mode for low standby power consumption

- Internal High Voltage Current Source

- High level of integration, allows a very low number external component count

- Maximum Frequency Limited

- Internal Soft Start

- Internal 250nS Leading Edge Blanking

- Thermal shutdown (auto restart with hysteresis)

- Vcc Under Voltage Lockout with Hysteresis (UVLO)

- Over Voltage Protection

- · Over Load Protection.

#### **APPLICATIONS**

- Battery charger: cellular phone, digital camera, video camera, electrical shaver, emergency lighting system, etc

- Standby power supply: CRT-TV, Projection-TV, LCD-TV, PDP-TV, Desk top PC, Audio system, etc

- SMPS: Inc jet printer, DVD player/recorder, VCR, CD player, Set top box, Air conditioner, refrigerator, washing machine, dish washer, Adapter for NB, etc

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

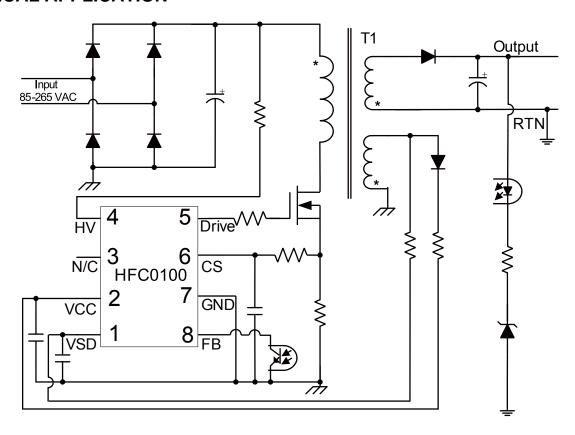

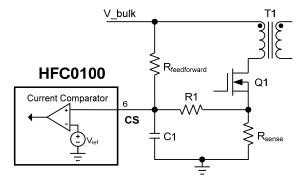

# **TYPICAL APPLICATION**

# **ORDERING INFORMATION**

| Part Number* | Package | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|--------------|---------|-------------|----------------------------------------|

| HFC0100HS    | SOIC8   | HFC0100     | -40°C to +125°C                        |

\*For Tape & Reel, add suffix –Z (e.g. HFC0100HS–Z); For RoHS compliant packaging, add suffix –LF (e.g. HFC0100HS–LF–Z)

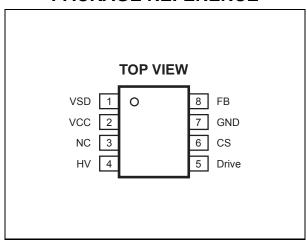

#### PACKAGE REFERENCE

| ABSOLUTE MAXIMUM RATINGS (1                               | )   |

|-----------------------------------------------------------|-----|

| HV Break Down Voltage0.7V to 700                          | V   |

| Vcc, DRV to GND0.3V to 22'                                | V   |

| FB, CS, VSD to GND0.3V to 7                               | V   |

| Continuous Power Dissipation $(T_A = +25^{\circ}C)^{(2)}$ | 2)  |

| 1.3\                                                      | Ν   |

| Junction Temperature 150°C                                | 3   |

| Thermal Shut Down 150°C                                   | С   |

| Thermal Shut Down Hysteresis 50°C                         | 0   |

| Lead Temperature 260°C                                    | С   |

| Storage Temperature60°C to +150°C                         | С   |

| ESD Capability Human Body Model (All Pi                   | ins |

| except HV)2.0k                                            | V   |

| ESD Capability Machine Model200                           | V   |

| Recommended Operation Conditions (3) |        |                        |  |  |

|--------------------------------------|--------|------------------------|--|--|

| Operating Vcc range                  |        |                        |  |  |

| Maximum Junction Temp. (T            | +125°C |                        |  |  |

| Thermal Resistance (4)<br>SOIC8      |        | <b>θ</b> ЈС<br>45 °С/W |  |  |

| Notes:                               |        |                        |  |  |

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERICS**

# For typical value T<sub>J</sub>=25 °C

| Parameter                                                                  | Symbol               | Conditions                                            | Min  | Тур   | Max  | Unit |

|----------------------------------------------------------------------------|----------------------|-------------------------------------------------------|------|-------|------|------|

| Start-up Current Source (Pin HV)                                           |                      |                                                       |      |       |      |      |

| Charging current from Pin HV                                               | Icharge              | Vcc=6V;V <sub>HV</sub> =400V                          | 1.4  | 2     | 2.6  | mA   |

| Leakage current from Pin HV                                                | I <sub>leak</sub>    | With auxiliary supply; V <sub>HV</sub> =400V, Vcc=13V |      | 20    |      | μA   |

| Break Down Voltage                                                         | $V_{BR}$             |                                                       | 700  |       |      | V    |

| Supply Voltage Management (Pin Vcc)                                        |                      |                                                       |      | •     | ı    |      |

| Vcc Upper Level at which the Internal                                      |                      |                                                       | 40.0 | 44.0  | 10   | .,   |

| High Voltage Current Source Stops                                          | V <sub>ССН</sub>     |                                                       | 10.6 | 11.8  | 13   | V    |

| Vcc Lower Level at which the Internal High Voltage Current Source Triggers | Vccl                 |                                                       | 7.2  | 8     | 8.8  | V    |

| Vcc Re-charge Level at which the protection occurs                         | Vccp                 |                                                       |      | 5.5   |      | V    |

| Internal IC Consumption, 1nF Load on Drive Pin,                            | lcc1                 | Fs=100kHz,<br>Vcc=12V                                 |      | 2.0   |      | mA   |

| Internal IC Consumption, Latch off phase,                                  | lcc2                 | VCC=6V                                                |      | 450   |      | μA   |

| Feedback Management (Pin FB)                                               |                      |                                                       |      | ı     | l    |      |

| Internal Pull Up Resistor                                                  | R <sub>FB</sub>      |                                                       |      | 10    |      | kΩ   |

| Internal Pull Up Voltage                                                   | Vup                  |                                                       |      | 4.5   |      | V    |

| FB Pin to Current Limit Division Ratio                                     | I <sub>div</sub>     |                                                       |      | 3     |      |      |

| Internal Soft-Start Time                                                   | Tss                  |                                                       |      | 2.4   |      | mS   |

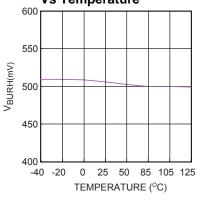

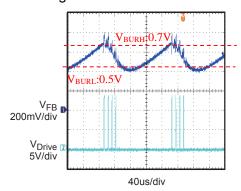

| FB Decreasing Level at which the                                           | V <sub>BURL</sub>    |                                                       |      | 0.5   |      | V    |

| controller enter the Burst Mode                                            |                      |                                                       |      |       |      |      |

| FB Increasing Level at which the controller leave the Burst Mode           | $V_{BURH}$           |                                                       |      | 0.7   |      | V    |

| Over Load Set Point                                                        | V <sub>OLP</sub>     |                                                       |      | 3.7   |      | V    |

| Valley Switching Management (Pin VS                                        |                      |                                                       |      |       | ı    | 1    |

| Valley Switching Threshold Voltage                                         | V <sub>VSD</sub>     |                                                       | 40   | 55    | 70   | mV   |

| Valley Switching Hysteresis                                                | V <sub>hys</sub>     |                                                       |      | 10    |      | mV   |

|                                                                            | Vvsdh                | High State;<br>Ipin2=3.0mA                            | 7    | 7.5   | 8    |      |

| Pin VSD Clamp Voltage                                                      | Vvsdl                | Low State;<br>Ipin2=-2.0mA                            | -0.8 | -0.65 | -0.5 | - V  |

| Valley Switching Propagation Delay                                         | T <sub>VSD</sub>     | Pull down from 2V<br>to -100mV                        | 100  | 160   | 200  | nS   |

| Minimum Off Time                                                           | T <sub>min</sub>     |                                                       | 6.6  | 7.8   | 9    | μS   |

| Re-start time After Last Valley detect Transition                          | T <sub>restart</sub> |                                                       |      | 4.6   |      | μS   |

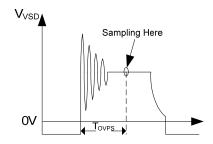

| OVP Sampling Delay                                                         | Tovps                |                                                       |      | 3.5   |      | μS   |

| Pin VSD OVP reference level                                                | Vovp                 |                                                       |      | 6     |      | V    |

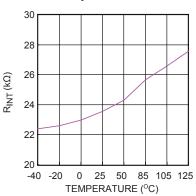

| Internal Impedance                                                         | Rint                 |                                                       |      | 24    |      | kΩ   |

| Current Sampling Management (Pin CS)                                       |                      |                                                       | •    |       |      |      |

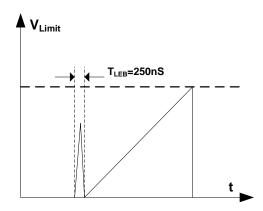

| Leading Edge Blanking                                                      | T <sub>LEB</sub>     |                                                       |      | 250   |      | nS   |

| Driving Signal (Pin DRIVE)                                                 |                      |                                                       | •    |       |      |      |

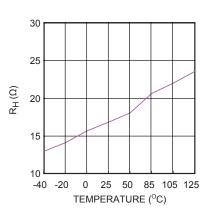

| Sourcing Resistor                                                          | R <sub>H</sub>       |                                                       |      | 17    |      | Ω    |

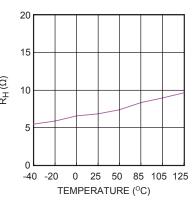

| Sinking Resistor                                                           | R∟                   |                                                       |      | 7     |      | Ω    |

| J                                                                          |                      |                                                       |      | 1     |      |      |

# **PIN FUNCTIONS**

| Pin# | Name  | Description                                                                                                                                                                                                         |

|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VSD   | Input from the auxiliary flyback signal, it ensures discontinuous operation and valley switching. It also offers a fixed OVP detection.                                                                             |

| 2    | Vcc   | Supply voltage Pin. This pin is connected to an external bulk capacitor of typically 22uf and a ceramic capacitor of typically 0.1uF.                                                                               |

| 3    | N/C   | This Pin ensures adequate creepage distance.                                                                                                                                                                        |

| 4    | HV    | Input for the start up current unit.                                                                                                                                                                                |

| 5    | Drive | Output of the driving signal.                                                                                                                                                                                       |

| 6    | CS    | Input of the current sense.                                                                                                                                                                                         |

| 7    | GND   | Ground.                                                                                                                                                                                                             |

| 8    | FB    | The Pin sets the peak current limit, by connecting an optocoupler to this Pin. A feedback voltage of 3.7V will trigger an over load protection, and a feedback voltage of 0.5V will trigger a burst mode operation. |

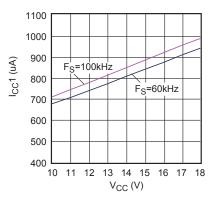

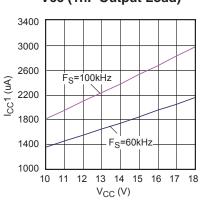

# TYPICAL PERFORMANCE CHARACTERISTICS

T<sub>A</sub>=25°C

IC Consumption Vs Vcc (No Output Load)

IC Consumption Vs Vcc (1nF Output Load)

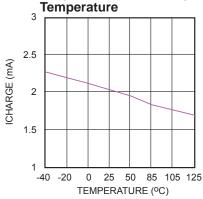

**Charging Current From Pin** HV (Vcc=6V, VHV=400V) Vs

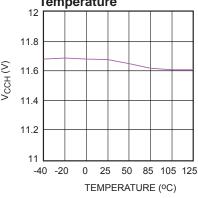

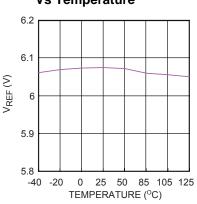

Vcc Upper Level at which the Internal High Voltage **Current Source Stops Vs Temperature**

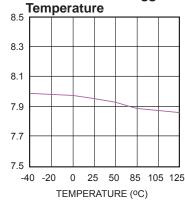

Vcc Lower Level at which the Internal High Voltage **Current Source Triggers Vs**

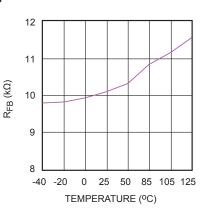

Pin FB Internal Pull Up **Resistor Vs Temperature**

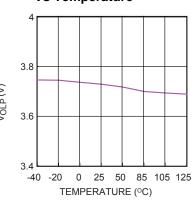

**Over Load Set Point** Vs Temperature

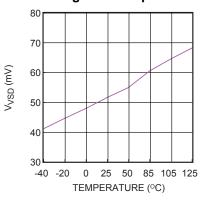

**Valley Switching Threshold** Voltage Vs Temperature

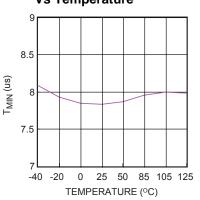

**Minimum Off Time** Vs Temperature

VCCL (V)

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continues)

**T**<sub>A</sub>=25℃

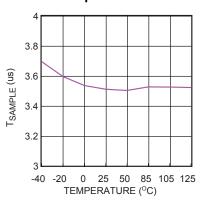

OVP Sampling Delay Vs Temperature

Pin VSD OVP reference level Vs Temperature

Pin VSD Internal Impedance Vs Temperature

Sourcing Resistor Vs Temperature

Sinking Resistor Vs Temperature

FB Decreasing Level at which the controller enter the Burst Mode Vs Temperature

FB Increasing Level at which the controller leave the Burst Mode Vs Temperature

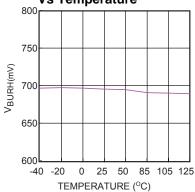

# **BLOCK DIAGRAME**

Figure 1— Block Diagram

#### **OPERATION**

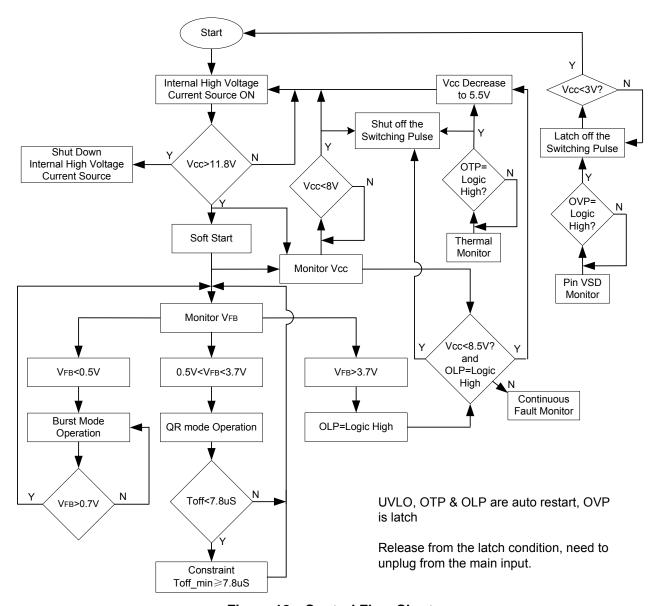

The HFC0100 incorporates all the necessary features needed to a reliable Switch Mode Power Supply. Its valley detector ensures minimum Drain-Source voltage switching (Quasi-Resonant operation). When the output power falls below a given level, the regulator enters the burst mode. An internal minimum off time limiter prevents the free running frequency to exceed 150kHz.

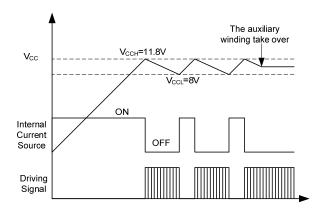

#### Start-Up

Initially, the IC is self supplying from the internal high voltage current source unit which drawn from the HV pin.

The IC starts switching and the internal high voltage current source unit is stopped as soon as the voltage on Pin Vcc reaches the threshold  $V_{\text{CCH}}$ —11.8V.

Before the supply is taken over by the auxiliary winding of the transformer, the Vcc capacitor supplies HFC0100 to maintain Vcc.

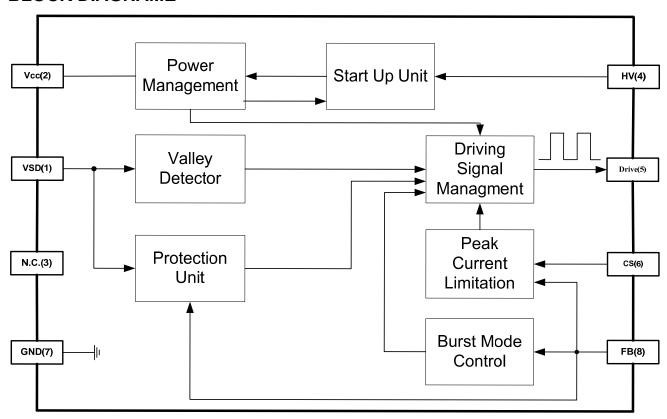

# **Quasi-Resonant Operation**

The HFC0100 operates in Discontinuous Conduction Mode (DCM). The valley detector ensures minimum Drain-Source voltage switching (Quasi-Resonant operation)

As a result, there are virtually no primary switch turn on losses and no secondary diode recovery losses. It ensures the reduction of the EMI noise.

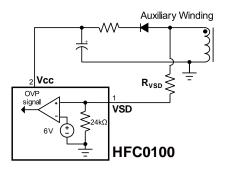

Figure 2 shows the valley detector unit.

When the voltage:

$$(V_{\text{DS}}-V_{\text{in}})x\frac{N_{\text{aux}}}{N_{\text{pri}}}x\frac{24k\Omega}{24k\Omega+R_{\text{VSD}}}<55mV$$

V<sub>DS</sub>—Drain Source Voltage of the primary FET

V<sub>IN</sub>—Input Voltage

Naux—Auxiliary Winding Turns of the transformer

N<sub>pri</sub>—Primary Winding Turns of the transformer

The valley detector sends out a valley signal to turn on the primary FET.

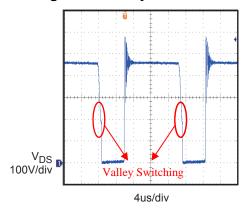

Figure 3 shows a typical drain source voltage waveform with valley switching.

Figure 2—Valley Detector

Figure 3—Valley Switching

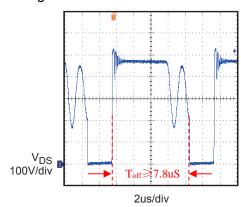

To ensure the switching frequency below the EN55022 start limit---150kHz, HFC0100 employs an internal minimum off time limiter---7.8µS, shows as figure 4.

Figure 4—Minimum Off Time Limit

#### **V<sub>CC</sub> Under-Voltage Lock-out**

When the Vcc below the UVLO threshold-8V, the HFC0100 stops switching and the internal high voltage current source unit re-starts, the Vcc external bulk capacitor is re-charged by it.

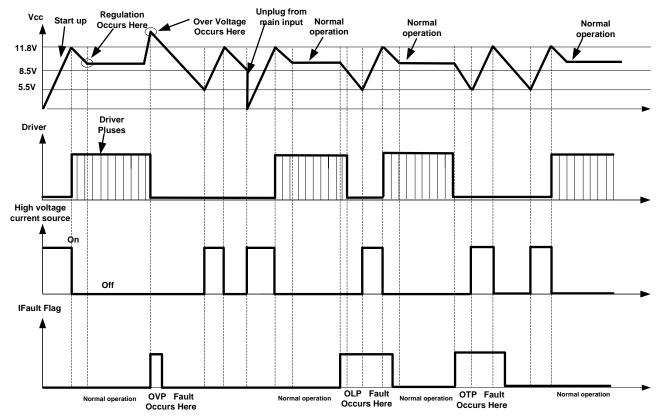

Figure 5 shows the typical waveform with Vcc under voltage lock out.

Figure 5—Vcc Under-Voltage Lock Out

Over-Voltage Protection (OVP)

The positive plateau of auxiliary winding voltage is proportional to the output voltage, the OVP use the auxiliary winding voltage instead of directly monitoring the output voltage.

The Figure 6 shows the OVP sample unit.

If the voltage:

$$V_O \times \frac{N_{aux}}{N_{SEC}} \times \frac{24k\Omega}{24k\Omega + R_{VSD}} > 6V$$

Vo-Output voltage

Naux—Auxiliary Winding Turns of the transformer

$N_{\text{SEC}}$ —Secondary Winding Turns of the transformer

The OVP circuit is triggered, and the HFC0100 stops the switching cycle and goes into latched fault condition. The controller stays fully latched in this position until the Vcc is decreased down to 3V, e.g. when the user unplugs the power supply from the main supply and re-plugs it.

Figure 6—OVP Sample Unit

To avoid the mis-trigger due to the oscillation of the leakage inductance and the parasitic capacitance, the OVP sampling has a  $T_{\text{OVPS}}$  blanking, typical 3.5 $\mu$ S, shows as Figure 7.

Figure 7

#### **Over Load Protection (OLP)**

The maximum output power is limited by the maximum switching frequency and maximum primary peak current. If the output consumes more than the maximum output power, the output voltage is drawn below the set point, this reduces the current through the optocoupler LED, which also reduces the transistor current, thus increases the FB voltage.

By continuously monitoring the Pin FB voltage, when the feedback voltage exceeds the threshold  $V_{\text{OLP}}$ —3.7V, it shuts off the switching cycle. The HFC0100 enters a safe low power operation that prevents from any lethal thermal or stress damage. As soon as the default disappears, the power supply resumes operation.

During the start up or load transient, the FB voltage will be high enough temporarily to mistrigger the OLP, to prevent this undesired protection, OLP circuit is designed to be triggered after Vcc is decreased below 8.5V.

#### **Burst Operation**

To minimize the power dissipation in no load or light load, the HFC0100 enters the burst mode operation. As the load decreases, the FB voltage decreases,, the HFC0100 stops the switching cycle when the FB voltage drops below the threshold  $V_{\text{BURL}}$ —0.5V. And the output voltage starts to drop at a rate dependent on the load. This causes the FB voltage to rise again. Once the FB voltage exceeds the threshold  $V_{\text{BURH}}$ —0.7V, switching resumes. The FB voltage then falls and rises repeatedly. The burst mode operation alternately enables and disables switching cycle of the MOSFET thereby reducing switching loss in the no load or light load conditions.

Figure 8 shows the typical FB and Drive waveform during the burst mode.

Figure 8—Burst Mode

# Thermal Shutdown (TSD)

To prevents from any lethal thermal damage. The HFC0100 shuts down switching cycle when the inner temperature exceeds 150DegC. As soon as the inner temperature drops below 100DegC, the power supply resumes operation.

#### **Soft-Start**

To reduce the stress on primary MOSFET and secondary diode during start up, to smoothly establish the output voltage, the HFC0100 has an internal soft-start circuit that increases the current comparator inverting input voltage, together with the MOSFET current, slowly after it starts up. The pulse width to the power switching device is progressively increased to establish the correct working conditions for transformers, inductors, and capacitors.

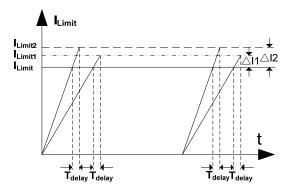

#### **Current Limit Setting**

The switch current is sensed by the resistor series between the Source of the FET and the ground. And the current limit is determined by the

FB signal,

$$V_{Limit} = \frac{V_{FB}}{I_{div}} = \frac{V_{FB}}{3}$$

. To limit the

maximum output power, the current limit is clamped at 1V when  $V_{\text{FB}}$  is bigger than 3.3V.

#### Leading Edge Blanking

In order to avoid the premature termination of the switching pulse due to the parasitic capacitance, an internal leading edge blanking (LEB) unit is employed between the CS Pin and the current comparator input. During the blanking time, the path, CS Pin to the current comparator input, is blocked. Figure 9 shows the leading edge blanking.

Figure 9—Leading Edge Blanking

#### **Over Power Compensation**

In the case of current sensing, shows as figure 10, the turn off of the FET is delayed due to the propagation delay of the control circuit, the delay time is the inherent characteristic of the control circuit, so  $T_{delay}$  can be seen fixed. This delay will cause an overshoot of the peak current.  $\triangle I2$  is bigger than  $\triangle I1$  due to the bigger rising ratio(the higher input voltage, the bigger rising ratio).

The propagation delay is done by means of the feedforward resistor, shown as Figure 11. Through this method, adding one offset voltage at CS pin (the higher input voltage, the bigger offset voltage.).

Figure 10—Propagation delay of the current limit

Figure 11—Over Power Compensation

Figure 12 shows the HFC0100 control flow chart.

Figure 13 shows the HFC0100 evolution of the signals in presence of faults

Figure 12—Control Flow Chart

Figure 13—Evolution of the Signals in Presence of Faults

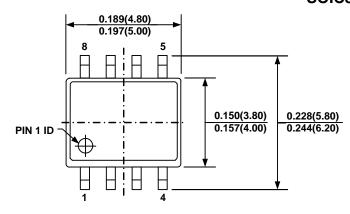

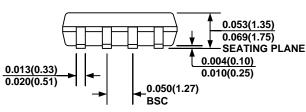

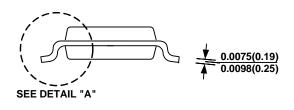

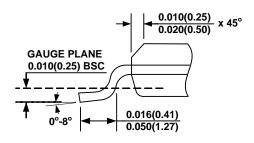

### PACKAGE INFORMATION

#### SOIC8

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

FRONT VIEW

**SIDE VIEW**

**DETAIL "A"**

#### **NOTE:**

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.