### **General Description**

The MAX17005B/MAX17006B/MAX17015B are high-frequency multichemistry battery chargers. These circuits feature a new high-frequency current-mode architecture that significantly reduces component size and cost. The charger uses a high-side MOSFET with n-channel synchronous rectifier. Widely adjustable charge current, charge voltage, and input current limit simplify the construction of highly accurate and efficient chargers.

The charge voltage and charge current are set with analog control inputs. The charge current setting can also be adjusted with a PWM input. High-accuracy current-sense amplifiers provide fast cycle-by-cycle current-mode control to protect against short circuits to the battery and respond quickly to system load transients. In addition, the charger provides a high-accuracy analog output that is proportional to the adapter current. In the MAX17015B, this current monitor remains active when the adapter is absent to monitor battery discharge current.

The MAX17005B charges three or four Li+ series cells, and the MAX17006B charges two or three Li+ series cells. The MAX17015B adjusts the charge voltage setting and the number of cells through a feedback resistor-divider from the output. All variants of the charger can provide at least 4A of charge current with a  $10m\Omega$ sense resistor.

The charger utilizes a charge pump to control an n-channel adapter selection switch. The charge pump remains active even when the charger is off. When the adapter is absent, a p-channel MOSFET selects the battery.

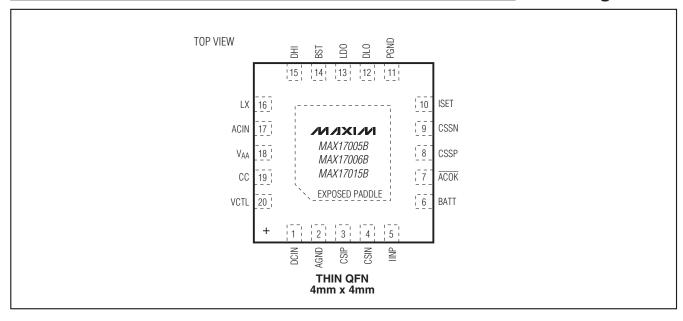

The MAX17005B/MAX17006B/MAX17015B are available in a small, 4mm x 4mm x 0.8mm 20-pin, lead-free TQFN package. An evaluation kit is available to reduce design time.

#### **Applications**

Notebook Computers

**Tablet PCs**

Portable Equipment with Rechargeable Batteries

### **Features**

- ♦ High Switching Frequency (1.2MHz)

- **♦ Controlled Inductor Current-Ripple Architecture Reduced BOM Cost Small Inductor and Output Capacitors**

- ♦ ±0.4% Accurate Charge Voltage

- **♦** ±2.5% Accurate Input-Current Limiting

- **♦** ±3% Accurate Charge Current

- **♦ Single-Point Compensation**

- **♦** Monitor Outputs for ±2.5% Accurate Input Current Limit ±2.5% Battery Discharge Current (MAX17015B Only) **AC Adapter Detection**

- ♦ Analog/PWM Adjustable Charge-Current Setting

- ♦ Battery Voltage Adjustable for 3 and 4 Cells (MAX17005B) or 2 and 3 Cells (MAX17006B)

- **♦** Adjustable Battery Voltage (4.2V to 4.4V/Cell)

- **♦ Cycle-by-Cycle Current Limit Battery Short-Circuit Protection Fast Response for Pulse Charging Fast System-Load-Transient Response**

- ♦ Programmable Charge Current < 5A</p>

- **♦ Automatic System Power Source Selection with** n-Channel MOSFET

- ♦ Internal Boost Diode

- ♦ +8V to +26V Input Voltage Range

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE  |

|---------------|----------------|--------------|

| MAX17005BETP+ | -40°C to +85°C | 20 TQFN-EP** |

| MAX17006BETP+ | -40°C to +85°C | 20 TQFN-EP** |

| MAX17015BETP+ | -40°C to +85°C | 20 TQFN-EP** |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Pin Configuration and Minimal Operating Circuit appear at end of data sheet.

<sup>\*\*</sup> EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| DCIN, CSSP, CSSN, BATT, CSIN, CSIP, ACOK, LX to AGND0.3V to +30V BST to LDO0.3V to +30V                                        | PGND to AGND                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| CSIP to CSIN, CSSP to CSSN0.3V to +0.3V IINP, FB, ACIN, CC to AGND0.3V to (VAA + 0.3V) VAA, LDO, ISET, VCTL to AGND0.3V to +6V | 16-Pin TQFN (derate 16.9mW/°C above +70°C)1349.1mW Operating Temperature Range40°C to +85°C Junction Temperature+150°C |

| DHI to LX0.3V to (V <sub>BST</sub> + 0.3V)<br>BST to LX0.3V to +6V                                                             | Storage Temperature Range60°C to +150°C Lead Temperature (soldering, 10s)+300°C                                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{DCIN} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 16.8V$ ,  $V_{VCTL} = V_{AA}$ ,  $V_{ISET} = 1V$ ,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                           | CONE                                                                                          | DITIONS                                         | MIN                         | TYP   | MAX                         | UNITS  |

|-------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------|-------|-----------------------------|--------|

| CHARGE-VOLTAGE REGULATION           |                                                                                               |                                                 |                             |       |                             | •      |

|                                     | 2 cells, V <sub>VCTL</sub> = V <sub>AGND</sub> (MAX17006B)                                    |                                                 | 8.3664                      | 8.40  | 8.4336                      |        |

|                                     | 3 cells, V <sub>VCTL</sub> = V <sub>AA</sub> (MAX1                                            | 17005B/MAX17006B)                               | 12.549                      | 12.60 | 12.651                      |        |

| Battery Regulation-Voltage Accuracy | 4 cells, V <sub>VCTL</sub> = V <sub>AGND</sub> (N                                             | MAX17005B)                                      | 16.733                      | 16.80 | 16.867                      | V      |

|                                     | FB accuracy using FB div (Note 1)                                                             | vider (MAX17015B)                               | 2.0916                      | 2.1   | 2.1084                      |        |

| FB Input Bias Current               |                                                                                               |                                                 | -1                          |       | +1                          | μΑ     |

| VOTI Danas                          | 2 cells (MAX17006B), 4 ce                                                                     | ells (MAX17005B)                                | 0                           |       | V <sub>AA</sub> /2<br>- 0.2 | V      |

| VCTL Range                          | 3 cells (MAX17005B/MAX                                                                        | (17006B)                                        | V <sub>AA</sub> /2<br>+ 0.2 |       | VAA                         | V      |

| VCTL Gain                           | V <sub>CELL</sub> /V <sub>V</sub> CTL                                                         | VCELL/VVCTL                                     |                             | 6     | 6.15                        | V/V    |

| VCTL Input Bias Current             | Vvctl = Vagno and VCTL = Vaa                                                                  |                                                 | -1                          |       | +1                          | μΑ     |

| CHARGE-CURRENT REGULATION           |                                                                                               |                                                 |                             |       |                             |        |

| ISET Range                          |                                                                                               |                                                 | 0                           |       | V <sub>AA</sub> /2          | V      |

| ISST Sull Sools Setting             | ISET = 1.4V                                                                                   |                                                 |                             | 80    |                             | mV     |

| ISET Full-Scale Setting             | ISET = 99.9% duty cycle                                                                       |                                                 |                             | 60    |                             | ] '''' |

|                                     |                                                                                               | VISET = VAA/4 or ISET                           | 58.2                        | 60    | 61.8                        | mV     |

| Full-Charge Current Accuracy        |                                                                                               | = 99.9% duty cycle                              | -3                          |       | +3                          | %      |

| (CSIP to CSIN)                      | V <sub>BATT</sub> = 1V to 16.8V                                                               | V <sub>ISET</sub> = V <sub>AA</sub> /6 or ISET  | 38.2                        | 40    | 41.8                        | mV     |

|                                     | VBATT = 1.0 10 10.00                                                                          | = 66.7% duty cycle                              | -4.5                        |       | +4.5                        | %      |

| Trickle Charge-Current Accuracy     |                                                                                               | V <sub>ISET</sub> = V <sub>AA</sub> /80 or ISET | 1.4                         | 3     | 4.6                         | mV     |

| Thickie Charge-Current Accuracy     |                                                                                               | = 5% duty cycle                                 | -52                         |       | +52                         | %      |

| Charge-Current Gain Error           | Based on Viset = VVAA/4 and Viset = VVAA/80                                                   |                                                 | -2                          |       | +2                          | %      |

| Charge-Current Offset Error         | Based on V <sub>ISET</sub> = V <sub>VAA</sub> /4 and V <sub>ISET</sub> = V <sub>VAA</sub> /80 |                                                 | -1.4                        |       | +1.4                        | mV     |

| BATT/CSIP/CSIN Input-Voltage Range  |                                                                                               |                                                 | 0                           |       | 24                          | V      |

| ISET Power-Down Mode Threshold      | ISET falling                                                                                  |                                                 | 21                          | 26    | 31                          | mV     |

|                                     | ISET rising                                                                                   |                                                 | 33                          | 40    | 47                          | ] '''V |

\_\_\_ /N/1XI/M

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{DCIN} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 16.8V$ ,  $V_{VCTL} = V_{AA}$ ,  $V_{ISET} = 1V$ ,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                      |                                                | CONDITIONS                          | MIN   | TYP  | MAX   | UNITS |

|------------------------------------------------|------------------------------------------------|-------------------------------------|-------|------|-------|-------|

| ICET Innut Dia a Current                       | VISET = 3V                                     |                                     | -0.2  |      | +0.2  |       |

| ISET Input Bias Current                        | CSSN = BATT, VI                                | SET = 5V                            | -0.2  |      | +0.2  | μΑ    |

| ISET PWM Threshold                             | Rising                                         |                                     |       |      | 2.4   | V     |

| ISET PWW THESHOLD                              | Falling                                        |                                     | 0.8   |      |       | ]     |

| ISET Frequency                                 |                                                |                                     | 0.128 |      | 500   | kHz   |

| ISET Effective Resolution                      | f <sub>PWM</sub> = 1.6MHz                      |                                     |       | 8    |       | Bits  |

| INPUT-CURRENT REGULATION                       |                                                |                                     |       |      |       |       |

| Input Current-Limit Threshold                  | VCSSP - VCSSN                                  |                                     | 58.5  | 60   | 61.5  | mV    |

|                                                | VCSSP - VCSSN                                  |                                     | -2.5  |      | +2.5  | %     |

| CSSN Input Bias Current                        | Adapter present a                              | at $T_A = +25^{\circ}C$             | -1    |      | +1    | μΑ    |

| CSSP/CSSN Input-Voltage Range                  |                                                |                                     | 8.0   |      | 26.0  | V     |

| IINP Transconductance                          | VCSSP - VCSSN =                                | 60mV                                | 2.66  | 2.8  | 2.94  | μA/mV |

| IINP Accuracy                                  | V <sub>CSSP</sub> - V <sub>CSSN</sub> = 0      | 60mV, V <sub>IINP</sub> = 0 to 4.5V | -2.5  |      | +2.5  | 0/    |

| Illive Accuracy                                | V <sub>CSSP</sub> - V <sub>CSSN</sub> = 35mV   |                                     | -2.5  |      | +2.5  | - %   |

| SUPPLY AND LINEAR REGULATOR                    |                                                |                                     |       |      |       |       |

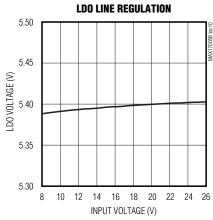

| DCIN Input-Voltage Range                       |                                                |                                     | 8     |      | 26    | V     |

| DCIN Undervoltage-Lockout (UVLO) Trip-Point    | DCIN falling                                   |                                     | 7.9   | 8.1  |       | V     |

| Doin ondervoitage-Lockout (OVLO) Imp-Foint     | DCIN rising                                    | DCIN rising                         |       | 8.7  | 8.9   | V     |

| DCIN + CSSP + CSSN Quiescent Current           | Adapter present                                |                                     |       | 3    | 6     | mA    |

| (Note 2)                                       | Adapter absent                                 |                                     |       | 30   | 50    | μΑ    |

| DATE COID COIN A LY Issued Comment             | V <sub>BATT</sub> = 16.8V                      | Adapter absent                      |       | 10   | 20    |       |

| BATT + CSIP + CSIN + LX Input Current (Note 2) | ABALL = 10.0A                                  | Charger shutdown                    |       | 10   | 20    | μΑ    |

| (14010-2)                                      | V <sub>BATT</sub> = 2V to 19V, adapter present |                                     |       | 200  | 500   |       |

| LDO Output Voltage                             | 8.0V < V <sub>DCIN</sub> < 26                  | 6V, no load                         | 5.15  | 5.35 | 5.55  | V     |

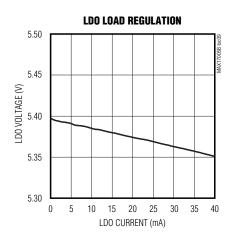

| LDO Load Regulation                            | 0 < I <sub>LDO</sub> < 40mA                    |                                     |       | 100  | 200   | mV    |

| LDO UVLO Threshold                             |                                                |                                     | 3.2   | 4.1  | 5.0   | V     |

| REFERENCES                                     |                                                |                                     | •     |      |       |       |

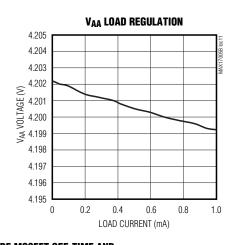

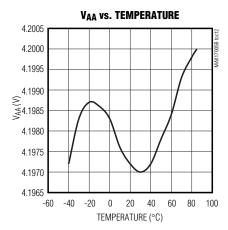

| V <sub>AA</sub> Output Voltage                 | ΙνΑΑ = 50μΑ                                    |                                     | 4.18  | 4.20 | 4.22  | V     |

| V <sub>AA</sub> UVLO Threshold                 | V <sub>AA</sub> falling                        |                                     |       | 3.1  | 3.9   | V     |

| ACIN                                           | •                                              |                                     |       |      |       |       |

| ACIN Threshold                                 |                                                |                                     | 2.058 | 2.1  | 2.142 | V     |

| ACIN Threshold Hysteresis                      |                                                |                                     | 10    | 20   | 30    | mV    |

| ACIN Input Bias Current                        |                                                |                                     |       |      | +1    | μΑ    |

| ACOK                                           |                                                |                                     | •     |      |       | •     |

| ACOK Sink Current                              | $V_{\overline{ACOK}} = 0.4V, V_A$              | CIN = 1.5V                          | 6     |      |       | mA    |

| ACOK Leakage Current                           | $V_{\overline{ACOK}} = 5.5V, V_A$              | CIN = 2.5V                          |       |      | 1     | μΑ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{DCIN} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 16.8V$ ,  $V_{VCTL} = V_{AA}$ ,  $V_{ISET} = 1V$ ,  $V_{A} = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $V_{A} = 10^{\circ}C$ .)

| PARAMETER                                                      | CONDITIONS                                                       | MIN   | TYP   | MAX   | UNITS |

|----------------------------------------------------------------|------------------------------------------------------------------|-------|-------|-------|-------|

| SWITCHING REGULATOR                                            |                                                                  |       |       |       | •     |

| DHI Off-Time K Factor                                          | V <sub>DCIN</sub> = 19V, V <sub>BATT</sub> = 10V                 | 0.029 | 0.035 | 0.041 | μs/V  |

| Sense Voltage for Minimum Discontinuous<br>Mode Ripple Current | V <sub>CSIP</sub> - V <sub>CSIN</sub>                            |       | 10    |       | mV    |

| Zero-Crossing Comparator Threshold                             | VCSIP - VCSIN                                                    |       | 10    |       | mV    |

| Cycle-by-Cycle Current-Limit Sense Voltage                     | VCSIP - VCSIN                                                    | 105   | 110   | 115   | mV    |

| DHI Resistance High                                            | I <sub>DLO</sub> = 10mA                                          |       | 1.5   | 3     | Ω     |

| DHI Resistance Low                                             | I <sub>DLO</sub> = -10mA                                         |       | 0.8   | 1.75  | Ω     |

| DLO Resistance High                                            | I <sub>DLO</sub> = 10mA                                          |       | 3     | 6     | Ω     |

| DLO Resistance Low                                             | I <sub>DLO</sub> = -10mA                                         |       | 3     | 7     | Ω     |

| ADAPTER DETECTION                                              |                                                                  |       |       |       |       |

| Adapter Absence-Detect Threshold                               | VDCIN - VBATT, VDCIN falling                                     | +70   | +120  | +170  | mV    |

| Adapter Detect Threshold                                       | V <sub>DCIN</sub> - V <sub>BATT</sub> , V <sub>DCIN</sub> rising | +360  | +420  | +580  | mV    |

| Adapter Switch Charge-Pump Frequency                           | Charger shutdown                                                 | 180   | 200   | 220   | Hz    |

| Adapter Switch Charge-Pump Refresh Pulse                       | DLO                                                              | 0.04  | 0.1   | 0.20  | 116   |

| Adapter Switch Charge-Fullip heliesh Fulse                     | DHI                                                              | 0.07  | 0.15  | 0.30  | μs    |

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{DCIN} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 16.8V$ ,  $V_{VCTL} = V_{AA}$ ,  $V_{ISET} = 1V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.)

| PARAMETER                           | PARAMETER CONDITIONS                                               |                             | TYP | MAX                         | UNITS |

|-------------------------------------|--------------------------------------------------------------------|-----------------------------|-----|-----------------------------|-------|

| CHARGE-VOLTAGE REGULATION           |                                                                    |                             |     |                             |       |

|                                     | 2 cells, V <sub>VCTL</sub> = V <sub>AGND</sub> (MAX17006B)         | 8.366                       |     | 8.433                       |       |

|                                     | 3 cells, V <sub>VCTL</sub> = V <sub>AA</sub> (MAX17005B/MAX17006B) | 12.549                      |     | 12.651                      |       |

| Battery Regulation-Voltage Accuracy | 4 cells, V <sub>VCTL</sub> = V <sub>AGND</sub> (MAX17005B)         | 16.73                       |     | 16.86                       | V     |

|                                     | FB accuracy using FB divider (MAX17015B) (Note 1)                  | 2.091                       |     | 2.108                       |       |

| VCTL Range                          | 2 cells (MAX17006B),<br>4 cells (MAX17005B)                        | 0                           |     | V <sub>AA</sub> /2<br>- 0.2 | V     |

| VOIL natige                         | 3 cells (MAX17005B/MAX17006B)                                      | V <sub>AA</sub> /2<br>+ 0.2 |     | VAA                         | V     |

| VCTL Gain                           | VCELL/VVCTL                                                        | 5.85                        |     | 6.15                        | V/V   |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{DCIN} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 16.8V$ ,  $V_{VCTL} = V_{AA}$ ,  $V_{ISET} = 1V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                            | CONDITIONS                                     |                                                                  |       | TYP | MAX                | UNITS |

|------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------|-------|-----|--------------------|-------|

| CHARGE-CURRENT REGULATION                            |                                                |                                                                  |       |     |                    |       |

| ISET Range                                           |                                                |                                                                  | 0     |     | V <sub>AA</sub> /2 | V     |

|                                                      |                                                | VISET = VAA/4 or                                                 | 57.5  |     | 62.5               | mV    |

| Full Charge-Current Accuracy                         |                                                | ISET = 99.9% duty cycle                                          | -4.2  |     | +4.2               | %     |

| (CSIP to CSIN)                                       |                                                | , VISET = VAA/6 or                                               | 38    |     | 42                 | mV    |

|                                                      | $V_{BATT} = 1V \text{ to } 16.8V$              | ISET = 66.7% duty cycle                                          | -5    |     | +5                 | %     |

| viset = VAA/80 or                                    |                                                | 1.4                                                              |       | 4.6 | mV                 |       |

| Trickle Charge-Current Accuracy                      |                                                | ISET = 5% duty cycle                                             | -52   |     | +52                | %     |

| Charge-Current Gain Error                            | Based on Viset = V                             | / <sub>VAA</sub> /4 and V <sub>ISET</sub> = V <sub>VAA</sub> /80 | -2    |     | +2                 | %     |

| Charge-Current Offset Error                          | Based on VISET = V                             | / <sub>VAA</sub> /4 and V <sub>ISET</sub> = V <sub>VAA</sub> /80 | -1.4  |     | +1.4               | mV    |

| BATT/CSIP/CSIN Input-Voltage Range                   |                                                |                                                                  | 0     |     | 24                 | V     |

| ISET Power-Down Mode Threshold                       | ISET falling                                   |                                                                  | 21    |     | 31                 | m\/   |

| ISET FOWEI-DOWN WIOGE THESHOID                       | ISET rising                                    |                                                                  | 33    |     | 47                 | - mV  |

| ISET PWM Threshold                                   | Rising                                         |                                                                  |       |     | 2.4                | V     |

| ISET PWW Trireshold                                  | Falling                                        |                                                                  | 0.8   |     |                    | ]     |

| ISET Frequency                                       |                                                |                                                                  | 0.128 |     | 500                | kHz   |

| INPUT-CURRENT REGULATION                             |                                                |                                                                  |       |     |                    |       |

| Input Current-Limit Threshold                        | VCSSP - VCSSN                                  |                                                                  | 58.2  |     | 61.8               | mV    |

| Imput Current-Limit Threshold                        | VCSSP - VCSSN                                  | VCSSP - VCSSN                                                    |       |     | +3                 | %     |

| CSSN Input Bias Current                              | Adapter present                                |                                                                  | -2    |     | +2                 | μΑ    |

| CSSP/CSSN Input-Voltage Range                        |                                                |                                                                  | 8.0   |     | 26.0               | V     |

| IINP Transconductance                                | V <sub>CSSP</sub> - V <sub>CSSN</sub> = 60     | )mV                                                              | 2.66  |     | 2.94               | μA/mV |

| IINP Accuracy                                        | VCSSP - VCSSN = 60                             | $0mV$ , $V_{IINP} = 0$ to $4.5V$                                 | -2.5  |     | +2.5               | %     |

| IIIVI Accuracy                                       | V <sub>CSSP</sub> - V <sub>CSSN</sub> = 35     | 5mV                                                              | -2.5  |     | +2.5               | /0    |

| SUPPLY AND LINEAR REGULATOR                          |                                                |                                                                  |       |     |                    |       |

| DCIN Input-Voltage Range                             |                                                |                                                                  | 8     |     | 26                 | V     |

| DCIN UVLO Trip-Point                                 | DCIN falling                                   |                                                                  | 7.9   |     |                    | V     |

| DOIN OVEO INP-I OIN                                  | DCIN rising                                    |                                                                  |       |     | 8.9                | V     |

| DCIN + CSSP + CSSN Quiescent Current Adapter present |                                                |                                                                  |       |     | 6                  | mA    |

| (Note 2)                                             | Adapter absent                                 |                                                                  |       |     | 50                 | μA    |

| DATE - CCID - CCINI - LV logist Current              | Adapter absent                                 |                                                                  |       |     | 20                 |       |

| BATT + CSIP + CSIN + LX Input Current (Note 2)       | V <sub>BATT</sub> = 16.8V                      | Charger shutdown                                                 |       |     | 20                 | μΑ    |

|                                                      | V <sub>BATT</sub> = 2V to 19V, adapter present |                                                                  |       |     | 500                |       |

| LDO Output Voltage                                   | 8.0V < V <sub>DCIN</sub> < 26V                 | , no load                                                        | 5.15  |     | 5.55               | V     |

| LDO Load Regulation                                  | 0 < I <sub>LDO</sub> < 40mA                    |                                                                  |       |     | 200                | mV    |

| LDO UVLO Threshold                                   |                                                |                                                                  | 3.2   |     | 5.0                | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{DCIN} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 16.8V$ ,  $V_{VCTL} = V_{AA}$ ,  $V_{ISET} = 1V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                  | CONDITIONS                                                       | MIN      | TYP M | ٩X  | UNITS |

|--------------------------------------------|------------------------------------------------------------------|----------|-------|-----|-------|

| REFERENCES                                 |                                                                  | •        |       |     |       |

| VAA Output Voltage                         | Ιναα = 50μΑ                                                      | 4.18     | 4.    | 22  | V     |

| VAA UVLO Threshold                         | V <sub>AA</sub> falling                                          |          | 3     | .9  | V     |

| ACIN                                       |                                                                  | <u>.</u> |       |     | •     |

| ACIN Threshold                             |                                                                  | 2.058    | 2.    | 142 | V     |

| ACIN Threshold Hysteresis                  |                                                                  | 10       | 3     | 0   | mV    |

| ACOK                                       |                                                                  |          |       |     |       |

| ACOK Sink Current                          | V <del>ACOK</del> = 0.4V, V <sub>ACIN</sub> = 1.5V               | 6        |       |     | mA    |

| SWITCHING REGULATOR                        |                                                                  |          |       |     |       |

| DHI Off-Time K Factor                      | V <sub>DCIN</sub> = 19V, V <sub>BATT</sub> = 10V                 | 0.029    | 0.0   | )41 | µs/V  |

| Cycle-by-Cycle Current-Limit Sense Voltage | VCSIP - VCSIN                                                    | 105      | 1     | 15  | mV    |

| DHI Resistance High                        | I <sub>DLO</sub> = 10mA                                          |          |       | 3   | Ω     |

| DHI Resistance Low                         | $I_{DLO} = -10mA$                                                |          | 1.    | 75  | Ω     |

| DLO Resistance High                        | I <sub>DLO</sub> = 10mA                                          |          |       | 3   | Ω     |

| DLO Resistance Low                         | $I_{DLO} = -10mA$                                                |          |       | 7   | Ω     |

| ADAPTER DETECTION                          |                                                                  |          |       |     |       |

| Adapter Absence-Detect Threshold           | VDCIN - VBATT, VDCIN falling                                     | +70      | + 1   | 70  | mV    |

| Adapter Detect Threshold                   | V <sub>DCIN</sub> - V <sub>BATT</sub> , V <sub>DCIN</sub> rising | +320     | +6    | 20  | mV    |

| Adapter Switch Charge-Pump Frequency       |                                                                  | 180      | 2     | 20  | Hz    |

| Adapter Switch Charge Bump Refresh Bules   | DLO                                                              | 0.04     | 0     | .2  | 110   |

| Adapter Switch Charge-Pump Refresh Pulse   | DHI                                                              | 0.07     | 0     | .3  | μs    |

Note 1: Accuracy does not include errors due to external resistance tolerances.

Note 2: Adapter present conditions are tested at V<sub>DCIN</sub> = 19V and V<sub>BATT</sub> = 16.8V. Adapter absent conditions are tested at V<sub>DCIN</sub> = 16V, V<sub>BATT</sub> = 16.8V.

\_\_\_\_\_\_MIXI/M

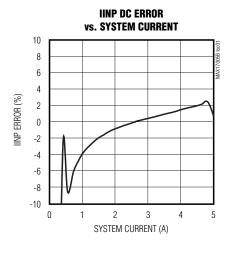

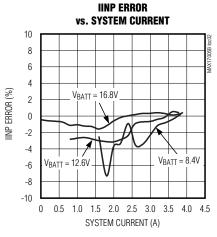

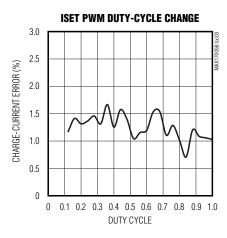

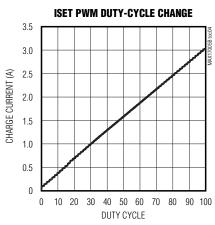

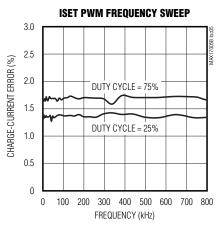

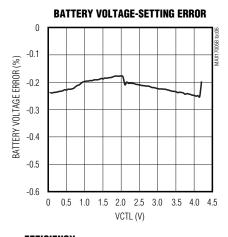

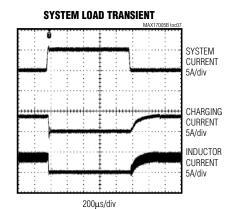

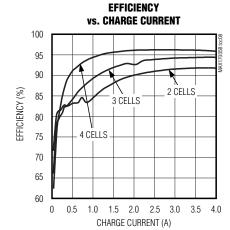

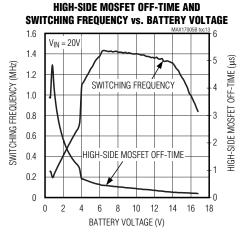

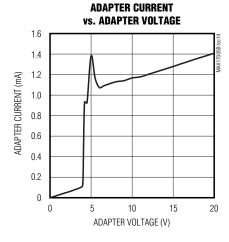

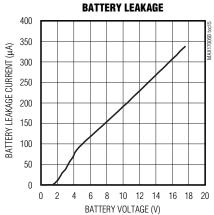

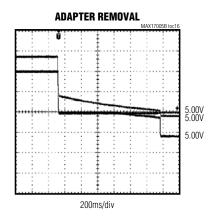

### Typical Operating Characteristics

(Circuit of Figure 1, adapter = 19V, battery = 10V, ISET = 1.05V, VCTL = AGND, TA = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(Circuit of Figure 1, adapter = 19V, battery = 10V, ISET = 1.05V, VCTL = AGND, T<sub>A</sub> = +25°C, unless otherwise noted.)

### **Pin Description**

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DCIN    | Charger Bias Supply Input. Bypass DCIN with a 1µF capacitor to PGND.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2   | AGND    | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | CSIP    | Output Current-Sense Positive Input. Connect a current-sense resistor from CSIP to CSIN.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4   | CSIN    | Output Current-Sense Negative Input                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5   | IINP    | Input Current-Monitor Output. IINP sources the current proportional to the current sensed across CSSP and CSSN. The transconductance from (CSSP - CSSN) to IINP is 2.8µA/mV. See the <i>Analog Input Current-Monitor Output</i> section to configure the current monitor for a particular gain setting.                                                                                                                                                                                          |

| 6   | BATT/FB | Battery Voltage Feedback Input. For the MAX17015B, connect a resistor voltage-divider from the battery output to FB (see Figure 1).                                                                                                                                                                                                                                                                                                                                                              |

| 7   | ACOK    | AC Detect Output. This open-drain output is high impedance when ACIN is lower than $V_{AA}/2$ . Connect a $10k\Omega$ pullup resistor from LDO to $\overline{ACOK}$ .                                                                                                                                                                                                                                                                                                                            |

| 8   | CSSP    | Input Current Sense for Positive Input. Connect a current-sense resistor from CSSP to CSSN.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9   | CSSN    | Input Current-Sense Negative Input                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10  | ISET    | Dual Mode™ Input for Setting Maximum Charge Current. ISET can be configured either with a resistor voltage-divider or with a PWM signal from 128Hz to 500kHz. If there is no clock edge within 20ms, ISET defaults to analog input mode. Pull ISET to AGND to shut down the charger. In the MAX17015B, when the adapter is absent, drive ISET above 1V to enable IINP during battery discharge. When the adapter is reinserted, ISET must be released to the correct control level within 300ms. |

| 11  | PGND    | Power Ground Connection for MOSFET Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12  | DLO     | Low-Side Power-MOSFET Driver Output. Connect to low-side n-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 13  | LDO     | Linear-Regulator Output. LDO provides the power to the MOSFET drivers. LDO is the output of the 5.4V linear regulator supplied from DCIN. Bypass LDO with a 4.7µF ceramic capacitor from LDO to PGND.                                                                                                                                                                                                                                                                                            |

| 14  | BST     | High-Side Driver Supply. Connect a 0.68µF capacitor from BST to LX.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 15  | DHI     | High-Side Power-MOSFET Driver Output. Connect to high-side n-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16  | LX      | High-Side Driver Source Connection. Connect a 0.68µF capacitor from BST to LX.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 17  | ACIN    | AC Adapter Detect Input. ACIN is the input to an uncommitted comparator.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 18  | VAA     | 4.2V Voltage Reference and Device Power-Supply Input. Bypass V <sub>AA</sub> with a 1μF capacitor to AGND.                                                                                                                                                                                                                                                                                                                                                                                       |

| 19  | CC      | Voltage Regulation Loop-Compensation Point. Connect a 0.01µF capacitor from CC to AGND.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 20  | VCTL    | Battery Voltage Adjust Input. VCTL sets the number of cells and adjusts the voltage per cell. The adjustment range is 4.2V to 4.4V per cell. See the Setting Charge Voltage section.                                                                                                                                                                                                                                                                                                             |

| _   | BP      | Backside Paddle. Connect the backside paddle to analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Dual Mode is a trademark of Maxim Integrated Products, Inc.

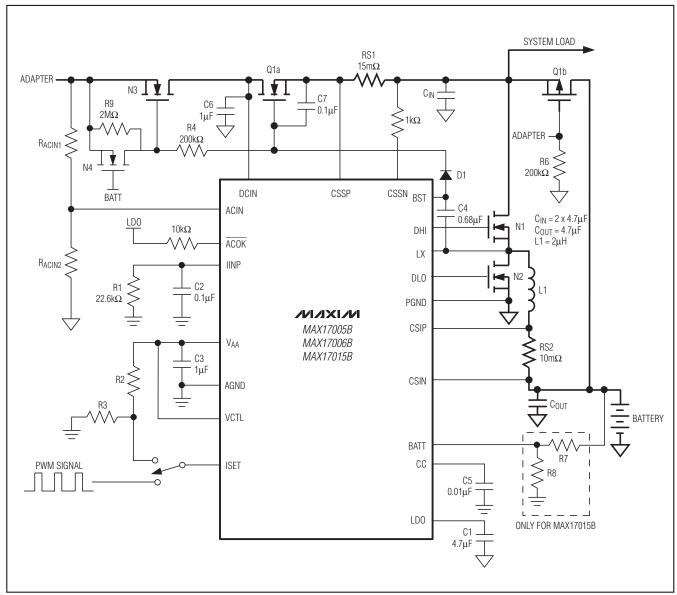

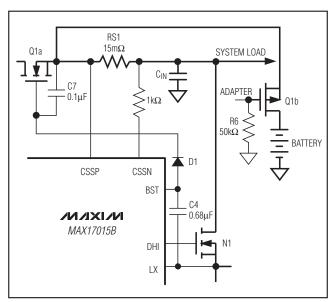

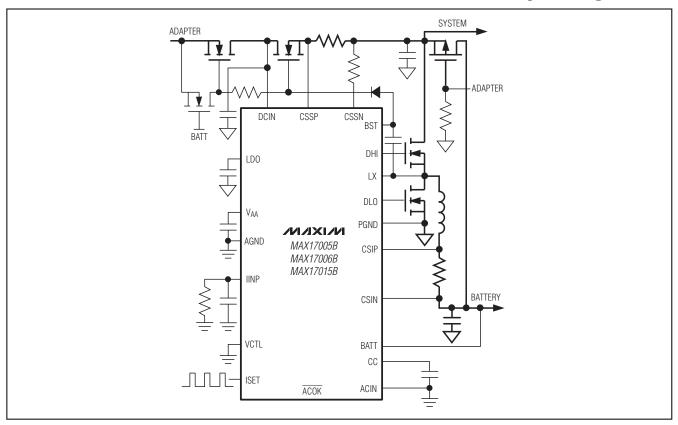

Figure 1. Typical Operating Circuit

### **Detailed Description**

The MAX17005B/MAX17006B/MAX17015B include all the functions necessary to charge Li+, NiMH, and NiCd batteries. An all n-channel synchronous-rectified stepdown DC-DC converter is used to implement a precision constant-current, constant-voltage charger. The charge current and input current-limit sense amplifiers have low-input offset errors (250µV typ), allowing the use of small-value sense resistors.

The MAX17005B/MAX17006B/MAX17015B use a new thermally optimized high-frequency architecture. With this new architecture, the switching frequency is adjusted to control the power dissipation in the high-side MOSFET. Benefits of the new architecture include reduced output capacitance and inductance, resulting in smaller PCB area and lower cost.

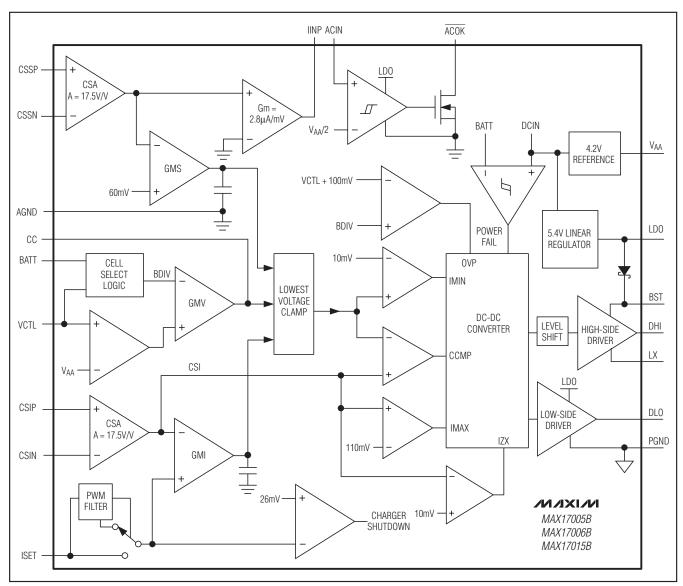

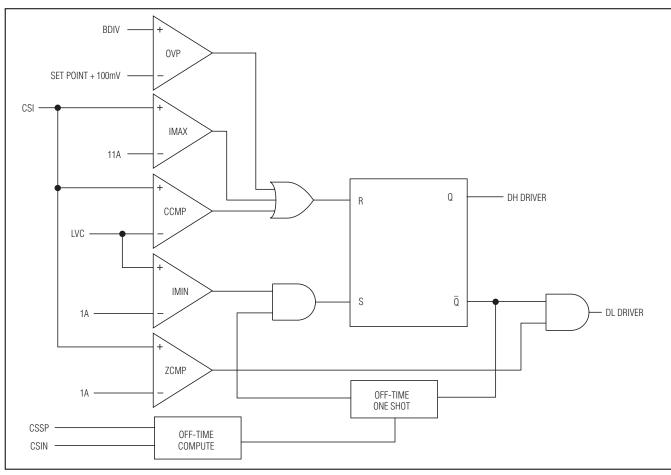

Figure 2. Functional Diagram

The MAX17005B/MAX17006B/MAX17015B feature a voltage-regulation loop (CCV) and two current-regulation loops (CCI and CCS). The loops operate independently of each other. The CCV voltage-regulation loop monitors BATT to ensure that its voltage never exceeds the voltage set by VCTL. The CCI battery charge current-regulation loop monitors current delivered to BATT to ensure that it never exceeds the current limit set by ISET. The charge current-regulation loop is in control as long as the battery voltage is below the set point. When the battery voltage reaches its set point, the voltage-

regulation loop takes control and maintains the battery voltage at the set point. A third loop (CCS) takes control and reduces the charge current when the adapter current exceeds the input current limit.

The MAX17005B/MAX17006B/MAX17015B have single-point compensation. The two current loops are internally compensated while the voltage loop is compensated with a capacitor at CC pin. A functional diagram is shown in Figure 2.

#### **Setting Charge Voltage**

The VCTL input adjusts the battery-output voltage, VBATT, and determines the number of cells. For 3- and 4-cell applications, use the MAX17005B; for 2- and 3-cell applications, use the MAX17006B. Use the MAX17015B to adjust the cell number and set the cell voltage with a resistive voltage-divider from the output. Based on the version of the part, the number of cells and the level of VCTL should be set as in Table 1.

Table 1. Cell Configuration

| VERSION   | NO. OF CELLS | LEVEL                     |

|-----------|--------------|---------------------------|

| MAX17005B | 3            | 2.4V < VCTL < 4.2V        |

| MAX17005B | 4            | 0 < VCTL < 1.8V           |

| MAX17006B | 2            | 0 < VCTL < 1.8V           |

| MAX17006B | 3            | 2.4V < VCTL < 4.2V        |

| MAX17015B | Sets FB      | VCTL = AGND or VCTL = VAA |

The MAX17005B/MAX17006B support from 4.2V/cell to 4.4V/cell, whereas the MAX17015B supports minimum 2.1V. The maximum voltage is determined with the dropout performance of IC. When the required voltage falls outside the range available with the MAX17005B or MAX17006B, the MAX17015B should be used.

The charge-voltage regulation for the MAX17005B and MAX17006B is calculated with the following equations:

$$V_{CELL} = V_{AA} + \frac{V_{AA} - V_{VCTL}}{6}$$

for 3-cell selection of MAX17005B and MAX17006B, 4.2V > VCTL > 2.4V:

$$V_{CELL} = V_{AA} + \frac{V_{VCTL}}{6}$$

for 2- or 4-cell selection of MAX17006B or MAX17005B, respectively, 0 < VCTL < 1.8V. Connect VCTL to GND or to  $V_{AA}$  for default 4.2V/cell battery-voltage setting.

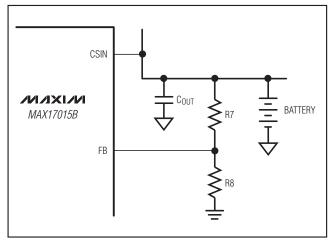

For the MAX17015B, connect VCTL to GND to set the FB regulation point to 2.1V. The charge-voltage regulation is calculated with the following equation:

$$V_{CHG\_REG} = V_{FB\_SETPOINT} \times \frac{R8 + R7}{R8}$$

There are two constraints in choosing R7 and R8. The resistors cannot be too small since they discharge the battery, and they cannot be too large because FB pin consumes less than  $1\mu A$  of input bias current. Pick R8 to be approximately  $10k\Omega$  and then calculate R7.

FB regulation error (±0.5% max) and the tolerance of R7 and R8 both contribute to the error on the battery voltage. Use 0.1% feedback resistors for best accuracy. Figure 3 shows the MAX17015B charge-voltage regulation feedback network.

#### **Setting Charge Current**

The voltage at ISET determines the voltage across current-sense resistor RS2. ISET can accept either analog or digital inputs. The full-scale differential voltage between CSIP and CSIN is 80mV (8A for RS2 =  $10m\Omega$ ) for the analog input, and 60mV (6A for RS2 =  $10m\Omega$ ) for the digital PWM input.

When the MAX17005B/MAX17006B/MAX17015B power up and the charger is ready, if there is no clock edge within 20ms, the circuit assumes ISET is an analog input, and disables the PWM filter block. To configure the charge current, force the voltage on ISET according to the following equation:

$$I_{CHG} = \frac{240 \text{mV}}{\text{RS2}} \times \frac{V_{ISET}}{V_{AA}}$$

The input range for ISET is from 0 to  $V_{AA}/2$ . To shut down the charger, pull ISET below 26mV.

If there is a clock edge on ISET within 20ms, the PWM filter is enabled and ISET accepts digital PWM input. The PWM filter has a DAC with 8-bit resolution that corresponds to equivalent VCSIP-CSIN steps.

Figure 3. MAX17015B Charge-Voltage Regulation Feedback Network

The PWM filter accepts the digital signal with a frequency from 128Hz to 500kHz. Zero duty cycle shuts down the MAX17005B/MAX17006B/MAX17015B, and 99.5% duty cycle corresponds to full scale (60mV) across CSIP and CSIN.

Choose a current-sense resistor (RS2) to have a sufficient power-dissipation rating to handle the full-charge current. The current-sense voltage can be reduced to minimize the power-dissipation period. However, this can degrade accuracy due to the current-sense amplifier's input offset (0.25mV typ). See *Typical Operating Characteristics* to estimate the charge-current accuracy at various set points.

#### **Setting Input-Current Limit**

The total input current, from a wall adapter or other DC source, is the sum of the system supply current and the current required by the charger. When the input current exceeds the set input-current limit, the controller decreases the charge current to provide priority to system load current. System current normally fluctuates as portions of the system are powered up or down. The input-current-limit circuit reduces the power requirement of the AC wall adapter, which reduces adapter cost. As the system supply rises, the available charge current drops linearly to zero. Thereafter, the total input current can increase without limit.

The total input current is the sum of the device supply current, the charger input current, and the system load current. The total input current can be estimated as follows:

$$I_{INPUT} = I_{LOAD} + \frac{I_{CHARGE} \times V_{BATTERY}}{V_{IN} \times \eta}$$

where  $\eta$  is the efficiency of the DC-to-DC converter (typically 85% to 95%).

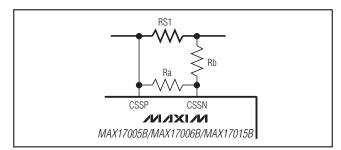

In the MAX17005B/MAX17006B/MAX17015B, the voltage across CSSP and CSSN is constant at 60mV. Choose the current-sense resistor, RS1, to set the input current limit. For example, for 4A input current limit, choose RS1 =  $15m\Omega$ . For the input current-limit settings, which cannot be achievable with standard sense resistor values, use a resistive voltage-divider between CSSP and CSSN to tune the setting (Figure 4).

$$I_{INPUT\_LIMIT} = \frac{60mV}{RS1} \times (1 + \frac{R_B}{R_A})$$

To minimize power dissipation, first choose RS1 according to the closest available value. For convenience, choose Ra =  $6k\Omega$  and calculate Rb from the above equation.

Choose a current-sense resistor (RS1) to have a sufficient power rating to handle the full system current. The current-sense resistor can be reduced to improve efficiency, but this degrades accuracy due to the current-sense amplifier's input offset (0.15mV typ). See *Typical Operating Characteristics* to estimate the input current-limit accuracy at various set points.

#### **Automatic Power-Source Selection**

The MAX17005B/MAX17006B/MAX17015B use an external charge pump to drive the gate of an n-channel adapter selection switch (N3 and Q1a). In Figure 1, when the adapter is present, BST is biased 5V above VADAPTER so that N3 and Q1a are on, and Q1b is off. As long as the adapter is present, even though the charger is off, the power stage forces a refresh pulse to the BST charge pump every 5ms.

When the adapter voltage is removed, the charger stops generating BST refresh pulses and N4 forces N2 off, Q1b turns on and supplies power to the system from the battery.

In Figure 1, D1 must have low forward-voltage drop and low reverse-leakage current to ensure sufficient gate drive at N3 and Q1a. A 100mA, low reverse-leakage Schottky diode is the right choice.

#### **Analog Input Current-Monitor Output**

Use IINP to monitor the system-input current, which is sensed across CSSP and CSSN. The voltage at IINP is proportional to the input current:

$$I_{INPUT} = \frac{V_{IINP}}{RS1 \times G_{IINP} \times R_{IINP}}$$

where I<sub>INPUT</sub> is the DC current supplied by the AC adapter, G<sub>IINP</sub> is the transconductance of the sense amplifier (2.8mA/V typ), and R<sub>IINP</sub> is the resistor connected between IINP and ground. Typically, IINP has a 0 to 3.5V output-voltage range. Leave IINP unconnected when not used.

Figure 4. Input Current-Limit Fine Tuning

Figure 5. Current-Monitoring Design Battery Discharge

IINP can also be used to monitor battery discharge current (see Figure 5). In the MAX17015B, when the adapter is absent, drive ISET above 2.4V to enable IINP during battery discharge. When the adapter is reinserted, ISET must be released to the correct control level within 300ms.

#### **AC Adapter Detection**

The MAX17005B/MAX17006B/MAX17015B include a hysteretic comparator that detects the presence of an AC power adapter. When ACIN is lower than 2.1V, the open-drain  $\overline{ACOK}$  output becomes high impedance. Connect a  $10k\Omega$  pullup resistance between LDO and  $\overline{ACOK}$ . Use a resistive voltage-divider from the adapter's output to the ACIN pin to set the appropriate detection threshold. Select the resistive voltage-divider so that the voltage on ACIN does not to exceed its absolute maximum rating (6V).

#### LDO Regulator and VAA

An integrated low-dropout (LDO) linear regulator provides a 5.4V supply derived from DCIN, and delivers over 40mA of load current. Do not use the LDO to external loads greater than 10mA. The LDO powers the gate drivers of the n-channel MOSFETs. See the MOSFET Drivers section. Bypass LDO to PGND with a 4.7μF ceramic capacitor. VAA is 4.2V reference supplied by DCIN. VAA biases most of the control circuitry, and should be bypassed to GND with a 1μF or greater ceramic capacitor.

#### **Operating Conditions**

The MAX17005B/MAX17006B/MAX17015B have the following operating states:

- Adapter Present: When DCIN is greater than 8.7V, the controller detects the adapter. In this condition, both the LDO and VAA turn on and battery charging is allowed:

- a) Charging: The total MAX17005B/MAX17006B/ MAX17015B quiescent current when charging is 3mA (max) plus the current required to drive the MOSFETs.

- b) **Not Charging:** To disable charging, drive ISET below 26mV. When the adapter is present and charging is disabled, the total adapter quiescent current is less than 1.5mA and the total battery quiescent current is less than 60μA. The charge pump still operates.

- Adapter Absent (Power Fail): When V<sub>DCIN</sub> is less than V<sub>CSIN</sub> + 120mV, the DC-DC converter is in dropout. The charger detects the dropout condition and shuts down.

The MAX17005B/MAX17006B/MAX17015B allow charging under the following conditions:

- DCIN > 7.5V, LDO > 4V, VAA > 3.1V

- VDCIN > VCSIN + 420mV (300mV falling hysteresis)

- V<sub>ISET</sub> > 45mV or PWM detected

#### **DC-DC Converter**

The MAX17005B/MAX17006B/MAX17015B employ a synchronous step-down DC-DC converter with an n-channel high-side MOSFET switch and an n-channel low-side synchronous rectifier. The charger features a controlled inductor current-ripple architecture, current-mode control scheme with cycle-by-cycle current limit. The controller's off-time (tOFF) is adjusted to keep the high-side MOSFET junction temperature constant. In this way, the controller switches faster when the high-side MOSFET has available thermal capacity. This allows the inductor current ripple and the output-voltage ripple to decrease so that smaller and cheaper components can be used. The controller can also operate in discontinuous conduction mode for improved light-load efficiency.

Figure 6. DC-DC Converter Functional Diagram

The operation of the DC-to-DC controller is determined by the following five comparators as shown in the functional diagram in Figures 2 and 6:

- The IMIN comparator triggers a pulse in discontinuous mode when the accumulated error is too high.

IMIN compares the control signal (LVC) against 10mV (referred at VCSIP VCSIN). When LVC is less than this threshold, DHI and DLO are both forced low. Indirectly, IMIN sets the peak inductor current in discontinuous mode.

- The CCMP comparator is used for current-mode regulation in continuous-conduction mode. CCMP compares LVC against the inductor current. The high-side MOSFET on-time is terminated when the CSI voltage is higher than LVC.

- The IMAX comparator provides a secondary cycleby-cycle current limit. IMAX compares CSI to 110mV (corresponding to 11A when RS2 = 10mΩ).

The high-side MOSFET on-time is terminated when the current-sense signal exceeds 11A. A new cycle cannot start until the IMAX comparator's output goes low.

- The ZCMP comparator provides zero-crossing detection during discontinuous conduction. ZCMP compares the current-sense feedback signal to 1A (RS2 = 10mΩ). When the inductor current is lower than the 1A threshold, the comparator output is high, and DLO is turned off.

- The OVP comparator is used to prevent overvoltage at the output due to battery removal. OVP compares BATT against the VCTL. When BATT is 100mV/cell above the set value, the OVP comparator output goes high, and the high-side MOSFET on-time is terminated. DHI and DLO remain off until the OVP condition is removed.

#### CC, CCI, CCS, and LVC Control Blocks

The MAX17005B/MAX17006B/MAX17015B control input current (CCS control loop), charge current (CCI control loop), or charge voltage (CC control loop), depending on the operating condition. The three control loops, CC, CCI, and CCS are brought together internally at the lowest voltage clamp (LVC) amplifier. The output of the LVC amplifier is the feedback control signal for the DC-DC controller. The minimum voltage at the CC, CCI, or CCS appears at the output of the LVC amplifier and clamps the other control loops to within 0.3V above the control point. Clamping the other two control loops close to the lowest control loop ensures fast transition with minimal overshoot when switching between different control loops (see the Compensation section). The CCS and CCI loops are compensated internally, and the CC loop is compensated externally.

#### **Continuous-Conduction Mode**

With sufficiently large charge current, the MAX17005B/MAX17006B/MAX17015Bs' inductor current never crosses zero, which is defined as continuous-conduction mode. The controller starts a new cycle by turning on the high-side MOSFET and turning off the low-side MOSFET. When the charge-current feedback signal (CSI) is greater than the control point (LVC), the CCMP comparator output goes high and the controller initiates the off-time by turning off the high-side MOSFET and turning on the low-side MOSFET. The operating frequency is governed by the off-time and is dependent upon VCSIN and VDCIN.

The on-time can be determined using the following equation:

$$t_{ON} = \frac{L \times I_{RIPPLE}}{V_{DCIN} - V_{CSIN}}$$

where:

$$I_{RIPPLE} = \frac{V_{CSIN} \times t_{OFF}}{L}$$

The switching frequency can then be calculated:

$$f_{SW} = \frac{1}{t_{ON} + t_{OFF}}$$

At the end of the computed off-time, the controller initiates a new cycle if the control point (LVC) is greater than 10mV (VCSIP - VCSIN referred), and the charge current is less than the cycle-by-cycle current limit. Restated another way, IMIN must be high, IMAX must be low, and OVP must be low for the controller to initiate a new cycle. If the peak inductor current exceeds IMAX comparator threshold or the output voltage exceeds the OVP threshold, then the on-time is terminated. The cycle-by-cycle current limit effectively protects against overcurrent and short-circuit faults.

If during the off-time the inductor current goes to zero, the ZCMP comparator output pulls high, turning off the low-side MOSFET. Both the high- and low-side MOSFETs are turned off until another cycle is ready to begin. ZCOMP causes the MAX17005B/MAX17006B/MAX17015B to enter into the discontinuous conduction mode (see the *Discontinuous Conduction* section).

#### **Discontinuous Conduction**

The MAX17005B/MAX17006B/MAX17015B can also operate in discontinuous conduction mode to ensure that the inductor current is always positive. The MAX17005B/MAX17006B/MAX17015B enter discontinuous conduction mode when the output of the LVC control point falls below 10mV (referred at VCSIP - VCSIN). For RS2 = 10m $\Omega$ , this corresponds to a peak inductor current of 1A.

In discontinuous mode, a new cycle is not started until the LVC voltage rises above IMIN. Discontinuous mode operation can occur during conditioning charge of overdischarged battery packs, when the charge current has been reduced sufficiently by the CCS control loop, or when the charger is in constant-voltage mode with a nearly full battery pack.

#### Compensation

The charge voltage, charge current, and input current-limit regulation loops are compensated separately. The charge current and input current-limit loops, CCI and CCS, are compensated internally, whereas the charge voltage loop is compensated externally at CC.

For CC compensation, connect a  $0.01\mu F$  capacitor at CC. The crossover frequency occurs at:

$$f_{CO\_CV} = GM_{OUT} \times G_{MV} \times \frac{1.7k\Omega}{2\pi \times C_{OUT}}$$

where:

$GMV = 0.125\mu A/mV$

GMOUT = 5A/V

\_\_ /N/XI/M

#### **MOSFET Drivers**

The DHI and DLO outputs are optimized for driving moderate-sized power MOSFETs. The MOSFET drive capability is the same for both the low-side and high-sides switches. This is consistent with the variable duty factor that occurs in the notebook computer environment where the battery voltage changes over a wide range. There must be a low-resistance, low-inductance path from the DLO driver to the MOSFET gate to prevent shoot-through. Otherwise, the sense circuitry in the MAX17005B/MAX17006B interpret the MOSFET gate as off while there is still charge left on the gate. Use very short, wide traces measuring 10 to 20 squares or fewer (1.25mm to 2.5mm wide if the MOSFET is 25mm from the device).

The high-side driver (DHI) swings from LX to 5V above LX (BST) and has a typical impedance of  $1.5\Omega$  sourcing and  $0.8\Omega$  sinking. The strong high-side MOSFET driver eliminates most of the power dissipation due to switching losses. The low-side driver (DLO) swings from LDO to ground and has a typical impedance of  $3\Omega$  sinking and  $3\Omega$  sourcing. This helps prevent DLO from being pulled up when the high-side switch turns on due to capacitive coupling from the drain to the gate of the low-side MOSFET. This places some restrictions on the MOSFETs that can be used. Using a low-side MOSFET with smaller gate-to-drain capacitance can prevent these problems.

### Design Procedure MOSFET Selection

Choose the n-channel MOSFETs according to the maximum required charge current. The MOSFETs must be able to dissipate the resistive losses plus the switching losses at both VDCIN(MIN) and VDCIN(MAX).

For the high-side MOSFET, the worst-case resistive power losses occur at the maximum battery voltage and minimum supply voltage:

$$PD_{COND}(High Side) = \frac{V_{CSIN(MAX)}}{V_{DCIN(MIN)}} \times I_{CHG}^{2} \times R_{DS(ON)}$$

Generally, a low gate-charge high-side MOSFET is preferred to minimize switching losses. However, the RDS(ON) required to stay within package power dissipation often limits how small the MOSFET can be. The optimum occurs when the switching losses equal the conduction losses. High-side switching losses do not usually become an issue until the input is greater than approximately 15V. Calculating the power dissipation in N1 due to switching losses is difficult since it must allow for difficult quantifying factors that influence the

turn-on and turn-off times. These factors include the internal gate resistance, gate charge, threshold voltage, source inductance, and PCB layout characteristics. The following switching-loss calculation provides only a very rough estimate and is no substitute for breadboard evaluation, preferably including a verification using a thermocouple mounted on N1:

$$PD_{SW}(HS) = \frac{1}{2} \times t_{TRANS} \times V_{CSSP} \times I_{CHG} \times f_{SW}$$

where  $t_{\mbox{\scriptsize TRANS}}$  is the drivers transition time and can be calculated as follows:

$$t_{TRANS} = \left(\frac{1}{I_{GSRC}} + \frac{1}{I_{GSNK}}\right) \times \left(Q_{GD} + Q_{GS}\right)$$

IGSRC and IGSNK are the peak gate-drive source/sink current ( $3\Omega$  sourcing and  $0.8\Omega$  sinking, typically). The MAX17005B/MAX17006B/MAX17015B control the switching frequency as shown in the *Typical Operating Characteristics*.

The following is the power dissipated due to high-side n-channel MOSFET's output capacitance (CRSS):

$$PD_{CRSS}(HS) \approx \frac{V^2_{CSSP} \times C_{RSS} \times f_{SW}}{2}$$

The following high-side MOSFET's loss is due to the reverse-recovery charge of the low-side MOSFET's body diode:

$$PD_{QRR}(HS) = \frac{Q_{RR2} \times V_{CSSP} \times f_{SW}}{2}$$

Ignore PDQRR(HS) if a Schottky diode is used parallel to a low-side MOSFET.

The total high-side MOSFET power dissipation is:

$$\begin{split} \text{PD}_{\text{TOTAL}}(\text{HS}) &\approx \text{PD}_{\text{COND}}(\text{HS}) + \text{PD}_{\text{SW}}(\text{HS}) \\ &+ \text{PD}_{\text{CRSS}}(\text{HS}) + \text{PD}_{\text{QRR}}(\text{HS}) \end{split}$$

Switching losses in the high-side MOSFET can become an insidious heat problem when maximum AC adapter voltages are applied. If the high-side MOSFET chosen for adequate RDS(ON) at low-battery voltages becomes hot when biased from VDCIN(MAX), consider choosing another MOSFET with lower parasitic capacitance.

For the low-side MOSFET (N2), the worst-case power dissipation always occurs at maximum input voltage:

$$PD_{COND}(LS) = \left(1 - \frac{V_{CSIN(MIN)}}{V_{CSSP(MAX)}}\right) \times I_{CHG}^{2} \times R_{DS(ON)}$$

The following additional loss occurs in the low-side MOSFET due to the body diode conduction losses:

$$PD_{BDY}(LS) = 0.05 \times I_{PFAK} \times 0.4V$$

The total power low-side MOSFET dissipation is:

$$PD_{TOTAL}(LS) \approx PD_{COND}(LS) + PD_{BDY}(LS)$$

These calculations provide an estimate and are not a substitute for breadboard evaluation, preferably including a verification using a thermocouple mounted on the MOSFET.

#### **Inductor Selection**

The selection of the inductor has multiple trade-offs between efficiency, transient response, size, and cost. Small inductance is cheap and small, and has a better transient response due to higher slew rate; however, the efficiency is lower because of higher RMS current. High inductance results in lower ripple so that the need of the output capacitors for output-voltage ripple goes low.

The MAX17005B/MAX17006B/MAX17015B combine all the inductor trade-offs in an optimum way by controlling switching frequency. High-frequency operation permits the use of a smaller and cheaper inductor, and consequently results in smaller output ripple and better transient response.

The charge current, ripple, and operating frequency (off-time) determine the inductor characteristics. For optimum efficiency, choose the inductance according to the following equation:

$$L = \frac{k \times V_{IN}^{2}}{4 \times I_{CHG} \times LIR_{MAX}}$$

where k = 35 ns/V.

For optimum size and inductor current ripple, choose LIRMAX = 0.4, which sets the ripple current to 40% the charge current and results in a good balance between inductor size and efficiency. Higher inductor values decrease the ripple current. Smaller inductor values save cost but require higher saturation current capabilities and degrade efficiency.

Inductor L1 must have a saturation current rating of at least the maximum charge current plus 1/2 the ripple current ( $\Delta I_L$ ):

$$ISAT = ICHG + (1/2) \Delta IL$$

The ripple current is determined by:

$$\Delta I_{L} = \frac{k \times V_{IN}^{2}}{4L}$$

#### **Input Capacitor Selection**

The input capacitor must meet the ripple current requirement (I<sub>RMS</sub>) imposed by the switching currents. Nontantalum chemistries (ceramic, aluminum, or OS-CON) are preferred due to their resilience to power-up and surge currents:

$$IRMS = ICHG \times \left( \frac{\sqrt{V_{CSIN} \times (V_{DCIN} - V_{CSIN})}}{V_{DCIN}} \right)$$

The input capacitors should be sized so that the temperature rise due to ripple current in continuous conduction does not exceed approximately 10°C. The maximum ripple current occurs at 50% duty factor or  $V_{DCIN} = 2 \times V_{BATT}$ , which equates to 0.5 x ICHG. If the application of interest does not achieve the maximum value, size the input capacitors according to the worst-case conditions.

#### **Output Capacitor Selection**

The output capacitor absorbs the inductor ripple current and must tolerate the surge current delivered from the battery when it is initially plugged into the charger. As such, both capacitance and ESR are important parameters in specifying the output capacitor as a filter and to ensure the stability of the DC-to-DC converter (see the *Compensation* section.) Beyond the stability requirements, it is often sufficient to make sure that the output capacitor's ESR is much lower than the battery's ESR. Either tantalum or ceramic capacitors can be used on the output. Ceramic devices are preferable because of their good voltage ratings and resilience to surge currents. Choose the output capacitor based on:

$$C_{OUT} = \frac{I_{RIPPLE}}{f_{SW} \times 8 \times \Delta V_{CSIN}} \times k_{CAP-BIAS}$$

Choose k<sub>CAP-BIAS</sub> is a derating factor of 2 for typical 25V-rated ceramic capacitors.

For fsw = 800kHz, IRIPPLE = 1A, and to get  $\Delta V_{BATT}$  = 70mV, choose  $C_{OUT}$  as 4.7 $\mu F$ .

If the internal resistance of battery is close to the ESR of the output capacitor, the voltage ripple is shared with the battery and is less than calculated.

### **Applications Information**

#### **Setting Input Current Limit**

The input current limit should be set based on the current capability of the AC adapter and the tolerance of the input current limit. The upper limit of the input current threshold should never exceed the adapter's minimum available output current. For example, if the adapter's output current rating is  $5A \pm 10\%$ , the input current limit should be selected so that its upper limit is less than  $5A \times 0.9 = 4.5A$ . Since the input current-limit accuracy of the MAX17005B/MAX17006B/MAX17015B is  $\pm 3\%$ , the typical value of the input current limit should be set at  $4.5A/1.03 \approx 4.36A$ . The lower limit for input current must also be considered. For chargers at the low end of the specification, the input current limit for this example could be  $4.36A \times 0.95$  or approximately 4.14A.

#### **Layout and Bypassing**

Bypass DCIN with a  $0.1\mu F$  ceramic capacitor to ground (Figure 1). N1 and N2 protect the MAX17005B/MAX17006B/MAX17015B when the DC power source input is reversed. Bypass VAA, CSSP, and LDO as shown in Figure 1.

Good PCB layout is required to achieve specified noise immunity, efficiency, and stable performance. The PCB layout designer must be given explicit instructions—preferably, a sketch showing the placement of the power switching components and high current routing. Refer to the PCB layout in the MAX17005B/MAX17006B/MAX17015B Evaluation Kit for examples. A ground plane is essential for optimum performance. In most applications, the circuit is located on a multilayer board, and full use of the four or more copper layers is recommended. Use the top layer for high-current connections, the bottom layer for quiet connections, and the inner layers for an uninterrupted ground plane.

Use the following step-by-step guide:

- 1) Place the high-power connections first, with their grounds adjacent:

- a) Minimize the current-sense resistor trace lengths, and ensure accurate current sensing with Kelvin connections.

- b) Minimize ground trace lengths in the high-current paths

- c) Minimize other trace lengths in the high-current paths.

- d) Use > 5mm wide traces in the high-current paths.

- e) Connect C<sub>IN</sub> to high-side MOSFET (10mm max length).

- f) Minimize the LX node (MOSFETs, rectifier cathode, inductor (15mm max length)). Keep LX on one side of the PCB to reduce EMI radiation.