#### CMOS 8-Bit Microcontroller

# TMP88CH47N, TMP88CH47F

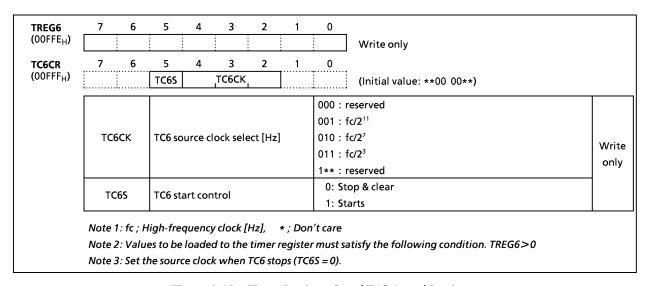

TMP88CH47N is high-speed and high-function 8-bit single-chip microcomputers whose built-in features include large-capacity RAM, multi-function timer/counter, and 10-bit AD converter, serial interface (UART/I2C bus). They are equipped with 3 phase brushless DC sensorless/sensor motor control, and AC motor inverter control.

| Part No.   | ROM       | RAM       | Package           | OTP MCU    |

|------------|-----------|-----------|-------------------|------------|

| TMP88CH47N | 16K bytes | E13 bytes | P-SDIP42-600-1.78 | TMP88PH47N |

| TMP88CH47F | 16K bytes | 512 bytes | P-QFP-1414-0.80D  | TMP88PH47F |

#### **Features**

- ▶8-bit single-chip microcomputer TLCS-870/X series microcomputer

- Interrupt sources: 23 (5 external, 18 Internal)

- ◆I/O ports: 34 pins

- Large-current output: 8 pins (typ. 20 mA), LED direct drive

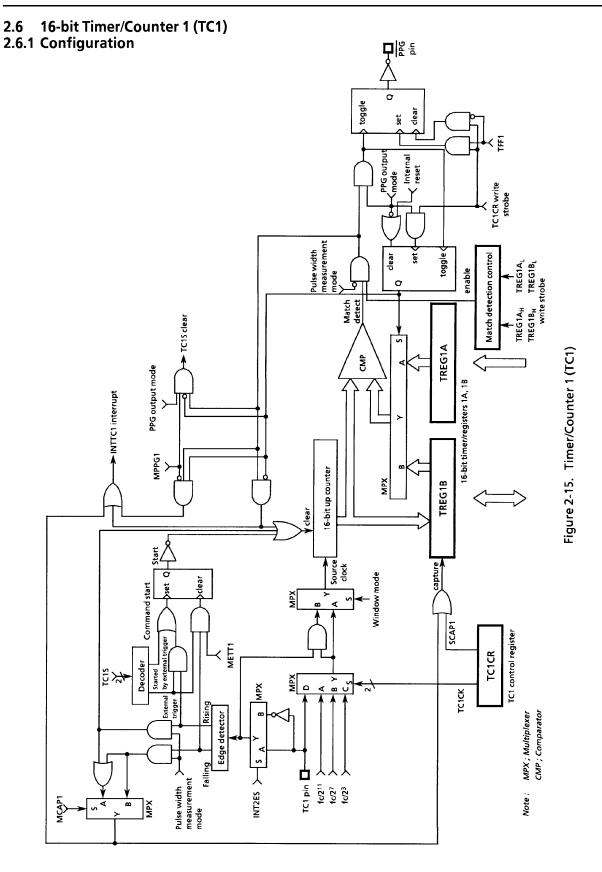

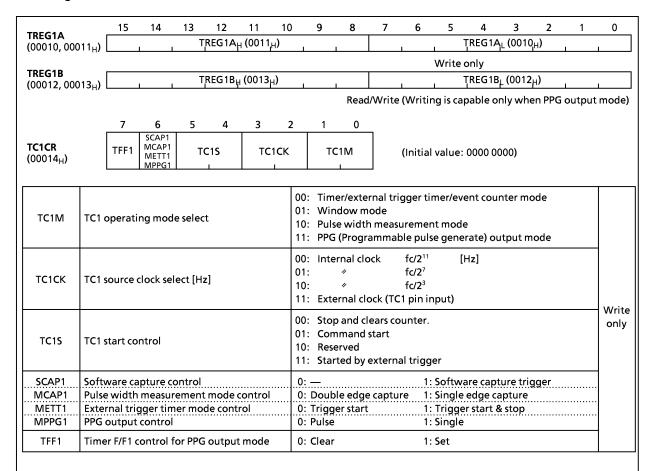

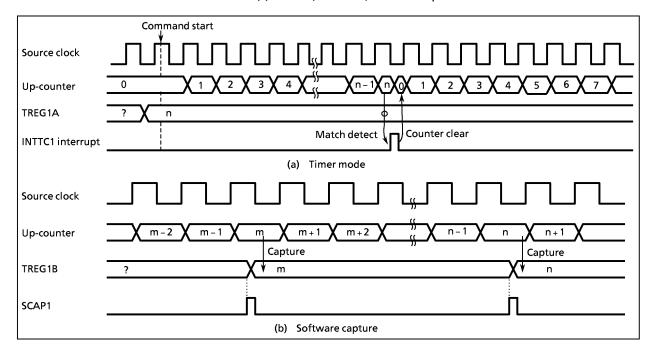

- ▶ 16-bit timer/counter: 2 channels

- Timer, event counter, programmable pulse generator (PPG) output, pulse width measurement, external trigger timer, window mode

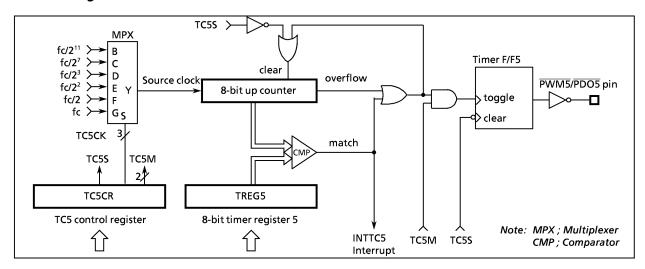

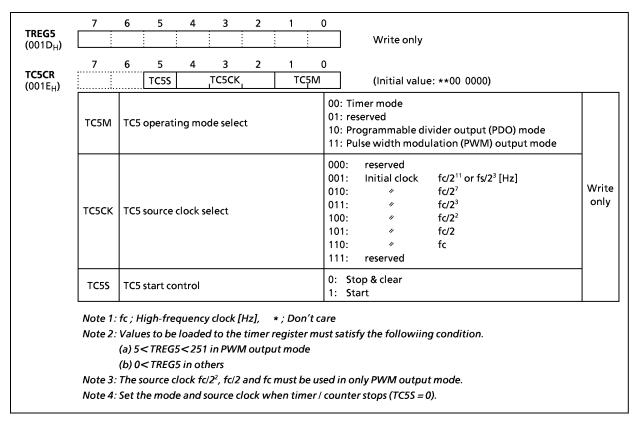

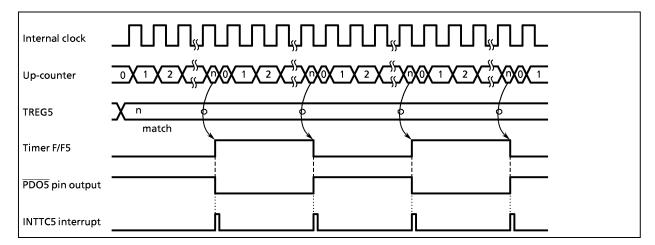

- ◆8-bit Timer/Counter: 1 channel

- Timer capture (pulse width measurement), programmable divider output (PDO) mode

- ◆Time base timer (interrupt frequency: 1 to 16384 Hz)

- ◆Watchdog timer

- Divider output function (frequency: 1 to 8 kHz)

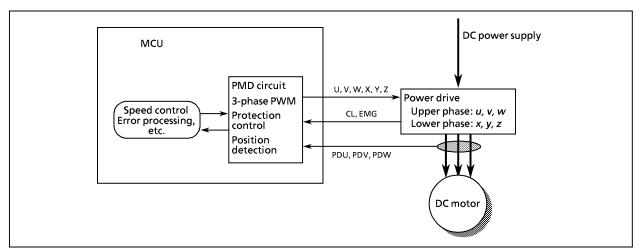

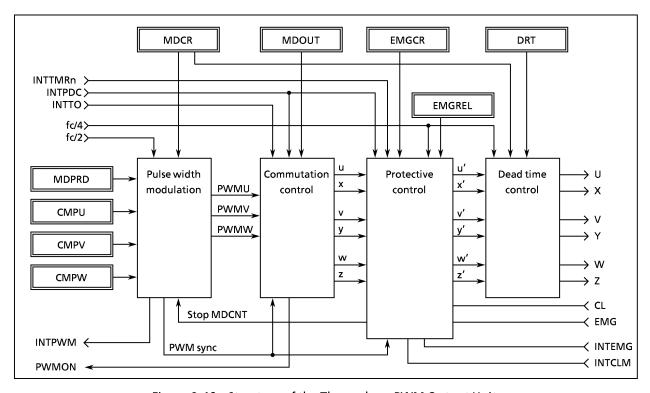

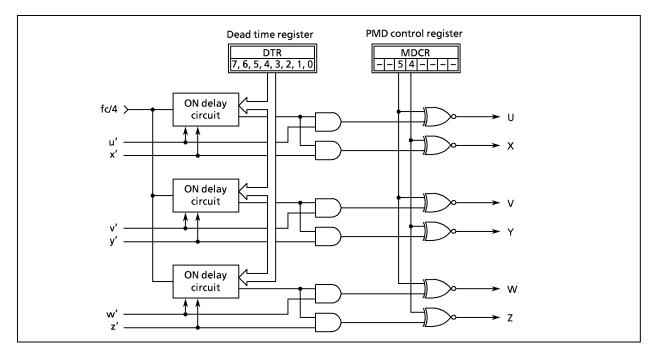

- Programmable motor driver (PMD): 1 channel

- Rotor position: minimum resolution of 250 ns for detecting rotor position

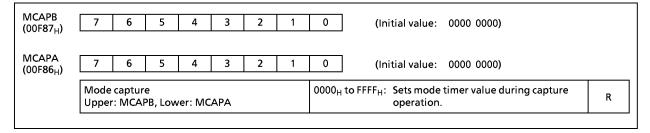

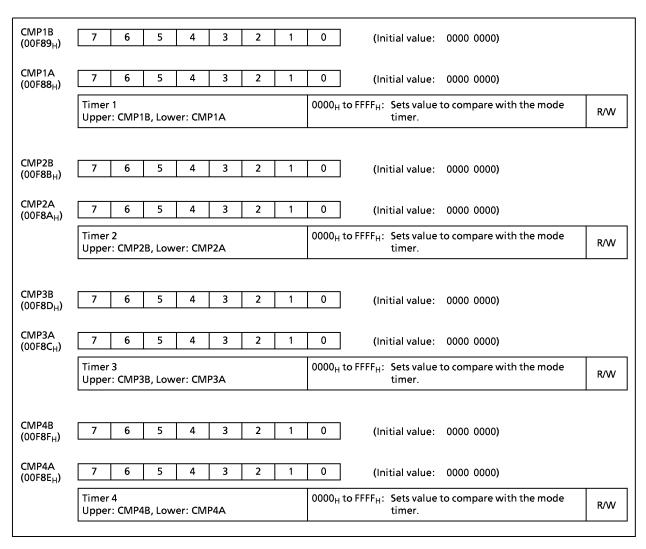

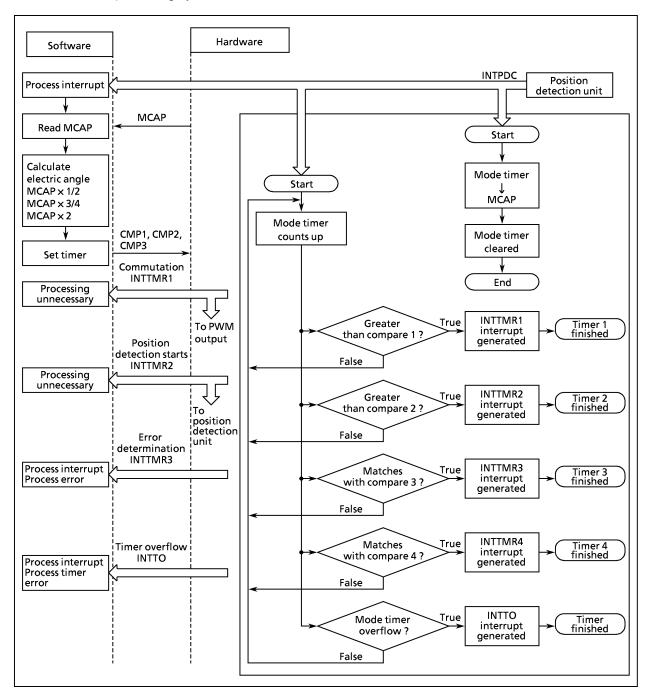

- Motor control timer, timer capture function

- Overload protection function DC overload protection function AC overload protection function

(Can halt counter in 3-phase PWM output circuit)

- Protection circuit for malfunction (urgent halt)

- Automatic direction change, automatic position detection start

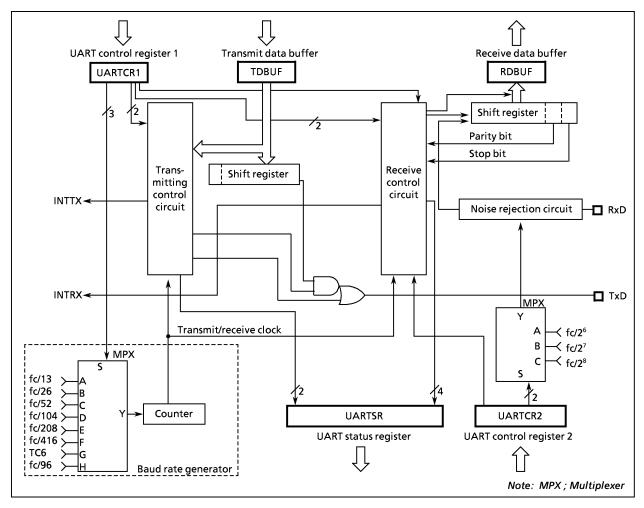

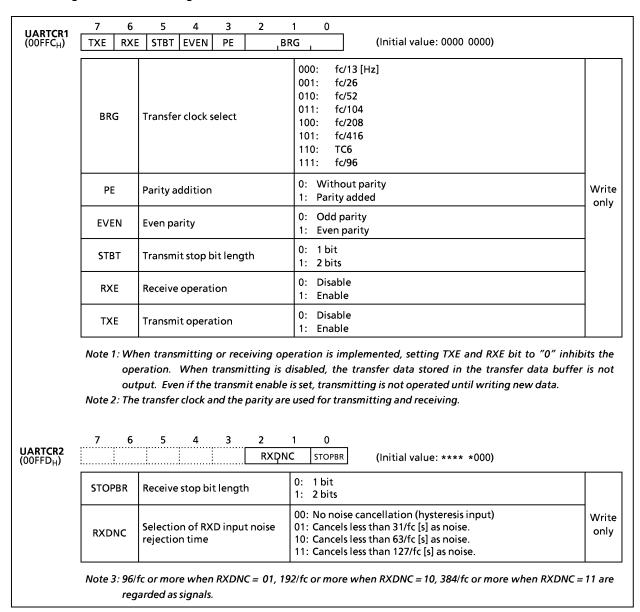

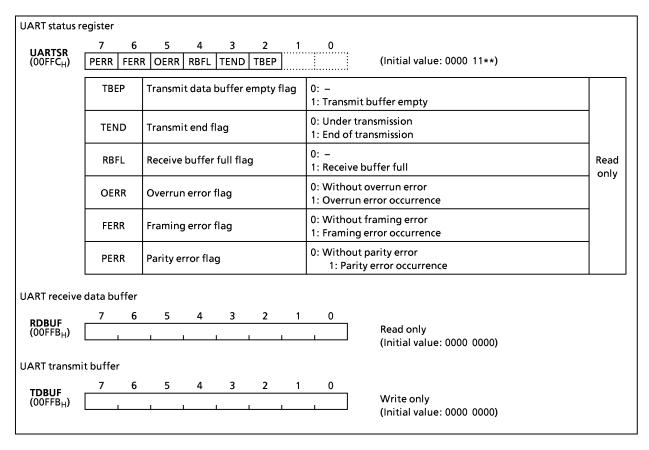

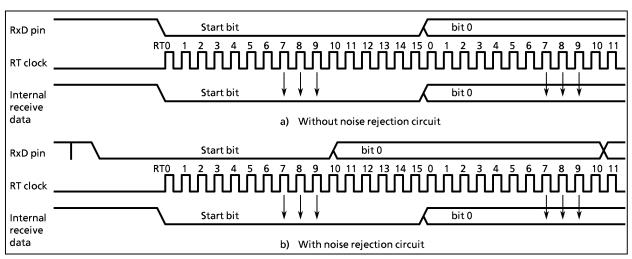

- Serial interface

- 8-bit SIO/I<sup>2</sup>C bus

- Universal asynchronous receiver transmitter (UART)

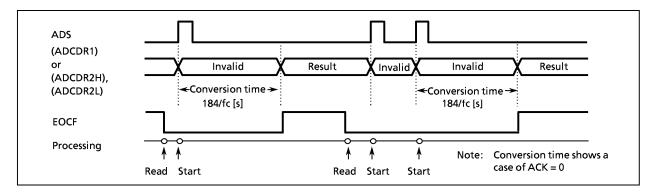

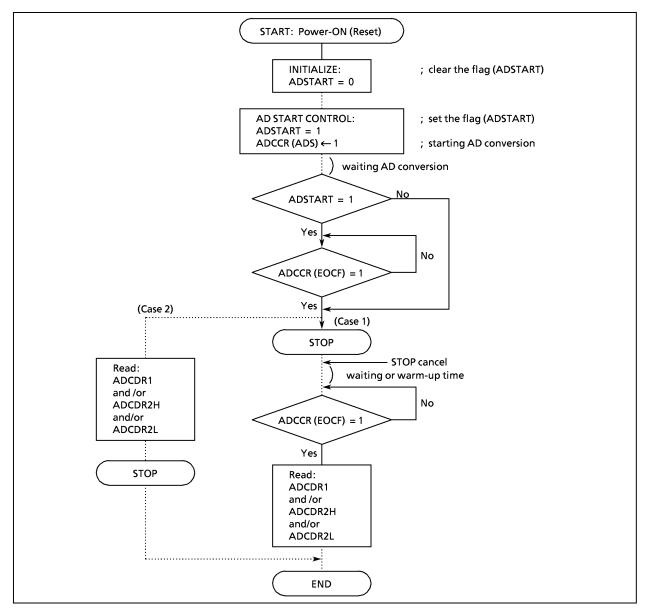

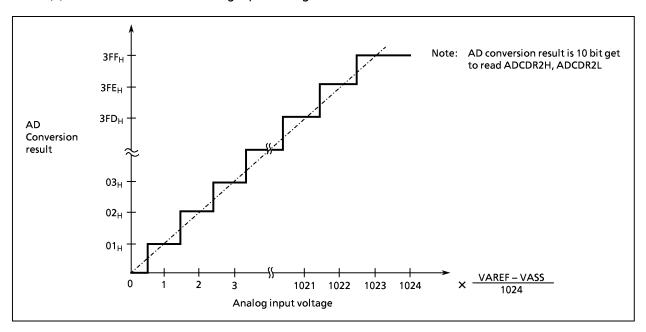

- 10-bit successive approximation type AD converter

- Analog input: 8 channels

- Conversion time: 11.5  $\mu$ s/46  $\mu$ s (at 16 MHz operation)

- Low power dissipation operation (2 modes)

- STOP mode: Stops oscillation (battery or capacitor backup). Port output hold or high impedance selectable

- IDLE mode: Stops CPU but continues operation of peripheral hardware. Released by interrupt (restarts CPU)

- ◆Operating voltage: 4.5 to 5.5 V at 16 MHz operation

980910EBP2

TMP88CH47N

TMP88PH47N

TMP88CH47F

TMP88PH47F

- 980910EBP2

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

Purchase of TOSHIBA I<sup>2</sup> C components conveys a license under the Philips I<sup>2</sup> C Patent Rights to use these components in an I<sup>2</sup> C system, provided that the system conforms to the I<sup>2</sup> C Standard Specification as defined by Philips.

> 3-47-1 1999-09-29

P-SDIP42-600-1.78

P-QFP44-1414-0.80D

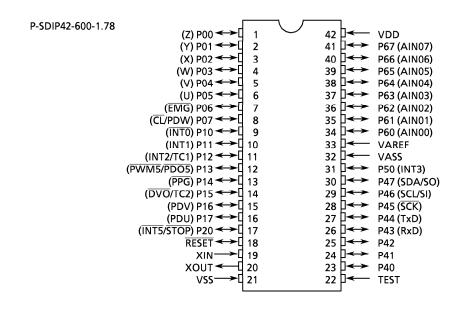

# **Pin Assignments**

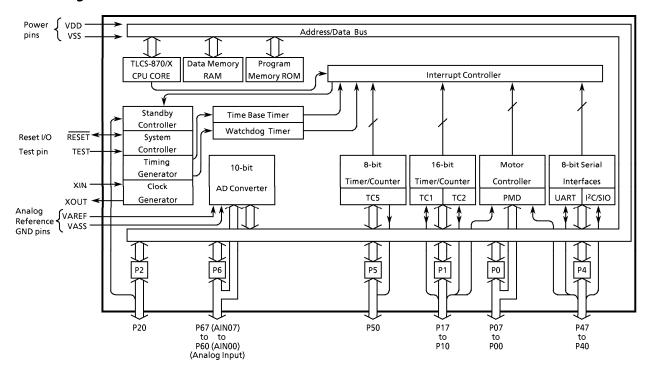

# **Block Diagram**

# **Pin Function**

| Pin Name                | 1/0                 | Fun-                                                                                                                     | ction                                                                                                                                |  |  |

|-------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P07 (CL/PDW) P06 (EMG)  | ··· I/O (Input)     | 8-bit programmable I/O port (tri state) Input or output specifiable in units of bits.  When using pins for motor control | Overload protection input /motor control circuit W-phase position detection input  Motor control circuit malfunction detection input |  |  |

| P05 (U)                 |                     | circuit, set accordingly using POCR, then MDCR to 1.                                                                     | Motor control circuit U-/V-/W-phase                                                                                                  |  |  |

| P04 (V)                 | I/O (Output)        |                                                                                                                          | output                                                                                                                               |  |  |

| P03 (W)                 |                     |                                                                                                                          | Natarasatal signification (N. 17 Jahren                                                                                              |  |  |

| P02 (X)                 |                     |                                                                                                                          | Motor control circuit X-/ Y-/Z-phase output                                                                                          |  |  |

| P01 (Y)                 | I/O (Output)        |                                                                                                                          |                                                                                                                                      |  |  |

| P00 (Z)                 |                     |                                                                                                                          |                                                                                                                                      |  |  |

| P17 (PDU)               | 1/0 (1-1-1)         | 8-bit programmable I/O port (tri state) Input or output specifiable units of bits.                                       | Motor control circuit U-phase position detection input                                                                               |  |  |

| P16 (PDV)               | ··· I/O (Input)     | When using pins for motor control circuit, timer/counter input, or external                                              | Motor control circuit V-phase position detection input                                                                               |  |  |

| P15 (DVO/TC2)           | II/O (Output/Input) | interrupt input, set them to input mode. When using pins for PPG output, divider                                         | Divider output or Timer/Counter 2 input                                                                                              |  |  |

| P14 (PPG)               |                     | output, or PWM output/PDO output, set                                                                                    | Programmable pulse generator output                                                                                                  |  |  |

| P13 (PWM5/PDO5)         | ··· I/O (Output)    | them to output mode.                                                                                                     | PWM5 output/PDO5 output                                                                                                              |  |  |

| P12 (INT2/TC1)          | I/O (Input)         |                                                                                                                          | External interrupt input 2 or<br>Timer/Counter 1 input                                                                               |  |  |

| P11 (INT1)              |                     |                                                                                                                          | External interrupt input 1                                                                                                           |  |  |

| P10 ( <del>INT0</del> ) | <u>"</u> ]          |                                                                                                                          | External interrupt input 0                                                                                                           |  |  |

| Pin Name                      | 1/0              | Function                                                                                                                                                                           |                                                              |  |  |  |

|-------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|

| P20 (INT5/STOP)               | I/O (Input)      | 1-bit I/O port When using pins for input port, external interrupt input, or STOP mode release input, set output latches to 1.                                                      | External interrupt input 5 or STOP mode release signal input |  |  |  |

| P47 (SDA/SO)                  | I/O (I/O/Output) | 8-bit I/O port                                                                                                                                                                     |                                                              |  |  |  |

| P46 (SCL/SI)                  | I/O (I/O/Input)  | When using pins for motor control                                                                                                                                                  | 12C/SIO I/O                                                  |  |  |  |

| P45 ( <del>SCK</del> )        | I/O (I/O)        | circuit input, UART/I <sup>2</sup> C/SIO, set output latches to 1.                                                                                                                 |                                                              |  |  |  |

| P44 (TxD)                     | I/O (Input)      | lateries to 1.                                                                                                                                                                     | UART data input                                              |  |  |  |

| P43 (RxD)                     | I/O (Output)     |                                                                                                                                                                                    | UART data output                                             |  |  |  |

| P42                           |                  |                                                                                                                                                                                    | <u> </u>                                                     |  |  |  |

| P41                           | 1/0              |                                                                                                                                                                                    | <u> </u>                                                     |  |  |  |

| P40                           |                  |                                                                                                                                                                                    | <u> </u>                                                     |  |  |  |

| P50 (INT3)                    | I/O (Input)      | 1-bit input/output port with latch. When using pins for input port, HPWM output, PWM output/PDO output, external interrupt input, or timer/counter input, set output latches to 1. | External interrupt 3 input                                   |  |  |  |

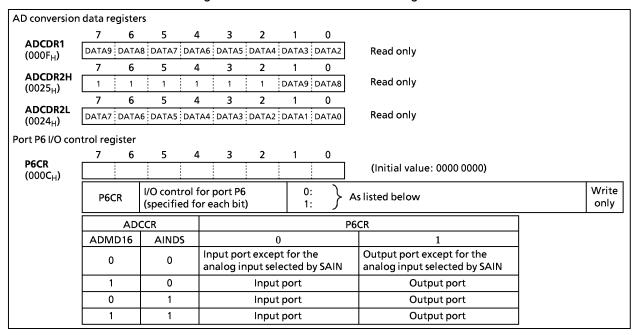

| P67 (AIN07)<br>to P60 (AIN00) | I/O (Input)      | 8-bit programmable I/O port (tri state) Input or output specifiable in units of bits. When using pins for analog input, set to input mode using P6CR and ADCCR.                    | AD converter analog input                                    |  |  |  |

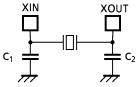

| XIN, XOUT                     | Input, Output    | High-frequency oscillator connecting pins. For external clock input, input to XIN and leave XOUT open.                                                                             |                                                              |  |  |  |

| RESET                         | 1/0              | Reset signal input, watchdog timer output, address trap reset output, system clock reset output                                                                                    |                                                              |  |  |  |

| TEST                          | Input            | Shipment test pin. Fix to "L" level.                                                                                                                                               |                                                              |  |  |  |

| VDD, VSS                      | Davies Supply    | + 5 V, 0 V (GND)                                                                                                                                                                   |                                                              |  |  |  |

| VAREF, VASS                   | Power Supply     | Analog reference voltage for AD conversion. Reference GND.                                                                                                                         |                                                              |  |  |  |

## **Operation**

# 1. CPU Core Functions

The CPU core consists of the CPU, system clock control circuit, and interrupt control circuit. This chapter describes the CPU core, program memory, data memory and the reset circuit.

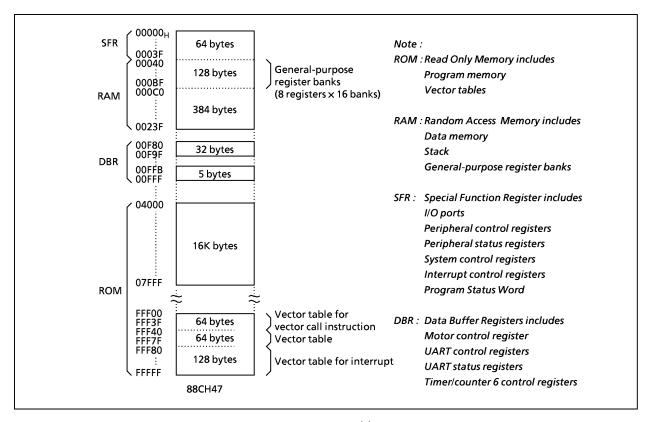

## 1.1 Memory Address Map

The TMP88CH47 memory consists of four blocks: ROM, RAM, special function registers (SFR) and Data buffer registers (DBR). They are all mapped to a 1M-byte address space. Figure 1-1 shows the TMP88CH47 memory address map. There are 16 general-purpose registers mapped to the RAM address space.

Figure 1-1. Memory Address Maps

# 1.2 Program Memory (ROM)

TMP88CH47 contains a 16K-byte program memory (mask ROM) at addresses from 04000 to 07FFF<sub>H</sub>. In addition, contains a 256-byte program memory (mask ROM) at addresses from FFF00 to FFFFF<sub>H</sub>.

## 1.3 Data Memory (RAM)

TMP88CH47 contains a 512-byte RAM at addresses from 00040 to 0023F<sub>H</sub>. The first 128 bytes in RAM (00040 to 000BF<sub>H</sub>) are also used as a general-purpose register bank.

Since the data in data memory become undefined at power on, initialize the RAM using the initialize routine.

Example: Clear RAM (zero-clear the whole RAM except bank 0).

LD HL, 00048H ; Sets start address.

SRAMCLR: LD (HL+), A

DEC BC

JRS F, SRAMCLR

Note: Since the general-purpose registers are allocated to RAM, do not clear RAM at addresses in the current bank. Therefore, in the above example, RAM except bank 0 is cleared.

3-47-6 1999-09-29

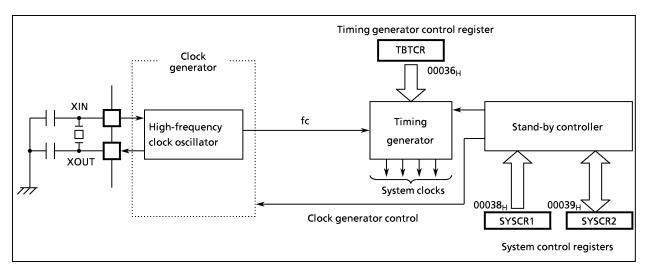

## 1.4 System Clock Control Circuit

The system clock control circuit consists of a clock generator, timing generator, and standby control circuit.

Figure 1-2. System Clock Controller

# 1.4.1 Clock Generator

The clock generator is an oscillator circuit which generates the basic clock pulse used as the system clock supplied to the CPU core and peripheral hardware.

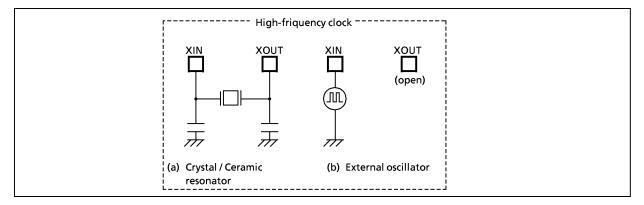

A high-frequency (frequency: fc) clock can be easily obtained by connecting the oscillator to the XIN and XOUT pins. A clock can also be input externally. In this case, input the clock from the XIN pin and leave the XOUT pin open.

Figure 1-3. Example of Resonator Connection

Adjustment of oscillator frequency

Note: Although the basic clock pulse cannot be directly monitored externally by hardware, it is possible to do so by software. That is, output pulses at a certain frequency to the port (for example, DVO), with interrupts and the watchdog timer disabled, then monitor pulses so that the frequency can be adjusted. For a system which requires the oscillator frequency to be adjusted, write a program for the required frequency adjustment.

3-47-7 1999-09-29

### 1.4.2 Timing Generator

The timing generator is a circuit used to generate, based on the basic clock pulse, system clocks supplied to the CPU core and peripheral hardware. The timing generator functions to generate the following:

(1) main system clock

- (5) internal source clock for timer/counter

- (2) divider output (DVO) pulse

- (6) warm-up clock at STOP mode release

- (3) source clock for time base timer

- (4) source clock for watchdog timer

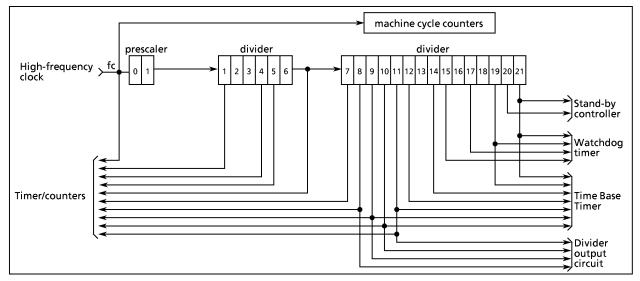

## (1) Configuration of timing generator

The timing generator consists of a 2-step prescaler, 21-step divider, and machine cycle counter. At reset, when STOP mode is entered or released, the prescaler and divider are zero-cleared.

Figure 1-4. Configuration of Timing Generator

Figure 1-5. Timing Generator Control Register

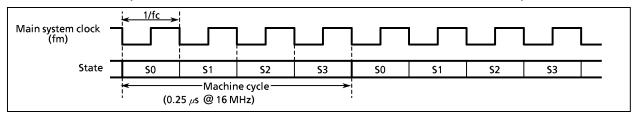

### (2) Machine cycle

Execution of instructions and operation of internal hardware are performed in sync with the system clock.

The minimum unit for instruction execution is called the machine cycle. TLCS-870/X series instructions are classified into 15 types: from 1-cycle instructions to 15-cycle instructions.

A machine cycle consists of four states (S0 to S3). Each state consists of one main system clock.

Figure 1-6. Machine Cycle

## 1.4.3 Standby Control Circuit

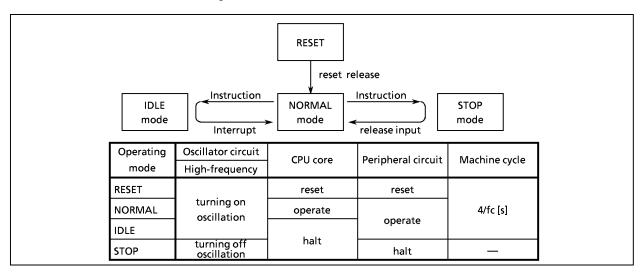

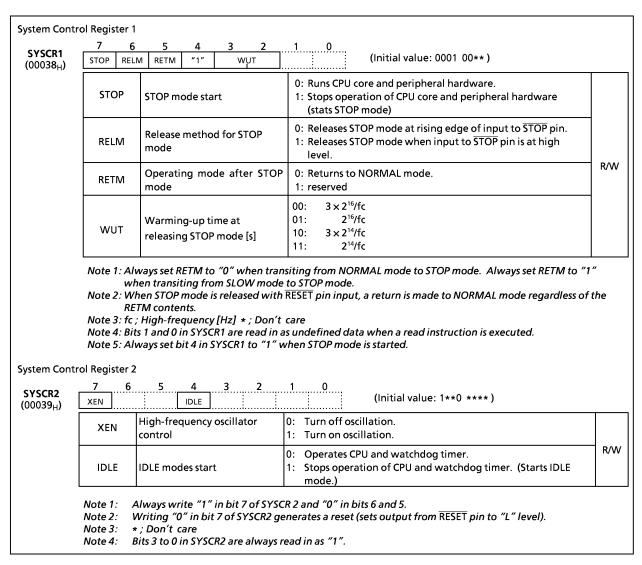

The standby control circuit operates or stops the oscillator circuit for the high-frequency clock. Control the operating mode using the system control register (SYSCR1, SYSCR2). Figure 1-7 is operating mode transition; Figure 1-8 is the control register.

## 1) NORMAL mode

Operates the CPU core and peripheral hardware using the high-frequency clock.

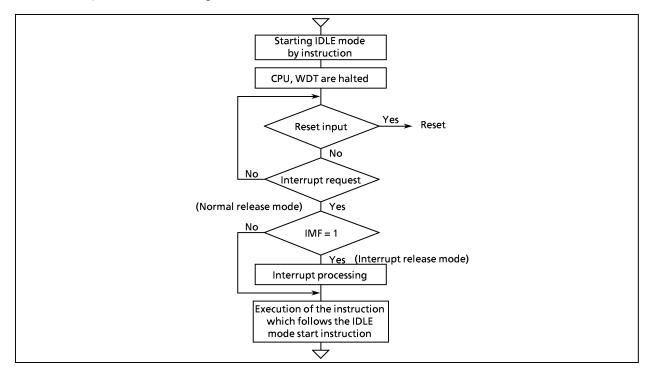

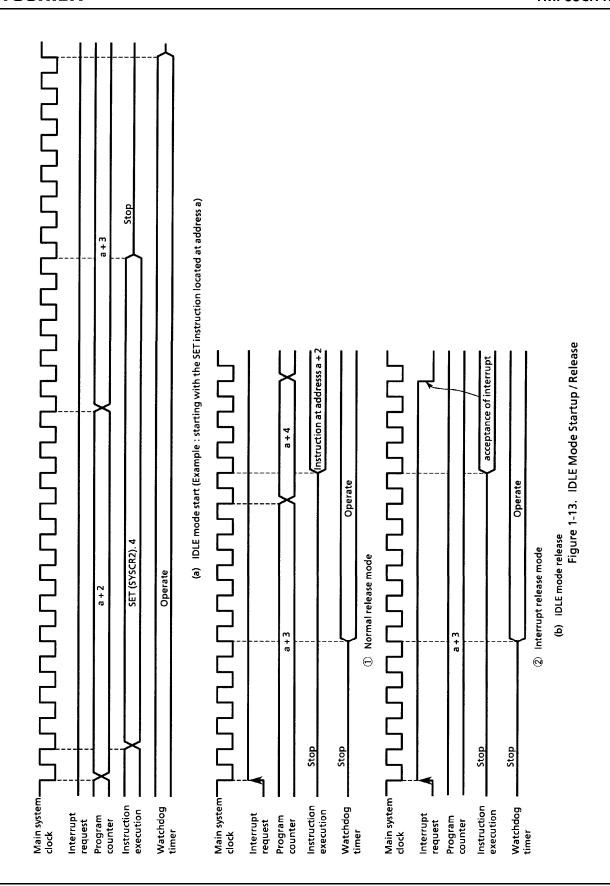

#### 2) IDLE mode

Stops the CPU and watchdog timer but operates peripheral hardware using the high-frequency clock. To start IDLE mode, use system control register 2. Interrupts from the peripheral hardware or external interrupts release IDLE mode and return to NORMAL mode. When IMF (interrupt master enable flag) is set to 1 (interrupt enabled), normal operation returns after interrupt processing. When IMF is set to 0 (interrupt disabled), the system restarts execution of the instruction following the instruction which started IDLE mode.

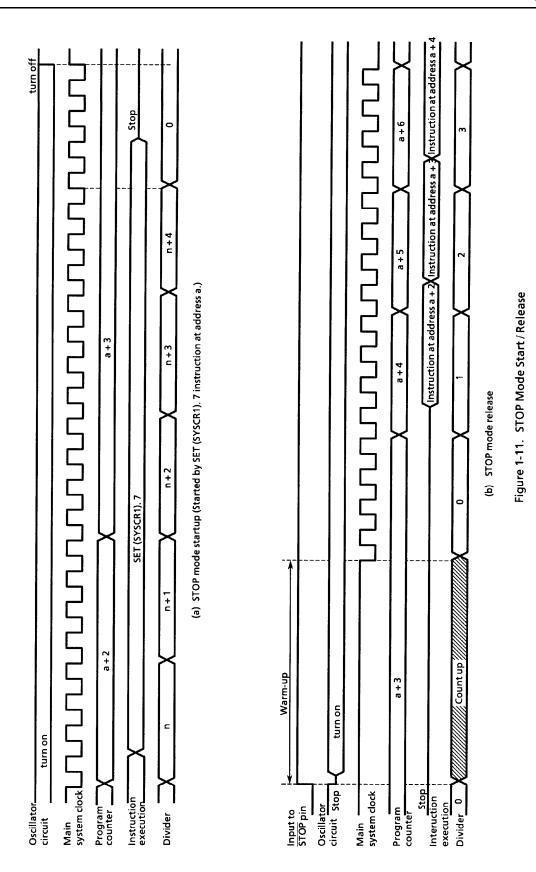

### 3) STOP mode

Stops all operation including the oscillator circuit but holds the internal states immediately before the stop at low power dissipation.

To start STOP mode, use system control register 1. Input to the STOP pin (level or edge selectable) releases STOP mode. After warm-up time elapses, the system restarts execution of the instruction following the instruction which started STOP mode.

Figure 1-7. Operation Mode Transition Diagram

Figure 1-8. System Control Registers

# 1.4.4 Operating Mode Control

### (1) STOP mode

Stop mode is controlled by system control register 1 (SYSCR1) and input to the STOP pin. The STOP pin is also used as P20 or INT5 (external interrupt input 5). Setting STOP (bit 7 in SYSCR1) to 1 activates STOP mode. During STOP mode, the following states are held.

- ① Stops oscillation and stops all internal operation.

- ② The states of data memory, registers, program status word, and port output latches just before entering STOP mode are held.

- 3 Zero-clears the timing generator prescaler and divider.

- The program counter indicates the address for the second instruction from the instruction which stared STOP mode.

For example, [SET (SYSCR1). 7]

STOP mode has two further modes, level and edge. Select one using RELM in system control register 1 (bit 6 in SYSCR1).

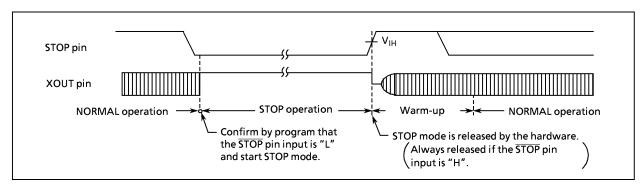

### a. Level-sensitive release mode (RELM = 1)

Releases STOP mode using "H" level input to the STOP pin. Used for capacitor backup at main power off or during long-time battery backup.

When an instruction is executed which uses a "H" level input to the STOP pin to activate STOP mode, processing does not enter STOP mode, but immediately moves to the release sequence (warm-up). To enter STOP mode in level-sensitive release mode, use the program to check that input to the STOP pin is "L" level. Checking can be done in either of the fol "L" ing two ways:

- ① Check P20

- ② Use INT5. (Interrupt is generated at the falling edge of input to the INT5 pin.)

Example 1: Starts STOP mode from NORMAL mode checking port 20.

LD (SYSCR1), 01010000B; Sets to level-sensitive release mode.

SSTOPH: TEST (P2).0; Waits until input to STOP pin becomes

"L" level.

JRS F, SSTOPH

SET (SYSCR1). 7 ; Starts STOP mode.

Example 2: Starts STOP mode from NORMAL mode using INT5.

PINT5: TEST (P2). 0 ; Does not enter STOP mode if input to P20

JRS F, SINT5 "H" level due to noise rejection.

LD (SYSCR1), 01010000B; Sets to level-sensitive release mode.

SET (SYSCR1). 7 ; Starts stop mode.

SINT5: RETI

Figure 1-9. Level-sensitive Release Mode

Note 1: Even if the STOP pin input is "L" after warming up start, the STOP mode is not restarted.

Note 2: In this case of changing to the level-sensitive release mode from the edge-sensitive release mode, the release mode is not switched until a rising edge of the STOP pin input is detected.

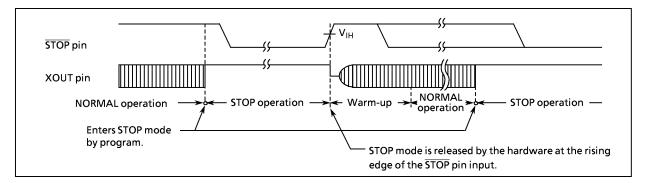

### b. Edge-sensitive release mode (RELM = 0)

Releases STOP mode at the rising edge of input to the STOP pin. Used to repeat a relatively short program at a certain cycle. Input this cycle signal (eg, a clock from the "L" power dissipation oscillator) to the STOP pin. In edge mode, STOP mode is entered even if input to the STOP pin is "H" level.

Example: Enter STOP mode from NORMAL mode.

LD (SYSCR1), 10010000B; Starts STOP mode with edge mode set.

Figure 1-10. Edge-sensitive Release Mode

STOP mode is released in the flowing sequence:

- (1) Starts oscillation.

- (2) To wait until oscillation stabilizes, performs warm-up. During warm-up, internal operation remain stopped. Select one of the four warm-up times using WUT (bits 3 and 2 in SYSCR1) depending on the characteristics of the oscillator.

- (3) After warm-up time elapses, the instruction following the instruction which activated STOP mode is executed. At this time, the timing generator prescaler and divider are zero-cleared.

| WUT | Warming-up Time [ms]    |             |  |  |  |  |  |  |

|-----|-------------------------|-------------|--|--|--|--|--|--|

| 00  | 3 × 2 <sup>16</sup> /fc | ( 12.288 m) |  |  |  |  |  |  |

| 01  | 2 <sup>16</sup> /fc     | ( 4.096 m)  |  |  |  |  |  |  |

| 10  | 3 × 2 <sup>14</sup> /fc | ( 3.072 m)  |  |  |  |  |  |  |

| 11  | 2 <sup>14</sup> /fc     | ( 1 024 m)  |  |  |  |  |  |  |

Table 1-1. Warming-up Time Example (at fc = 16 MHz)

Note: The warming-up time is obtained by dividing the basic clock by the divider: therefore, the warming-up time may include a certain amount of error if there is any fluctuation of the oscillation frequency when STOP mode is released. Thus, the warming-up time must be considered an approximate value.

For immediate ordinary reset, STOP mode can also be released by setting the  $\overline{\text{RESET}}$  pin to "L" level.

Note: STOP mode should not be released when voltage is low. Before releasing STOP mode, increase the supply voltage to the operating voltage. At this time, the RESET pin is at "H" level, which increases along with the supply voltage. If a time constant circuit is externally connected, the increase in the voltage of the input to the RESET pin starts later than that of the supply voltage. If the input voltage drops below the non-inverted "H" level input voltage of the RESET pin (hysteresis input), a reset may be generated.

3-47-12 1999-09-29

3-47-13 1999-09-29

#### (2) IDLE Mode

IDLE mode is controlled by system control register 2 (SYSCR2) and maskable interrupts. During IDLE mode, the following states are held:

- ① CPU and watchdog timer operation stop, but operation of peripheral hardware continues.

- ② The states of data memory, registers, program status word, port output latch immediately before entering IDLE mode are held.

- ③ The program counter holds the address fo the second instruction after the instruction which started IDLE mode.

Example: Start IDLE mode.

SET (SYSCR2), 4

IDLE mode is released by normal release mode or interrupt release mode. Select one using the interrupt master enable flag (IMF). After IDLE mode is released, the mode returns to NORMAL.

Figure 1-12. IDLE Mode

#### a. Normal release mode (when IMF = 0)

IDLE mode is released either by an interrupt source enabled by the interrupt enable flag (EF) or by an external interrupt 0 (INTO) request. Instruction execution restarts from the instruction following the instruction which started IDLE mode. Usually, the interrupt latch (IL) for the interrupt source used for IDLE mode release must be zero-cleared using the load instruction.

### b. Interrupt release mode (when IMF = 1)

IDLE mode is released either by an interrupt source enabled by the interrupt enable flag (EF) or by an external interrupt 0 ( $\overline{\text{INT0}}$ ) request, and interrupt processing starts. After interrupt processing, the instruction following the instruction which started IDLE mode is executed.

For immediate ordinary reset, IDLE mode can also be released by setting the RESET pin to "L" level.

Note: When a watchdog timer interrupt is generated immediately before IDLE mode is started, the watchdog timer interrupt will be processed but IDLE mode will not be started.

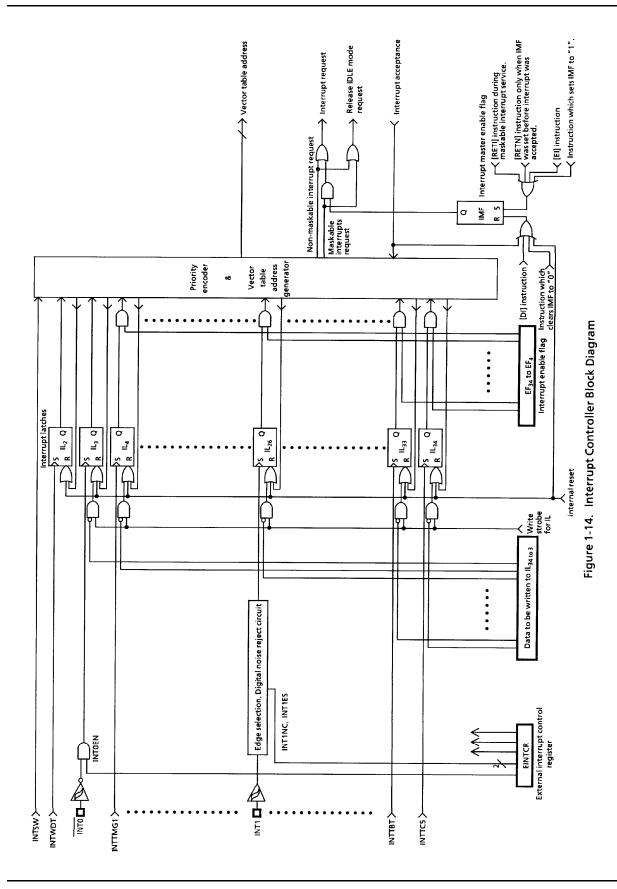

## 1.5 Interrupt Control Circuit

TMP88CH47 supports 23 interrupt sources enabling multiple interrupts with priorities. Two internal interrupts are pseudo non-maskable, the rest are all maskable interrupts.

Interrupt sources are provided with interrupt latches (IL), which hold interrupt requests, and independent vectors. Interrupt latches are set to 1 by the generation of interrupt requests which request the CPU to accept the interrupts. Interrupts are enabled or disabled by program using the interrupt master enable flag (IMF) and interrupt enable flag (EF). If more than one interrupt is generated simultaneously, interrupts are accepted in order of the priority specified by hardware. Figure 1-14 shows the interrupt control circuit.

Table 1-2. Interrupt Sources

|          | lı       | nterrupt source                                   | Enable condition           | Interrupt<br>latch | Vector<br>table<br>address | Priority |

|----------|----------|---------------------------------------------------|----------------------------|--------------------|----------------------------|----------|

| Internal | INTSW    | (Software interrupt)                              | Pseudo non-                | _                  | FFFF8 <sub>H</sub>         | 1        |

| Internal | INTWDT   | (Watchdog timer interrupt)                        | maskable                   | IL <sub>2</sub>    | FFFF4 <sub>H</sub>         | 2        |

| External | INT0     | (External interrupt)                              | IMF = 1, INT0EN = 1        | IL <sub>3</sub>    | FFFF0 <sub>H</sub>         | 3        |

| Internal | INTEMG1  | (CH1 malfunction detect interrupt)                | IMF • EF <sub>4</sub> = 1  | IL <sub>4</sub>    | FFFEC <sub>H</sub>         | 4        |

| Internal | INTT01   | (CH1 mode timer overflow/capture range overwrite) | IMF • EF <sub>6</sub> = 1  | IL <sub>6</sub>    | FFFE4 <sub>H</sub>         | 5        |

| Internal | INTCLM1  | (CH1 current limit interrupt)                     | IMF • EF <sub>8</sub> = 1  | IL <sub>8</sub>    | FFFDC <sub>H</sub>         | 6        |

| Internal | INTPDC1  | (CH1 position detect interrupt)                   | IMF • EF <sub>10</sub> = 1 | IL <sub>10</sub>   | FFFD4 <sub>H</sub>         | 7        |

| Internal | INTPWM1  | (CH1 waveform generator interrupt)                | $IMF \cdot EF_{12} = 1$    | IL <sub>12</sub>   | FFFCC <sub>H</sub>         | 8        |

| External | INT5     | (External interrupt)                              | IMF • EF <sub>15</sub> = 1 | IL <sub>15</sub>   | FFFC0 <sub>H</sub>         | 9        |

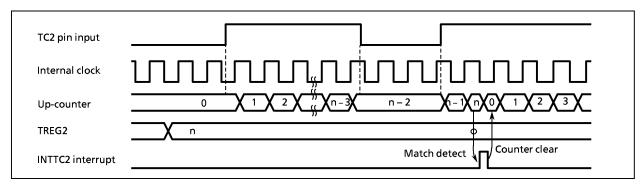

| Internal | INTTC1   | (16-bit TC1 interrupt)                            | IMF · EF <sub>16</sub> = 1 | IL <sub>16</sub>   | FFFBC <sub>H</sub>         | 10       |

| Internal | INTTC2   | (16-bit TC2 interrupt)                            | IMF · EF <sub>17</sub> = 1 | IL <sub>17</sub>   | FFFB8 <sub>H</sub>         | 11       |

| Internal | INTTMR11 | (CH1 timer 1 interrupt)                           | IMF · EF <sub>18</sub> = 1 | IL <sub>18</sub>   | FFFB4 <sub>H</sub>         | 12       |

| Internal | INTTMR21 | (CH1 timer 2 interrupt)                           | IMF · EF <sub>20</sub> = 1 | IL <sub>20</sub>   | FFFAC <sub>H</sub>         | 13       |

| Internal | INTTMR31 | (CH1 timer 3 interrupt)                           | IMF • EF <sub>22</sub> = 1 | IL <sub>22</sub>   | FFFA4 <sub>H</sub>         | 14       |

| Internal | INTTMR41 | (CH1 timer 4 interrupt)                           | IMF · EF <sub>24</sub> = 1 | IL <sub>24</sub>   | FFF9C <sub>H</sub>         | 15       |

| External | INT1     | (External interrupt)                              | IMF · EF <sub>26</sub> = 1 | IL <sub>26</sub>   | FFF94 <sub>H</sub>         | 16       |

| External | INT2     | (External interrupt)                              | IMF · EF <sub>27</sub> = 1 | IL <sub>27</sub>   | FFF90 <sub>H</sub>         | 17       |

| External | INT3     | (External interrupt)                              | IMF · EF <sub>28</sub> = 1 | IL <sub>28</sub>   | FFF8C <sub>H</sub>         | 18       |

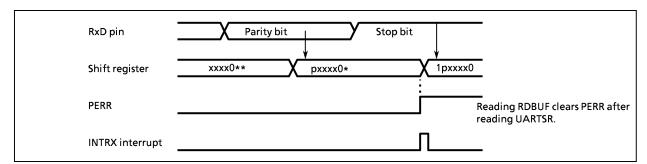

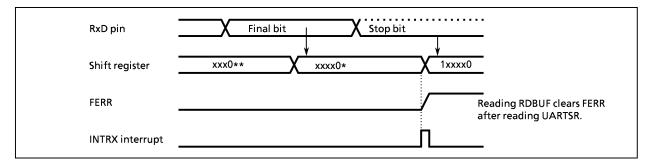

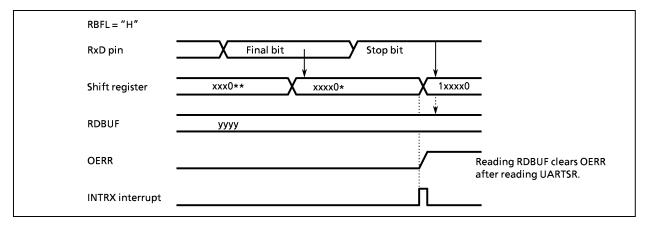

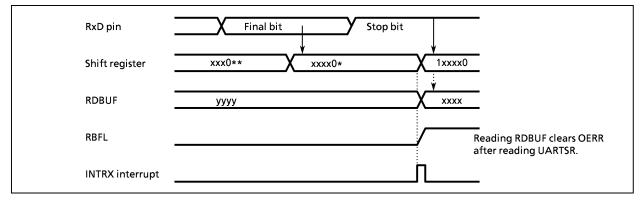

| Internal | INTRX    | (UART receive interrupt)                          | IMF · EF <sub>30</sub> = 1 | IL <sub>30</sub>   | FFF84 <sub>H</sub>         | 19       |

| Internal | INTTX    | (UART transmit interrupt)                         | IMF · EF <sub>31</sub> = 1 | IL <sub>31</sub>   | FFF80 <sub>H</sub>         | 20       |

| Internal | INTSBI   | (Serial bus interface interrupt)                  | IMF ⋅ EF <sub>32</sub> = 1 | IL <sub>32</sub>   | FFF3C <sub>H</sub>         | 21       |

| Internal | INTTBT   | (Timer base timer interrupt)                      | IMF · EF <sub>33</sub> = 1 | IL <sub>33</sub>   | FFF38 <sub>H</sub>         | 22       |

| Internal | INTTC5   | (8-bit TC5 interrupt)                             | IMF · EF <sub>34</sub> = 1 | IL <sub>34</sub>   | FFF34 <sub>H</sub>         | 23       |

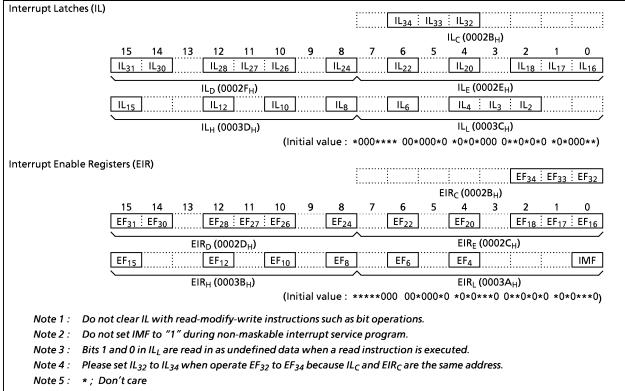

### (1) Interrupt latches (IL<sub>34</sub> to IL<sub>2</sub>)

Latches are provided for all interrupt sources except software interrupts. Generation of an interrupt request sets the latch to 1. If the interrupt is enabled, the CPU is requested to accept the interrupt. Immediately the interrupt is accepted, the interrupt latch is zero-cleared. At reset, interrupt latches are all initialized to 0.

The interrupt latches are allocated to addresses 0003C, 0003D, 0002B, 0002E, and 0002F<sub>H</sub> in SFR. An interrupt latch can be cleared independently by instructions (other than read-modify-write instructions such as bit manipulation and arithmetic instructions). Interrupt requests can be canceled or initialized by program. Note that interrupt latches cannot be set by instruction. Since interrupt latch data can be read, interrupt requests can be tested by software.

```

Example 1: Clear interrupt latch.

```

```

LDW

(ILL), 1110100111101111B

; IL<sub>12</sub>, IL<sub>10</sub>, IL<sub>6</sub>, IL<sub>4</sub>←0

LDW

(ILE), 1111111111111000B

IL_{18} to IL_{16}\leftarrow 0

LD

(ILC), 00010111B

IL<sub>34</sub>, IL<sub>33</sub>←0

Example 2: Read interrupt latch.

WA, (ILL)

W←IL<sub>H</sub>, A←IL<sub>L</sub>

LD

LD

BC, (ILE)

B \leftarrow IL_D, C \leftarrow IL_E

D\leftarrow IL_C

LD

D, (ILC)

Example 3: Test interrupt latch.

TEST

(ILE). 0

; If IL_{16} = 1, jump.

JR

F, SSET

```

### (2) Interrupt enable register (EIR)

Enables or disables interrupt sources except pseudo non-maskable interrupts (software interrupt and watchdog timer interrupt). Pseudo non-maskable interrupts are accepted regardless of the setting in the interrupt enable register. Note that more than one pseudo non-maskable interrupt must not be generated simultaneously.

The interrupt enable register consists of the interrupt master enable flag (IMF) and the interrupt enable flag (EF). EIR is allocated to addresses 0003A, 0003B, 0002B, 0002C, and 0002D<sub>H</sub> in SFR. Data can be read from or written to the interrupt enable register by instructions (including read-modify-write instructions such as the bit manipulation instruction.)

#### 1 Interrupt master enable flag (IMF)

Enables or disables all maskable interrupt requests. If zero-cleared, all maskable interrupt requests are disabled; if set to 1, enabled.

Once an interrupt request is accepted, the interrupt master enable flag is zero-cleared, disabling all subsequent maskable interrupt requests. After interrupt processing is executed, the flag is set to 1 by the maskable interrupt return instruction (RETI) so that interrupts are enabled again. That is, if an interrupt request is already generated, interrupt processing starts immediately after execution of the RETI instruction.

With pseudo non-maskable interrupts, the non-maskable interrupt return instruction (RETN) is used to return. Only when the pseudo non-maskable interrupt processing is entered with interrupt request enabled (IMF = 1), the interrupt master enable flag is set to 1. If the interrupt master enable flag is zero-cleared during the interrupt service program, the interrupt master enable flag remains as 0.

The interrupt master enable flag is allocated to bit 0 in  $EIR_L$  (at address  $0003A_H$  in SFR). Data can be read from or written to the flag using an instruction. Usually, the flag is set or cleared using the El or the DI instruction. At reset, the flag is initialized to 0.

#### 2 Interrupt enable flag (EF<sub>34</sub> to EF<sub>4</sub>)

Independently enables or disables maskable interrupt requests except external interrupt 0. If set to 1, enables interrupt requests; to 0, disables requests.

Figure 1-15. Interrupt Latches (IL) and Interrupt Enable Registers (EIR)

#### 1.5.1 Interrupts Sequence

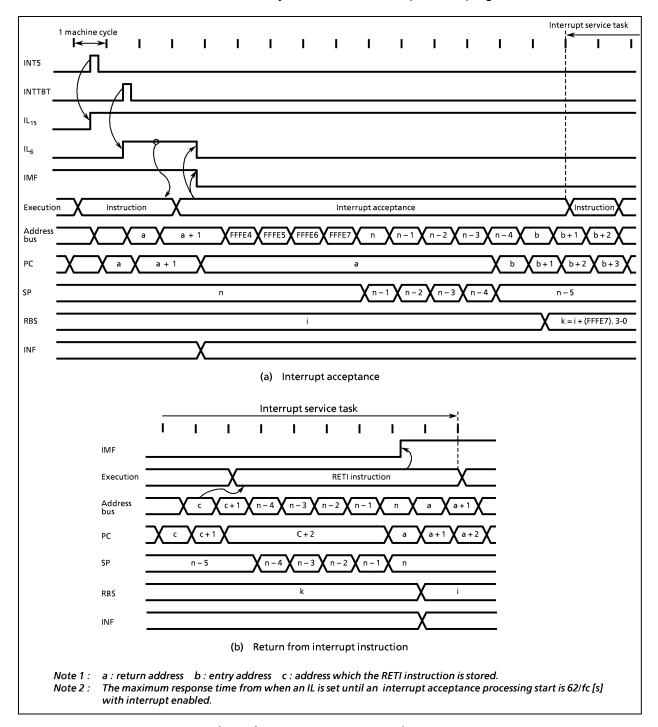

An interrupt request is held until the interrupt is accepted or the interrupt latch is zero-cleared by reset or instruction. After execution of the current instruction is complete, the interrupt is accepted in 12 machine cycles (3  $\mu$ s, @ 16 MHz). The interrupt service program ends after executing an interrupt return instruction: RETI for maskable interrupts and RETN for pseudo non-maskable interrupts. Figure 1-16 shows interrupt accept processing timing.

#### (1) Interrupt acceptance

Interrupts are automatically accepted as follows:

- ① Zero-clears the interrupt master flag (IMF). This temporarily disables subsequent maskable interrupt requests. If a non-maskable interrupt request is accepted, also temporarily disables the subsequent non-maskable interrupt requests.

- ② Zero-clears the latch of the accepted interrupt request.

- ③ Saves the data in the program counter (PC) and program status word (PSW) to the stack. (Pushes down from PSW<sub>H</sub>, PSW<sub>L</sub>, PC<sub>E</sub>, PC<sub>H</sub>, PC<sub>L</sub>.) The stack pointer (SP) is decremented five times.

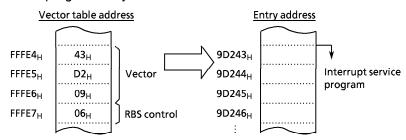

- Reads the entry address (interrupt vector) of the interrupt service program from the vector table address corresponding to the interrupt source and sets the read entry address in the program counter.

© Reads the register bank selector (RBS) control code from the vector table and adds the lower 4 bits to RBS.

© The instruction stored at the entry address of the interrupt service program is executed.

Figure 1-16. Timing Chart of Interrupt Acceptance and Interrupt Return Instruction

Example: Correspondence between vector table address for INTTBT processing and interrupt service program entry address

Even when a maskable interrupt source is generated whose priority is higher than the interrupt currently being processed, the later interrupt is not accepted until the interrupt master enable flag is set to "1". Thus, to process multiple interrupt requests, set the interrupt master enable flag to "1" using the interrupt service program. At the same time, enable interrupt requests which are acceptable using the interrupt enable flag. Note that external interrupt 0 cannot be disabled using the interrupt enable flag. Either disable external interrupts (while INT0EN = 0, IL3 is not set, thus the falling edge of input to the INT0 pin cannot be detected), or disable interrupt processing by software.

Example 1: Disable external interrupt 0 using the external interrupt control register.

LD (EINTCR), 00000000B; INT0EN←0

Example 2: Disable interrupt processing for external interrupt 0 by software. (The interrupt

processing disable switch is bit 0 at address 000F0<sub>H</sub>.)

PINTO: TEST (000F0H). 0 ; If (000F0H) 0 = 1, Returns without processing interrupt.

JRS T, SINTO RETI

SINT0: Interrupt processing

RETI

VINT0: DL PINT0

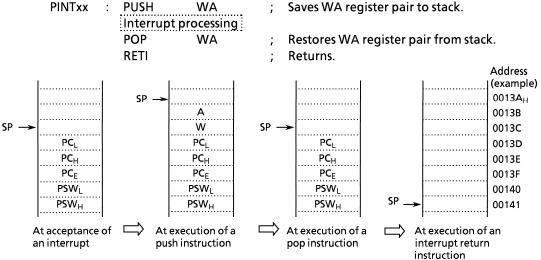

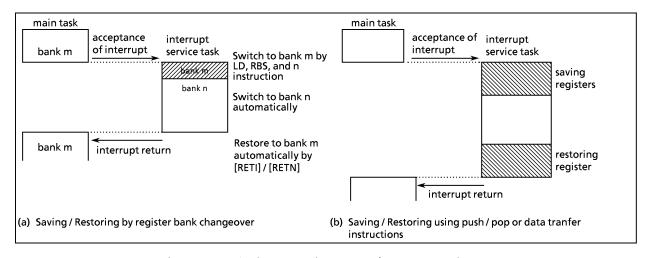

### (2) Saving / Restoring general-purpose registers

Processing for accepting interrupts automatically saves data from the program counter and the program status word to the stack but not data from the accumulator and other registers, which can be saved by program if necessary. For multiple interrupts, be careful not to overlap data memory when saving the above data.

Data from general-purpose registers are saved in one of the following four ways.

① General-purpose register save / restore by automatic register bank changeover.

Switching to an unused register bank saves data from general-purpose registers at high speed.

Usually, bank 0 is allocated to main tasks; banks 1 to 15, to interrupt service tasks.

Executing an interrupt return instruction (RETI or RETN) automatically restores banks.

Therefore, RBS need not be saved by program.

Example: Switch register banks.

PINTxx : Interrupt processing

RETI ; Restores bank and returns.

:

VINTxx : DP PINTxx ; Interrupt service routine entry address

DB 1 ; RBS←RBS + 1

© General-purpose register save / restore by register bank changeover

Switching to an unused register bank saves data from general-purpose registers at high speed.

Usually, bank 0 is allocated to main tasks; banks 1 to 15, to interrupt service tasks. To improve data memory efficiency, allocate the common bank to the non-multiple interrupt sources.

Executing an interrupt return instruction (RETI or RETN) automatically restores banks.

Therefore, RBS need not be saved by program.

Example: Switch register banks.

PINTxx: LD RBS, n Interrupt processing:

RETI; Restores bank and returns.

VINTxx: DP PINTxx; Interrupt service routine entry address

DB 0:

③ General-purpose registers save / restore using push and pop instructions To save data from a specific register or to generate more than one interrupt request for the same interrupt source, save or restore data from the general-purpose register using the push and pop instructions.

$\label{eq:example:save} \textbf{Example: Save and restore register using the push and pop instructions.}$

General-purpose registers save / restore using data transfer instructions For non-multiple interrupt processing, to save data from a specific register, save and restore data between the register and data memory using the load instruction.

Example: Save and restore data between register and data memory using the load

instruction

PINTxx : LD (GSAVA), A ; Saves register A.

Interrupt processing

LD A, (GSAVA); Restores register A.

RETI ; Returns.

Figure 1-17. Saving/Restoring General-Purpose Registers

## (3) Interrupt return

The interrupt return instructions [RETI] / [RETN] perform the following operations.

|   | [RETI] Maskable interrupt return                                                             |   | [RETN] Non-maskable interrupt return                                                                                                                                                                                              |

|---|----------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | The contents of the program counter and the program status word are restored from the stack. | 1 | The contents of the program counter and program status word are restored from the stack.                                                                                                                                          |

| 2 | The stack pointer is incremented 5 times.                                                    | 2 | The stack pointer is incremented 5 times.                                                                                                                                                                                         |

| 3 | The interrupt master enable flag is set to "1".                                              | 3 | The interrupt master enable flag is set to "1" only when a non-maskable interrupt is accepted in interrupt enable status. However, the interrupt master enable flag remains at "0" when so clear by an interrupt service program. |

| 4 | The interrupt nesting counter is decremented, and the interrupt nesting flag is changed.     | 4 | The interrupt nesting counter is decremented, and the interrupt nesting flag is changed.                                                                                                                                          |

Interrupt requests are sampled during the final cycle of the instruction being executed. Thus, the next interrupt can be accepted immediately after the interrupt return instruction is executed.

Note: When the interrupt processing time is longer than the interrupt request generation time, the interrupt service task is performed but not the main task.

# 1.5.2 Software Interrupt (INTSW)

Executing the SWI instruction generates a software interrupt and immediately starts interrupt processing (highest priority). However, if a non-maskable interrupt is already being processed, executing the SWI instruction does not generate a software interrupt and processing is the same as for the NOP instruction. Do not use the SWI instruction for other than detecting address errors or debugging as described below:

#### 1 Address error detection

If the CPU fetches an instruction from an address not found in memory for some reason (eg, noise), FF<sub>H</sub> is read. Code FF<sub>H</sub> is the SWI instruction; thus, a software interrupt is generated so that an address error is detected. Filling the unused program memory area with FF<sub>H</sub> widens the range for detecting address errors. If the CPU fetches an instruction from RAM or the SFR area, an address trap is generated.

## 2 Debugging

Allocating the SWI instruction to the software break point set address improves debugging efficiency.

3-47-24 1999-09-29

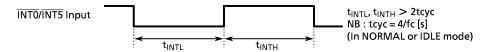

### 1.5.3 External Interrupts

TMP88CH47 supports five external interrupts out of which four are provided with a digital noise rejection circuit (rejects pulse input shorter than the specified time as noise).

Edge can be selected for pins INT1 to INT3. The INT0/P10 pin can be specified for external interrupt input or as an I/O port. At reset, the pin is set to input port.

To select edge, control noise rejection, or select INTO/P10 pin function, use the external interrupt control register.

| Source | Pin  | Secondary<br>function pin | Enable conditions          | Edge              | Digital noise reject                                                                                                                |

|--------|------|---------------------------|----------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| INT0   | ĪNT0 | P10                       | IMF = 1, INT0EN = 1        | falling edge      | — (hysteresis input)                                                                                                                |

| INT1   | INT1 | P11                       | IMF • EF <sub>26</sub> = 1 | falling edge      | Pulses of less than 15/fc or 63/fc [s] are eliminated as noise. Pulses of 48/fc or 192/fc [s] or more are considered to be signals. |

| INT2   | INT2 | P12/TC1                   | IMF • EF <sub>27</sub> = 1 | or<br>rising edge | pulses of less than 7/fc [s] are eliminated as noise. Pulses of 24/fc                                                               |

| INT3   | INT3 | P50/TC3                   | IMF • EF <sub>28</sub> = 1 |                   | [s] or more are considered to be signals.                                                                                           |

| INT5   | ĪNT5 | P20/STOP                  | IMF • EF <sub>15</sub> = 1 | falling edge      | — (hysteresis input)                                                                                                                |

Table 1-3. External Interrupts

Note 1: The noise reject function is turned off in SLOW and SLEEP modes. Also, the noise reject times are not constant for pulses input while transiting between operating modes.

Note 2: The noise reject function is also affected for timer / counter input (TC1 pin).

Note 3: The pulse width (both "H" and "L" level) for input to the INTO and INT5 pins must be over 2 machine cycle.

Note 4: If a noiseless signal is input to the external interrupt pin in the NORMAL 1/2 or IDLE 1/2 mode, the maximum time from the edge of input signal until the IL is set is as follows:

① INT1 pin 49/fc [s] (INT1NC = 1), 193/fc [s] (INT1NC = 0)

② INT2, 3 pin 25/fc [s]

Note 5: Even if the falling edge of  $\overline{\text{INTO}}$  pin input is detected at INTOEN = 0, the interrupt latch IL<sub>3</sub> is not set.

Figure 1-18. External Interrupt Control Register

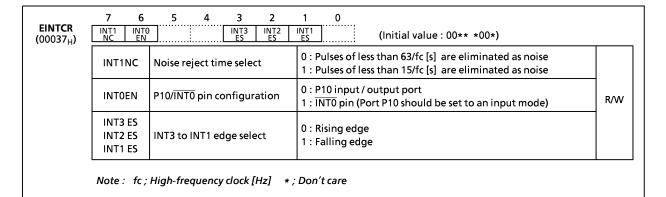

### 1.6 Reset Circuit

TMP88CH47 supports four types of reset generation: external reset input, address trap reset output, watchdog timer reset output, and system clock reset output.

Table 1-4 shows initialization of the internal hardware by reset.

At power on, the internal reset output circuits (watchdog timer reset, address trap reset, and system clock reset) are not initialized. Thus, at power on, the  $\overline{\text{RESET}}$  pin may output "L" level for up to 24/fc [s] (1.5  $\mu$ s, @ 16 MHz).

| Internal hardware                                            |                 | Initial value                               | Internal hardware               | Initial value               |

|--------------------------------------------------------------|-----------------|---------------------------------------------|---------------------------------|-----------------------------|

| Program counter                                              | (PC)            | (FFFFC <sub>H</sub> to FFFFE <sub>H</sub> ) | Presseles and Divides of timing |                             |

| Stack pointer                                                | (SP)            | not initialized.                            | Prescaler and Divider of timing | 0                           |

| General-purpose register (WAI                                | BCDEHL)         | not initialized.                            | generator                       |                             |

| Register bank selector                                       | (RBS)           | 0                                           | NA/at als disputing an          | Enable                      |

| Jump status flag                                             | (JF)            | 1                                           | Watchdog timer                  | Enable                      |

| Zero flag                                                    | (ZF)            | not initialized.                            |                                 |                             |

| Carry flag                                                   | Carry flag (CF) |                                             |                                 |                             |

| Half carry flag                                              | (HF)            | not initialized.                            | Output latakas 1/O manta        | Refer to I/O port circuitry |

| Sign flag                                                    | (SF)            | not initialized.                            | Output latches I/O ports        |                             |

| Overflow flag                                                | (VF)            | not initialized.                            |                                 |                             |

| Interrupt master enable flag (IMF)                           |                 | 0                                           |                                 |                             |

| Interrupt individual enable flag (EF) Interrupt latches (IL) |                 | 0                                           | Cantual nanistana               | Refer to each of            |

|                                                              |                 | 0                                           | Control registers               | control register            |

|                                                              |                 |                                             | RAM                             | not initialized.            |

Table 1-4. Initialization of Internal Hardware by Reset

# 1.6.1 External Reset Input

The RESET pin has a pull-up resistor for hysteresis input. When the supply voltage is within the operating voltage and oscillation is stabilized, holding the RESET pin at "L" level for a minimum of 3 machine cycles (12/fc [s]) generates reset and initializes the internal states.

When the  $\overline{\text{RESET}}$  pin input reaches "H" level, reset is released. Execution of the program starts from the vector address stored at addresses FFFFC to FFFFE<sub>H</sub>.

Figure 1-19. Reset Circuit

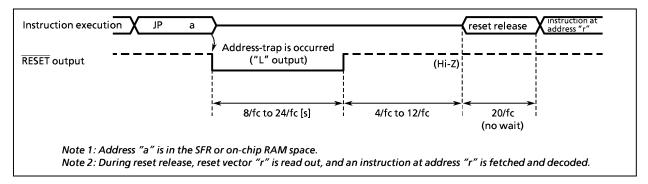

## 1.6.2 Address-Trap-Reset

When CPU runaway is caused by noise, for example, and an attempt is made to fetch an instruction from on-board RAM or the SFR, an internal reset is generated and a reset signal ("L" level) is output from the  $\overline{\text{RESET}}$  pin. The reset signal is output for 8/fc to 24/fc [s] (0.5 to 1.5  $\mu$ s @ 16 MHz)

Figure 1-20. Address Trap Reset

# 1.6.3 System-Clock-Reset

Zero-clearing bits 7 and 6 in SYSCR2 stops the system clock and causes MCU deadlock. To avoid deadlock, detecting that bits 7 and 6 in SYSCR2 are both set to 0 automatically generates a reset signal and continues oscillation. Reset signal is output from the  $\overline{\text{RESET}}$  pin. Reset signal is output for 8/fc to 24/fc [s] (0.5 to 1.5  $\mu$ s @ 16 MHz)

# 2. On-Chip Peripheral Functions

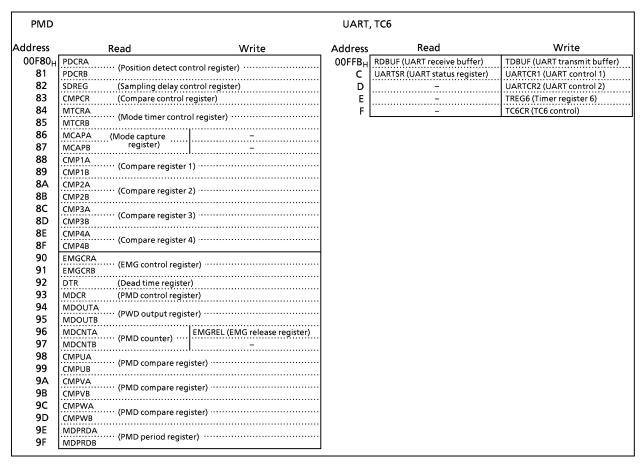

# 2.1 Special Function Registers (SFR) and Data Buffer Registers (DBR)

The TLCS-870 series uses memory mapped I/O: peripheral hardware control and data transfer are performed using the special function registers (SFR) and data buffer registers (DBR).

SFRs are mapped to addresses 00000 to 0003F<sub>H</sub>; DBR, to addresses 00F80 to 00F9F<sub>H</sub> and 00FFB to 00FFF<sub>H</sub>.

Figure 2-1 (1/2) shows the TMP88CH47 SFRs; 2-1 (2/2), DBRs.

| Address            | Read                          | Write                                | Address            | Read                                                                                                    | Write                                |  |

|--------------------|-------------------------------|--------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------|--|

| 00000 <sub>H</sub> | Port P0                       |                                      | 00020 <sub>H</sub> | _                                                                                                       | SBICR1 (SBI control 1)               |  |

| 01                 | Port P1                       |                                      | 21                 | SBIDBR (SB                                                                                              | l data buffer)                       |  |

| 02                 | Port P2                       |                                      | 22                 |                                                                                                         | I2CAR (I <sup>2</sup> C bus address) |  |

| 03                 | reserved                      |                                      | 23                 | SBISR (SBI status)                                                                                      | SBICR2 (SBI control 2)               |  |

| 04                 | Port P4                       |                                      | 24                 | ADCDR2L (The lower 8 bits of ADCDR2L (AD conv. result ADCDR2H (AD conv. result ADCDR2H (AD conv. result | )                                    |  |

| 05                 | Port P5                       |                                      | 25                 | ADCDR2H ( AD conv. result                                                                               |                                      |  |

| 06                 | Port P6                       |                                      | 26                 |                                                                                                         | erved                                |  |

| 07                 | reserved                      |                                      | 27                 | res                                                                                                     | erved                                |  |

| 08                 | reserved                      |                                      | 28                 | res                                                                                                     | erved                                |  |

| 09                 | reserved                      |                                      | 29                 | res                                                                                                     | erved                                |  |

| 0A                 | — P0CF                        | (Port P0 I/O control)                | 2A                 | res                                                                                                     | erved                                |  |

| 0В                 | – P1CR                        | (Port P1 I/O control)                | 2B                 | EIRC (Extended interrupt enable r                                                                       | egister/extended interrupt latch     |  |

| 0C                 | – P6CR                        | (Port P6 I/O control)                | 2C                 | EIRE (Extended interrupt enable r                                                                       | egister lower)                       |  |

| 0D                 | reserved                      |                                      | 2D                 | EIRD (Extended interrupt enable register upper)                                                         |                                      |  |

| 0E                 | ADCCR (AD converte            | er control)                          | 2E                 | ILE (Extended interrupt latch lowe                                                                      | er)                                  |  |

| 0F                 | ADCDR1 (The upper 8 bits of ) |                                      | 2F                 | ILD (Extended interrupt latch upp                                                                       | er)                                  |  |

| 10                 | - TREG                        | i1A <sub>L</sub> (Timer register 1A) | 30                 | res                                                                                                     | erved                                |  |

| 11                 | – TREC                        | i1A <sub>H</sub>                     | 31                 | res                                                                                                     | erved                                |  |

| 12                 | TREG1B <sub>L</sub>           | · (Timer register 1B)                | 32                 | res                                                                                                     | erved                                |  |

| 13                 | TICO TO H                     |                                      | 33                 | res                                                                                                     | erved                                |  |

| 14                 | – TC10                        | R (TC1 control)                      | 34                 | -                                                                                                       | WDTCR1 (WDT control 1)               |  |

| 15                 | – TC20                        | R (TC2 control)                      | 35                 | -                                                                                                       | WDTCR2 (WDT control 2)               |  |

| 16                 | – TREC                        | i2 <sub>L</sub> (Timer register 2)   | 36                 | TBTCR (TBT/TG/DV                                                                                        | O control)                           |  |

| 17                 | - TREC                        | i2 <sub>H</sub>                      | 37                 | EINTCR (External i                                                                                      | nterrupt control)                    |  |

| 18                 | reserved                      |                                      | 38                 | SYSCR1 (System co                                                                                       | ntrol 1)                             |  |

| 19                 | reserved                      |                                      | 39                 | SYSCR2 (System co                                                                                       | ntrol 2)                             |  |

| 1A                 | reserved                      |                                      | 3A                 | EIRL //a-t                                                                                              | errupt enable register) ·······      |  |

| 1B                 | reserved                      |                                      | 3B                 | EIRH (INT                                                                                               | errupt enable register)              |  |

| 1C                 | reserved                      |                                      | 3C                 | ILL                                                                                                     | errupt latch) ······                 |  |

| 1D                 | TREC                          | 55 (Timer register 5)                | 3D                 | ILH (Int                                                                                                | errupt latch)                        |  |

| 1E                 | TC5C                          | R (TC5 control)                      | 3E                 | PSWL /p-                                                                                                |                                      |  |

| 1F                 | reserved                      |                                      | 3F                 | PSWH (Pro                                                                                               | ogram status word) ·····             |  |

Figure 2-1. SFR & DBR (1/2)

Figure 2-1. SFR & DBR (2/2)

### 2.2 **I/O Ports**

TMP88CH47 features eight built-in I/O ports (34 pins).

|         | Primary Function | Secondary Function                                                                     |

|---------|------------------|----------------------------------------------------------------------------------------|

| Port P0 | 8-bit I/O port   | motor control circuit I/O                                                              |

| Port P1 | 8-bit I/O port   | external interrupt, timer/counter I/O, divider output, and motor control circuit input |

| Port P2 | 1-bit I/O port   | external interrupt and STOP mode release signal input                                  |

| Port P4 | 8-bit I/O port   | serial interface I/O and motor control circuit input                                   |

| Port P5 | 1-bit I/O port   | external interrupt input                                                               |

| Port P6 | 8-bit I/O port   | analog input                                                                           |

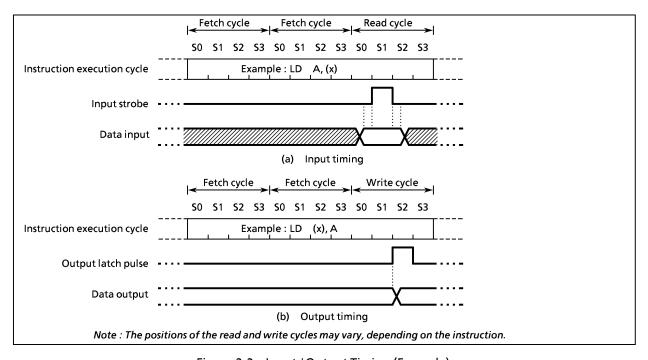

All output ports have built-in latches in which data are held. Input ports do not have latches; thus, data should be held externally until read externally, or held after more than one read. Figure 2-2 shows data input and output timings.

External data are read from I/O ports at the S1 state of the read cycle at instruction execution. This timing cannot be checked externally; thus, transient input data such as chattering should be handled by program. Data are output to I/O ports at the S2 state of the write cycle at instruction execution.

Figure 2-2. Input / Output Timing (Example)

When data are read from an I/O port other than a programmable I/O port, whether pin input values or output latch data are read depends on the instruction as follows.

### (1) Instructions which read output latch data:

- ① XCH r, (src) ⑤ LD (pp). b,CF ② SET/CLR/CPL (src). b ⑥ XCH CF, (src).b

- ③ SET/CLR/CPL (pp). g ⑦ ADD/ADDC/SUB/SUBB/AND/OR/XOR (src), n

- 4 LD (src). b, CF8 ADD/ADDC/SUB/SUBB/AND/OR/XOR (src), (src)-side for (HL) instruction

9 MXOR (src), m

### (2) Instructions which read pin input values:

Instructions other than (1) above, and ADD/ADDC/SUB/SUBB/AND/OR/XOR (src), (HL)-side for (HL) instructions.

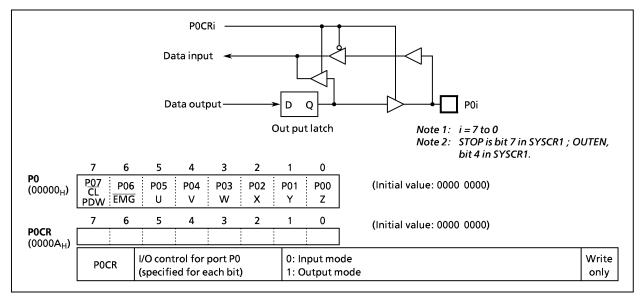

# 2.2.1 Port P0 (P07 to P00)

Port P0 is an 8-bit general-pupose I/O port whose input or output is specifiable in units of bits. Specify input or output using the Port P0 I/O control register (P0CR). At reset, P0CR is initialized to 0, port P0 is set to input mode, and the port P0 output latches are initialized to 0.

Note: Input mode port reads the state of input pin. When input / output mode is used to mixed, the contents of output latch setting to the input mode port may be overwritten by executing bit manipulation instructions.

Figure 2-3. Port P0 and P0CR

Example: Set upper 4 bits of port P0 to input mode and lower 4 bits to output mode. The initial output value is 1010B.

LD (P0), 00001010B ; Sets initial value for port P0 output latches.

LD (POCR), 00001111B; Sets I/O mode for port P0.

## 2.2.2 Port P1 (P17 to P10)

Port P1 is an 8-bit port whose input or output is specifiable in units of bits. Specify input or output using the Port P1 I/O control register (P1CR). At reset, P1CR is initialized to 0, port P1 is set to input mode, and the port P1 output latches are initialized to 0.

To use port P1 pins as function pins, set the input pins to input mode. For output mode, set the output latches for the output pins to 1. We recommend you use the P11 and P12 pins for external interrupt input, timer/counter input or as an input port. (If used as an output port, the interrupt latches are set by a rising or falling edge.) The P10 pin can be used for either I/O port or external interrupt input according to the external interrupt control register (INT0EN). At reset, the P10 pin is set to an input port.

Figure 2-4. Port P1 and P1CR

Example: Set P17 and P16 to an output port, P13 and P11 to an input port, the other pins as function pins. P17 outputs 1 and P16 outputs 0.

LD (EINTCR), 01000000B; INT0EN  $\leftarrow 1$

LD (P1), 10111111B ;  $P17 \leftarrow 1$ ,  $P14 \leftarrow 1$ ,  $P16 \leftarrow 0$

LD (P1CR), 11010000B

Note: Input mode port reads the state of input pin. When input / output mode is used to mixed, the contents of output latch setting to the input mode port may be overwritten by executing bit manipulation instructions.

3-47-32 1999-09-29

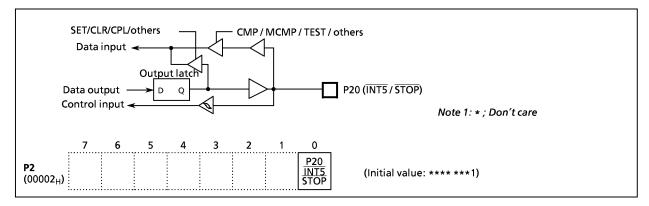

## 2.2.3 Port P2 (P22 to P20)

Port P2 is a 1-bit I/O port. It is also used for external interrupt input, and STOP mode release signal. To use port P2 as function pins or an input port, set the output latches to 1. At reset, the output latches are initialized to 1.

We recommend that the P20 pin be used for external interrupt input, STOP mode release signal input, or input port. (If used as an output port pin, the interrupt latch is set at a falling edge.)

When the read instruction is executed for port P2, undefined values are read from bits 7 to 1.

Figure 2-5. Port P2

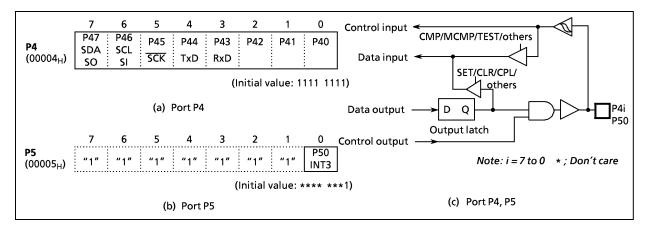

# 2.2.4 Port P4 (P47 and P40)

To use port P4 as an input port or as function pins, set the output latches to 1. At reset, the port P4 output latches are initialized to 1.

# 2.2.5 Port P5 (P50)

Port P5 is a 1-bit I/O port. To use port P5 as input pins or function pins, set the output latches to 1. At reset, the port P5 output latches are initialized to 1.

When the read instruction is executed for port P5, 1s are read from bits 7 to 1.

Example: Clear the P50 pin ("L" level output)

CLR (P5). 0 ;  $P50 \leftarrow 0$

Figure 2-6. Port P4 and P5

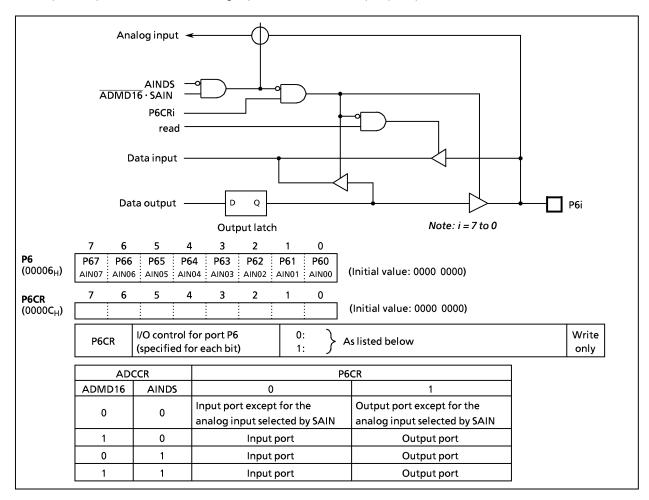

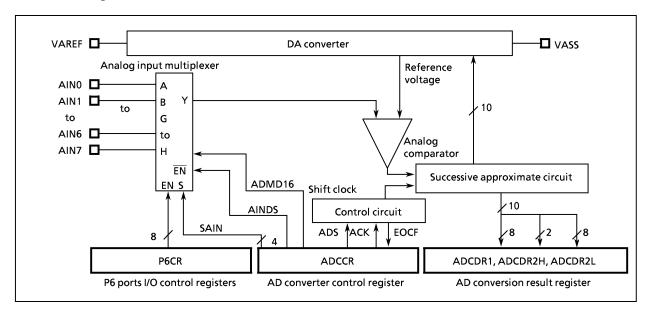

# 2.2.6 Port P6 (P67 to P60)

Port P6 is an 8-bit I/O port whose input or output is specifiable in units of bits. Port P6 is also used for analog input. Specify input or output using the port P6 I/O control register (P6CR) and AINDS (bit 4 in ADCCR).

At reset, P6CR is set to 1; AINDS is cleared to 0; thus, port P6 is set to analog input. At reset, the port P6 output latches are initialized to 0. P6CR is a write-only register. When using the AD converter, the port P6 pins not used for analog input can be used as input port pins.

Figure 2-7. Port P6 and P6CR

Note: Input mode port reads the state of input pin. When input / output mode is used to mixed, the contents of output latch setting to the input mode port may be overwritten by executing bit manipulation instructions.

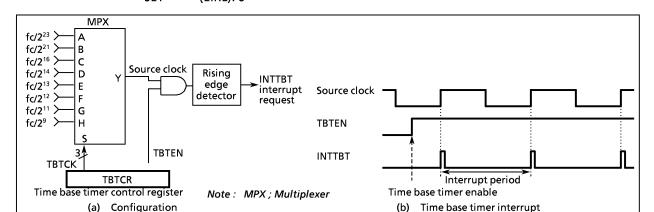

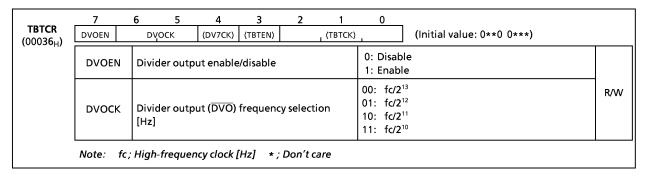

## 2.3 Time Base Timer (TBT)

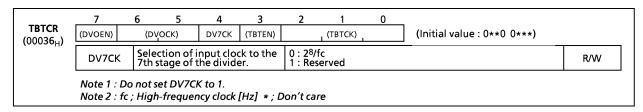

The time base timer is the reference time generation timer for key scan and dynamic display processing; it generates the time base timer interrupt (INTBT) at a fixed cycle.

After the time base timer is enabled, time base timer interrupts are generated at the first rising edge of the source clock (select timing generator divider output using TBTCK). Sine the divider is not cleared by program, only the first interrupt may be generated before the set interrupt cycle. (Figure 2-8 (b)) Select the interrupt frequency with the time base timer disabled. (When switching to timer disabled from timer enabled, do not change the set interrupt frequency.) Note that selecting the frequency and enabling the time base timer can be performed simultaneously.

Example: Set time base timer interrupt frequency to fc/216 [Hz] and enable interrupts.

LD (TBTCR), 00001010B SET (EIRL). 6

Figure 2-8. Time Base Timer

| TBTCR                 | 7         | 6          | 5           | 4           | 3         | 2       | 1       | 0                                                            | _                        | (I. 12. I                                                                                                                              |     |   |

|-----------------------|-----------|------------|-------------|-------------|-----------|---------|---------|--------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|---|

| (00036 <sub>H</sub> ) | (DVOEN)   | (D         | уоск)       | (DV7CK)     | TBTEN     |         | , ТВТСК |                                                              |                          | (Initial value: 0**0 0***)                                                                                                             |     |   |

|                       | TBTEN     | Tim        | ne base tir | mer enabl   | e / disab | le      |         | 1 "                                                          | sabl<br>able             |                                                                                                                                        |     |   |

|                       | ТВТСК     | Tim<br>[Hz | ne base tir | mer interr  | upt freq  | uency s | elect   | 000:<br>001:<br>010:<br>011:<br>100:<br>101:<br>110:<br>111: | fc/<br>fc/<br>fc/<br>fc/ | 12 <sup>23</sup> 12 <sup>21</sup> 12 <sup>16</sup> 12 <sup>14</sup> 12 <sup>13</sup> 12 <sup>12</sup> 12 <sup>11</sup> 12 <sup>9</sup> | R/W |   |

|                       | Note: fc; | High       | h frequen   | cy clock [l | Hz] *;    | Don't c | are     |                                                              |                          |                                                                                                                                        | •   | - |

Figure 2-9. Time Base Timer Control Register

Table 2-1. Time Base Timer Interrupt Frequency (Example; fc = 16MHz)

| ТВТСК | Time base timer interrupt frequency [Hz] |

|-------|------------------------------------------|

| 000   | 1.91                                     |

| 001   | 7.63                                     |

| 010   | 244.14                                   |

| 011   | 976.56                                   |

| 100   | 1953.12                                  |

| 101   | 3906.25                                  |

| 110   | 7812.50                                  |

| 111   | 31250                                    |

3-47-35 1999-09-29

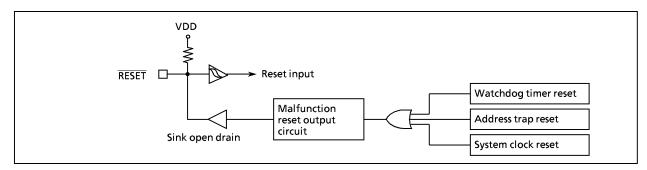

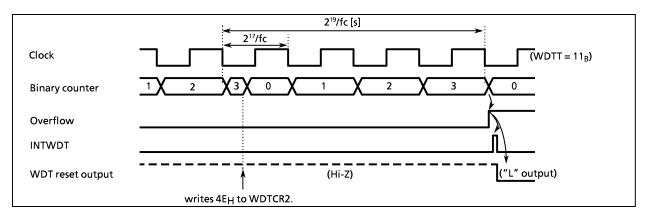

## 2.4 Watchdog Timer (WDT)

The watchdog timer is a fail-safe function, which detects misoperation (runaway) of the CPU caused by, for example, noise or deadlock, and returns it to normal operation.

Runaway signals detected by the watchdog timer, selectable by program, can be either reset output or pseudo non-maskable interrupt request. Note that this selection can be mode only once. At reset release, initialized to reset output.

When the watchdog timer is not used for detecting runaway, it can be used as a timer which generates interrupts at a fixed cycle.

# 2.4.1 Watchdog Timer Configuration

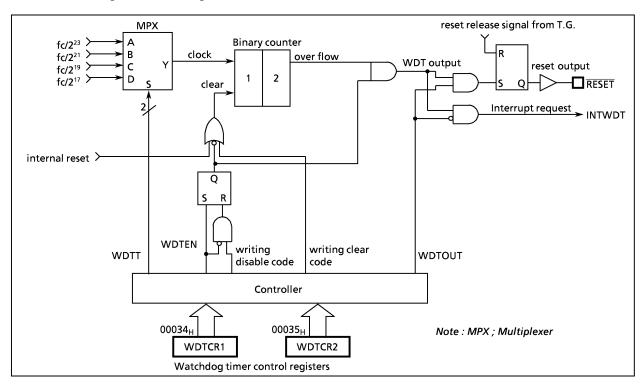

Figure 2-10. Watchdog Timer Configuration

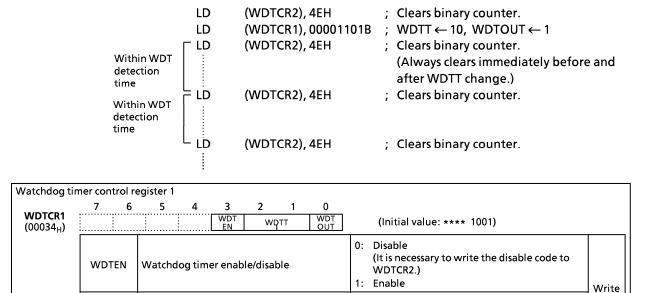

## 2.4.2 Watchdog Timer Control

Figure 2-11 shows the watchdog timer control registers. Releasing reset enables the watchdog timer.

## (1) How to detect runaway using the watchdog timer

CPU runaway is detected as follows:

- ① Set detection time, select output, and clear the binary counter.

- ② Repeat clearing of the binary counter within every set detection time.

If runaway or deadlock occurs, and the binary counter is not cleared, the binary counter overflows causing the watchdog timer output (WDTOUT) to be active. At this time, if WDTOUT = 1, reset signals are output from the  $\overline{\text{RESET}}$  pin and the internal hardware is reset. If WDTOUT = 0, a watchdog timer interrupt (INTWDT) is generated.

In STOP (including warm up) or IDLE mode, the watchdog timer temporarily stops counting. Releasing STOP or IDLE mode automatically restarts the watchdog timer.

Example: Set watchdog timer detection time to 2<sup>21</sup>/fc [s] and resets runaway detection.

Note 1: WDTOUT cannot be set to "1" by program after clearing WDTOUT to "0".

Note 2: fc; High-frequency clock [Hz], \*; Don't care

Watchdog timer output select

Watchdog timer detection time [s]

Note 3: WDTCR1 is a write-only register and must not be used with any of read-modify-write instructions.

Note 4: The watchdog timer must be disabled or the counter must be cleared immediately before entering to the STOP mode. When the counter is cleared, the counter must be cleared again immediately after releasing the STOP mode.

00: 2<sup>25</sup>/fc

01: 2<sup>23</sup>/fc

10: 2<sup>21</sup>/fc 11: 2<sup>19</sup>/fc

0: Interrupt request

1: Reset output

only

Watchdog timer control register 2 WDTCR2 (Initial value: \*\*\*\* \*\*\*\*)  $(00035_{H})$ 4E<sub>H</sub>: Watchdog timer binary counter clear. (clear code) Write WDTCR2 Writes watchdog timer control code. B1<sub>H</sub>: Watchdog timer disable. only (disable code) others: Invalid

Note 1: The disable code is invalid unless written when WDTEN = 0.

Note 2: \*; Don't care

WDTT

WDTOUT

Note 3: The binary counter of the watchdog timer must not be cleared by the interrupt task.

Figure 2-11. Watchdog Timer Control Registers

### (2) Watchdog timer enable

Setting 1 in WDTEN (bit 3 in WDTCR1) enables the watchdog timer. Resetting initializes WDTEN to 1; thus, releasing reset immediately starts the watchdog timer.

### (3) Watchdog timer disable

Zero-clearing WDTEN (bit 3 in WDTCR1) and writing disable code (B1<sub>H</sub>) in WDTCR2 disables the watchdog timer. Note that first writing disable code in WDTCR2 then zero-clearing WDTEN do not disable the watchdog timer. While the watchdog timer is disabled, the watchdog timer binary counter is cleared.

Example: Disable watchdog timer.

LDW (WDTCR1), 0B101H ; WDTEN  $\leftarrow$  0, WDTCR2  $\leftarrow$  disable code

Table 2-2. Watchdog Timer Detection Time (Example: fc = 16 MHz)

| WDTT | Watchdog Timer Detection Time [s] |

|------|-----------------------------------|

| 00   | 2.097                             |

| 01   | 524.288 m                         |

| 10   | 131.072 m                         |

| 11   | 32.768 m                          |

# 2.4.3 Watchdog Timer Interrupt (INTWDT)

Watchdog timer interrupts are pseudo non-maskable. They are accepted regardless of the contents in the interrupt enable register. However, if another watchdog timer interrupt or software interrupt is being processed, the new watchdog timer interrupt must wait until processing of the current interrupt is complete (RETN instruction execution completes).

Set the stack pointer before setting watchdog timer output as the interrupt source in WDTOUT.

Example: Set Watchdog timer interrupt.

LD SP, 0043FH ; Sets SP. LD (WDTCR1), 00001000B ; WDTOUT  $\leftarrow$  0

#### 2.4.4 Watchdog Timer Reset

"L" level is output from the  $\overline{\text{RESET}}$  pin and, at the same time, internal hardware is reset. Reset timer is 8/fc to 24/fc [s] (0.5 to 1.5  $\mu$ s at fc = 16 MHz). The  $\overline{\text{RESET}}$  pin is sink open-drain I/O with a pull-up resistor.

Figure 2-12. Watchdog Timer Interrupt / Reset

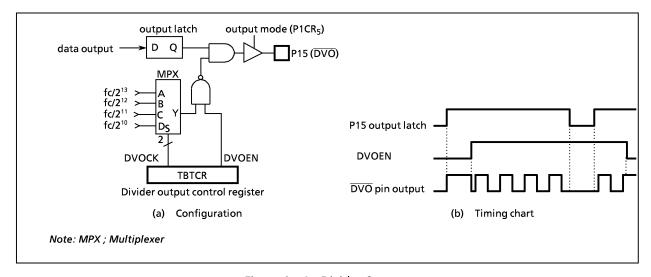

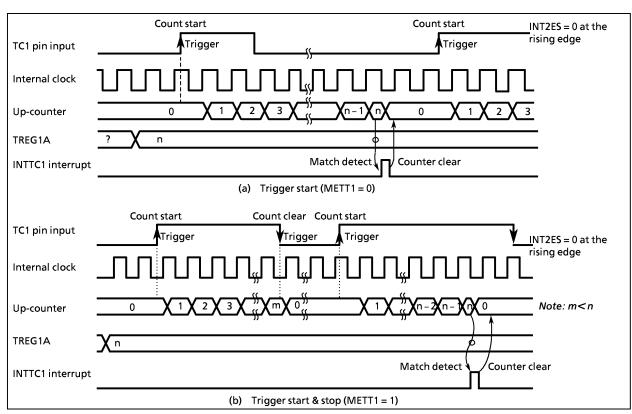

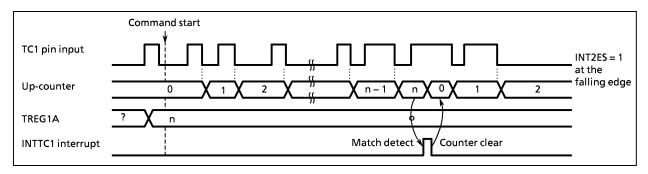

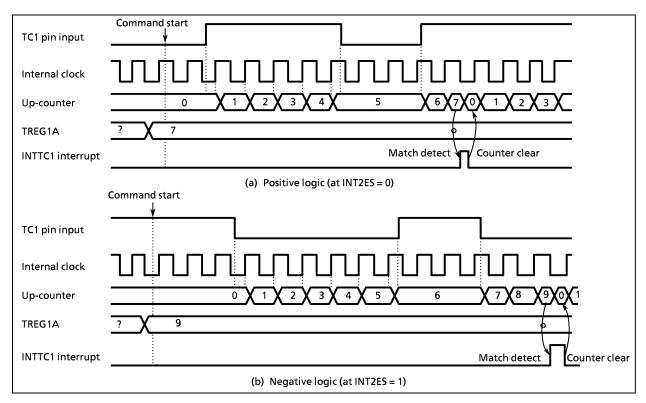

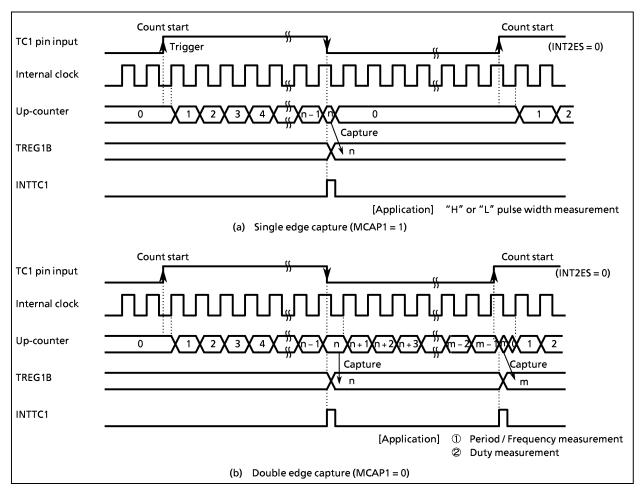

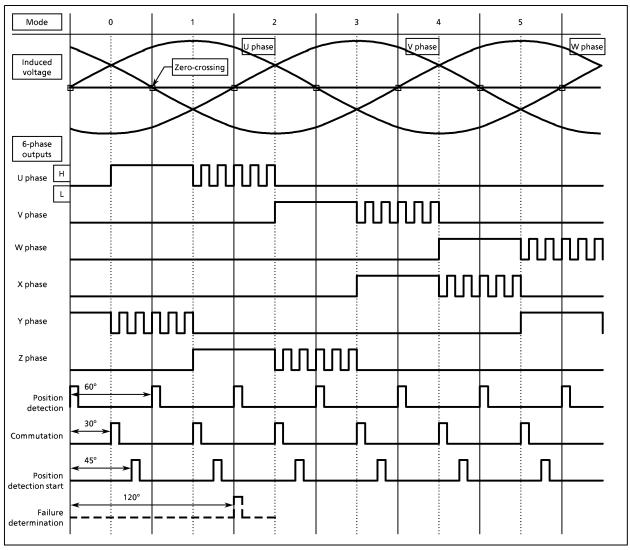

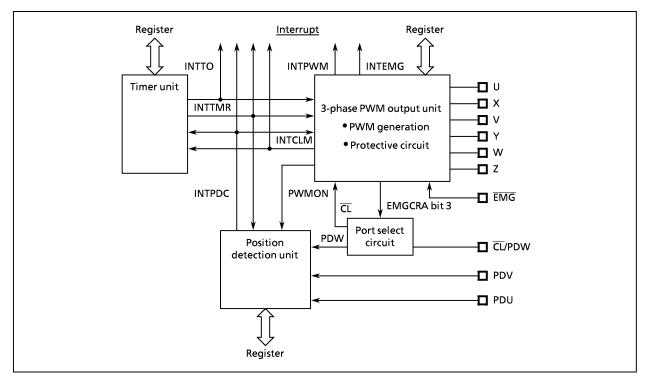

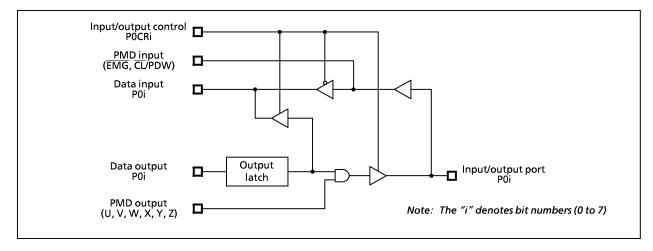

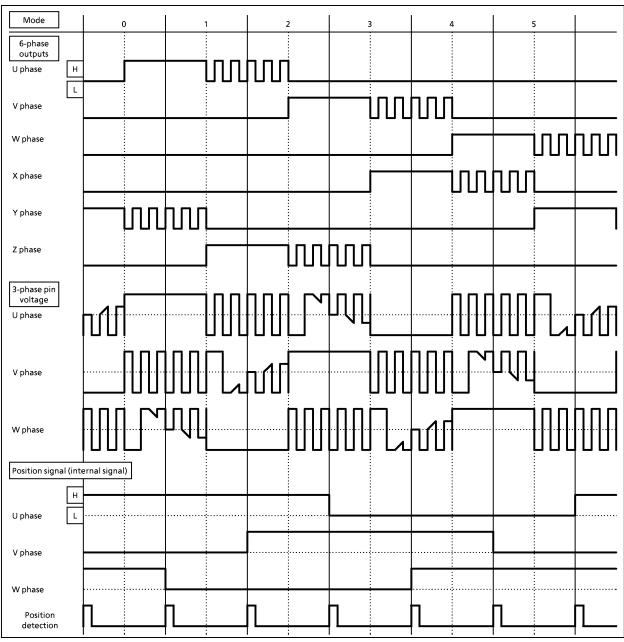

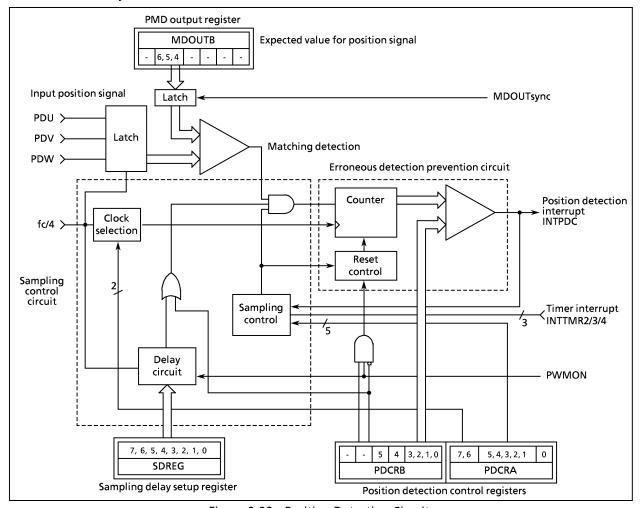

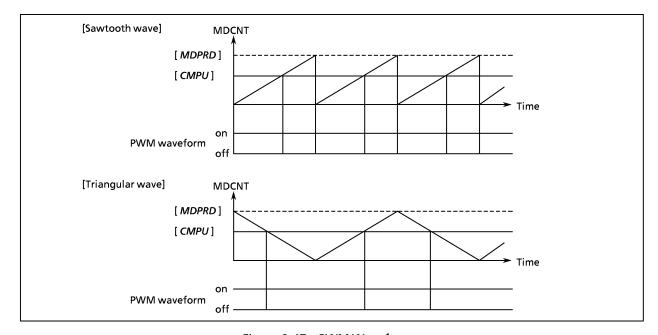

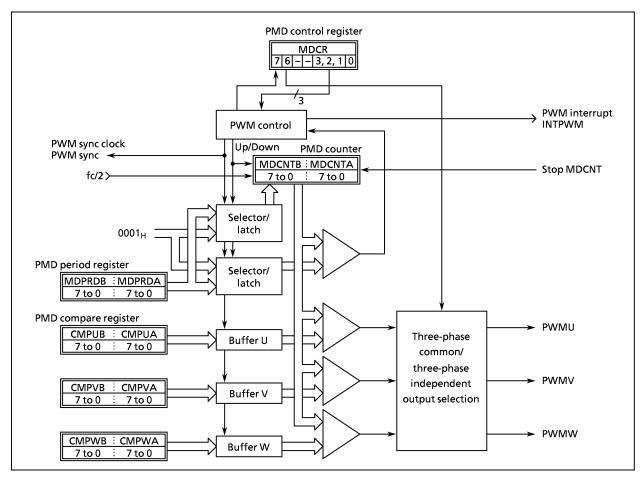

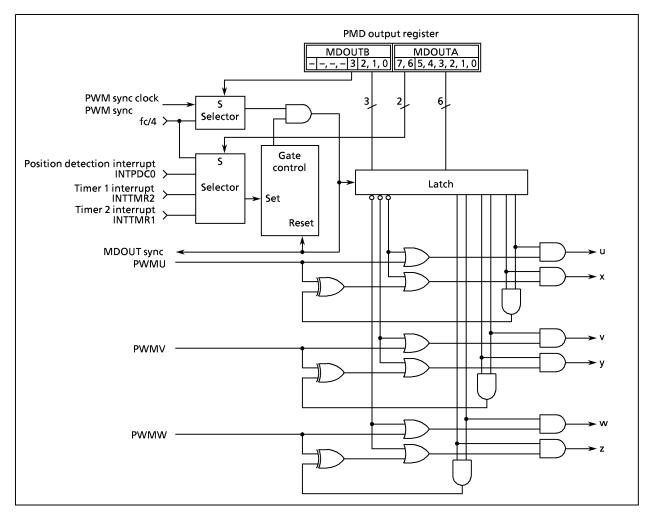

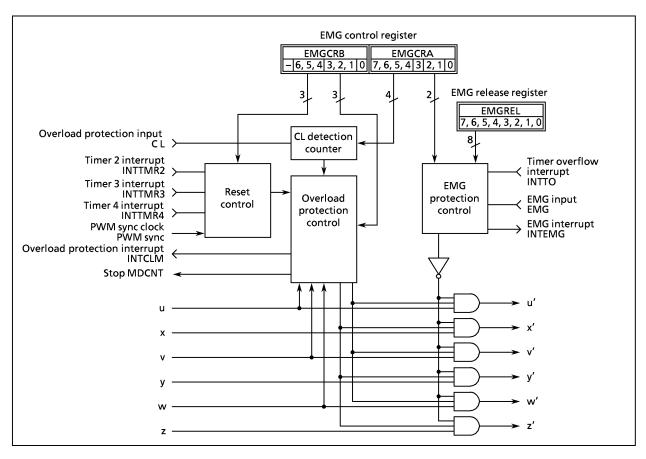

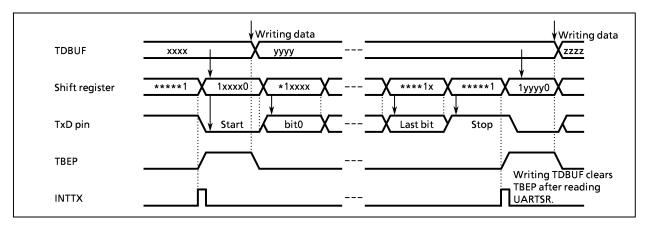

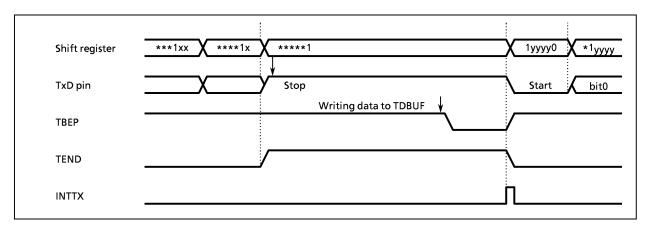

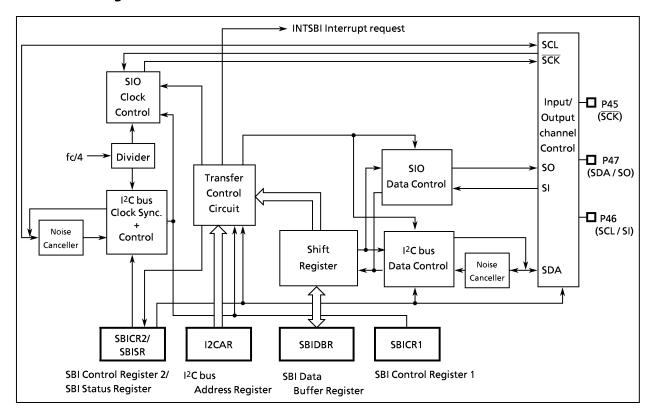

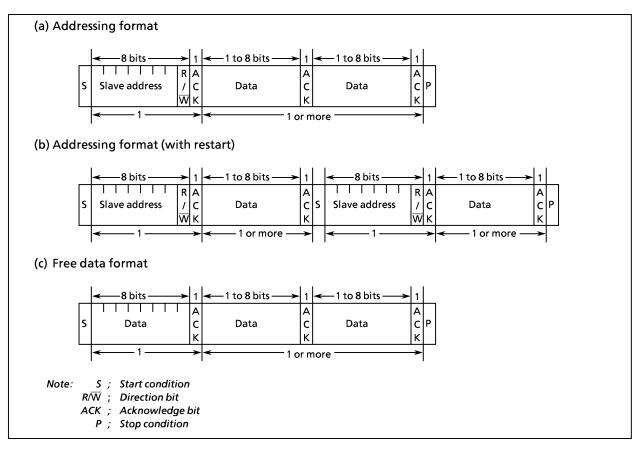

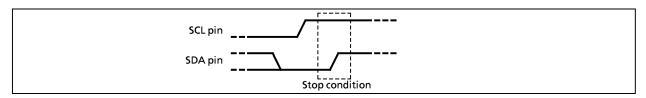

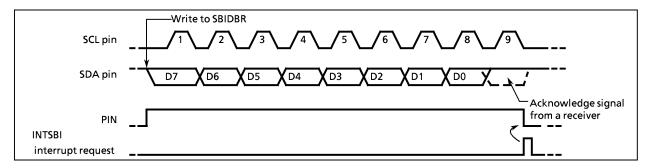

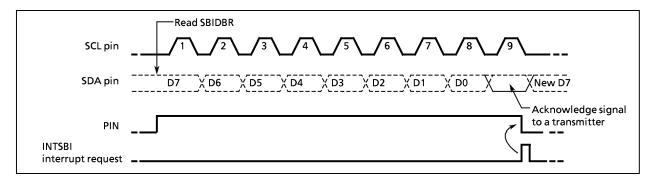

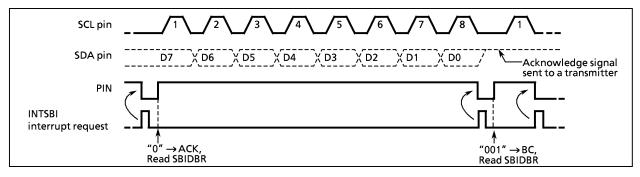

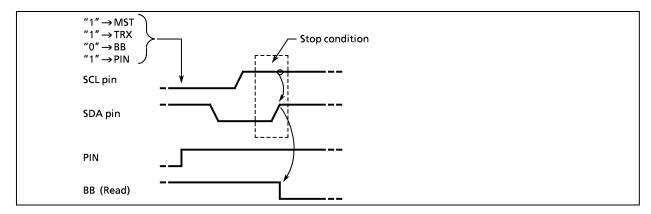

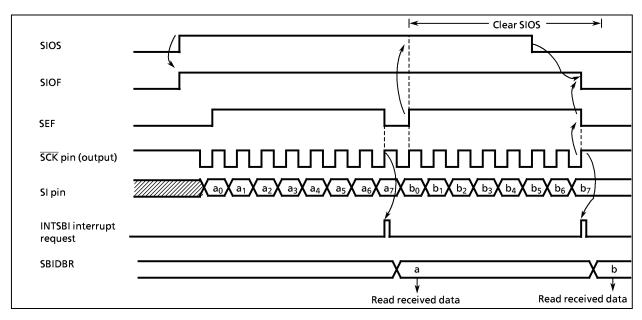

### 2.5 Divider Output (DVO)