# **JN Semiconductor®**

To k are more about Old Semiconductor, please visit our website at www.onsemi.com

Please note. As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

January 2008

# 74LVT574, 74LVTH574 Low Voltage Octal D-Type Flip-Flop with 3-STATE Outputs

### **Features**

- Input and output interface capability to systems at 5V V<sub>CC</sub>

- Bushold data inputs eliminate the need for external pull-up resistors to hold unused inputs (74LVTH574), also available without bushold feature (74LVT574)

- Live insertion/extraction permitted

- Power Up/Down high impedance provides glitch-free bus loading

- Outputs source/sink -32mA/+64mA

- Functionally compatible with the 74 series 574

- Latch-up performance exceeds 500mA

- ESD performance:

- Human-body model > 2000V

- Machine model > 200V

- Charged-device model > 1000V

### **General Description**

The LVT574 and LVTH574 are high-speed, low-power octal D-type flip-flop featuring separation D-type inputs for each flip-flop and 3-STATE couputs bus-oriented applications. A buffered Clr k ( $\stackrel{\frown}{OE}$ ) and utput Enable ( $\stackrel{\frown}{OE}$ ) are common to all p-flops.

The LVTH574 dat inp. ....clude bushold, aliminating the need for extern put o sistors to hold unused inputs.

The plotta lip-library designed for low-voltage (3.3V) 'CC is placed by some state of the capability to provide a TTL part of the state of the capability to provide a TTL part of the state of the capability to provide a TTL part of the state of the capability to provide a TTL part of t

### Ordering Information

|                | Dack   | X K W X Y                                                                   |

|----------------|--------|-----------------------------------------------------------------------------|

| Order N nbc.   | N nber | Package Description                                                         |

| 7/· - 74Vi     | м20B   | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide  |

| LVT57 J        | N:20D  | 20 Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide               |

| 74. T57 MSA    | MSA20  | 20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide       |

| 74LV - 574M1 C | M7020  | 20-LCad Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm      |

| 74LVTF.574WM   | M20E   | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide  |

| 74'_VTH574SJ   | N.20D  | 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide               |

| 74LVTH574MSA   | MiSA20 | 20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide       |

| 74LVTH574MTC   | MTC20  | 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide |

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering number.

All packages are lead free per JEDEC: J-STD-020B standard.

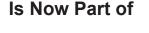

### **Connection Diagram**

### **Pin Description**

| Pin Names                      | Description                 |

|--------------------------------|-----------------------------|

| D <sub>0</sub> –D <sub>7</sub> | Data Inputs                 |

| СР                             | Clock Pulse Input           |

| ŌĒ                             | 3-STATE Output Enable Input |

| O <sub>0</sub> –O <sub>7</sub> | 3-STATE Outputs             |

### Functional Description

The LVT574 ar  $^{\circ}$  Vi 574 c sist of suffit edge-triggered flip-ups with all D-type inputs and 3-STATE in the buffered clock and buffered Output Ene a arc common to all flip-flops. The eight flimops vill one are state of their individual D-type in its the metalthe setup and hold time requirements on a LO -to-HIGH Clock (CP) transition. With the Output Ene ( $\overline{\rm OF}$ ) LOW, the contents of the stock flip-flops are available at the outputs. When the  $\overline{\rm OE}$  is HIGH, the outputs go to the high impedance state. Operation of the  $\overline{\rm OE}$  input does not affect the state of the flip-flops.

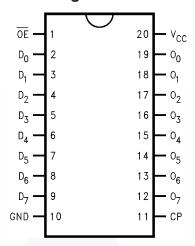

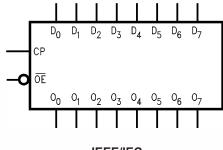

### **Logic Symbols**

### **IEEE/IEC**

### Cruth Table

| 10             | Inputs |    | Outputs        |

|----------------|--------|----|----------------|

| D <sub>n</sub> | СР     | ŌĒ | O <sub>n</sub> |

| Н              |        | L  | Н              |

| L              |        | L  | L              |

| Х              | L      | L  | O <sub>o</sub> |

| Х              | Х      | Н  | Z              |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

∠ = LOW-to-HIGH Transition

O<sub>o</sub> = Previous O<sub>o</sub> before HIGH to LOW of CP

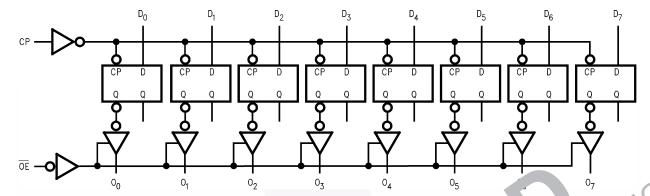

### **Logic Diagram**

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                           | Rating             |

|------------------|-----------------------------------------------------|--------------------|

| V <sub>CC</sub>  | Supply Voltage                                      | -0.5V to +4.6V     |

| VI               | DC Input Voltage                                    | -0.5V to +7.0V     |

| Vo               | DC Output Voltage                                   |                    |

|                  | Output in 3-STATE                                   | -0.5V to +7.0V     |

|                  | Output in HIGH or LOW State <sup>(1)</sup>          | -0.5V to +7.0V     |

| I <sub>IK</sub>  | DC Input Diode Current, V <sub>I</sub> < GND        | -50mA              |

| I <sub>OK</sub>  | DC Output Diode Current, V <sub>O</sub> < GND       | -50mA              |

| Io               | DC Output Current, V <sub>O</sub> > V <sub>CC</sub> |                    |

|                  | Output at HIGH State                                | 64mA               |

|                  | Output at LOW State                                 | 128mA              |

| I <sub>cc</sub>  | DC Supply Current per Supply Pin                    | ±64mA              |

| I <sub>GND</sub> | DC Ground Current per Ground Pin                    | ±128mA             |

| T <sub>STG</sub> | Storage Temperature                                 | -65° C tc → 150° C |

### Note:

1. In Absolute Maximum Rating must be of a ved.

### Recommended Operation Corditions

The Recommended Ope and Continue conditions for actual device operation. Recommended operating conditions are pecified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend excelling to assolute maximum ratings.

| Symb           | Paraniever                                              | Min | Max | Units |

|----------------|---------------------------------------------------------|-----|-----|-------|

|                | Single oltage                                           | 2.7 | 3.6 | V     |

| V <sub>I</sub> | nput Voltage                                            | 0   | 5.5 | V     |

| IOH            | HIGH-Level Output Current                               |     | -32 | mA    |

| JL             | LOW-Leve! Output Current                                |     | 64  | mA    |

| TA             | T <sub>A</sub> Free-Air Operating Temperature           |     | 85  | °C    |

| Δ*/ \V         | Input Edge Rate, $V_{IN} = 0.8V-2.0V$ , $V_{CC} = 3.0V$ | 0   | 10  | ns/V  |

### **DC Electrical Characteristics**

|                                     |                           |                     | $T_A = -40$ °C to +85°C               |                                         |                     |      |       |

|-------------------------------------|---------------------------|---------------------|---------------------------------------|-----------------------------------------|---------------------|------|-------|

| Symbol                              | Parameter                 | V <sub>CC</sub> (V) | Conditions                            | Min.                                    | Typ. <sup>(2)</sup> | Max. | Units |

| V <sub>IK</sub>                     | Input Clamp Diode Voltage | 2.7                 | I <sub>I</sub> = -18mA                |                                         |                     | -1.2 | V     |

| V <sub>IH</sub>                     | Input HIGH Voltage        | 2.7–3.6             | $V_0 \le 0.1V$ or                     | 2.0                                     |                     |      | V     |

| V <sub>IL</sub>                     | Input LOW Voltage         | 2.7–3.6             | $V_O \ge V_{CC} - 0.1V$               |                                         |                     | 0.8  | V     |

| V <sub>OH</sub>                     | Output HIGH Voltage       | 2.7–3.6             | $I_{OH} = -100 \mu A$                 | V <sub>CC</sub> -0.2                    |                     |      | V     |

|                                     |                           | 2.7                 | $I_{OH} = -8mA$                       | 2.4                                     |                     |      | 1     |

|                                     |                           | 3.0                 | $I_{OH} = -32mA$                      | 2.0                                     |                     |      | 1     |

| V <sub>OL</sub>                     | Output LOW Voltage        | 2.7                 | $I_{OL} = 100 \mu A$                  |                                         |                     | 0.2  | V     |

|                                     |                           |                     | I <sub>OL</sub> = 24mA                |                                         |                     | 0.5  |       |

|                                     |                           | 3.0                 | I <sub>OL</sub> = 16mA                |                                         |                     | 0.4  | , G)  |

|                                     |                           |                     | $I_{OL} = 32mA$                       |                                         |                     | 0.5  |       |

|                                     |                           |                     | I <sub>OL</sub> = 64mA                |                                         |                     | 0.55 | 1     |

| I <sub>I(HOLD)</sub> <sup>(3)</sup> | Bushold Input Minimum     | 3.0                 | V <sub>I</sub> = 0.8V                 | 75                                      |                     | 9    | μA    |

|                                     | Drive                     |                     | V <sub>I</sub> = 2.0V                 | -75                                     | 19                  |      | 1     |

| I <sub>I(OD)</sub> (3)              | Bushold Input Over-Drive  | 3.0                 | (4)                                   | 500                                     |                     |      | μA    |

|                                     | Current to Change State   |                     | Tr.                                   | -500                                    | all,                |      | 1     |

| I <sub>I</sub>                      | Input Current             | 3.5                 | \ -5.5V                               | ) \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | 5 7                 | 16   | μA    |

|                                     | Control Pins              | 3.0                 | V <sub>I</sub> = V or V <sub>CC</sub> | 0                                       |                     | ±1   |       |

|                                     | Data Pins                 |                     | $V_I = 0V$                            | 6                                       | 141                 | -5   |       |

|                                     |                           |                     | V <sub>I</sub> = V <sub>CC</sub>      | 100                                     |                     | 1    |       |

| I <sub>OFF</sub>                    | Power Off Leakage Irrent  | U                   | $vV \le V_1 \text{ or } V_0 \le 5.5V$ | 7/                                      |                     | ±100 | μA    |

| I <sub>PU/PD</sub>                  | Power up/ Jwn 3-STA       | 0-1.5               | $V_0 = 0.5V \text{ to } 3.0V,$        |                                         |                     | ±100 | μA    |

|                                     | Output C rent             | 60                  | $V_1 = CND \text{ or } V_{CC}$        |                                         |                     |      |       |

| I <sub>OZL</sub>                    | STATE O akage             | 3.6                 | $V_0 = 0.5V$                          |                                         |                     | -5   | μA    |

|                                     | O OTATE A LIVE            | (0)                 | W 24 24                               |                                         |                     |      | _     |

| 1 11                                | 3-STATE Jutput Leakage    | 3.6                 | $V_C = 3.0V$                          |                                         |                     | 5    | μA    |

| l <sub>ozh</sub> +                  | 3-STATE Oviput Leakage    | 3.6                 | $V_{CC} < V_O \le 5.5V$               |                                         |                     | 10   | μA    |

| OZH                                 | Chire it                  | W.                  |                                       |                                         |                     | 7    |       |

| Icch                                | Power Supply Current      | 3.6                 | Outputs HIGH                          |                                         |                     | 0.19 | mA    |

| locr                                | Power Supply Cur ent      | 3.6                 | Outputs LOW                           |                                         |                     | 5    | mA    |

| locz                                | Power Suprly Current      | 3.6                 | Outputs Disabled                      |                                         |                     | 0.19 | mA    |

| I <sub>CCZ</sub> +                  | Power Surply Current      | 3.6                 | $V_{CC} \le V_O \le 5.5V$ ,           |                                         |                     | 0.19 | mA    |

|                                     |                           |                     | Outputs Disabled                      |                                         |                     |      |       |

| $\Delta I_{CC}$                     | Increase in Power Supply  | 3.6                 | One Input at V <sub>CC</sub> – 0.6V,  |                                         |                     | 0.2  | mA    |

|                                     | Current <sup>(6)</sup>    |                     | Other Inputs at V <sub>CC</sub> or    |                                         |                     |      |       |

### Notes:

- 2. All typical values are at  $V_{CC} = 3.3V$ ,  $T_A = 25^{\circ}C$ .

- 3. Applies to bushold versions only (74LVTH574).

- 4. An external driver must source at least the specified current to switch from LOW-to-HIGH.

- 5. An external driver must sink at least the specified current to switch from HIGH-to-LOW.

- 6. This is the increase in supply current for each input that is at the specified voltage level rather than  $V_{CC}$  or GND.

## Dynamic Switching Characteristics<sup>(7)</sup>

|                  |                                                 |                     | Conditions                      | 1    | A = 25°0 | 2    |       |

|------------------|-------------------------------------------------|---------------------|---------------------------------|------|----------|------|-------|

| Symbol           | Parameter                                       | V <sub>CC</sub> (V) | $C_L = 50 pF, R_L = 500 \Omega$ | Min. | Тур.     | Max. | Units |

| V <sub>OLP</sub> | Quiet Output Maximum<br>Dynamic V <sub>OL</sub> | 3.3                 | (8)                             |      | 0.8      |      | V     |

| V <sub>OLV</sub> | Quiet Output Minimum<br>Dynamic V <sub>OL</sub> | 3.3                 | (8)                             |      | -0.8     |      | V     |

### Notes:

- 7. Characterized in SOIC package. Guaranteed parameter, but not tested.

- 8. Max number of outputs defined as (n). n-1 data inputs are driven 0V to 3V. Output under test held LOW.

### **AC Electrical Characteristics**

|                  |                                         |                          | -40° to<br>50pF, = | - 10°             | N      | OF    |

|------------------|-----------------------------------------|--------------------------|--------------------|-------------------|--------|-------|

|                  |                                         | V <sub>CC</sub> = 3. ( ± | 3V                 | V <sub>CC</sub> = | - ?.7V |       |

| Symbol           | Parameter                               | Min. ~~o.\               | 1                  | Win.              | Max.   | Units |

| $f_{MAX}$        | Maximum Clock Frequency                 | 150                      |                    | 150               |        | MHz   |

| t <sub>PHL</sub> | Propagation Delay, CP to O <sub>n</sub> | 1.8                      | 4.6                | 1.80              | 5.3    | ns    |

| t <sub>PLH</sub> |                                         | 8                        | 4.5                | `.σ               | 5.3    |       |

| t <sub>PZL</sub> | Output Enable Time                      | 1.5                      | 5.2                | 1.5               | 6.1    | ns    |

| t <sub>PZH</sub> |                                         | 1.5                      | 1.8                | 1.5               | 5.9    |       |

| $t_{PLZ}$        | Output Disable ne                       | 59                       | 4.1                | 2.0               | 4.4    | ns    |

| $t_{PHZ}$        |                                         | 2.0                      | 4.8                | 2.0               | 5.1    |       |

| t <sub>S</sub>   | Setup me                                | 2.0                      |                    | 2.4               |        | ns    |

| t <sub>H</sub>   | Hold Tin                                | 0.3                      |                    | 0.0               |        | ns    |

| t <sub>W</sub>   | uise 'idth                              | 3.3                      |                    | 3.3               |        | ns    |

| t 7SL            | to Ou ou Skew <sup>(10)</sup>           |                          | 1.0                |                   | 1.0    | ns    |

### 'es:

- 9. If tyre all values are at  $V_{C,C} = 0.3 \text{ V}$ ,  $T_{\Lambda} = 25^{\circ} \text{ C}$ .

- 10. Show is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, elinor HiGH-to-LOW (tostill) or LOW-to-HIGH (tostill).

### Capacitance<sup>(11)</sup>

| Symbol           | Parameter          | Conditions                                 | Typical | Units |

|------------------|--------------------|--------------------------------------------|---------|-------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{CC} = Open, V_I = 0V or V_{CC}$        | 4       | pF    |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 3.0V$ , $V_{O} = 0V$ or $V_{CC}$ | 6       | pF    |

### Note:

11. Capacitance is measured at frequency f = 1MHz, per MIL-STD-883, Method 3012.

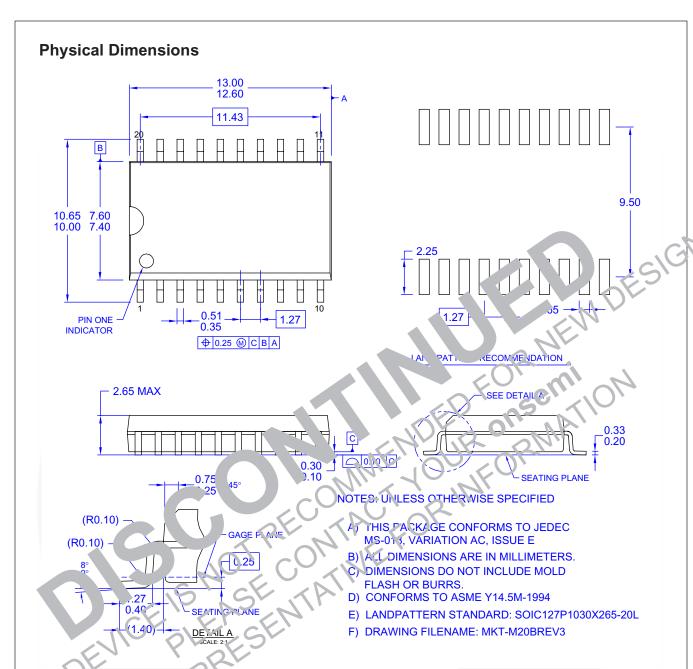

Figure 1. 20-Level Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

### Physical Dimensions (Continued) 12.6±0.10 0.40 TYP -A-20 11 12 11 5.01 TYP 5.3±0.10 9.27 TYP 7.8 -B-3.9 (2.13)△ 0.2 C B A 10 ALL LEAD TIPS PIN #1 IDENT. J.6 TYP 1.27 ALL LEAD TIPS △ 0.1 C 2.1 MAX.--C-0.15 - 0.255.35-0.51 1.27 TYP 7° TYP ARE IN MILLIMATER GAGE PLANE 0°-8° TYP CONFORMS TO LIAU EDG-7320 REGISTRATION ESTABLISHED IN DECEMBER, 1998. D.Y.L.NSIONS ARE EXCLUSIVE OF TURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS. $0.60\pm0.15$ SEATING PLANE 1.25 -DETAIL A

Figure 2. 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

M20DREVC

9.12

# Physical Dimensions (Continued) 0.68 TYP В 5.3±0.30 7.8 10 3.9 ○ 0.2 C A B PIN #1 IDENT. RECOMMENDATIONS △ 0.10 C ALL LEAD TIPS 1.75±u 2.0 MAX. 0.65 TYP 0.15M L

NOTES

- A. NFORMS TO JEDIC REGISTRATION MO-150, ARIATION AE, LATE 1/94.

- J. DIMENSIONS ARE IN MILLINIZIERS.

- C. DIMERISIONS ARE EXCLUSIVE CF DUPRS, MOLD FLASH, AND THE BAR EXTRUSIONS

- L DIMENSIONS AND TOLERAILC'S PER ASME Y14.5M 1994.

MSA20REVB

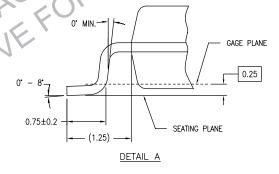

Figure 3. 20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

# Physical Dimensions (Continued) -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.20 -0.

MTC20REVD1

D. DIMENSIONS AND TO ERANCES PER ANSI Y14.5M, 1982.

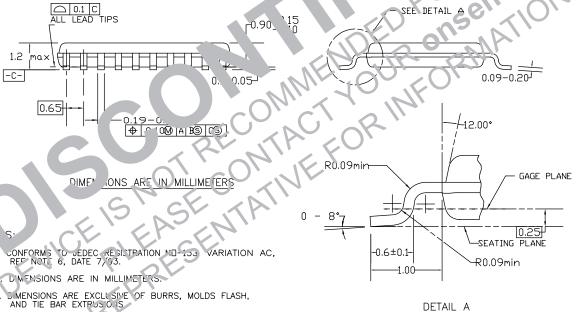

Figure 4. 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

Build it Now™ CorePLUS™  $CROSSVOLT^{\text{TM}}$ CTL™

Current Transfer Logic™ EcoSPARK®

EZSWITCH™ \*

Fairchild<sup>®</sup> Fairchild Semiconductor® FACT Quiet Series™

FACT<sup>®</sup>  $\mathsf{FAST}^{\mathbb{R}}$ FastvCore™ FlashWriter® FPS™  $\mathsf{FRFET}^{\scriptscriptstyle{\textcircled{\tiny{\$}}}}$

Global Power Resource<sup>™</sup>

Green FPS™

Green FPS™e-Series™

GTO™ i-Lo™ IntelliMAX™ ISOPLANAR™ MegaBuck™

MICROCOUPLER™ MicroFET™

MicroPak™ MillerDrive™ Motion-SPM™ OPTOLOGIC®

**OPTOPLANAR®**

PDP-SPM™ Power220® POWEREDGE® Power-SPM™ PowerTrench<sup>®</sup>

Programmable Active Droop™

OFFT<sup>©</sup> QS™

QT Optoelectronics™ Quiet Series™ RapidConfigure™ SMART START SPM<sup>®</sup> STEA' TH' Superl T™

~SO 43 S eic Su<sub>k</sub> SOT -8 SupreMOS™ SyncFET™

SYSTEM ® GENERAL The Power Franchise®

bwer riny ost™ TinyB、™ TinyLo\_\_\_® VY TO Ti y Power TinyP'VM™ TinyVVire M

บSerDes™ . CHC® Ultra FRFET™

Ur.'⊏.∵T™ **√CX**™

### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVE RILL TITO. LE CHALLES WITHOUT FURTHER NOT CE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FLOCTION, RILL SIGN. FAIR CHALLES NOT A SSUME AND LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CHURCH DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE SOLVETHER THESES PECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND UNDITIONS. ..-ICALLY THE WARRANTY THERE'N, WHICH COVERS THESE PRODUCTS.

### LIFE SUPPORT OLICY

FAIRCHILE PL RE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS V HOUT THE XPRESS VIRITEN AF PROVAL OF TAIRCHILD SEMICONDUCTOR CORPORATION.

Life s por devices or systems are devices or systems thich a) are intended for surgical implant into the body or port o suscin life, and (c) whose failure to perform when properly used in a condance with a structions for use provided in the labeling, can be reasonably expected to result in a significant injury of the uper.

2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### PRODUCT STATUS DEFINITIONS

### **Definition of Terms**

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                               |

|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production       | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.                                      |

Rev. I33

<sup>\*</sup> EZSWITCH™ and FlashWriter® are trademarks of Stem Ge ral Coi, ration, used under licence in Fairchiid Semiconductor.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor nakes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnif

### **PUBLICATION ORDERING INFORMATION**

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative