To our customers,

---

## Old Company Name in Catalogs and Other Documents

---

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <http://www.renesas.com>

April 1<sup>st</sup>, 2010

Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<http://www.renesas.com>)

Send any inquiries to <http://www.renesas.com/inquiry>.

## Notice

1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

(Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

(Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# M61311SP/M61316SP

## I<sup>2</sup>C BUS Controlled Video Pre-amp for High Resolution Color Display

REJ03F0199-0201

Rev.2.01

Mar 31, 2008

### Description

M61311SP/M61316SP is semiconductor integrated circuit for CRT display monitor.

It includes OSD blanking, OSD mixing, retrace blanking, video detector, sync separator, wide band amplifier, brightness control.

Main/sub contrast, video response adjust, ret BLK adjust, 4ch D/A OUT and OSD level adjust function can be controlled by I<sup>2</sup>C BUS.

### Features

|                             |                                                                           |

|-----------------------------|---------------------------------------------------------------------------|

| • Frequency band width: RGB | 200 MHz (M61311SP)<br>150 MHz (M61316SP)<br>(4 V <sub>P-P</sub> at -3 dB) |

| OSD                         | 80 MHz                                                                    |

| • Input: RGB                | 0.7 V <sub>P-P</sub> (typ.)                                               |

| OSD                         | 3.5 V to 5.0 V (positive)                                                 |

| OSD BLK                     | 3.5 V to 5.0 V (positive)                                                 |

| Retrace BLK                 | 2.5 V to 5.0 V (positive)                                                 |

| Clamp pulse                 | 2.5 V to 5.0 V (positive)                                                 |

| Output: RGB                 | 5 V <sub>P-P</sub> (at Brightness less than 2 V <sub>DC</sub> )           |

| OSD                         | 4 V <sub>P-P</sub> (at Brightness less than 2 V <sub>DC</sub> )           |

| Sync OUT                    | 5 V <sub>P-P</sub>                                                        |

| Video det OUT               | High = 4.2 V <sub>DC</sub> , Low = 0.7 V <sub>DC</sub>                    |

### Application

CRT display monitor

### Recommended Operating Conditions

|                       |                                                        |

|-----------------------|--------------------------------------------------------|

| Supply voltage range: | 11.50 V to 12.50 V (V3, V29)<br>4.75 V to 5.25 V (V11) |

| Rated supply voltage: | 12.00 V (V3, V29)<br>5.00 V (V11)                      |

### Major Specification

I<sup>2</sup>C BUS controlled 3ch video pre-amp with OSD mixing function and retrace blanking function.

The difference in the M61311SP/M61316SP is RGB video frequency band width.

M61311SP is 200 MHz, M61316SP is 150 MHz in conditions RGB output is 4 V<sub>P-P</sub> at -3 dB.

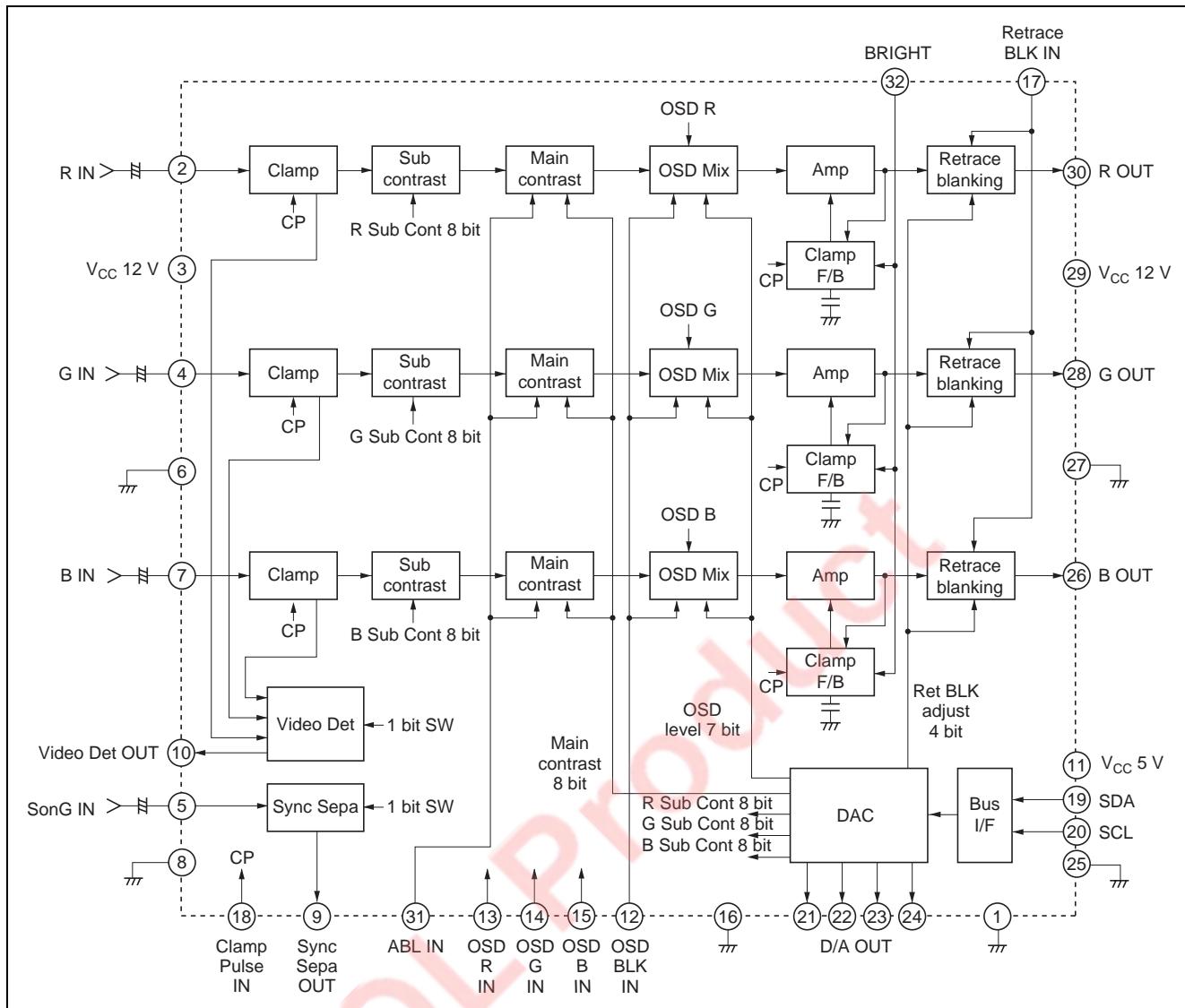

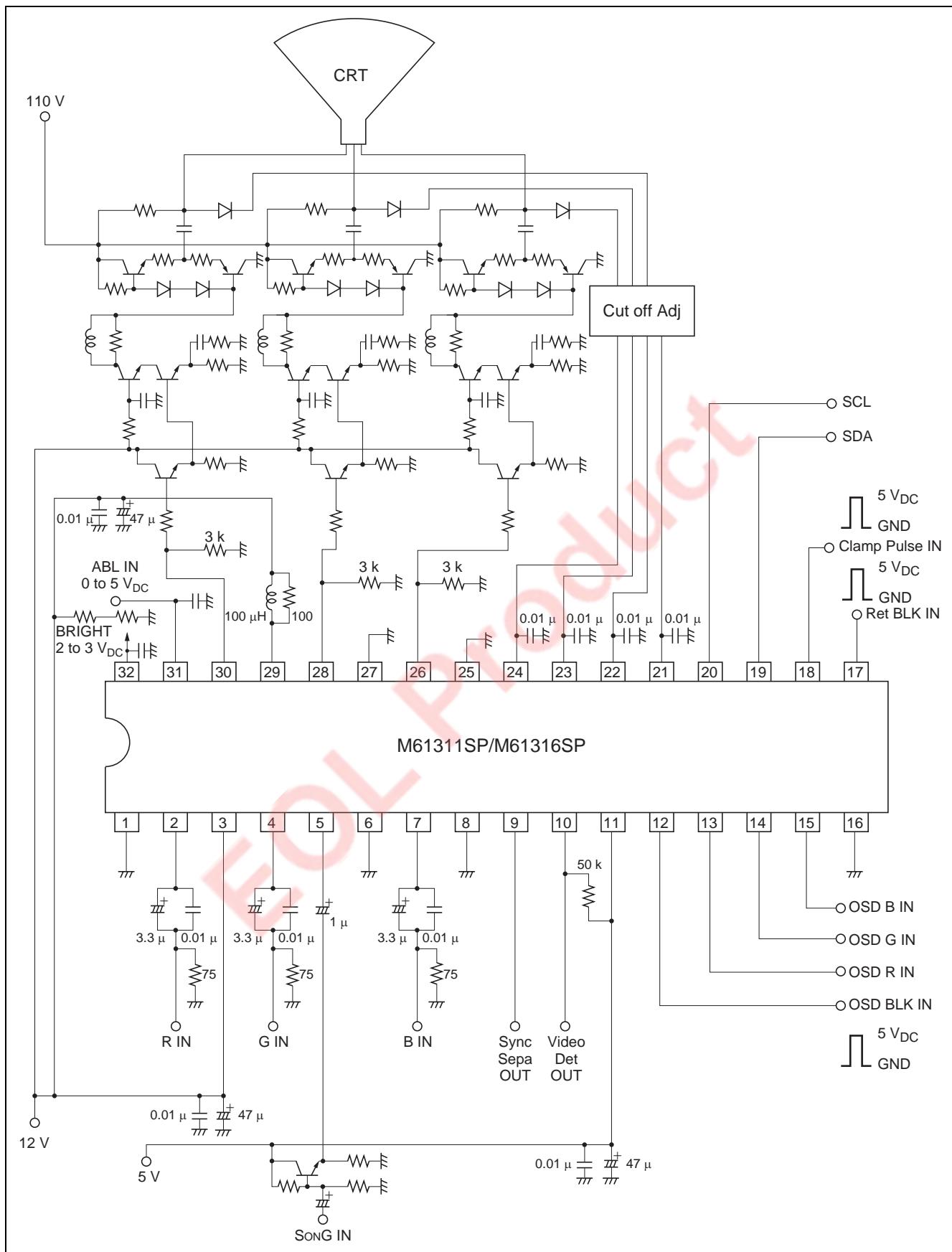

## Block Diagram

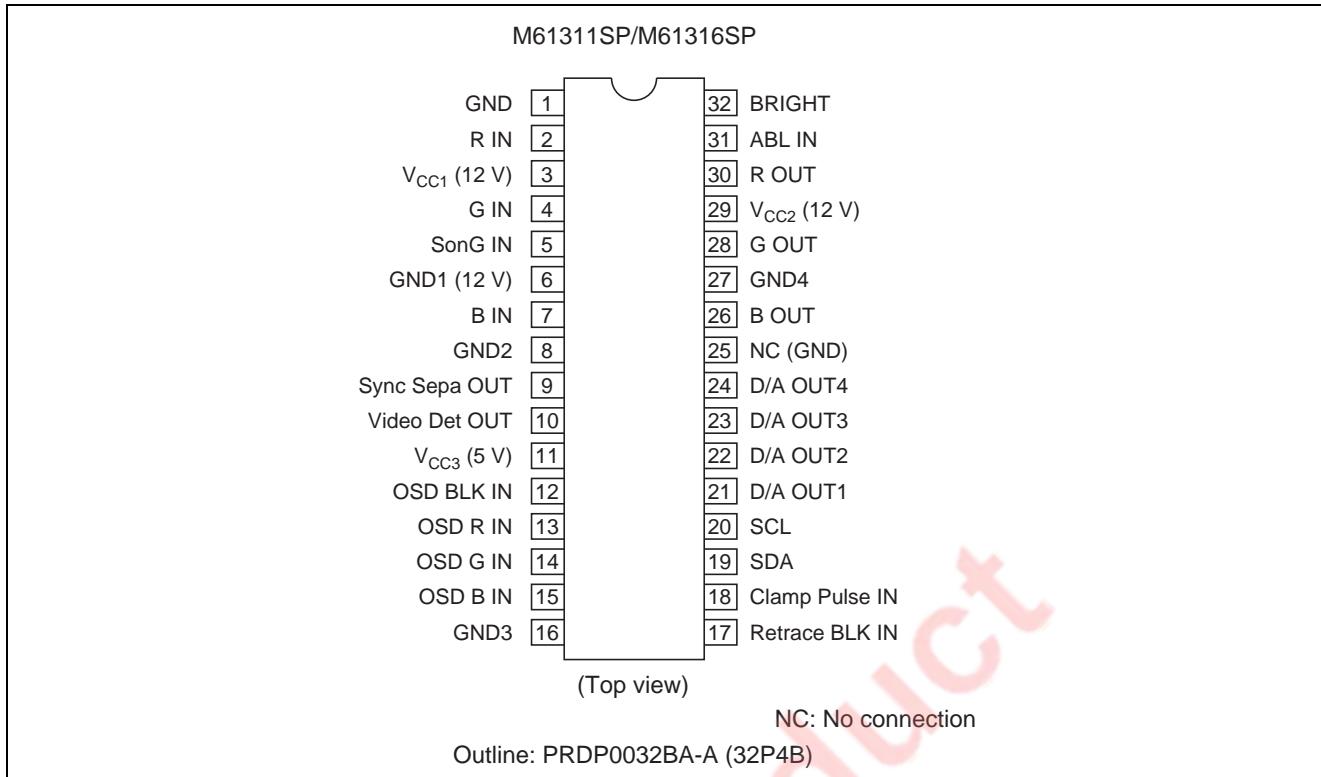

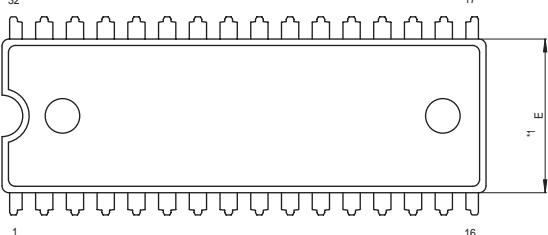

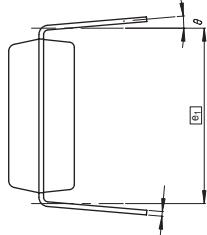

## Pin Arrangement

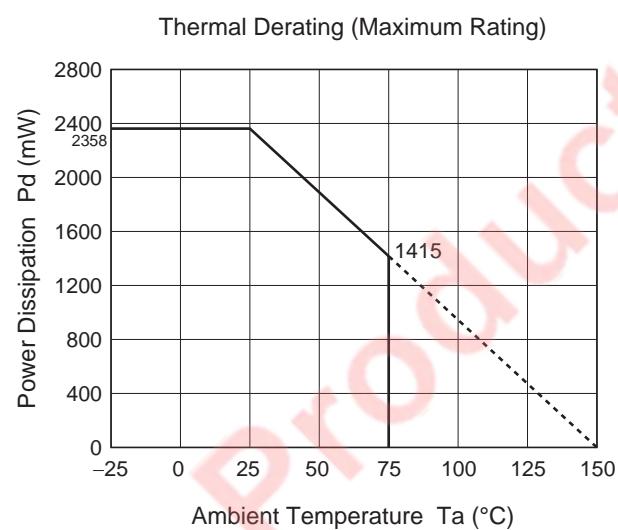

**Absolute Maximum Ratings**

(Ta = 25°C)

| Item                       | Symbol              | Ratings      | Unit |

|----------------------------|---------------------|--------------|------|

| Supply voltage (pin 3, 29) | V <sub>cc12</sub>   | 13.0         | V    |

| Supply voltage (pin 11)    | V <sub>cc5</sub>    | 6.0          | V    |

| Power dissipation          | P <sub>d</sub>      | 2358         | mW   |

| Ambient temperature        | T <sub>opr</sub>    | -20 to +75   | °C   |

| Storage temperature        | T <sub>stg</sub>    | -40 to +150  | °C   |

| Recommended supply 12      | V <sub>opr12</sub>  | 12.0         | V    |

| Recommended supply 5       | V <sub>opr5</sub>   | 5.0          | V    |

| Voltage range 12           | V <sub>opr'12</sub> | 11.5 to 12.5 | V    |

| Voltage range 5            | V <sub>opr'5</sub>  | 4.75 to 5.25 | V    |

**BUS Control Table**

(1) Slave address:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | R/W |       |

|----|----|----|----|----|----|----|-----|-------|

| 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0   | = 88H |

(2) Slave receiver format:

Normal mode

| 8 bit |               | 8 bit |             |  | 8 bit |           |  |   |   |

|-------|---------------|-------|-------------|--|-------|-----------|--|---|---|

| S     | Slave address | A     | Sub address |  | A     | Data byte |  | A | P |

Auto increment mode

| 8 bit                               |               | 8 bit                               |                         |   | 8 bit |                               |  |   |

|-------------------------------------|---------------|-------------------------------------|-------------------------|---|-------|-------------------------------|--|---|

| S                                   | Slave address | A                                   | Sub address (0XH) + 10H |   | A     | Data byte (Sub address = 0XH) |  | A |

| 8 bit                               |               | 8 bit                               |                         |   | 8 bit |                               |  |   |

| Data<br>(Sub address = 0 (X + 1) H) | A             | Data<br>(Sub address = 0 (X + 2) H) |                         | A |       |                               |  |   |

Note: S: Start condition, A: Acknowledge, P: Stop condition

(3) Sub address byte and data byte format:

| Function          | Bit | Sub Add. | Data Byte (Top: Byte Format, Under: Start Condition) |     |     |     |     |     |     |     |

|-------------------|-----|----------|------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

|                   |     |          | D7                                                   | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Main contrast     | 8   | 00H      | A07                                                  | A06 | A05 | A04 | A03 | A02 | A01 | A00 |

|                   |     |          | 0                                                    | 0   | 0   | 0   | 0   | 0   | 0   | 1*  |

| Sub contrast R    | 8   | 01H      | A17                                                  | A16 | A15 | A14 | A13 | A12 | A11 | A10 |

|                   |     |          | 0                                                    | 0   | 0   | 0   | 0   | 0   | 0   | 1*  |

| Sub contrast G    | 8   | 02H      | A27                                                  | A26 | A25 | A24 | A23 | A22 | A21 | A20 |

|                   |     |          | 0                                                    | 0   | 0   | 0   | 0   | 0   | 0   | 1*  |

| Sub contrast B    | 8   | 03H      | A37                                                  | A36 | A35 | A34 | A33 | A32 | A31 | A30 |

|                   |     |          | 0                                                    | 0   | 0   | 0   | 0   | 0   | 0   | 1*  |

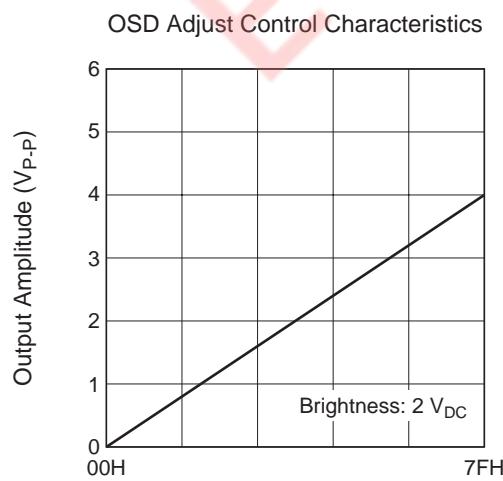

| OSD level         | 7   | 04H      | —                                                    | A46 | A45 | A44 | A43 | A42 | A41 | A40 |

|                   |     |          | —                                                    | 0   | 0   | 0   | 0   | 0   | 0   | 1*  |

| RE-BLK adjust     | 4   | 05H      | —                                                    | —   | —   | —   | A53 | A52 | A51 | A50 |

|                   |     |          | —                                                    | —   | —   | —   | 0   | 0   | 0   | 1*  |

| Sharpness control | 4   | 06H      | —                                                    | —   | —   | —   | A63 | A62 | A61 | A60 |

|                   |     |          | —                                                    | —   | —   | —   | 0   | 0   | 0   | 1*  |

| Sync Sepa SW      | 1   |          | —                                                    | —   | —   | A64 | —   | —   | —   | —   |

|                   |     |          | —                                                    | —   | —   | 0   | —   | —   | —   | —*  |

| Video Det SW      | 1   |          | —                                                    | —   | A65 | —   | —   | —   | —   | —   |

|                   |     |          | —                                                    | —   | 0   | —   | —   | —   | —   | —*  |

| Test mode         | 2   |          | A67                                                  | A66 | —   | —   | —   | —   | —   | —   |

|                   |     |          | 0                                                    | 0   | —   | —   | —   | —   | —   | —*  |

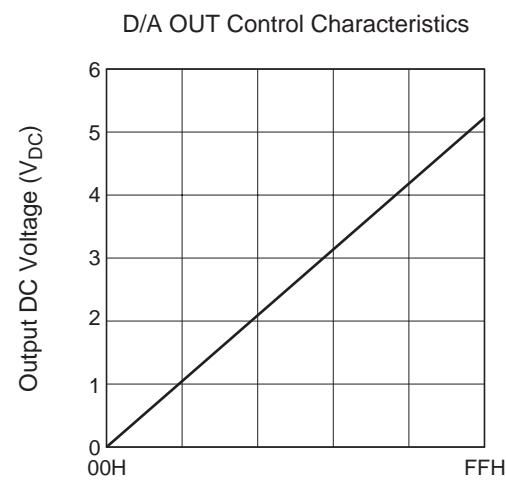

| D/A OUT1          | 8   | 07H      | A77                                                  | A76 | A75 | A74 | A73 | A72 | A71 | A70 |

|                   |     |          | 0                                                    | 0   | 0   | 0   | 0   | 0   | 0   | 1*  |

| D/A OUT2          | 8   | 08H      | A87                                                  | A86 | A85 | A84 | A83 | A82 | A81 | A80 |

|                   |     |          | 0                                                    | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| D/A OUT3          | 8   | 09H      | A97                                                  | A96 | A95 | A94 | A93 | A92 | A91 | A90 |

|                   |     |          | 0                                                    | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| D/A OUT4          | 8   | 0AH      | AA7                                                  | AA6 | AA5 | AA4 | AA3 | AA2 | AA1 | AA0 |

|                   |     |          | 0                                                    | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Note: pre-data

Sub add. 06H

Sync Sepa SW A64

0: Sync Sepa ON

1: Sync Sepa OFF

Video Det SW A65

0: Video Det ON

1: Video Det OFF

Always set up as A66 and A67 in 0

For I<sup>2</sup>C Data, please transfer in the period of vertical.

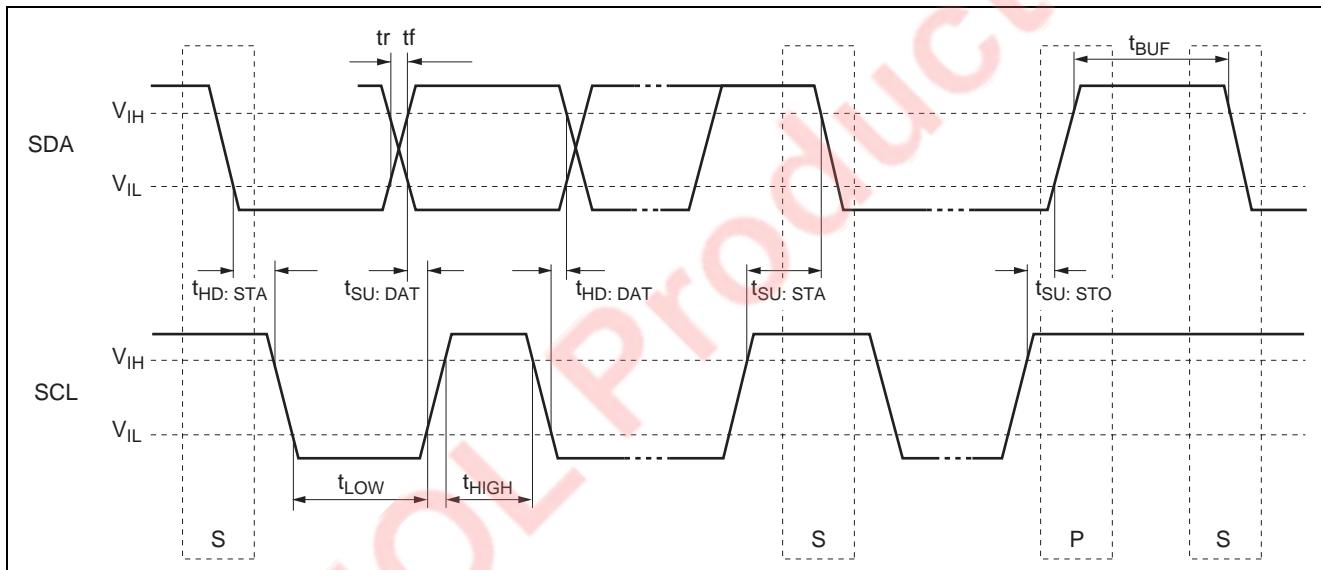

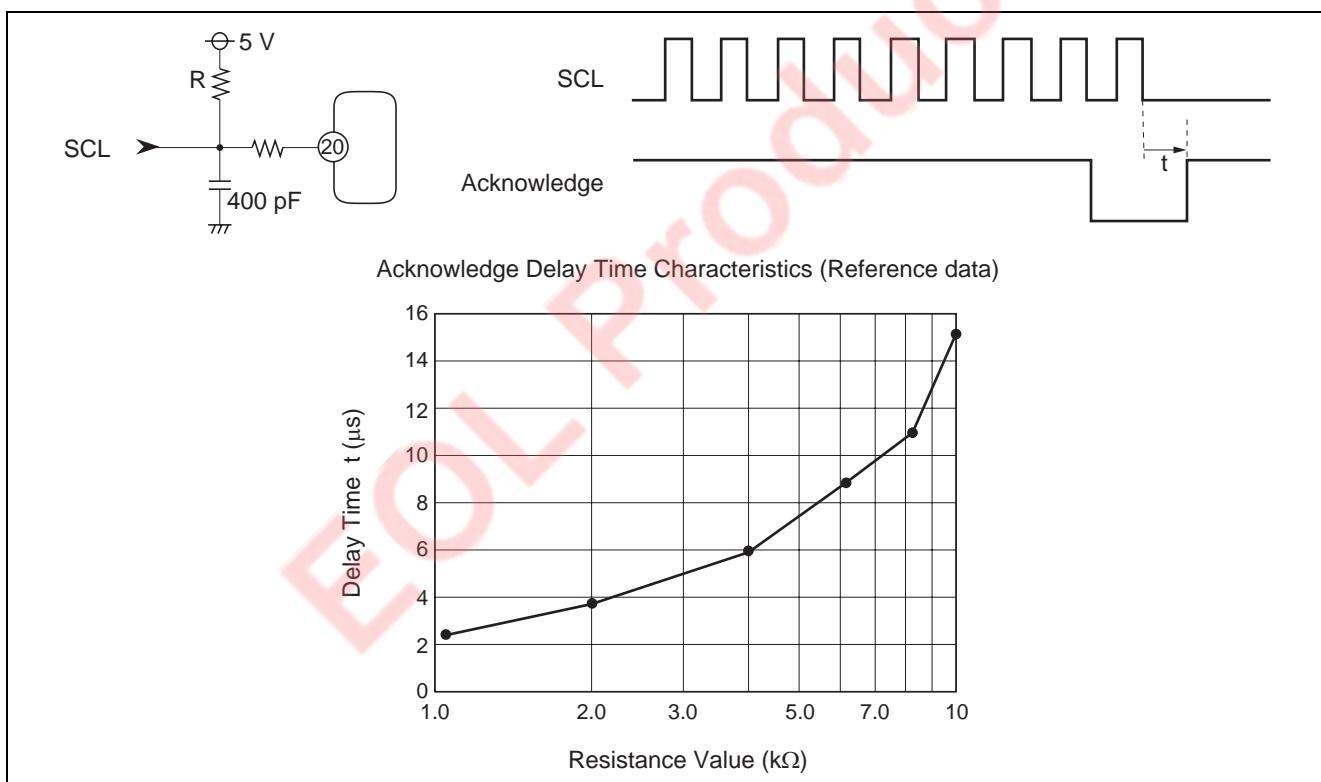

**I<sup>2</sup>C BUS Control Section SDA, SCL Characteristics**

| Item                                                                            | Symbol       | Min.        | Max. | Unit    |

|---------------------------------------------------------------------------------|--------------|-------------|------|---------|

| Min. input LOW voltage                                                          | $V_{IL}$     | -0.5        | 1.5  | V       |

| Max. input HIGH voltage                                                         | $V_{IH}$     | 3.0         | 5.5  | V       |

| SCL clock frequency                                                             | $f_{SCL}$    | 0           | 400  | kHz     |

| Time the bus must be free before a new transmission can start                   | $t_{BUF}$    | 1.3         | —    | $\mu s$ |

| Hold time start condition. After this period the first clock pulse is generated | $t_{HD:STA}$ | 0.6         | —    | $\mu s$ |

| The LOW period of the clock                                                     | $t_{LOW}$    | 1.3         | —    | $\mu s$ |

| The HIGH period of the clock                                                    | $t_{HIGH}$   | 0.6         | —    | $\mu s$ |

| Set up time for start condition (Only relevant for a repeated start condition)  | $t_{SU:STA}$ | 0.6         | —    | $\mu s$ |

| Hold time DATA                                                                  | $t_{HD:DAT}$ | 0           | 0.9  | $\mu s$ |

| Set-up time DATA                                                                | $t_{SU:DAT}$ | 100         | —    | ns      |

| Rise time of both SDA and SCL lines                                             | $tr$         | $20+0.1C_b$ | 300  | ns      |

| Fall time of both SDA and SCL lines                                             | $tf$         | $20+0.1C_b$ | 300  | ns      |

| Set-up time for stop condition                                                  | $t_{SU:STO}$ | 0.6         | —    | $\mu s$ |

**Timing Chart**

## Electrical Characteristics

(V<sub>CC</sub> = 12 V, 5 V; Ta = 25°C, unless otherwise noted)

| Item                                                  | Symbol            | Limits |      |      | Test Point       | Input      |        |     |     |     |       |     |        |        |        |        |        | CTL Vol | BUS CTL (H) |        |               |                |                |                |             |                |           |       |       |        |          |               |               |               |

|-------------------------------------------------------|-------------------|--------|------|------|------------------|------------|--------|-----|-----|-----|-------|-----|--------|--------|--------|--------|--------|---------|-------------|--------|---------------|----------------|----------------|----------------|-------------|----------------|-----------|-------|-------|--------|----------|---------------|---------------|---------------|

|                                                       |                   | Min.   | Typ. | Max. |                  | Unit       | 3 12 V | 2 R | 4 G | 5 S | 6 G   | 7 B | 12 OSD | 13 OSD | 14 OSD | 15 OSD | 17 RET | 18 CP   | 31 ABL      | 32 BRT | 00H Main cont | 01H Sub R cont | 02H Sub G cont | 03H Sub B cont | 04H OSD Adj | 05H Re-BLK Adj | 06H Sharp | 06H S | 06H G | 06H B  | 06H VDET | 07H D/A OUT 1 | 08H D/A OUT 2 | 09H D/A OUT 3 |

| 5 V Circuit current1 power save mode                  | I <sub>CC1</sub>  | —      | 6    | 10   | mA               | IB         | a      | a   | a   | a   | a     | a   | a      | a      | a      | a      | a      | b       | 5           | 2      | FF 255        | FF 255         | FF 255         | FF 255         | 00 0        | 00 0           | 08 0      | 0 0   | 0 0   | 0 0    | 00 0     | 00 0          | 00 0          | 00 0          |

| 12 V Circuit current2 normal mode                     | I <sub>CC2</sub>  | —      | 105  | 130  | mA               | IA         | b      | a   | a   | a   | a     | a   | a      | a      | a      | a      | a      | b       | 5           | 2      | FF 255        | FF 255         | FF 255         | FF 255         | 00 0        | 00 0           | 08 0      | 0 0   | 0 0   | 0 0    | 00 0     | 00 0          | 00 0          | 00 0          |

| 5 V Circuit current3 normal mode                      | I <sub>CC3</sub>  | —      | 4    | 8    | mA               | IB         | b      | a   | a   | a   | a     | a   | a      | a      | a      | a      | a      | b       | 5           | 2      | FF 255        | FF 255         | FF 255         | FF 255         | 00 0        | 00 0           | 08 0      | 0 0   | 0 0   | 0 0    | 00 0     | 00 0          | 00 0          | 00 0          |

| Output dynamic range                                  | V <sub>max</sub>  | 7.5    | 9    | —    | V <sub>DC</sub>  | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 5       | 0.5         | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Maximum input                                         | V <sub>max</sub>  | 1.4    | —    | —    | V <sub>P-P</sub> | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 5       | 2           | 46 70  | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Maximum gain                                          | G <sub>V</sub>    | 16     | 17.5 | 19   | dB               | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 5       | 2           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Relative maximum gain                                 | ΔG <sub>V</sub>   | 0.8    | 1.0  | 1.2  | —                | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

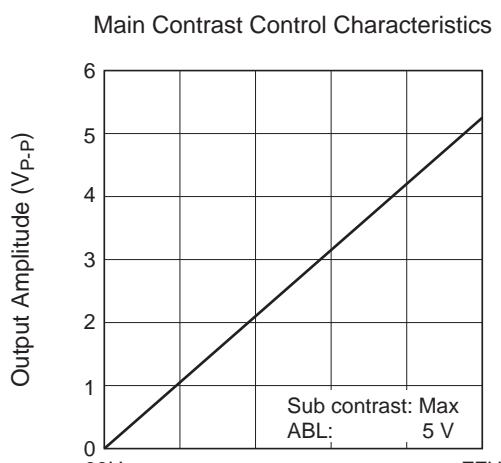

| Main contrast control characteristics1 (Max.)         | V <sub>C1</sub>   | 3.3    | 4    | 4.7  | V <sub>P-P</sub> | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 5       | 2           | C8 200 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Main contrast control relative characteristics1       | ΔV <sub>C1</sub>  | 0.8    | 1.0  | 1.2  | —                | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | C8 200 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Main contrast control characteristics2 (Typ.)         | V <sub>C2</sub>   | 2.3    | 2.8  | 3.3  | V <sub>P-P</sub> | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 5       | 2           | 80 128 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Main contrast control relative characteristics2       | ΔV <sub>C2</sub>  | 0.8    | 1.0  | 1.2  | —                | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | 80 128 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Main contrast control characteristics3 (Min.)         | V <sub>C3</sub>   | 0.25   | 0.55 | 0.85 | V <sub>P-P</sub> | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 5       | 2           | 10 16  | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Main contrast control relative characteristics3       | ΔV <sub>C3</sub>  | -0.2   | 0    | 0.2  | V <sub>P-P</sub> | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | 10 16  | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

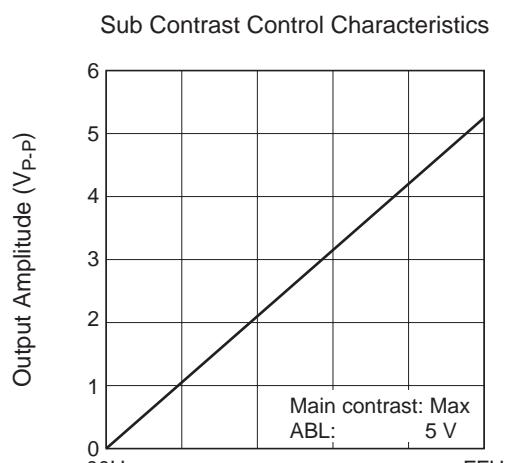

| Sub contrast control characteristics1 (Max.)          | V <sub>S1</sub>   | 3.3    | 4    | 4.7  | V <sub>P-P</sub> | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 5       | 2           | FF 255 | C8 200        | C8 200         | C8 200         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Sub contrast control relative characteristics1        | ΔV <sub>S1</sub>  | 0.8    | 1.0  | 1.2  | —                | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 255 | C8 200        | C8 200         | C8 200         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Sub contrast control characteristics2 (Typ.)          | V <sub>S2</sub>   | 2.3    | 2.8  | 3.3  | V <sub>P-P</sub> | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 5       | 2           | FF 255 | 80 128        | 80 128         | 80 128         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Sub contrast control relative characteristics2        | ΔV <sub>S2</sub>  | 0.8    | 1.0  | 1.2  | —                | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 255 | 80 128        | 80 128         | 80 128         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Sub contrast control characteristics3 (Min.)          | V <sub>S3</sub>   | 0.2    | 0.5  | 0.8  | V <sub>P-P</sub> | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 5       | 2           | FF 255 | 10 16         | 10 16          | 10 16          | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Sub contrast control relative characteristics3        | ΔV <sub>S3</sub>  | -0.2   | 0    | 0.2  | V <sub>P-P</sub> | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 255 | 10 16         | 10 16          | 10 16          | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

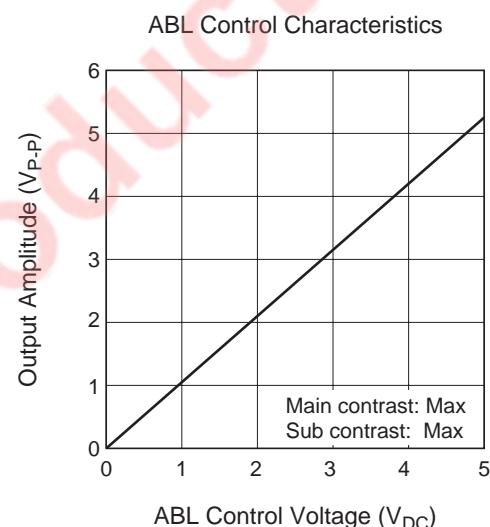

| ABL control characteristics1                          | ABL1              | 3.4    | 4.2  | 5.0  | V <sub>P-P</sub> | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 4       | 2           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| ABL control relative characteristics1                 | ΔABL1             | 0.8    | 1.0  | 1.2  | —                | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| ABL control characteristics2                          | ABL2              | 1.5    | 2.0  | 2.5  | V <sub>P-P</sub> | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 2       | 2           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| ABL control relative characteristics2                 | ΔABL2             | 0.8    | 1.0  | 1.2  | —                | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| ABL control characteristics3                          | ABL3              | -0.3   | 0    | 0.3  | V <sub>P-P</sub> | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 0       | 2           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| ABL control relative characteristics3                 | ΔABL3             | -0.2   | 0    | 0.2  | V <sub>P-P</sub> | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

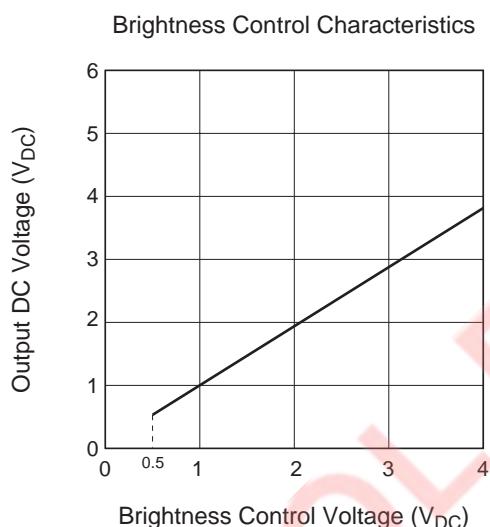

| Brightness control characteristics1                   | VB1               | 3.4    | 3.8  | 4.2  | V <sub>DC</sub>  | 26, 28, 30 | b      | a   | a   | a   | a     | a   | a      | a      | a      | a      | b      | 5       | 4           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Brightness control relative characteristics1          | ΔVB1              | -0.3   | 0    | 0.3  | V                | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Brightness control characteristics2                   | VB2               | 1.6    | 1.9  | 2.2  | V <sub>DC</sub>  | 26, 28, 30 | b      | a   | a   | a   | a     | a   | a      | a      | a      | a      | b      | 5       | 2           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Brightness control relative characteristics2          | ΔVB2              | -0.3   | 0    | 0.3  | V                | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Brightness control characteristics3                   | VB3               | 0.3    | 0.5  | 0.7  | V <sub>DC</sub>  | 26, 28, 30 | b      | a   | a   | a   | a     | a   | a      | a      | a      | a      | b      | 5       | 0.5         | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Brightness control relative characteristics3          | ΔVB3              | -0.3   | 0    | 0.3  | V                | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Pulse characteristics1 (4 V <sub>P-P</sub> )          | Tr                | —      | 2.2  | 3.0  | ns*              | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 5       | 2           | FF 200 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Relative pulse characteristics1 (4 V <sub>P-P</sub> ) | ΔTr               | -0.8   | 0    | 0.8  | ns               | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 200 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Pulse characteristics2 (4 V <sub>P-P</sub> )          | Tf                | —      | 2.2  | 3.0  | ns*              | 26, 28, 30 | b      | b   | b   | a   | b     | a   | a      | a      | a      | a      | b      | 5       | 2           | FF 200 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Relative pulse characteristics2 (4 V <sub>P-P</sub> ) | ΔTf               | -0.8   | 0    | 0.8  | ns               | —          | —      | —   | —   | —   | —     | —   | —      | —      | —      | —      | —      | —       | —           | FF 200 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Clamp pulse threshold voltage                         | V <sub>thCP</sub> | 0.7    | 1.5  | 2.3  | V <sub>DC</sub>  | 26, 28, 30 | b      | a   | a   | a   | a     | a   | a      | a      | a      | a      | b      | 5       | 2           | FF 255 | FF 255        | FF 255         | FF 255         | 00 0           | 00 0        | 08 0           | 0 0       | 0 0   | 0 0   | FF 255 | FF 255   | FF 255        | FF 255        |               |

| Clamp pulse minimum width                             | W <sub>CP</sub>   | 0.2    | —    | —    | μs               | 26, 28, 30 | b      | a   | a   | a   | a</td |     |        |        |        |        |        |         |             |        |               |                |                |                |             |                |           |       |       |        |          |               |               |               |

## Electrical Characteristics (cont.)

| Item                                         | Symbol   | Limits |      |      | Test Point       | Input              |        |        |           |        |                          |                          |                          |                          |                          |          |            | CTL Vol    | BUS CTL (H)   |                |                |                |             |                |               |             |             |               |               |               |               |

|----------------------------------------------|----------|--------|------|------|------------------|--------------------|--------|--------|-----------|--------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|----------|------------|------------|---------------|----------------|----------------|----------------|-------------|----------------|---------------|-------------|-------------|---------------|---------------|---------------|---------------|

|                                              |          | Min.   | Typ. | Max. |                  | 3 V <sub>Vcc</sub> | 2 R IN | 4 G IN | 5 SonG IN | 7 B IN | 12 OSD <sub>BLK</sub> IN | 13 OSD <sub>BLK</sub> IN | 14 OSD <sub>BLK</sub> IN | 15 OSD <sub>BLK</sub> IN | 17 RET <sub>BLK</sub> IN | 18 CP IN | 31 ABL (V) | 32 BRT (V) | 00H Main cont | 01H Sub R cont | 02H Sub G cont | 03H Sub B cont | 04H OSD Adj | 05H Re-BLK Adj | 06H Sharpness | 07H SonG SW | 08H VDET SW | 07H D/A OUT 1 | 08H D/A OUT 2 | 09H D/A OUT 3 | 0AH D/A OUT 4 |

| OSD pulse characteristics1                   | OTr      | —      | 2    | 5    | ns               | 26, 28, 30         | b      | a      | a         | a      | a                        | b                        | b                        | b                        | a                        | b        | 5          | 2          | FF 255        | FF 255         | FF 255         | FF 255         | FF 111      | FF 127         | 00 08         | 08 0 0      | FF 255      | FF 255        | FF 255        | FF 255        |               |

| OSD pulse characteristics2                   | OTf      | —      | 4    | 7    | ns               | 26, 28, 30         | b      | a      | a         | a      | a                        | b                        | b                        | b                        | a                        | b        | 5          | 2          | FF 255        | FF 255         | FF 255         | FF 255         | FF 111      | FF 127         | 00 08         | 08 0 0      | FF 255      | FF 255        | FF 255        | FF 255        |               |

| OSD adjust control characteristics1 (Max.)   | Oadj1    | 3.3    | 4.0  | 4.9  | V <sub>P-P</sub> | 26, 28, 30         | b      | a      | a         | a      | a                        | b                        | b                        | b                        | b                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 127         | 00 08         | 08 0 0      | FF 255      | FF 255        | FF 255        | FF 255        |               |

| OSD adjust control relative characteristics1 | ΔOadj1   | 0.8    | 1.0  | 1.2  | —                | —                  | —      | —      | —         | —      | —                        | —                        | —                        | —                        | —                        | —        | —          | —          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 127         | 00 08         | 08 0 0      | FF 255      | FF 255        | FF 255        | FF 255        |               |

| OSD adjust control characteristics2 (Typ.)   | Oadj2    | 1.2    | 1.8  | 2.4  | V <sub>P-P</sub> | 26, 28, 30         | b      | a      | a         | a      | a                        | b                        | b                        | b                        | b                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 64          | FF 64         | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| OSD adjust control relative characteristics2 | ΔOadj2   | 0.8    | 1.0  | 1.2  | —                | —                  | —      | —      | —         | —      | —                        | —                        | —                        | —                        | —                        | —        | —          | —          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 64          | FF 64         | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| OSD adjust control characteristics3 (Min.)   | Oadj3    | -0.5   | -0.1 | 0.3  | V <sub>P-P</sub> | 26, 28, 30         | b      | a      | a         | a      | a                        | b                        | b                        | b                        | b                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| OSD adjust control relative characteristics3 | ΔOadj3   | -0.2   | 0    | 0.2  | —                | —                  | —      | —      | —         | —      | —                        | —                        | —                        | —                        | —                        | —        | —          | —          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| OSD input threshold voltage                  | VthOSD   | 1.7    | 2.5  | 3.3  | V <sub>DC</sub>  | 26, 28, 30         | b      | a      | a         | a      | a                        | b                        | b                        | b                        | b                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| Black level difference in OSD BLK on/off     | OBLK     | -0.5   | -1.0 | 0.3  | V <sub>DC</sub>  | 26, 28, 30         | b      | a      | a         | a      | a                        | b                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| Relative OBLK                                | ΔOBLK    | -0.2   | 0    | 0.2  | —                | 26, 28, 30         | b      | a      | a         | a      | a                        | b                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| OSD BLK input threshold voltage              | VthBLK   | 1.7    | 2.5  | 3.3  | V <sub>DC</sub>  | 26, 28, 30         | b      | b      | b         | a      | b                        | b                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| Retrace BLK characteristics1                 | HBLK1    | 1.6    | 1.9  | 2.2  | V <sub>DC</sub>  | 26, 28, 30         | b      | a      | a         | a      | a                        | a                        | a                        | a                        | a                        | b        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 0F       | 0F 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| Retrace BLK characteristics2                 | HBLK2    | 1.0    | 1.3  | 1.6  | V <sub>DC</sub>  | 26, 28, 30         | b      | a      | a         | a      | a                        | a                        | a                        | a                        | a                        | b        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| Retrace BLK characteristics3                 | HBLK3    | 0.3    | 0.6  | 0.9  | V <sub>DC</sub>  | 26, 28, 30         | b      | a      | a         | a      | a                        | a                        | a                        | a                        | a                        | b        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| Retrace BLK input threshold voltage          | Vth-HBLK | 0.7    | 1.5  | 2.3  | V <sub>DC</sub>  | 26, 28, 30         | b      | a      | a         | a      | a                        | a                        | a                        | a                        | a                        | b        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| SOG input maximum noise voltage              | SS-NV    | —      | —    | 0.02 | V <sub>P-P</sub> | 9                  | b      | a      | a         | b      | a                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| SOG minimum input voltage                    | SS-SV    | 0.2    | —    | —    | V <sub>P-P</sub> | 9                  | b      | a      | a         | b      | a                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| Sync output high level                       | VSH      | 4.5    | 4.9  | 5.0  | V <sub>DC</sub>  | 9                  | b      | a      | a         | b      | a                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| Sync output low level                        | VSL      | 0      | 0.4  | 0.7  | V <sub>DC</sub>  | 9                  | b      | a      | a         | b      | a                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| Sync output delay time1                      | TDS-F    | 10     | 30   | 65   | ns               | 9                  | b      | a      | a         | b      | a                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| Sync output delay time2                      | TDS-R    | 10     | 30   | 65   | ns               | 9                  | b      | a      | a         | b      | a                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| V-DET input maximum noise voltage            | VD-NV    | —      | —    | 0.05 | V <sub>P-P</sub> | 10                 | b      | b      | b         | a      | b                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| V-DET minimum input voltage                  | VD-SV    | 0.2    | —    | —    | V <sub>P-P</sub> | 10                 | b      | b      | b         | a      | b                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| V-DET output high level                      | VVDH     | 3.8    | 4.2  | 5.0  | V <sub>DC</sub>  | 10                 | b      | b      | b         | a      | b                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| V-DET output low level                       | VVDL     | 0      | 0.7  | 1.1  | V <sub>DC</sub>  | 10                 | b      | b      | b         | a      | b                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| V-DET output delay time1                     | TDV-F    | 10     | 23   | 50   | ns               | 10                 | b      | b      | b         | a      | b                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| V-DET output delay time2                     | TDV-R    | 1      | 13   | 40   | ns               | 10                 | b      | b      | b         | a      | b                        | a                        | a                        | a                        | a                        | a        | b          | 5          | 2             | FF 255         | FF 255         | FF 255         | FF 255      | FF 0           | FF 0          | 00 08       | 08 0 0      | FF 255        | FF 255        | FF 255        | FF 255        |

| D/A output maximum voltage                   | VDH      | 4.7    | 5.2  | 5.7  | V <sub>DC</sub>  | 21, 22, 23, 24     | b      | a      | a         | a      | a                        | a                        | a                        | a                        | a                        | b        | 5          | 2          | FF 255        | FF 255         | FF 255         | FF 255         | FF 0        | FF 0           | 00 08         | 08 0 0      | FF 255      | FF 255        | FF 255        | FF 255        |               |

| D/A output minimum voltage                   | VDL      | 0      | 0    | 0.5  | V <sub>DC</sub>  | 21, 22, 23, 24     | b      | a      | a         | a      | a                        | a                        | a                        | a                        | a                        | b        | 5          | 2          | FF 255        | FF 255         | FF 255         | FF 255         | FF 0        | FF 0           | 00 08         | 08 0 0      | FF 255      | FF 255        | FF 255        | FF 255        |               |

| D/A OUT input current1                       | IA+1     | 0.18   | —    | —    | mA               | 21, 22, 23, 24     | b      | a      | a         | a      | a                        | a                        | a                        | a                        | a                        | b        | 5          | 2          | FF 255        | FF 255         | FF 255         | FF 255         | FF 0        | FF 0           | 00 08         | 08 0 0      | FF 255      | FF 255        | FF 255        | FF 255        |               |

| D/A OUT input current2                       | IA+2     | 0.18   | —    | —    | mA               | 21, 22, 23, 24     | b      | a      | a         | a      | a                        | a                        | a                        | a                        | a                        | b        | 5          | 2          | FF 255        | FF 255         | FF 255         | FF 255         | FF 0        | FF 0           | 00 08         | 08 0 0      | FF 255      | FF 255        | FF 255        | FF 255        |               |

| D/A OUT output current                       | IA-      | —      | —    | 0.4  | mA               | 21, 22, 23, 24     | b      | a      | a         | a      | a                        | a                        | a                        | a                        | a                        | b        | 5          | 2          | FF 255        | FF 255         | FF 255         | FF 255         | FF 0        | FF 0           | 00 08         | 08 0 0      | FF 255      | FF 255        | FF 255        | FF 255        |               |

| D/A nonlinearity                             | DNL      | -1.0   | —    | 1.0  | LSB              | 21, 22, 23, 24     | b      | a      | a         | a      | a                        | a                        | a                        | a                        | a                        | b        | 5          | 2          | FF 255        | FF 255         | FF 255         | FF 255         | FF 0        | FF 0           | 00 08         | 08 0 0      | FF 255      | FF 255        | FF 255        | FF 255        |               |

## Electrical Characteristics Test Method

### **I<sub>CC1</sub> 5 V Circuit Current1 Power Save Mode**

Measuring conditions are as listed in supplementary Table. Measured with a current meter at test point IB.

### **I<sub>CC2</sub> 12 V Circuit Current2 Normal Mode**

Measuring conditions are as listed in supplementary Table. Measured with a current meter at test point IA.

### **I<sub>CC3</sub> 5 V Circuit Current3 Normal Mode**

Measuring conditions are as listed in supplementary Table. Measured with a current meter at test point IB.

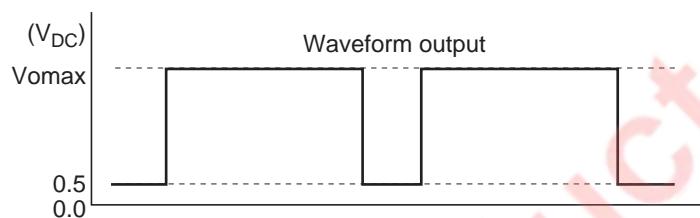

### **V<sub>OMAX</sub> Output Dynamic Range**

It makes the amplitude of SG1 1.4 <sub>P-P</sub>. Measure the DC voltage of the white level of the waveform output.

The measured value is called V<sub>OMAX</sub>.

### **V<sub>IMAX</sub> Maximum Input**

Increase the input signal (SG1) amplitude gradually, starting from 0.7 V<sub>P-P</sub>. Measure the amplitude of the input signal when the output signal starts becoming distorted.

### **GV Maximum Gain**

Input SG1, and measure the amplitude output at OUT (26, 28, 30). The amplitude is called V<sub>OUT</sub> (26, 28, 30).

Maximum gain GV is calculated by the equation below:

$$GV = 20 \log (V_{OUT} / 0.7) \text{ (dB)}$$

### **ΔGV Relative Maximum Gain**

Relative maximum gain ΔGV is calculated by the equation below:

$$\Delta GV = V_{OUT} (26) / V_{OUT} (28),$$

$$V_{OUT} (28) / V_{OUT} (30),$$

$$V_{OUT} (30) / V_{OUT} (26)$$

### **VC1 Main Contrast Control Characteristics1 (Max.)**

Input SG1, and measure the amplitude output at OUT (26, 28, 30). The amplitude is called V<sub>OUT</sub> (26, 28, 30).

The measured value is called VC1.

### **ΔVC1 Main Contrast Control Relative Characteristics1**

Relative characteristics ΔVC1 is calculated by the equation below:

$$\Delta VC1 = V_{OUT} (26) / V_{OUT} (28),$$

$$V_{OUT} (28) / V_{OUT} (30),$$

$$V_{OUT} (30) / V_{OUT} (26)$$

### **VC2 Main Contrast Control Characteristics2 (Typ.)**

Measuring condition and procedure are the same as described in VC1.

### **ΔVC2 Main Contrast Control Relative Characteristics2**

Measuring condition and procedure are the same as described in ΔVC1.

### **VC3 Main Contrast Control Characteristics3 (Min.)**

Measuring condition and procedure are the same as described in VC1.

### **ΔVC3 Main Contrast Control Relative Characteristics3**

Relative characteristics ΔVC3 is calculated by the equation below:

$$\Delta VC3 = VOUT(26) - VOUT(28),$$

$$VOUT(28) - VOUT(30),$$

$$VOUT(30) - VOUT(26)$$

### **VSC1 Sub Contrast Control Characteristics1 (Max.)**

Input SG1, and measure the amplitude output at OUT (26, 28, 30). The amplitude is called VOUT (26, 28, 30).

The measured value is called VSC1.

### **ΔVSC1 Sub Contrast Control Relative Characteristics1**

Relative characteristics ΔVSC1 is calculated by the equation below:

$$\Delta VSC1 = VOUT(26) / VOUT(28),$$

$$VOUT(28) / VOUT(30),$$

$$VOUT(30) / VOUT(26)$$

### **VSC2 Sub Contrast Control Characteristics2 (Typ.)**

Measuring condition and procedure are the same as described in VSC1.

### **ΔVSC2 Sub Contrast Control Relative Characteristics2**

Measuring condition and procedure are the same as described in ΔVSC1.

### **VSC3 Sub Contrast Control Characteristics3 (Min.)**

Measuring condition and procedure are the same as described in VSC1.

### **ΔVSC3 Sub Contrast Control Relative Characteristics3**

Relative characteristics ΔVSC3 is calculated by the equation below:

$$\Delta VSC3 = VOUT(26) - VOUT(28),$$

$$VOUT(28) - VOUT(30),$$

$$VOUT(30) - VOUT(26)$$

### **ABL1 ABL Control Characteristics1**

Measure the amplitude output at OUT (26, 28, 30). The amplitude is called VOUT (26, 28, 30).

The measured value is ABL1.

### **ΔABL1 ABL Control Relative Characteristics1**

Relative characteristics  $\Delta$ ABL1 is calculated by the equation below:

$$\Delta\text{ABL1} = \text{VOUT (26)} / \text{VOUT (28)},$$

$$\text{VOUT (28)} / \text{VOUT (30)},$$

$$\text{VOUT (30)} / \text{VOUT (26)}$$

### **ABL2 ABL Control Characteristics2**

Measuring condition and procedure are the same as described in ABL1.

### **ΔABL2 ABL Control Relative Characteristics2**

Measuring condition and procedure are the same as described in  $\Delta$ ABL1.

### **ABL3 ABL Control Characteristics3**

Measuring condition and procedure are the same as described in ABL1.

### **ΔABL3 ABL Control Relative Characteristics3**

Relative characteristics  $\Delta$ ABL3 is calculated by the equation below:

$$\Delta\text{ABL3} = \text{VOUT (26)} - \text{VOUT (28)},$$

$$\text{VOUT (28)} - \text{VOUT (30)},$$

$$\text{VOUT (30)} - \text{VOUT (26)}$$

### **VB1 Brightness Control Characteristics1**

Measure the DC voltage at OUT (26, 28, 30). The amplitude is called VOUT (26, 28, 30).

The measured value is called VB1.

### **ΔVB1 Brightness Control Relative Characteristics1**

Relative characteristics  $\Delta$ VB1 is calculated by the equation below:

$$\Delta\text{VB1} = \text{VOUT (26)} - \text{VOUT (28)},$$

$$\text{VOUT (28)} - \text{VOUT (30)},$$

$$\text{VOUT (30)} - \text{VOUT (26)}$$

### **VB2 Brightness Control Characteristics2**

Measuring condition and procedure are the same as described in VB1.

### **ΔVB2 Brightness Control Relative Characteristics2**

Measuring condition and procedure are the same as described in  $\Delta$ VB1.

### **VB3 Brightness Control Characteristics3**

Measuring condition and procedure are the same as described in VB1.

### **ΔVB3 Brightness Control Relative Characteristics3**

Measuring condition and procedure are the same as described in  $\Delta$ VB1.

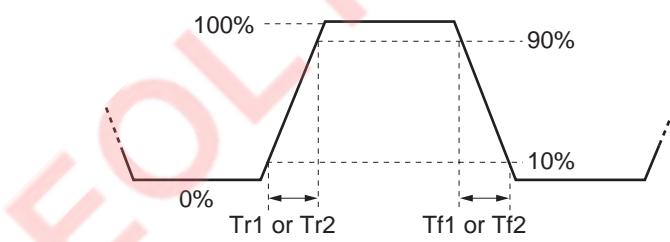

**Tr Pulse Characteristics1 (4 V<sub>P-P</sub>)**

Measure the time needed for the input pulse to rise from 10% to 90% (Tr1) and for the output pulse to rise from 10% to 90% (Tr2) with an active probe.

Pulse characteristics Tr is calculated by the equations below:

$$Tr = \sqrt{(Tr2)^2 - (Tr1)^2} \quad (\text{ns})$$

**ΔTr Relative Pulse Characteristics1 (4 V<sub>P-P</sub>)**

Relative characteristics ΔTr is calculated by the equation below:

$$\Delta Tr = Tr (26) - Tr (28),$$

$$Tr (28) - Tr (30),$$

$$Tr (30) - Tr (26)$$

**Tf Pulse Characteristics2 (4 V<sub>P-P</sub>)**

Measure the time needed for the input pulse to fall from 90% to 10% (Tf1) and for the output pulse to fall from 90% to 10% (Tf2) with an active probe.

Pulse characteristics Tf is calculated by the equations below:

$$Tf = \sqrt{(Tf2)^2 - (Tf1)^2} \quad (\text{ns})$$

**ΔTf Relative Pulse Characteristics2 (4 V<sub>P-P</sub>)**

Relative characteristics ΔTf is calculated by the equation below:

$$\Delta Tf = Tf (26) - Tf (28),$$

$$Tf (28) - Tf (30),$$

$$Tf (30) - Tf (26)$$

**VthCP Clamp Pulse Threshold Voltage**

Decrease the SG5 input level gradually from 5.0 V<sub>P-P</sub> monitoring the waveform output. Measure the top level of input pulse when the output pedestal voltage turn decrease with unstable. And increase the SG5 input level gradually from 0 V<sub>P-P</sub>. Measure the top level of input pulse when the output pedestal voltage turn increase with stable (a point of 2.0 V). The measured value is called VthCP.

**WCP Clamp Pulse Minimum Width**

Decrease the SG5 pulse width gradually from 0.5 μs, monitoring the output. Measure the SG5 pulse width when the output pedestal voltage turn decrease with unstable. And increase the SG5 pulse width gradual from 0 μs. Measure the SG5 pulse width when the output pedestal voltage turn increase with stable (a point of 2.0 V). The measured value is called WCP.

### OTr OSD Pulse Characteristics1

Measure the time needed for the output pulse to rise from 10% to 90% (OTr) with an active probe.

### OTf OSD Pulse Characteristics2

Measure the time needed for the output pulse to fall from 90% to 10% (OTf) with an active probe.

### Oadj1 OSD Adjust Control Characteristics1 (Max.)

Measure the amplitude output at OUT (26, 28, 30). The amplitude is called VOUT (26, 28, 30). The measured value is called Oadj1.

### ΔOadj1 OSD Adjust Control Relative Characteristics1

Relative characteristics ΔOadj1 is calculated by the equation below:

$$\Delta Oadj1 = VOUT(26) / VOUT(28),$$

$$VOUT(28) / VOUT(30),$$

$$VOUT(30) / VOUT(26)$$

### Oadj2 OSD Adjust Control Characteristics2 (Typ.)

Measuring condition and procedure are the same as described in Oadj1.

### ΔOadj2 OSD Adjust Control Relative Characteristics2

Measuring condition and procedure are the same as described in ΔOadj1.

### Oadj3 OSD Adjust Control Characteristics3 (Min.)

Measuring condition and procedure are the same as described in Oadj1.

### ΔOadj3 OSD Adjust Control Relative Characteristics3

Relative characteristics ΔOadj3 is calculated by the equation below:

$$\Delta Oadj3 = VOUT(26) - VOUT(28),$$

$$VOUT(28) - VOUT(30),$$

$$VOUT(30) - VOUT(26)$$

### VthOSD OSD Input Threshold Voltage

Decrease the SG6 input level gradually from 5.0 V<sub>P.P.</sub>, monitoring the output. Measure the top level of SG6 when the output is disappeared. And increase the SG6 input level gradually from 0 V<sub>P.P.</sub>. Measure the top level of SG6 when the output is appeared. The measured value is called VthOSD.

### OBLK Black Level Difference in OSD BLK on/off

Calculating the black level voltage minus the output voltage of high section of SG6 it makes VOUT (26, 28, 30). The calculated value is called OBLK.

### ΔOBLK Relative OBLK

Relative characteristics ΔOBLK is calculated by the equation below:

$$\Delta OBLK = VOUT(26) - VOUT(28),$$

$$VOUT(28) - VOUT(30),$$

$$VOUT(30) - VOUT(26)$$

### VthBLK OSD BLK Input Threshold Voltage

Confirm that output signal is being blanked by the SG6 at the time.

Decrease the SG6 input level gradually from 5.0 V<sub>P-P</sub>, monitoring the output. Measure the top level of SG6 when the blanking period is disappeared. And increase the SG6 input level gradually from 0 V<sub>P-P</sub>. Measure the top level of SG6 when the blanking period is appeared. The measured value is called VthBLK.

### HBLK1 Retrace BLK Characteristics1

Measure the bottom voltage at amplitude of OUT (26, 28, 30). The measured value is called HBLK1.

### HBLK2 Retrace BLK Characteristics2

Measuring condition and procedure are the same as described in HBLK1.

### HBLK3 Retrace BLK Characteristics3

Measuring condition and procedure are the same as described in HBLK1.

### VthHBLK Retrace BLK Input Threshold Voltage

Decrease the SG7 input level gradually from 5.0 V<sub>P-P</sub>, monitoring the output. Measure the top level of SG7 when the output is disappeared. And increase the SG7 input level gradually from 0 V<sub>P-P</sub>. Measure the top level of SG7 when the output is appeared. The measured value is called VthHBLK.

### SS-NV SOG Input Maximum Noise Voltage

When SG4 is all black (no video), the sync's amplitude of SG4 gradually from 0 V<sub>P-P</sub> to 0.02 V<sub>P-P</sub>. No pulse output permitted.

### SS-SV SOG Minimum Input Voltage

When SG4 is all white or all black, the sync's amplitude of SG4 gradually from 0.2 V<sub>P-P</sub> to 0.3 V<sub>P-P</sub>. Positive pulse has occurred to Sync Sepa OUT.

### VSH Sync Output High level

Measure the high voltage at Sync Sepa OUT. The measured value is treated as VSH.

### VSL Sync Output Low Level

Measure the low voltage at Sync Sepa OUT. The measured value is treated as VSL.

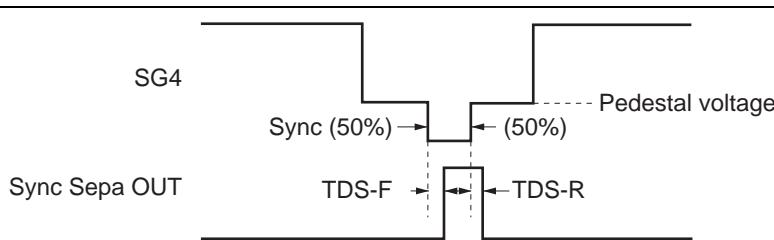

### TDS-F Sync Output Delay Time1

Sync Sepa OUT becomes high with sink part of SG4.

Measure the time needed for the front edge of SG4 Sync to fall from 50% and for SyncOUT to rise from 50% with an active probe. The measured value is called TDS-F.

### TDS-R Sync Output Delay Time2

Sync Sepa OUT becomes high with sink part of SG4.

Measure the time needed for the rear edge of SG4 Sync to rise from 50% and for SyncOUT to fall from 50% with an active probe. The measured value is called TDS-R.

### VD-NV V-DET Input Maximum Noise Voltage

Increase the SG1 input level gradually from 0 V<sub>P-P</sub> to 0.05 V<sub>P-P</sub>. No pulse Video Det OUT permitted.

### VD-SV V-DET Minimum Input Voltage

Decrease the SG1 input level gradually from 0.2 V<sub>P-P</sub> to 0.3 V<sub>P-P</sub>. Positive pulse has occurred to Video Det OUT.

### VVDH V-DET Output High Level

Measure the high voltage at Video Det OUT. The measured value is treated as VVDH.

### VVDL V-DET Output Low Level

Measure the low voltage at Video Det OUT. The measured value is treated as VVDL.

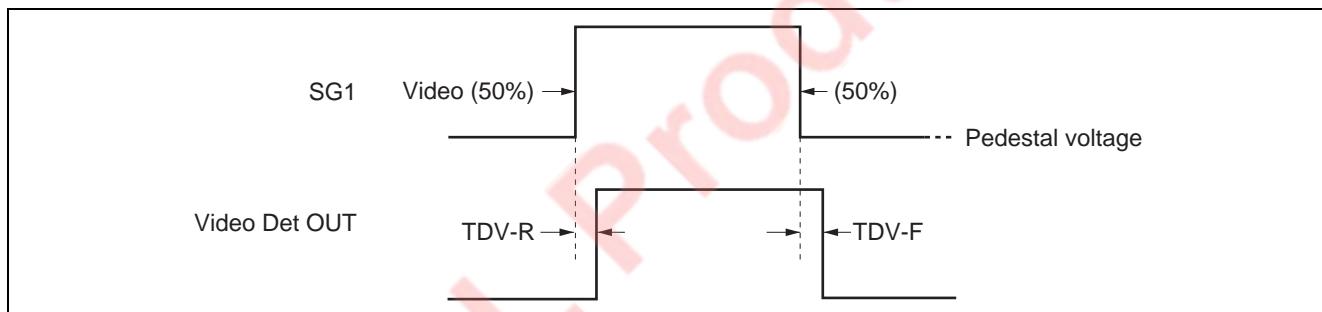

### TDV-F V-DET Output Delay Time1

Video Det OUT becomes high with signal part of SG1.

Measure the time needed for the SG1 to fall from 50% and for Video Det OUT to fall from 50% with an active probe. The measured value is called TDV-F.

### TDV-R V-DET Output Delay Time2

Video Det OUT becomes high with signal part of SG1.

Measure the time needed for the SG1 to rise from 50% and for Video Det OUT to rise from 50% with an active probe. The measured value is called TDV-R.

### VDL D/A Output Minimum Voltage

Measure the DC voltage at D/A OUT. The measured value is called VDL.

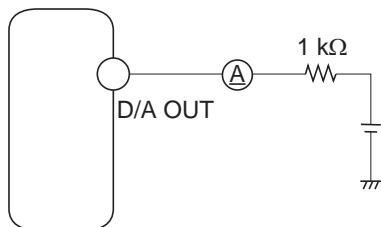

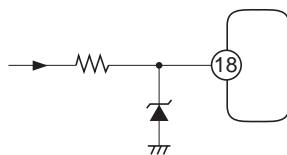

### IA+1 D/A OUT Input Current1

Measure the input current that flows into D/A OUT through 1 kΩ by 2 V<sub>DC</sub>.

### IA+2 D/A OUT Input Current2

Measure the input current that flows into D/A OUT through 1 kΩ by 0.5 V<sub>DC</sub>.

### IA- D/A OUT Output Current

Measure the output current that flows out of D/A OUT through 1 kΩ by 4.2 V<sub>DC</sub>.

### DNL D/A Nonlinearity

The difference of differential non-linearity of D/A OUT must be less than  $\pm 1.0$  LSB.

## Input Signal

| SG No.                                           | Signals                                                                                                                                                                                                                               |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

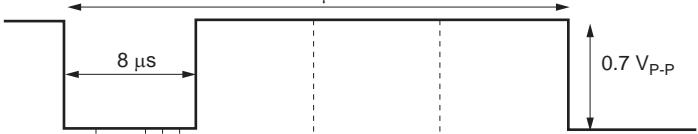

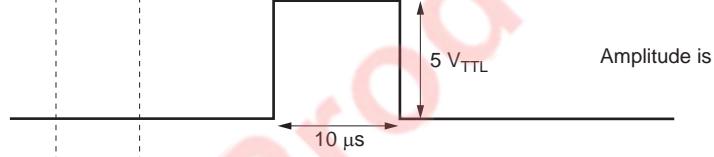

| SG1<br>Video signal<br>(all white)               | Pulse with amplitude of $0.7 \text{ V}_{\text{P-P}}$ ( $f = 30 \text{ kHz}$ ). Video width of $25 \mu\text{s}$ . (75%) (Amplitude is variable.)<br> |

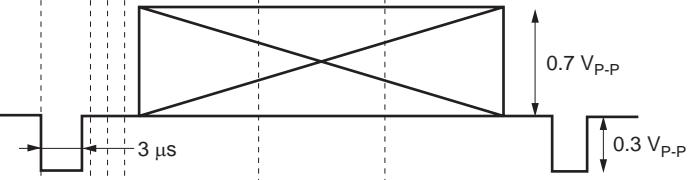

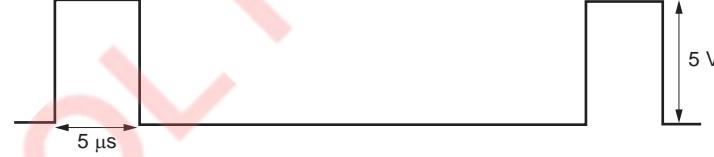

| SG4<br>Video signal<br>(all white,<br>all black) | Video width of $25 \mu\text{s}$ . (75%)<br>                                                                                                         |

| SG5<br>Clamp pulse                               | Pulse width and amplitude are variable.<br>                                                                                                         |

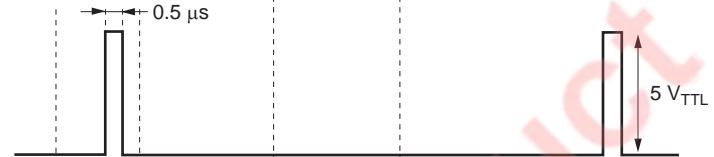

| SG6<br>OSD pulse                                 |                                                                                                                                                    |

| SG7<br>BLK pulse                                 |                                                                                                                                                   |

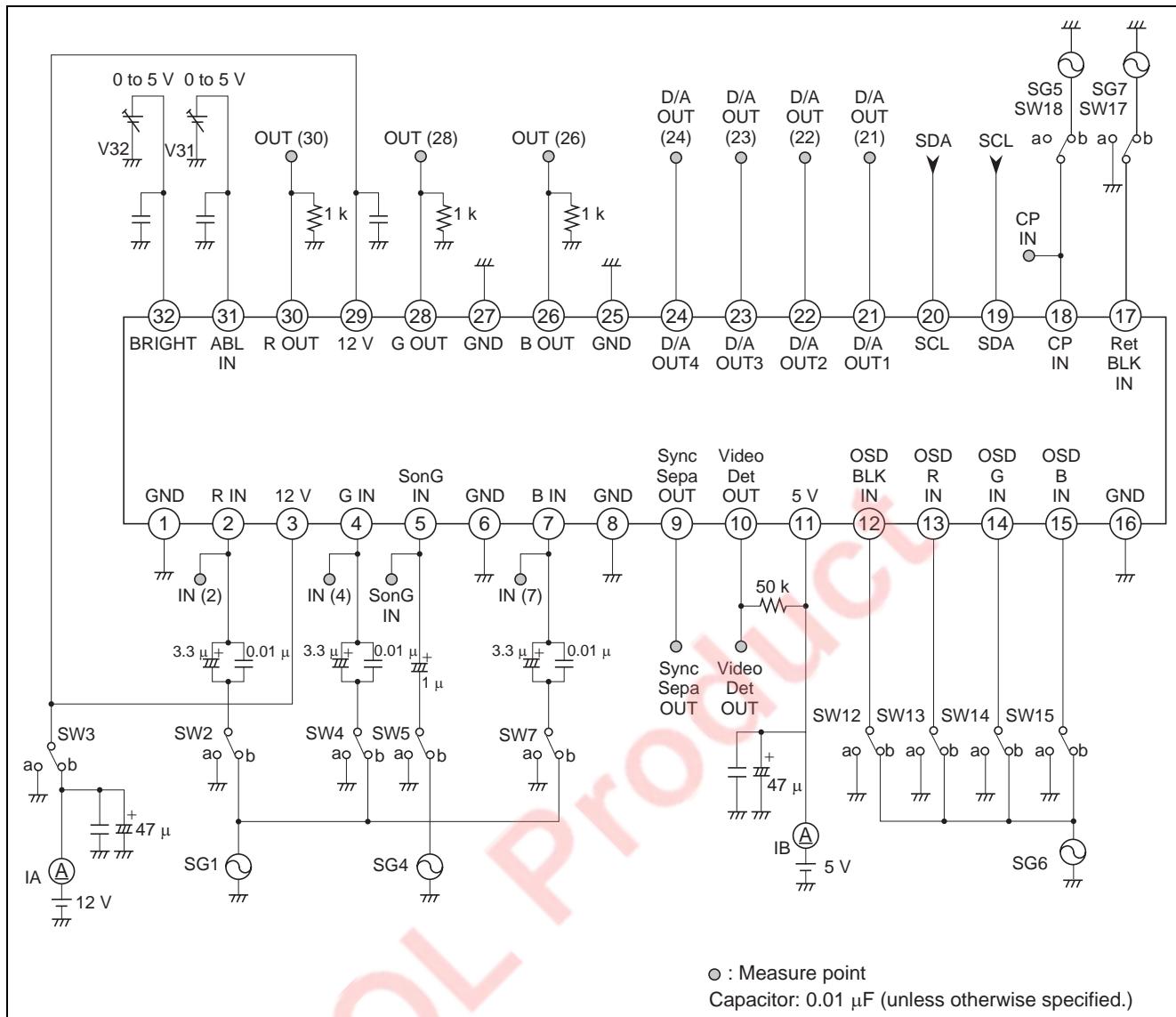

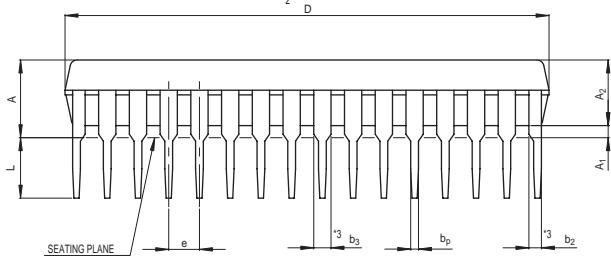

## Test Circuit

## Pin Description

| Pin No. | Name                    | DC Voltage (V) | Peripheral Circuit | Function                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-------------------------|----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | R IN                    | 3.5            |                    | Clamp to about 3.5 V due to clamp pulse from pin 18. Input at low impedance.                                                                                                                                                                                                                                                                                               |

| 4       | G IN                    |                | —                  |                                                                                                                                                                                                                                                                                                                                                                            |

| 7       | B IN                    |                | —                  |                                                                                                                                                                                                                                                                                                                                                                            |

| 3       | V <sub>CC1</sub> (12 V) | 12             | —                  | Connect to the power supply that stabilized.                                                                                                                                                                                                                                                                                                                               |

| 5       | SonG IN                 | When open 2.3  |                    | SYNC ON VIDEO input pin. Sync is negative. Input signal at pin 5, compare with the reference voltage of internal circuit in order to separate Sync signal from Sync on Green signal. Input at low impedance. Do not input the signal without the Sync. When it does not use this function, connect to capacitor between GND, turn on Sync Sepa SW by I <sup>2</sup> C BUS. |

| 1       | GND                     | GND            | —                  | Connect to GND.                                                                                                                                                                                                                                                                                                                                                            |

| 6       | GND 1                   |                | —                  |                                                                                                                                                                                                                                                                                                                                                                            |

| 8       | GND 2                   |                | —                  |                                                                                                                                                                                                                                                                                                                                                                            |

| 16      | GND 3                   |                | —                  |                                                                                                                                                                                                                                                                                                                                                                            |

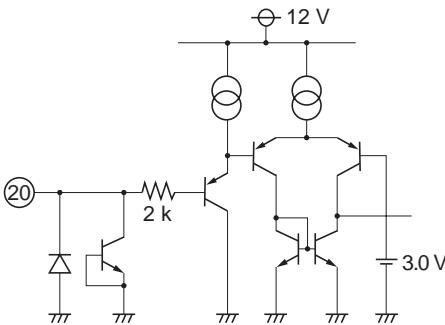

| 27      | GND 4                   |                | —                  |                                                                                                                                                                                                                                                                                                                                                                            |