#### 4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

#### **DESCRIPTION**

The M5M5408B is a family of 4-Mbit static RAMs organized as 524,288-words by 8-bit, fabricated by Mitsubishi's high-performance 0.25 $\mu$ m CMOS technology.

The M5M5408B is suitable for memory applications where a simple interfacing, battery operating and battery backup are the important design objectives.

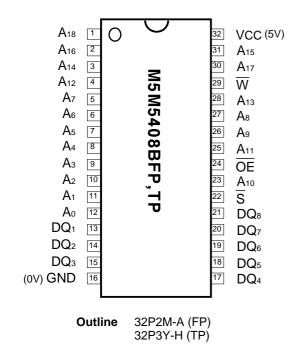

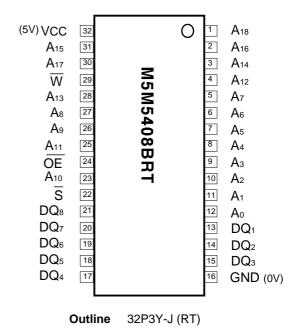

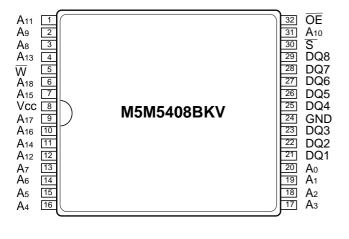

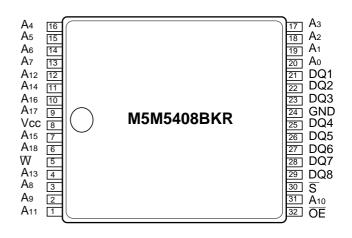

M5M5408B is packaged in 32-pin plastic SOP, 32-pin plastic TSOP and 32-pin 8mm x 13.4mm STSOP packages. Two types of TSOPs and two types of STSOPs are available, M5M5408BTP (normal-lead-bend TSOP), M5M5408BRT (reverse-lead-bend TSOP), M5M5408BKV (normal-lead-bend STSOP) and M5M5408BKR (reverse-lead-bend STSOP). These two types TSOPs and two types STSOPs are suitable for a surface mounting on double-sided printed circuit boards.

From the point of operating temperature, the family is divided into three versions; "Standard", "W-version", and "I-version". Those are summarized in the part name table below.

### **FEATURES**

- Single +5V power supply

- Small stand-by current: 0.4µA(3V,typ.)

- No clocks, No refresh

- Data retention supply voltage=2.0V to 5.5V

- All inputs and outputs are TTL compatible.

- Easy memory expansion by \overline{S}

- Common Data I/O

- Three-state outputs: OR-tie capability

- OE prevents data contention in the I/O bus

- Process technology: 0.25µm CMOS

- Package:

M5M5408BFP: 32 pin 525 mil SOP

M5M5408BTP/RT: 32 pin 400 mil TSOP(II)

M5M5408BKV/KR: 32 pin 8mm x 13.4mm STSOP

#### PART NAME TABLE

| Version,                 | Part name                  | Power  | Access |           | urrent lcc(PD) | , Vcc=3.0V    | Active          |

|--------------------------|----------------------------|--------|--------|-----------|----------------|---------------|-----------------|

| Operating                | (## stands for "FP", "TP", | Supply | time   | typical * | Ratings        | (max.)        | current<br>lcc1 |

| temperature              | "RT","KV"or"KR")           | Сарріу | max.   | 25°C      | 70°C           | 85°C          | (5.0V, typ.)    |

|                          | M5M5408B## -55L            |        | 55ns   |           |                |               |                 |

|                          | M5M5408B## -70L            | 5.0V   | 70ns   |           | 50µA           |               |                 |

| Standard                 | M5M5408B## -10L            |        | 100ns  |           |                |               |                 |

| 0 ~ +70°C                | M5M5408B## -55H            |        | 55ns   |           |                |               |                 |

|                          | M5M5408B## -70H            | 5.0V   | 70ns   | 0.4µA     | 10µA           |               |                 |

|                          | M5M5408B## -10H            |        | 100ns  |           |                |               |                 |

|                          | M5M5408B## -55LW           | 5.0V   | 55ns   |           |                | 100μA<br>20μA | 50mA<br>(10MHz) |

|                          | M5M5408B## -70LW           |        | 70ns   |           |                |               |                 |

| W-version                | M5M5408B## -10LW           |        | 100ns  |           |                |               |                 |

| -20 ~ +85°C              | M5M5408B## -55HW           |        | 55ns   |           |                |               | 25mA<br>(1MHz)  |

|                          | M5M5408B## -70HW           | 5.0V   | 70ns   | 0.4µA     |                |               |                 |

|                          | M5M5408B## -10HW           |        | 100ns  |           |                |               |                 |

|                          | M5M5408B## -55LI           |        | 55ns   |           |                |               |                 |

|                          | M5M5408B## -70LI           | 5.0V   | 70ns   |           |                | 100µA         |                 |

| I-version<br>-40 ~ +85°C | M5M5408B## -10LI           |        | 100ns  |           |                | ,             |                 |

|                          | M5M5408B## -55HI           |        | 55ns   |           |                |               |                 |

|                          | M5M5408B## -70HI           | 5.0V   | 70ns   | 0.4µA     |                | 20μΑ          |                 |

|                          | M5M5408B## -10HI           |        | 100ns  |           |                |               |                 |

<sup>\* &</sup>quot;typical" parameter is sampled, not 100% tested.

### 4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

### PIN CONFIGURATION (TOP VIEW)

Outline 32P3K-B

#### 4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

#### **FUNCTION**

The M5M5408BFP,TP,RT,KV,KR is organized as 524,288-words by 8-bit. These devices operate on a single +5.0V power supply, and are directly TTL compatible to both input and output. Its fully static circuit needs no clocks and no refresh, and makes it useful.

A write operation is executed during the  $\overline{S}$  low and  $\overline{W}$  low overlap time. The address(A0~A18) must be set up before the write cycle

A read operation is executed by setting  $\overline{W}$  at a high level and  $\overline{OE}$  at a low level while S are in an active state( $\overline{S}$ =L).

When setting  $\overline{S}$  at a high level, the chips are in a non-selectable mode in which both reading and writing are disabled. In this mode, the output stage is in a high-impedance state, allowing OR-tie with other chips. Setting the  $\overline{OE}$  at a high level,the output stage is in a high-impedance state, and the data bus contention problem in the write cycle is eliminated.

The power supply current is reduced as low as  $0.4\mu A(25^{\circ}C$ , typical), and the memory data can be held at +2V power supply, enabling battery back-up operation during power failure or power-down operation in the non-selected mode.

#### **FUNCTION TABLE**

| s | $\overline{W}$ | ŌE | Mode          | DQ              | lcc     |

|---|----------------|----|---------------|-----------------|---------|

| Н | Х              | Х  | Non selection | High-impedance  | Standby |

| L | L              | Х  | Write         | Data input (D)  | Active  |

| L | Н              | L  | Read          | Data output (Q) | Active  |

| L | Н              | Н  | Read          | High-impedance  | Active  |

| Pin            | Function            |

|----------------|---------------------|

| A0 ~ A18       | Address input       |

| DQ1 ~ DQ8      | Data input / output |

| S              | Chip select input   |

| $\overline{W}$ | Write control input |

| ŌĒ             | Output inable input |

| Vcc            | Power supply        |

| GND            | Ground supply       |

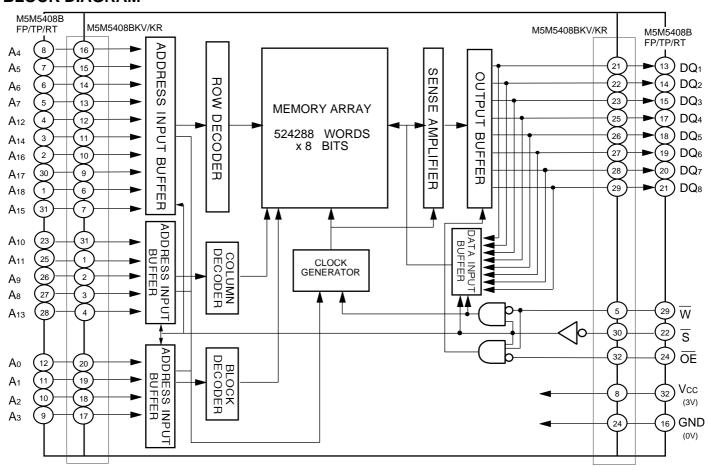

#### **BLOCK DIAGRAM**

### 4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter             | Conditions           | Ratings           | Units |

|--------|-----------------------|----------------------|-------------------|-------|

| Vcc    | Supply voltage        | With respect to GND  | -0.3* ~ +7        |       |

| Vı     | Input voltage         | With respect to GND  | -0.3* ~ Vcc + 0.3 | V     |

| Vo     | Output voltage        | With respect to GND  | 0 ~ Vcc           |       |

| Pd     | Power dissipation     | Ta=25°C              | 700               | mW    |

|        | Onevetica             | Standard (-L, -H)    | 0 ~ +70           |       |

| Ta     | Operating temperature | W-version (-LW, -HW) | -20 ~ +85         | °C    |

|        | temperature           | I-version (-LI, -HI) | -40 ~ +85         |       |

| Tstg   | Storage temperature   |                      | -65 ~150          | °C    |

<sup>\* -3.0</sup>V in case of AC (Pulse width ≤ 30ns)

### DC ELECTRICAL CHARACTERISTICS

( Vcc=5V±10%, unless otherwise noted)

| Cumbal           | Danamatan                                | 0 111                           | Conditions    |          | Limits |          | 1.1-24- |

|------------------|------------------------------------------|---------------------------------|---------------|----------|--------|----------|---------|

| Symbol           | Parameter                                | Conditions                      | Min           | Тур      | Max    | Units    |         |

| VIH              | High-level input voltage                 |                                 |               | 2.2      |        | Vcc+0.3V |         |

| VIL              | Low-level input voltage                  |                                 |               | -0.3 *   |        | 0.8      |         |

| V <sub>OH1</sub> | High-level output voltage 1              | Iон= -1mA                       |               | 2.4      |        |          | V       |

| V <sub>OH2</sub> | High-level output voltage 2              | Iон= -0.1mA                     |               | Vcc-0.5V |        |          |         |

| Vol              | Low-level output voltage                 | IoL=2mA                         |               |          |        | 0.4      |         |

| lı               | Input leakage current                    | Vı=0 ~ Vcc                      | Vi=0 ~ Vcc    |          |        | ±1       | μA      |

| lo               | Output leakage current                   | S=VIH or OE=VIH, VI/0=0 ~ Vcc   |               |          |        | ±1       | μΛ      |

| lcc1             | Active supply current                    | S≤0.2V Output-open              | minimum cycle | -        | 50     | 80       |         |

| 1001             | ( AC,MOS level )                         | Other inputs ≤0.2V or ≥Vcc-0.2V | f= 1MHz       | -        | 25     | 30       | m Λ     |

|                  | Active supply current                    | S=VIL Output-open               | minimum cycle | -        | 60     | 90       | mA      |

| lcc2             | ( AC,TTL level )                         | Other inputs=VIH or VIL         | f= 1MHz       | -        | 30     | 40       |         |

|                  |                                          |                                 | -LW, -LI      | -        | -      | 200      |         |

| lcc3             | Stand by supply current                  | S≥Vcc-0.2V                      | -L            | -        | -      | 100      |         |

|                  | ( AC,MOS level )                         | Other inputs=0~Vcc              | -HW, -HI      | -        | 0.4    | 40       | μΑ      |

|                  |                                          |                                 | -H            | -        | 0.4    | 20       |         |

| Icc4             | Stand by supply current ( AC,TTL level ) | S=V ,Other inputs= 0 ~ Vcc      |               | -        | -      | 3        | mA      |

Note 1: Direction for current flowing into IC is indicated as positive (no mark)

### **CAPACITANCE**

(Vcc=5.0V±10%, unless otherwise noted)

| Symbol Parameter | Parameter          | Conditions                 | Limits |     |       | l laita |

|------------------|--------------------|----------------------------|--------|-----|-------|---------|

|                  | Conditions         | Min                        | Тур    | Max | Units |         |

| Сі               | Input capacitance  | Vi=GND, Vi=25mVrms, f=1MHz |        |     | 8     |         |

| Со               | Output capacitance | Vo=GND,Vo=25mVrms, f=1MHz  |        |     | 10    | pF      |

Note 2: Typical value is for Vcc=5.0V and Ta=25°C

<sup>\* -3.0</sup>V in case of AC (Pulse width ≤ 50ns)

## 4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

## AC ELECTRICAL CHARACTERISTICS (Vcc=5.0V±10%, unless otherwise noted)

## (1) TEST CONDITIONS

| Supply voltage                | 5.0V                                                                               |

|-------------------------------|------------------------------------------------------------------------------------|

| Input pulse                   | VIH=2.4V,VIL=0.6V (FP,TP,RT,KV,KR-70,-10 )<br>VIH=3.0V,VIL=0V (FP,TP,RT,KV,KR-55 ) |

| Input rise time and fall time | 5ns                                                                                |

| Reference level               | VOH=VOL=1.5V                                                                       |

|                               | Transition is measured ±500mV from                                                 |

|                               | steady state voltage.(for ten,tdis)                                                |

| Output loads                  | Fig.1, CL=100pF (FP,TP,RT,KV,KR-70,-10)                                            |

|                               | CL=30pF (fp,tp,rt,kv,kr-55)                                                        |

|                               | CL=5pF (for ten,tdis)                                                              |

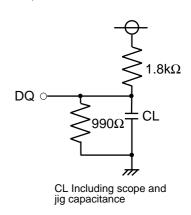

Fig.1 Output load

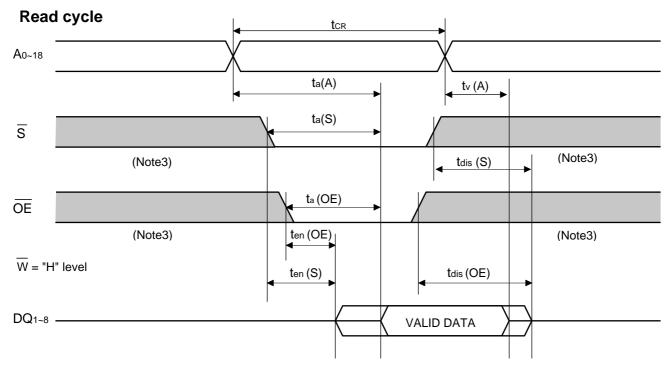

### (2) READ CYCLE

|                      |                                                 | Limits   |                        |         |                        |          |                       |       |

|----------------------|-------------------------------------------------|----------|------------------------|---------|------------------------|----------|-----------------------|-------|

| Symbol               | Parameter                                       | M5M5408E | BFP,TP,RT,<br>KV.KR-55 | M5M5408 | BFP,TP,RT,<br>KV,KR-70 | M5M5408B | FP,TP,RT,<br>KV,KR-10 | Units |

|                      |                                                 | Min      | Max                    | Min     | Max                    | Min      | Max                   |       |

| <b>t</b> cr          | Read cycle time                                 | 55       |                        | 70      |                        | 100      |                       | ns    |

| ta(A)                | Address access time                             |          | 55                     |         | 70                     |          | 100                   | ns    |

| ta(S)                | Chip select access time                         |          | 55                     |         | 70                     |          | 100                   | ns    |

| ta(OE)               | Output enable access time                       |          | 25                     |         | 35                     |          | 50                    | ns    |

| t <sub>dis</sub> (S) | Output disable time after \$\overline{S}\$ high |          | 20                     |         | 25                     |          | 35                    | ns    |

| tdis(OE)             | Output disable time after OE high               |          | 20                     |         | 25                     |          | 35                    | ns    |

| ten(S)               | Output enable time after $\overline{S}$ low     | 10       |                        | 10      |                        | 10       |                       | ns    |

| ten(OE)              | Output enable time after OE low                 | 5        |                        | 5       |                        | 5        |                       | ns    |

| t∨(A)                | Data valid time after address                   | 10       |                        | 10      |                        | 10       |                       | ns    |

## (3) WRITE CYCLE

|                      |                                                         | Limits   |                        |         |                        |     |                        |       |

|----------------------|---------------------------------------------------------|----------|------------------------|---------|------------------------|-----|------------------------|-------|

| Symbol               | Parameter                                               | M5M5408E | BFP,TP,RT,<br>KV,KR-55 | M5M5408 | BFP,TP,RT,<br>KV,KR-70 |     | BFP,TP,RT,<br>KV.KR-10 | Units |

|                      |                                                         | Min      | Max                    | Min     | Max                    | Min | Max                    |       |

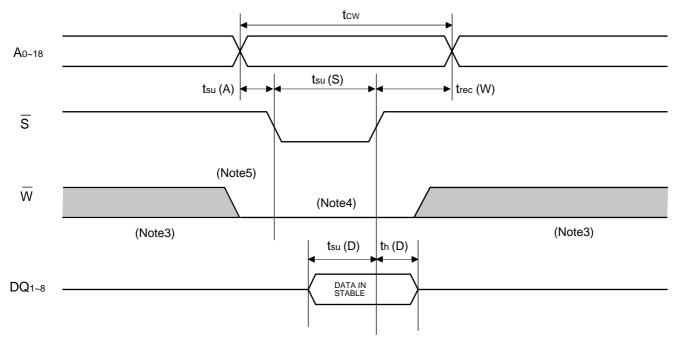

| tcw                  | Write cycle time                                        | 55       |                        | 70      |                        | 100 |                        | ns    |

| t <sub>w</sub> (W)   | Write pulse width                                       | 40       |                        | 50      |                        | 60  |                        | ns    |

| tsu(A)               | Address set up time                                     | 0        |                        | 0       |                        | 0   |                        | ns    |

| tsu(A-WH)            | Address set up time with respect to W high              | 50       |                        | 60      |                        | 80  |                        | ns    |

| tsu(S)               | Chip select set up time                                 | 50       |                        | 60      |                        | 80  |                        | ns    |

| tsu(D)               | Data set up time                                        | 25       |                        | 30      |                        | 35  |                        | ns    |

| th(D)                | Data hold time                                          | 0        |                        | 0       |                        | 0   |                        | ns    |

| trec(W)              | Write recovery time                                     | 0        |                        | 0       |                        | 0   |                        | ns    |

| t <sub>dis</sub> (W) | Output disable time after $\overline{\overline{W}}$ low |          | 20                     |         | 25                     |     | 35                     | ns    |

| tdis(OE)             | Output disable time after OE high                       |          | 20                     |         | 25                     |     | 35                     | ns    |

| t <sub>en</sub> (W)  | Output enable time after W high                         | 5        |                        | 5       |                        | 5   |                        | ns    |

| ten(OE)              | Output enable time after OE low                         | 5        |                        | 5       |                        | 5   |                        | ns    |

### 4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

## (4)TIMING DIAGRAMS

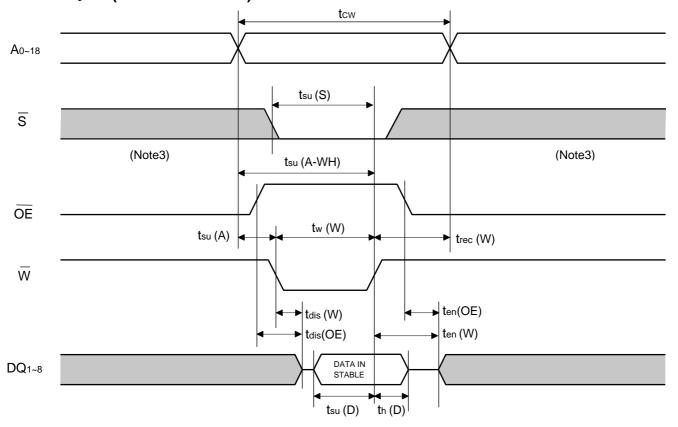

## Write cycle ( W control mode )

### 4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

## Write cycle (S control mode)

- Note 3: Hatching indicates the state is "don't care".

- Note 4: A Write occurs during the overlap of a low  $\overline{S}$  and a low  $\overline{W}$ .

- Note 5: If  $\overline{W}$  goes low simultaneously with or prior to  $\overline{S}$ , the output remains in the high impedance state.

- Note 6: Don't apply inverted phase signal externally when DQ pin is in output mode.

### 4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

#### POWER DOWN CHARACTERISTICS

## (1) ELECTRICAL CHARACTERISTICS

| Symbol Dorometer |                                  | T ( 196               |          | Units   |      |     |       |

|------------------|----------------------------------|-----------------------|----------|---------|------|-----|-------|

| Symbol           | Symbol Parameter Test conditions |                       |          | Min     | Тур. | Max | Units |

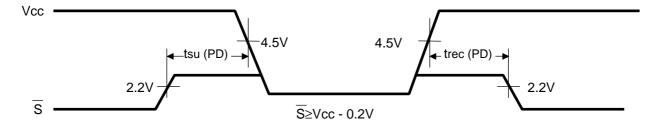

| Vcc (PD)         | Power down supply voltage        |                       |          | 2       | -    | •   | V     |

| VI (S)           | Chip select input $\bar{S}$      | Vcc(PD) ≥ 2.2V        |          | 2.2     | -    | -   | V     |

|                  |                                  | 2.2V ≥ Vcc(PD) ≥ 2.0V | -        | Vcc(PD) | -    | V   |       |

|                  |                                  |                       | -LW, -LI | -       | -    | 100 | μA    |

| ICC (PD)         | Power down                       | Vcc=3.0V, S≥Vcc-0.2V, | -L       | -       | -    | 50  | μA    |

|                  | supply current                   | Other inputs=0 ~ Vcc  | -HW, -HI | -       | 0.4  | 20  | μA    |

|                  |                                  | -Н                    |          | _       | 0.4  | 10  | μA    |

Typical value is for Ta=25°C

## (2) TIMING REQUIREMINTS

| Symbol Parameter | - ·                      | T . 197         |     | l lista |     |       |

|------------------|--------------------------|-----------------|-----|---------|-----|-------|

|                  | Parameter                | Test conditions | Min | Тур     | Max | Units |

| tsu (PD)         | Power down set up time   |                 | 0   |         |     | ns    |

| trec (PD)        | Power down recovery time |                 | 5   |         |     | ms    |

## (3) TIMING DIAGRAM

### S control mode

## 4194304-BIT (524288-WORD BY 8-BIT) CMOS STATIC RAM

**Revision History**

Revision No. History Date

K0.1e The first edition '98.7.30 Preliminary