| Table of Contents      | Page |

|------------------------|------|

| Abstract               |      |

| Introduction           | 3    |

| HITFET® Construction   |      |

| Protection-Functions   | 5    |

| Drive Requirements     |      |

| Current-Sense          |      |

| Status Feedback Signal | 10   |

| Reverse Polarity       | 11   |

| Typical Applications   | 11   |

| Summary                | 13   |

| References             |      |

1

#### **Abstract**

Today's wide palette of intelligent power semiconductors provides system engineers with many opportunities to develop more reliable systems at lower overall cost in a smaller package. Many of these intelligent power semiconductors require very few external components, if any, since they have a built-in protection against overtemperature or short circuit, and can be driven directly by a microcontroller. Siemens offers a wide variety of smart power switches for high-side and low-side applications. The name PROFET® (fully PROtected FET) designates high-side switch families that require a minimum number of external

components while providing high-side switching function with numerous protection functions needed in automotive industrial and applications<sup>(1)</sup>. The name TEMPFET® (TEMperature Protected FET) designates a family of short circuit and overtemperature protected low side switches<sup>(2,3)</sup>. Finally, there is also a family of new low-side switches called HITFET® (High InTegration FET) which includes a very high level of integration of control and protection functions in a single package<sup>(4)</sup>. This paper describes HITFET® devices in detail. In the following tables all available types are listed:

Table 1 3-Pin HITFET® with Fixed Current Limit

| Туре    | $V_{DS(AZ)}$ [V] | $R_{	extsf{DS(ON)}}$ [m $\Omega$ ] | I <sub>D-ISO min</sub> [A] | I <sub>D(lim) min</sub> [A] | Status at<br>Input Pin | Package |

|---------|------------------|------------------------------------|----------------------------|-----------------------------|------------------------|---------|

| BTS 117 | 60               | 100                                | 3.5                        | 10.5                        | single                 | TO 220  |

| BTS 133 | 60               | 50                                 | 7                          | 21                          | single                 | TO 220  |

| BTS 141 | 60               | 28                                 | 12                         | 25                          | single                 | TO 220  |

| BTS 149 | 60               | 18                                 | 19                         | 30                          | single                 | TO 220  |

Table 2 5-Pin HITFET® with Adjustable Current Limitation and Current Sense

| Туре    | $V_{DS(AZ)}$ [V] | $R_{ m DS(ON)}$ [m $\Omega$ ] | I <sub>D-ISO min</sub> | I <sub>D(lim) min</sub> | Status at<br>Current<br>Sence Pin | Package  |

|---------|------------------|-------------------------------|------------------------|-------------------------|-----------------------------------|----------|

| BTS 917 | 60               | 100                           | 3.5                    | 2.5 45                  | analog                            | TO 220/5 |

| BTS 933 | 60               | 50                            | 7                      | 7 80                    | analog                            | TO 220/5 |

| BTS 941 | 60               | 28                            | 12                     | 12 130                  | analog                            | TO 220/5 |

| BTS 949 | 60               | 18                            | 19                     | 19 220                  | analog                            | TO 220/5 |

## Introduction

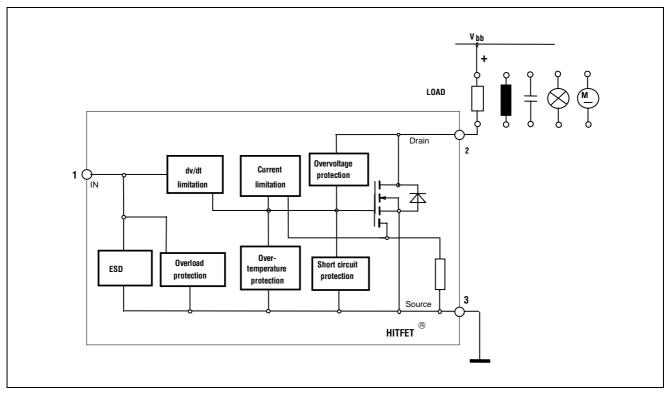

Figure 1

HITFET® Block Diagram, Fixed Current Limit

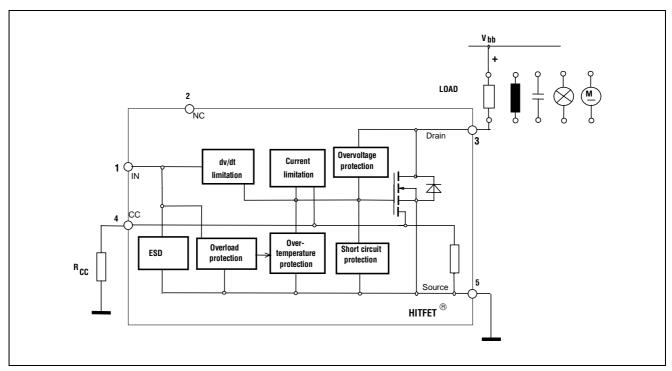

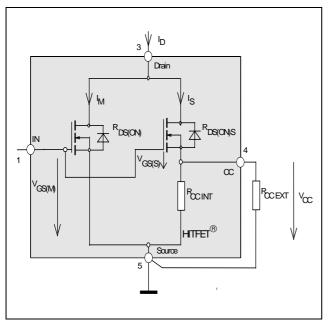

Figure 2 HITFET<sup>®</sup> Block Diagram, Adjustable Current Limit

The HITFET® device designs are based on the standard SIPMOS<sup>®</sup> (Siemens Power MOS) technology with additional elements that provide new and unique characteristics. Figure 1 and Figure 2 show that each HITFET® type has a built-in protection against overvoltage, overtemperature, short circuit, ESD, and switching speed limiting (dv/dt limiting) circuit. The most important are the short circuit and overtemperature protection. They are achieved by the use of two separate temperature sensors. The combination of the sensors guarantees that the power chip temperature is limited to a relatively low transient temperature during severe overload conditions and to a very safe maximum operating temperature on a continuous base just slightly above the maximum specified operating temperature of 150 °C. Almost equally important are the protection against overvoltage transients that allows for trouble-free operation with inductive loads, and a current limiting circuit that

provides safe operating current values at all times. The voltage slew rate limiting circuit that is connected in series between the input and the power transistor gate connection virtually eliminates EMI noise by keeping the switching speed within a desirable range. **Figure 2** also shows a current sense terminal for devices packaged in a 5-pin TO-220 package. The current limit value can be programmed by connecting an appropriate resistor value between the pins 4 and 5.

The uniqueness of the HITFET® design is that most if not all of the external components that a SIPMOS® or TEMPFET® transistor may need for protection or for on-resistance optimization are eliminated. The HITFET® dynamic behavior is nearly the same as that of a TEMPFET® with the same basic ratings except that the switching speed of the HITFET® is limited internally.

### HITFET® Construction

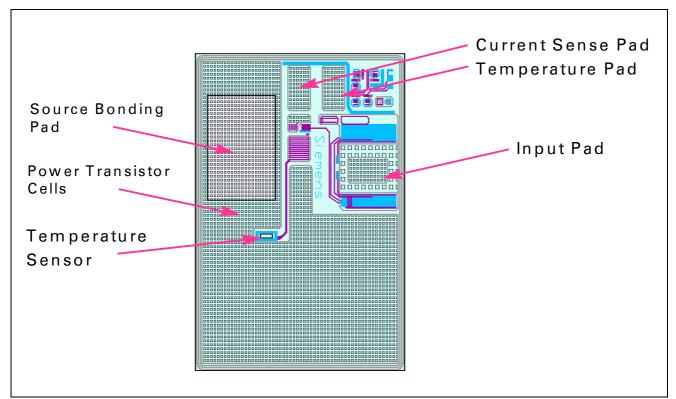

Figure 3 HITFET® Power Chip Layout

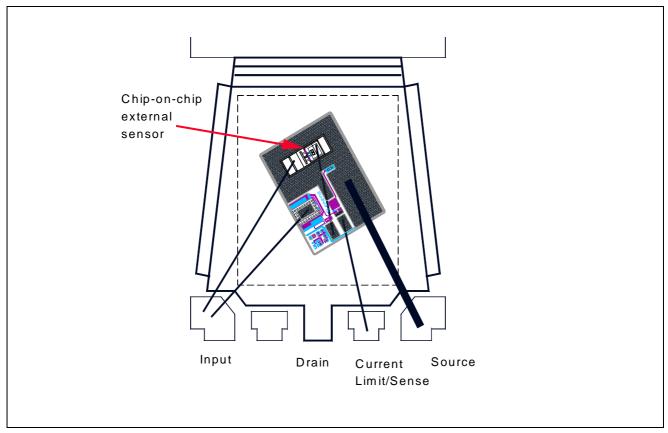

Figure 4 HITFET® Internal Assembly

Figure 3 and Figure 4 show the HITFET® internal construction that includes a SIPMOS® power chip with integrated control and protection circuits, and a separate chip-on-chip thermal sensor. The three pin version has a fixed current limit, while the 5-pin version has an adjustable (programmable) current limit capability. The chipon-chip construction of a HITFET® is identical to the construction of a TEMPFET<sup>®</sup>. The same type of temperature sensor chip is glued on the top surface of the power chip. The HITFET® power chip is a new design based on the milli-Smart technology. It combines a very low  $R_{on}$  vertical SIPMOS® (specific resistance power  $0.25 \Omega/\text{mm}^2$ ) with integrated control and protection circuits, fabricated using self-isolated lateral CMOS devices. The integrated drive stage and all protection functions require about 1 mm<sup>2</sup> of the chip area regardless of the overall device size. This allows production of a family of devices with a maximum resistance as low as 18 m $\Omega$  in a TO-220 package. All HITFET<sup>®</sup> devices have a minimum breakdown voltage above 60 V over the entire temperature operating range of  $-40\,^{\circ}\text{C}$  to  $+150\,^{\circ}\text{C}$  and are fully compatible with logic level and standard level input drive voltages. The result is that one can replace several TEMPFET® types with a single HITFET® type.

### **Protection-Functions**

As already mentioned, a HITFET® is fully against short protected ESD. circuit. overtemperature, overvoltage, and overcurrent. The ESD protection is designed for 3 kV human body model capability for any pin combination. It is provided by a 11 V (typical voltage) zener diode connected between the input and source pins, and several zener diodes and one blocking diode connected in series between the drain and gate terminals of the power chip. combination of the above elements provides the ESD protection for any pin combination for either polarity. Furthermore, the same string of zener diodes provides protection against inductive turnoff overvoltage transients once the drain to source voltage exceeds 60 V. As soon as the

voltage between the drain and source reaches the series diode combination breakdown voltage, the diodes become conductive and provide charge to the gate terminal. This forces the transistor to conduct in the constant current mode until the stored energy in the unclamped inductive load is dissipated. Even though this is thermally quite stressful, it is still the best protection choice, because the operation of any FET in the active clamping mode (constant current source) is more rugged compared to the operation in the avalanche mode. The maximum acceptable clamping energy ( $E_{\rm AS}$ ) that a HITFET® can withstand depends primarily upon

thermal properties of each device type and is defined in the data sheet.

However, the most significant protection provided is that against the short circuit and overtemperature. It is achieved by the use of two separate temperature sensors. The two sensor approach is based on the goal of providing a device that can accommodate high inrush current loads such as lamps and motors, while being fully protected against longer lasting overloads and short circuits without causing potentially damaging junction temperatures. Most importantly, the protection must operate well at all times including abnormally low supply and input drive voltages.

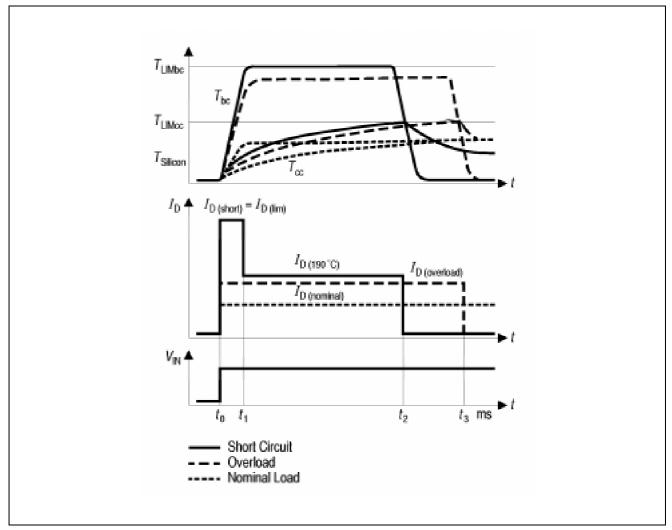

Figure 5 HITFET® Temperature Behavior

Figure 5 shows waveforms of the HITFET® silicon temperature and operation in the normal mode, overload, and short circuit. The base chip sensor is an integral part of the power transistor (please see Figure 3). This sensor is a very fast reacting sensor that gets activated within a few microseconds once the chip temperature  $T_{hc}$ reaches the trip temperature  $T_{LIMbc}$  of about 190 °C. The top temperature and current traces in Figure 5 show the behavior in case of a short circuit. The initial peak current is limited to the value defined in the data sheet as the  $I_{D(lim)}$ . This is the highest current the device is capable of conducting in case a short or overload. The combination of a high current flow and most of the supply voltage across the switch in case of a short circuit causes very high dissipation and a very rapid increase of the chip temperature. As soon as the base chip temperature reaches the maximum allowable temperature (at  $t = t_1$ ) the base chip sensor activates a current limiting circuit, which reduces the current to a lower value so that the base chip temperature does not exceed 190 °C. At the same time, the chip-onchip temperature sensor continues to heat up  $(T_{cc}$  dashed curve). Once it reaches the trip temperature  $T_{\text{LIMCC}}$  (>150 °C, typical value = 160 °C) at  $t = t_2$ , it turns on and shunts the gate drive signal with a typical saturation voltage of about 1 V between the gate and source, resulting in turn-off of the power chip. As long as the input drive signal remains on, the HITFET® remains latched off, because the chip-on-chip sensor continues to conduct. Reset is accomplished by removal and reapplication of the input drive signal. The middle temperature and current traces in Figure 5 show a case of the thermal overload, whereby the base chip temperature does not reach the  $T_{\rm LIMbc}$  trip point, but is above the  $T_{\rm LIMcc}$  chip-on-chip temperature trip point. In this case the current amplitude does not change until the chip-on-chip sensor temperature reaches the  $T_{\text{LIMCC}}$  trip point at  $t = t_3$ , when the sensor shuts off the power chip. Since the thermal load in this case is smaller compared to the short circuit load, it takes longer to reach the chip-on-chip trip temperature. The bottom current and temperature traces show normal operation with a nominal load current.

The device evaluations confirm the goals of having several major benefits by employment of two separate sensors. The first benefit is operation with optimized on-resistance at all times without the need for additional external components. In case of a TEMPFET®, the short circuit current has to be limited by the gate drive voltage in order to protect the device against too high transient junction temperature. This reduces the minimum on-resistance of the device to a higher value that the device is normally capable of producing. There is a discrete circuit that can provide 10 V or even higher gate drive during normal operation and reduced gate drive voltage when the load is shorted. Unfortunately, there is an associated cost with discrete components required to provide such optimized on-resistance operation. In case of a HITFET® there are no external components needed and the only difference between operation with 10 V at the input compared to 5 V is about 20% increase in on-resistance at 5 V input drive. The second major benefit is that the peak transient temperature during short circuit is limited to a relatively low transient temperature of 190 °C with the maximum steady state operating temperature limited to a very safe level of just above 150 °C. This makes the design very rugged in terms of long term reliability, since the milliFET® technology is qualified for continuous operation at 175 °C. Finally, the chip-on-chip temperature sensor guarantees short circuit protection at very low input drive voltages. The basic issue is that the input control circuit requires certain minimum voltage to operate properly. However, the chip-on-chip sensor makes this a non-issue because it requires only 0.5 mA at typically less than 1.0 V to remain latched on at room temperature.

### **Drive Requirements**

The HITFET® input is compatible with logic level and standard level drive signals. If the input voltage is sourced from a 5 V regulated supply or the drive signal comes directly from a microcontroller, the drive circuit is one of the simplest available. The only difference in performance in this case is an increase of the on-resistance of about 20% compared to the

on-resistance when driven by 10 V. This is considered quite acceptable considering that a direct drive from a very popular microcontroller type such as 8051 or drive from a discrete logic circuit are among the most cost effective solutions. Only one pull up resistor is necessary, if the driver supplies less than the minimal needed input current of 500  $\mu$ A.

The continuous input voltage should normally be limited to the maximum of 10 V. However, this limit can be exceeded, provided that the input current is limited to 2 mA. Once the input voltage reaches about 11 V, it exceeds the breakdown voltage of the input ESD protective diode. Therefore, the input current must be limited in order to keep the diode junction dissipation to a safe value. The input voltage typically exceeds 10 V level only when the HITFET® is used as a high side driver or the input drive voltage is supplied directly from the battery in low side applications.

Regardless of the type of the drive circuit, the drive source must be capable of providing at least 0.5 mA for the chip-on-chip sensor to stay latched at room temperature or 1.0 mA to stay latched at -40 °C.

The minimum allowed input voltage is -0.2 V. If there is a possibility that the input voltage exceeds -0.2 V minimum limit, the input current has to be limited to -2.0 mA to prevent the latch-up and possible damage of the input circuit. The input voltage reverse polarity typically occurs in high side switching applications or when there is a potential difference between the logic driver circuit ground and power ground. If this is the case, a sufficient series resistance in the reverse input current path has to be included in the turn-off circuit.

Both of the above requirements imply than only a moderate switching speed is practical. This is the case indeed, since the input circuitry includes a dv/dt limiter which restricts the maximum slew rate to 3 V/ms during turn-on and turn-off. This assures low noise operation, while providing reasonably low switching losses at switching frequencies up to a few kHz.

#### **Current-Sense**

The current sense terminal that is available in a 5-pin TO-220 package enables the user to monitor the sense voltage that is proportional to the load current. The sense voltage is generated across the internal sensing resistor  $R_{\rm CCINT}$  by the current flow from only a few power transistor cells that are in parallel with all of the main power transistor cells. The typical sense voltage range is 0 - 0.5 V. This voltage can be used as a linear feedback signal or as an indicator of the normal operation and fault modes such as short or open circuit. **Figure 6** shows the equivalent circuit of the HITFET® current sensing principle.

The sense current  $I_{\mathrm{S}}$  is proportional to the load current as long as the  $R_{\rm CCINT}$  sensing resistor has low enough resistance. The principal of current proportionality is based on the fact that all power transistor cells share the load current equally as long as they are all equal in size and the connecting resistance between the drain and the source of all cells is equal. In order to create the voltage that is proportional to the load current, there is a need for a resistor in series with the current sense path. This changes the symmetry of the circuit resulting in a deviation of the proportionality, by reducing the effective gate voltage in the sense cells due to the source voltage feedback from the sensing resistor. However, as long as the resistance of the sense resistor is low enough, the results acceptable.

Figure 6

Equivalent Circuit of the HITFET® Sense Path

Furthermore, the external resistor connected in parallel with the internal sense resistor improves the proportionality and minimizes the voltage increase when the junction temperature increases. The following calculation illustrates the influence of the sense resistor value on the current proportionality.

The load current is given by

$$I_{D} = I_{M} + I_{S} \tag{1a}$$

The voltage drop across the transistor is:

$$V_{DS} = I_{M} \times R_{DS(ON)} = I_{S} \times (R_{DS(ON)S} + R_{CCRES})$$

(1b)

In the ideal case  $(R_{\text{CCRES}} = 0 \Omega)$  the divider ratio r is:

$$r = \frac{I_{\rm D}}{I_{\rm S}} = 1 + \frac{R_{\rm DS(ON)S}}{R_{\rm DS(ON)}} \tag{2}$$

With  $R_{\text{CCRES}} \neq 0 \Omega$ , the ratio changes to r':

$$r' = \frac{I_D}{I_S} = r + \frac{R_{CCRES}}{R_{DS(ON)}}$$

(3)

In the case of the BTS 917 as an example, this means:

$$r' = 530 + \frac{47||160}{0.136} = 797$$

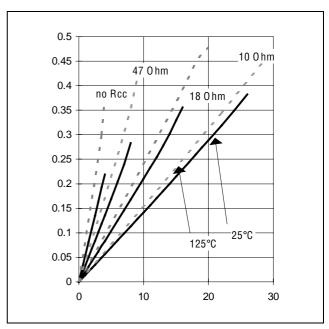

Figure 7 BTS 917 Sense Voltage vs.  $I_D$

Figure 8 BTS 917 Typical Short Circuit Current vs.  $V_{\rm DS}$

The resistance values are chosen at 125 °C, as a very typical operating condition. The typical measured r' of a BTS 917 under those conditions is 850, which is less than 7% higher than calculated. **Figure 7** and **Figure 8** above show that a lower value of  $R_{\rm CCFXT}$  increases the

short circuit current limit and decreases the output sense voltage. At the same time, it also minimizes the temperature influence on the sensing voltage caused by the temperature dependence of the internal sense resistor. The final selection of the external resistance value depends upon the desirable short circuit current limit as well as upon the desirable sense voltage level.

## Status Feedback Signal

The HITFET® does not have a status signal, but this does not preclude the option of monitoring the input current to create the status signal. Since there are three states of the input current, they can be utilized for determination of the HITFET® operating status. During the normal operation the input current  $I_{\rm in}^{(1)}$  has a typical value of 30  $\mu$ A. Once the HITFET® is in the current limiting mode, the input current  $I_{in}^{(2)}$  has a typical value of 120 µA. The third operating mode is thermal shutdown followed by the input latching "low". This mode requires a minimum current of 500 µA at room temperature or 1.0 mA at -40 °C for the HITFET® to stay latched. Therefore, the difference between 500 µA (or higher input current up the theoretical maximum of 4.0 mA) and 30 µA of the input current signifies the difference between the thermal shutdown and normal operation. This also makes the implementation of the status signal quite simple by monitoring the voltage drop across the resistor in series with the input.

During the normal operation, the voltage drop across the series resistor is very small resulting in the voltage at the input being nearly the same as the supply voltage of the input driving circuit. Once the HITFET® latches "off", the input voltage drops to 1.3 V or below in order to keep the power transistor off. Therefore, if one drives the HITFET® input from a microcontroller through a series resistor  $R_{\rm in}$  (or by an open drain and  $R_{\rm in}$  resistor connected to the 5 V logic voltage source) and senses the voltage at the HITFET® input, the voltage level can be observed for normal and fault modes.

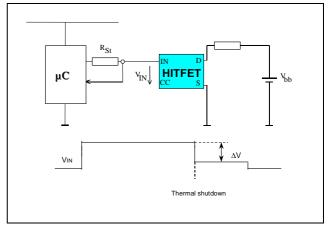

Figure 9

Status Implementation through the Input Pin

With the input "low" the status is always "low" and with the input "high" the status is "high" as long as there is no short circuit or thermal overload. The status "low" in this case means voltage level of 1.3 V or less. The most practical series resistor value seems to be the value that provides the maximum of 1.0 mA latching current to the input. This means:

$$R_{\rm in} = \frac{V_{\rm drive(hi)} - 1.3}{1 \times 10^{-3}}$$

or  $R_{\rm in}\cong 3.6~{\rm k}\Omega$  (rounded off to the standard value) if assuming  $V_{\rm drive(hi)}=5~{\rm V}$  (standard logic supply voltage). The typical voltage drop across this resistor during normal operation would be only 108 mV and therefore, would have a minimal influence on the drive voltage reduction that could affect the HITFET® on-resistance. Figure 9 shows the input voltage waveforms during normal and short circuit operation. The short circuit fault is indicated when the drive voltage is "high" and the input voltage is "low".

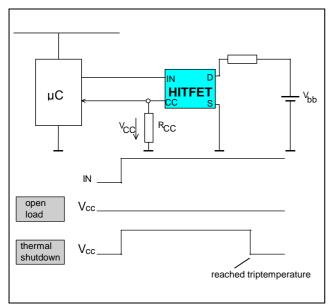

One can also use the sensing pin voltage  $V_{\rm cc}$  of a five-pin HITFET® for the status monitoring. **Figure 10** above shows this option. During normal operation the sense voltage  $V_{\rm cc}$  across resistor  $R_{\rm cc}$  is "high" when the input drive voltage is "high". In case of a thermal shutdown, the input drive voltage is "high" ( $V_{\rm drive(hi)} = 5$  V),

the input voltage  $V_{\rm in}$  is "low", and  $V_{\rm cc}$  is "low". On the other hand, if  $V_{\rm in}$  is "high" and  $V_{\rm cc}$  "low", this is an indication of an open load.

Therefore, in addition to using the  $V_{\rm cc}$  voltage as proportional current sensing means, it can be also used as the status pin that can distinguish between the normal operation, thermal shutdown, and open circuit.

Figure 10 Sense Pin Status Indicator

## **Reverse Polarity**

Reverse polarity of the battery voltage causes very much higher power dissipations in the device than in normal forward operation. The reason for this behavior is the parasitic reverse diode, which is produced by the SIPMOS technology. The following example should illustrate this fact:

$R_{\rm Load}$  = 3  $\Omega$ ,  $R_{\rm DSON}$  = 50 m $\Omega$ ,  $V_{\rm BAT}$  = 12 V; In normal forward operation mode, the drain current is:

$$I_{\rm D} = \frac{V_{\rm BAT}}{R_{\rm Load} + R_{\rm DSON}} = \frac{12 \text{ V}}{3 \text{ W} + 50 \text{ mW}} = 3.93 \text{ A}$$

the resulting power dissipation is:

$$P_{\text{TOT}} = I_D^2 \times R_{\text{DSON}} = (3.93 \text{ A})^2 \times 50 \text{ m}\Omega = 776 \text{ mW}$$

A change of the polarity of the battery voltage however causes a voltage drop of about 1 V at

the reverse diode, if the HITFET® is switched off. At the load thus there is a voltage of:

$$V_{\text{Load}} = V_{\text{BAT}} - V_{\text{Diode}} = 12 \text{ V} - 1 \text{ V} = 11 \text{ V}$$

.

In this case the drain current is:

$$I_{\rm D} = \frac{V_{\rm Load}}{R_{\rm Load}} = \frac{11 \text{ V}}{3 \Omega} = 3.67 \text{ A}$$

With this result, the power dissipation in the reverse diode increases to:

$$P_{\text{TOT}} = I_D \times V_{\text{Diode}} = (3.67 \text{ A})^2 \times 1 \text{ V} = 3.67 \text{ W}.$$

Because of the relation between these two very different power dissipations, it is necessary to have a look at the cooling conditions.

If firmness against reverse battery is demanded, the dimension of the heat sink is to be adapted to the higher power dissipation of the reverse operating mode.

# **Typical Applications**

The HITFET® family of devices are designed to be used in variety of low frequency switching applications or linear applications. They are most frequently used in low voltage lighting applications and inductive load drive applications such as solenoid or motor drives. The key advantage in lighting applications is the ability to limit the inrush current. This ability is expected to increase the lamp life without any additional cost of the drive circuit or increased switch dissipation caused by on-resistance that is not fully optimized.

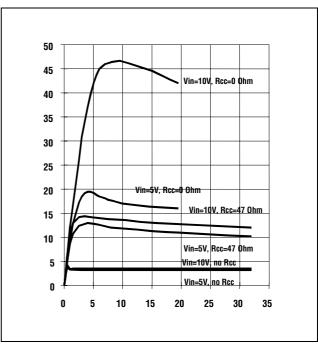

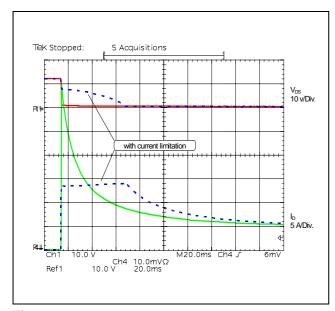

Figure 11 shows a typical lamp load switched on with a five-pin HITFET® with and without current limit activated. The inrush current through the HITFET® is below 50% of the unlimited inrush current and the only consequence is a slight increase of the lamp warm-up time. This does not affect the visible performance of the lamp, since the process is still very short, but the life expectancy of the lamp filament is greatly improved. In the case of a DC motor drive application, the device should be selected so that the current limit is either above the inrush current or above the minimum current required to start the motor, particularly in case of a PWM variable speed application.

Figure 11 Lamp Inrush when Switched with Five-Pin HITFET®

This is important so that the turn-on dissipation does not cause thermal shutdown when operating at high ambient temperature. In this case, it may be advantageous to use a five pin HITFET<sup>®</sup>, since the current limit can be programmed over a wider range compared to the equivalent three pin device.

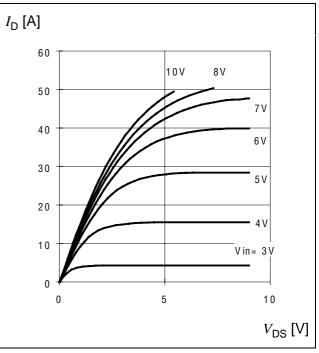

In addition to the above, even though HITFETs® are intended mostly for low frequency switching applications (up to a few kHz), they are quite capable of operation in a linear mode, just like any other SIPMOS® or TEMPFET® transistors. This is obvious when one examines the output characteristics in Figure 10.

The typical characteristics are very much like the characteristics of a standard SIPMOS® transistor. Therefore, any linear low frequency application such as variable speed dc motor drive can be accomplished with a HITFET®. The key limitation in such case is the maximum dissipation that can be afforded without thermal shutdown. It depends upon the HITFET® chip size, the HITFET® package size, thermal properties of the heatsink, and the maximum ambient temperature.

Figure 12 BTS 917 typical Output Characteristics

If a single HITFET® cannot dissipate enough power to drive the motor, two or more devices can be paralleled just like any other MOSFETs. The only requirement is that they all are mounted on the same heatsink or that individual heatsinks have similar thermal properties. Otherwise, the device that has to dissipate much higher power than the rest could shut down and cause increased thermal load in the remaining devices that could result in shutdown of all devices.

## **Summary**

The development of the TEMPFET® family of devices created the first MOSFET based transistors that provide reliable protection against overtemperature and short circuit. The new family of HITFET® devices goes a step further by including the ESD protection, overvoltage protection, programmable current limit, optimized on-resistance, built-in switching speed control to limit dv/dt, and lower junction to case thermal impedance, in addition to thermal and short circuit protection. Remarkably, all of this has been accomplished with a chip size that is smaller that the chip size of the TEMPFET® with on-resistance. In short, development is another step forward in efforts to reach better performing products that also afford lower systems cost.

#### References

- 1. K. Reinmuth and L. Lorenz, "HITFET® Intelligent Lowside Switch for High Current Applications", PCIM Conference, Las Vegas, September 1996

- 2. M. Glogolja, "TEMPFET®- A Device One Step Closer to an Ideal Power Semiconductor Switch" Smart Power Economics, Technology, and Applications by Intertec Communications, October 1989.

- 3. M. Glogolja, "A High Current Short Circuit Tolerant MOSFET® Switch", IEEE Workshop on Automotive Electronics, October, 1989.

- 4. M. Glogolja and J. Tihanyi, "Smart SIPMOS<sup>®</sup> An Intelligent Power Switch", IEEE Industrial Applications Society, October 1986.

- 5. M. Glogolja and K. Reinmuth, "HITFET® A Low-side Smart Power Switch with Current sense", January 1997.

#### **Authors**

K. Reinmuth, M. Glogolja