## ICM7240/50/60 **CMOS Programmable** Timers/Counters

#### **FEATURES**

- Replaces 8240/50/60, 2240 in most applications

- Timing from microseconds to days

- . May be used as fixed or programmable counter

- · Programmable with standard thumbwheel switches

- · Select output count from 1RC to 255RC (ICM7240) 1RC to 99RC (ICM7250) 1RC to 59RC (ICM7260)

- · Monostable or astable operation

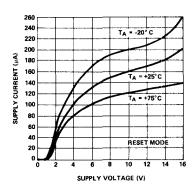

- Low supply current: 115μA @ 5 volts

- Wide supply voltage range: 2-16 volts

- Cascadeable

### **GENERAL DESCRIPTION**

The ICM7240/50/60 is a family of CMOS Timer/Counter circuits intended to replace Intersil's ICL 8240/50/60 and the 2240 in most applications. Together with the ICM7555/56 (CMOS versions of the SE/NE 555/6), they provide a complete line of RC oscillators/timers/ counters offering lower supply currents, wider supply voltage ranges, higher operating frequencies, lower component counts and a wider range of timing components. They are intended to simplify the selection of various time delays or frequency outputs from a fixed RC oscillator circuit.

Each device consists of a counter section, control circuitry, and an RC oscillator requiring an external resistor and capacitor. For counter/divider applications, the oscillator may be inhibited and an input clock applied to the TB terminal. The ICM7240 is intended for straight binary counting or timing, whereas the ICM7250 is optimized for decimal counting or timing. The ICM7260 is specifically designed for time delays in seconds, minutes and hours. All three devices use open drain output transistors, thereby allowing wire AND-ing. Manual programming is easily accomplished by the use of standard thumbwheel switches or hardwired connections. The ICM7240/50/60 are packaged in 16 pin CERDIP packages.

Applications include programmable timing, long delay generation, cascadeable counters, programmable counters, low frequency oscillators, and sequence timina.

### ORDERING INFORMATION

| , | PART<br>NUMBER | TEMPERATURE<br>RANGE | PACKAGE        |  |  |  |

|---|----------------|----------------------|----------------|--|--|--|

|   | ICM7240IJE     | -20°C to +85°C       | 16 Lead CERDIP |  |  |  |

|   | ICM7250IJE     | -20°C to +85°C       | 16 Lead CERDIP |  |  |  |

|   | ICM7260IJE     | -20°C to +85°C       | 16 Lead CERDIP |  |  |  |

|   | ICM7240/D      |                      | Dice Only      |  |  |  |

|   | ICM7250/D      |                      | Dice Only      |  |  |  |

|   | ICM7260/D      |                      | Dice Only      |  |  |  |

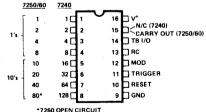

### PIN CONFIGURATION (OUTLINE DRAWING JE)

ICM7240, 7250, 7260

\*7260 OPEN CIRCUIT

### ICM7240/50/60

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage               | 18V             |

|------------------------------|-----------------|

| Input Voltage <sup>[1]</sup> | CND 03V+c       |

| Terminals 10,11,12,13,14     | V++0.3V         |

|                              | V + 0.3V        |

| Maximum continuous output    | FO A            |

| current (each output)        |                 |

| Power Dissipation [2]        |                 |

| Operating Temperature Range  | 20°C to +85°C   |

| Storage Temperature Range    | -55°C to +125°C |

#### NOTES:

- 1. Due to the SCR structure inherent in the CMOS process, connecting any terminal to voltages greater than V+ or less than GROUND may cause destructive device latchup. For this reason, it is recommended that no inputs from external sources not operating on the same supply be applied to the device before its supply is established, and that in multiple supply systems, the supply to the ICM7240/50/60 be turned on first.

- 2. Derate at -2 mW/°C above 25°C.

NOTE: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

OUTPUT

OUTPUT

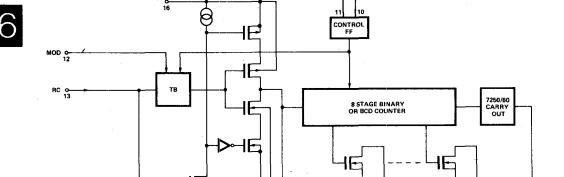

### **BLOCK DIAGRAM**

#### ICM7240/50/60

TRIGGER

RESET

| TB 1/O

GND

### ICM7240/50/60

### **ELECTRICAL CHARACTERISTICS**

Each of the three devices utilizes an identical timebase, control flip-flops, and basic counters, with the outputs consisting of open drain n-channel transistors. Only the ICM7250/60 have CARRY outputs.

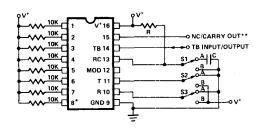

Test Conditions: Test circuit,  $V^+=5V$ ,  $T_A=+25^{\circ}C$ ,  $R=10K\Omega$ ,  $C=0.1\mu F$ , unless otherwise specified.

| PARAMETER                                    | SYMBOL. | CONDITIONS                                                                         | MIN | TYP  | MAX | UNITS  |

|----------------------------------------------|---------|------------------------------------------------------------------------------------|-----|------|-----|--------|

| Guaranteed Supply Voltage                    | V+      |                                                                                    | 2   |      | 16  | V      |

| Supply Current                               | I+      | Reset                                                                              |     | 125  |     | μΑ     |

|                                              | 1       | Operating, R = $10K\Omega$ , C = $0.1\mu$ F                                        |     | 300  | 700 | μΑ     |

|                                              |         | Operating, R = 1M $\Omega$ , C = 0.1 $\mu$ F                                       |     | 120  | 500 | μΑ     |

|                                              |         | TB Inhibited, RC Connected to GND                                                  |     | 125  |     | μA     |

| Timing Accuracy                              |         |                                                                                    |     | 5    |     | %      |

| RC Oscillator Frequency<br>Temperature Drift | ∆f/∆T   | (Exclusive of RC Drift)                                                            |     | 250  |     | ppm/°C |

| Time Base Output Voltage                     | Vотв    | ISOURCE = 1 mA                                                                     | 3.5 | 4.2  |     | . V    |

|                                              |         | Isink = 3.2 mA                                                                     |     | 0.25 | 0.6 | ) v    |

| Time Base Output<br>Leakage Current          | ITBLK   | RC = Ground                                                                        |     |      | 25  | μА     |

| Mod Voltage Level                            | VMOD    | V+ = 5V                                                                            |     | 3.5  |     | V      |

|                                              |         | V <sup>+</sup> = 15V                                                               |     | 11.0 |     | V      |

| Trigger Input Voltage                        | VTRIG   | V+ = 5V                                                                            |     | 1.6  | 2.0 | V      |

| • •                                          |         | V <sup>+</sup> = 15V '                                                             |     | 3.5  | 4.5 | V      |

| Reset Input Voltage                          | VRST    | V <sup>+</sup> = 5V                                                                |     | 1.3  | 2.0 | V      |

|                                              |         | V <sup>+</sup> = 15V                                                               |     | 2.7  | 4.0 | V      |

| Max Count Toggle Rate                        | ft      | V+ = 2V 7                                                                          |     | 1    |     | MHz    |

| 7240                                         | 1       | V <sup>+</sup> = 5V Counter/Divider Mode                                           | 2   | , 6  |     | MHz    |

|                                              |         | V+ = 15V                                                                           |     | 13   |     | MHz    |

|                                              |         | 50% Duty Cycle Input with Peak to<br>Peak Voltages Equal to V <sup>+</sup> and GND |     |      |     |        |

| Max Counter Toggle Rate 7250, 7260           | ft      | V <sup>+</sup> = 5V<br>(Counter/Divider Mode)                                      | 1.5 | 5    |     | MHz    |

| Max Count Toggle Rate<br>7240, 7250, 7260    | ft      | Programmed Timer — Divider Mode                                                    |     |      | 100 | KHz    |

| Output Saturation Voltage                    | VSAT    | All Outputs except TB Output<br>V <sup>+</sup> = 5V, I <sub>OUT</sub> = 3.2 mA     |     | 0.22 | 0.4 | V      |

| Output Leakage Current                       | lork    | V <sup>+</sup> = 5V, per Output                                                    |     |      | 1   | μΑ     |

| MIN Timing Capacitor                         | Ct      |                                                                                    | 10  |      |     | pF     |

| Timing Resistor Range                        | Rt      | V <sup>+</sup> ≤ 5.5V                                                              | 1K  |      | 22M | Ω      |

| •                                            | 1       | V <sup>+</sup> ≤ 16V                                                               | 1K. |      | 22M | Ω      |

### **TEST CIRCUIT**

S1-A = RC RUN B = T. B. INPUT RUN

S2--A = INACTIVE

S3-A = INACTIVE B = RESET

NOTE: S1-B INHIBITS THE TIMEBASE SECTION, ALLOWING TERMINAL 14 TO BECOME THE COUNTER INPUT.

\* TERMINAL 15 IS CARRY OUTPUT FOR 7250/60 DEVICES.

\* TERMINAL 8 IS OPEN CIRCUIT FOR 7260.

### TYPICAL PERFORMANCE CHARACTERISTICS

#### SUPPLY CURRENT AS A FUNCTION OF SUPPLY VOLTAGE

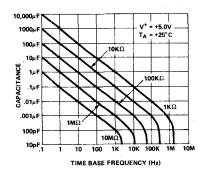

### TIMEBASE FREE RUNNING FREQUENCY AS A FUNCTION OF R AND C

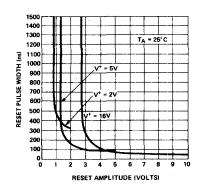

### MINIMUM RESET PULSE WIDTH AS A FUNCTION OF RESET AMPLITUDE

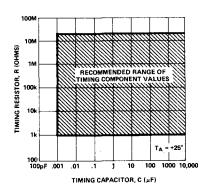

## RECOMMENDED RANGE OF TIMING COMPONENT VALUES FOR ACCURATE TIMING

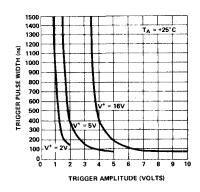

### MINIMUM TRIGGER PULSE WIDTH AS A FUNCTION OF TRIGGER AMPLITUDE

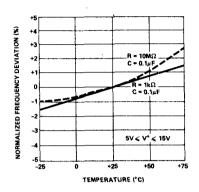

### NORMALIZED FREQUENCY STABILITY IN THE ASTABLE MODE AS A FUNCTION OF TEMPERATURE

### TYPICAL PERFORMANCE CHARACTERISTICS

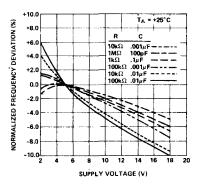

# NORMALIZED FREQUENCY STABILITY IN THE ASTABLE MODE AS A FUNCTION OF SUPPLY VOLTAGE

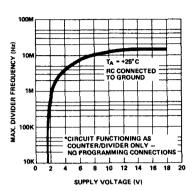

### MAXIMUM DIVIDER FREQUENCY vs. SUPPLY VOLTAGE\*

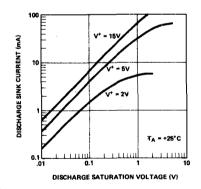

### DISCHARGE OUTPUT CURRENT AS A FUNCTION OF DISCHARGE OUTPUT VOLTAGE

### OUTPUT SATURATION CURRENT AS A FUNCTION OF OUTPUT SATURATION VOLTAGE

### **DESCRIPTION OF PIN FUNCTIONS**

### **COUNTER OUTPUTS (PINS 1 THROUGH 8)**

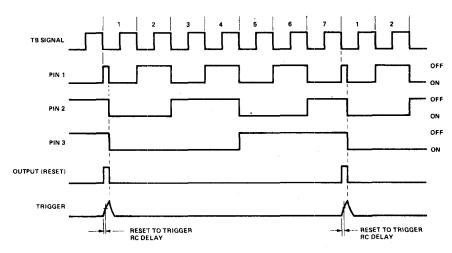

Each binary counter output is a buffered "open-drain" type. At reset condition, all the counter outputs are at a high, or non-conducting state. After a trigger input or when using the internal timebase, the outputs change state (see timing diagram, Figure 1). If an external clock input is used, the trigger input must overlap at least the first falling edge of the clock. The counter outputs can be used individually, or can be connected together in a wired-AND configuration, as described in the Programming section.

#### **GROUND (PIN 9)**

This is the return or most negative supply pin. It should have a very low impedance as the capacitor discharge and other switched currents could create transients.

#### RESET AND TRIGGER INPUTS (PINS 10 AND 11)

The circuits are reset or triggered by positive going control pulses applied to pins 10 and 11, and once triggered they ignore additional trigger inputs until either the timing cycle is completed or a reset signal is applied. If both reset and trigger are applied simultaneously trigger overrides reset. Minimum input pulse widths are shown in the typical performance characteristics. Note that all devices feature power ON reset.

### MODULATION AND SYNC INPUT (PIN 12)

The period t of the time base oscillator can be modulated by applying a DC voltage to this terminal. The time base oscillator can be synchronized to an external clock by applying a sync pulse to pin 12.

### TIMEBASE INPUT/OUTPUT PIN (TERMINAL 14)

While this pin can be used as either a time base input or output terminal, it should only be used as an input terminal if terminal 13 (RC) is connected to GND.

If the counter is to be externally driven, care should be taken to ensure that fall times are fast (see Operating Limits section).

Under no conditions is a 300pF capacitor on this terminal useful and should be removed if a 7240/50/60 is used to replace an 8240/50/60 or 2240.

### CARRY OUTPUT (TERMINAL 15, ICM7250/60 ONLY)

This pin will go HI for the last 10 counts of a 59 or 99 count, and can be used to drive another 7250 or 7260 counter stage while still using all the counter outputs of the first. Thus, by cascading several 7250's a large BCD countdown can be achieved.

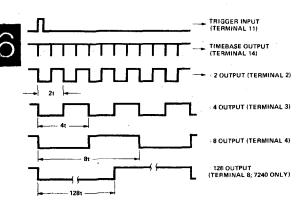

The basic timing diagrams for the ICM7240/50/60 are shown in Figure 1. Assuming that the device is in the RESET mode, which occurs on powerup or after a positive signal on the RESET terminal (if TRIGGER is low), a positive edge on the trigger input signal will initiate normal operation. The discharge transistor turns on, discharging the timing capacitor C, and all the flip-flops in the counter chain change states.

Note that for straight binary counting the outputs are symmetrical; that is, a 50% duty cycle HI-LO. This is not the case when using BCD counting. See Figure 3.

Figure 1. Timing Diagram for ICM7240/50/60

#### CIRCUIT DESCRIPTION

The timing cycle is initiated by applying a positive-going trigger pulse to pin 11. This pulse enables the counter section, sets all counter outputs to the LOW or ON state, and starts the time base oscillator. Then, external C is charged through external R from 20% to 70% of V+, generating a timing waveform with period t, equal to 1RC. A short negative clock or time base pulse occurs during the capacitor discharge portion of the waveform. These clock pulses are counted by the binary counter of the 7240 or by two cascaded Binary Coded Decimal (BCD) Counters in the 7250/60. The timing cycle terminates when a positive-going reset

pulse is applied to pin 10. When the circuit is at reset, both the time base and the counter sections are disabled and all the counter outputs are at a HIGH or OFF state. The carrry-out is also HIGH.

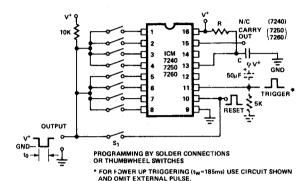

In most timing applications, one or more of the counter outputs are connected back to the reset terminal; the circuit will start timing when a trigger is applied and will automatically reset itself to complete the timing cycle when a programmed count is completed. If none of the counter outputs are connected back to the reset terminal (switch S<sub>1</sub> open), the circuit operates in its astable, or free-running mode, after initial triggering.

### PROGRAMMING CAPABILITY

The counter outputs, pins 1 through 8, are open-drain N-channel FETs, and can be shorted together to a common pull-up resistor to form a "wired-AND" connection. The combined output will be LOW as long as any one of the outputs is low. Each output is capable of sinking ≈5 mA. In this manner, the time delays associated with each counter output can be summed by simply shorting them together to a common output. For example, if only pin 6 is connected to the output and the rest left open, the total duration of the timing cycle (monostable mode) to would be 32t for a 7240 and 20t for a 7250/60. Similarly, if pins 1, 5, and 6 were shorted to the output bus, the total time delay would be  $t_0 = (1 + 16 + 32)t$  for the 7240 or (1 + 10 + 20)t for the 7250/60. Thus, by selecting the number of counter terminals connected to the output bus, the timing cycle can be programmed from:

$1t \le t_0 \le 255t \ (7240)$

$1t \le t_0 \le 99t (7250)$

$1t \le t_0 \le 59t (7260)$

Note that for the 7250 and 7260, invalid count states (BCD values  $\geq$  10) will not be recognized and the counter will not stop.

The 7240/50/60 can be configured to initiate a controlled timing cycle upon power up, and also reset internally; see figure 2. Applications for this could include lawn watering sprinkler timing, pump operation, etc.

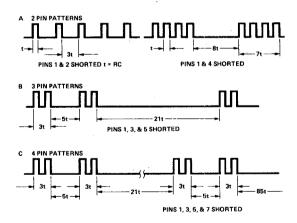

### **BINARY OR DECIMAL PATTERN GENERATION**

In astable operation, as shown in Figure 2, the output of the 7240/50 appears as a complex pulse pattern. The waveform of the output pulse train can be determined directly from the timing diagram of Figure 1, which shows the phase relations between the counter outputs. Figure 3 shows some of these complex pulse patterns. The pulse pattern repeats itself at a rate equal to the period of the highest counter bit connected to the common output bus. The minimum pulse width contained in the pulse train is determined by the lowest counter bit connected to the output.

### THUMBWHEEL SWITCHES

While the ICM7240 is frequently hard wired for a particular function, the ICM7250 and ICM7260 can easily be programmed using thumbwheel switches. Standard BCD thumbwheel switches have one common and four inputs (1,2,4 and 8) which are connected according to the binary equivalent to the digits 0 through 9.

### ICM7240/50/60

For a single ICM7250 two such switches would select a time of 1<sub>RC</sub> to 99<sub>RC</sub>. Cascading two ICM7250's (using the carry out gate) would expand selection to 9999<sub>RC</sub>. For a ICM7260, there are standard BCD thumbwheel switches for the 0 through 5 digit (twelve position 0 to 5 repeated).

Figure 2. Generalized Circuit for Timing Applications (Switch S1 open for astable operation, closed for monostable operation)

Figure 3. Pulse Patterns Obtained by Shorting Various Counter Outputs

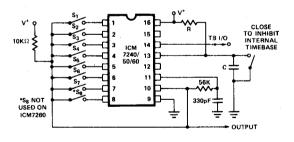

#### NOTES ON THE COUNTER SECTION

Used as a straight binary counter (ICM7240), as a  $\div 100$  (ICM7250), or  $\div 60$  (ICM7260) all devices are significantly faster than their bipolar equivalents. However, when using these devices as programmable counters the maximum frequency of operation is reduced by more than an order of magnitude. For any division ratio other than 256 (ICM7240), 100 (ICM7250), or 60 (ICM7260) the maximum input frequency must be limited to approximately 100 KHz or less (with V+equal to  $\pm 5$  volts). The reason for this is two-fold:

- a. Since Ripple counters are used, there is a propagation delay between each individual ÷2 counter (8 counters for the ICM7240/50 and 7 for the ICM7260). Outputs from the individual ÷2 counters are AND'ed together to provide the output signal and the Reset/Trigger signal.

- b. There must be a delay of the positive going output to the Reset terminal, (pin 10) and the Trigger terminal (pin 11). The Reset signal must therefore be generated first, and from this signal another signal is obtained through a delay network. The trigger overrides Reset.

The delay between Trigger and Reset is generated by the signal RC network consisting of the  $56k\Omega$  resistor and the 330pF capacitor.

The delay caused by the counter Ripple delays can be as long as  $2\mu s$  (5 volt supply), and the delay between Reset and Trigger should be at least  $2\mu s$ . The sum of these two delays cannot be greater than one-half of the input clock period for reliable operation. See Figure 4 and 5.

Figure 4. Programming the Counter Section of the ICM7240/50/60

Figure 5. Waveforms for Programming the Counter Section for a Division Ratio of 7 (S1, S2, S3 Closed)

#### **APPLICATIONS**

#### **GENERAL CONSIDERATIONS**

Shorting the RC terminal or output terminals to V<sup>+</sup> may exceed dissipation ratings and/or maximum DC current limits (especially at high supply voltages).

6

There is a limit of 50pF maximum loading on the TB I/O terminal if the timebase is being used to drive the counter section. If higher value loading is used, the counter sections may miscount.

For greatest accuracy, use timing component values shown in the graph under Typical Performance Characteristics. For highest frequency operation it will be desirable to use very low values for the capacitor; accuracy will decrease for oscillator frequencies in excess of 200 KHz.

When driving the counter section from an external clock, the optimum drive waveform is a square wave with an amplitude equal to supply voltage. If the clock is a very slow ramp triangular, sine wave, etc., it will be necessary to "square up" the waveform (rise/fall time  $\leq 1\mu s$ ); this can be done by using two CMOS inverters in series, operating from the same supply voltage as the ICM 7240/50/60.

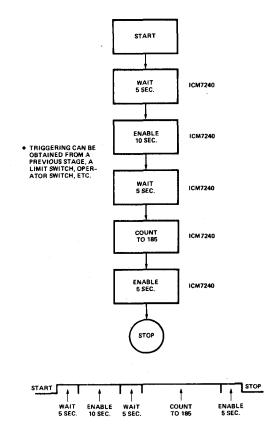

By cascading devices, use of low cost CMOS AND/OR gates and appropriate RC delays between stages, numerous sequential control variations can be obtained. Typical applications include injection molding machine controllers, phonograph record production machines, automatic sequencers (no metal contacts or moving parts), milling machine controllers, process timers, automatic lubrication systems, etc.

By selection of R and C, a wide variety of sequence timing can be realized. A typical flow chart for a machine tool controller could be as follows:

Figure 6.

## 6

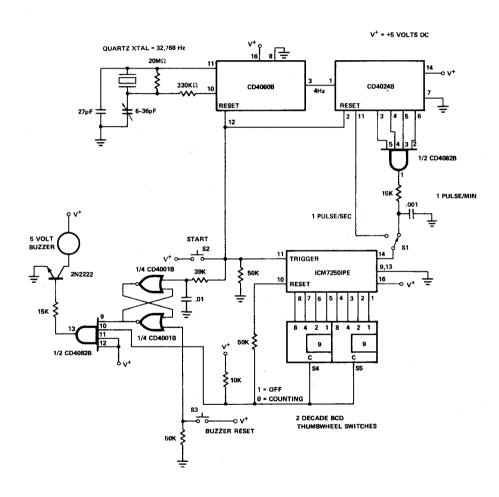

### CMOS PRECISION PROGRAMMABLE 0-99 SECONDS/MINUTES LABORATORY TIMER

The ICM7250 is well suited as a laboratory timer to alert personnel of the expiration of a preselected interval of time.

When connected as shown, the timer can accurately measure preselected time intervals of 0-99 seconds or 0-99 minutes. A 5 volt buzzer alerts the operator when the preselected time interval is over.

The circuit operates as follows:

The time base is first selected with S1 (seconds or minutes), then units 0-99 are selected on the two thumbwheel switches S4 and S5. Finally, switch S2 is depressed to start the timer. Simultaneously the quartz crystal controlled divider circuits are reset, the ICM7250 is triggered and counting begins. The ICM7250 counts until the pre-programmed value is reached, whereupon it is reset, pin 10 of the CD4082B is enabled and the buzzer is turned on. Pressing S3 turns the buzzer off.

Figure 7.

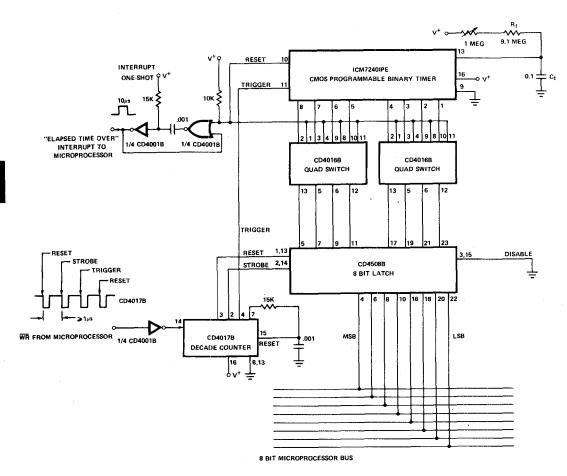

### LOW POWER MICROPROCESSOR PROGRAMMABLE INTERVAL TIMER

The ICM7240 CMOS programmable binary timer can be configured as a low cost microprocessor controlled interval timer with the addition of a few inexpensive CD4000 series devices.

With the devices connected as shown, the sequence of operation is as follows:

The microprocessor sends out an 8 bit binary code on its 8 bit I/O bus (the binary value needed to program the ICM7240), followed by four WRITE pulses into the CD4017B decade counter. The first pulse resets the 8 bit latch, the second strobes the binary value into the 8

bit latch, the third triggers the ICM7240 to begin its timing cycle and the fourth resets the decade counter.

The ICM7240 then counts the interval of time determined by the R-C value on pin 13, and the programmed binary count on pins 1 through 8. At the end of the programmed time interval, the interrupt one-shot is triggered, informing the microprocessor that the programmed time interval is over.

With a resistor of approximately 10 M $\Omega$  and capacitor of 0.1  $\mu$ F, the time base of the ICM7240 is one second. Thus, a time of 1-255 seconds can be programmed by the microprocessor, and by varying R or C, longer or shorter time bases can be selected.

Figure 8.

6

### INTERSIL

### CHIP TOPOGRAPHY

ALL CHIPS 68 x 69 mils