# High Speed 12 Bit A/D Converter

#### General Description

The AD578 is a 12-bit successive approximation analog-to-digital converter complete with internal clock and reference. The combination of bipolar and CMOS technology optimizes accuracy, speed, and power in a convenient 32 pin ceramic DIP. Maximum conversion time is  $3\mu S$  (L version) however the device may be operated at faster speeds with reduced resolution by short cycling.

Multiple input ranges are accommodated in both unipolar and bipolar modes using internal resistors. These resistors also track those in the reference for low gain drift with temperature. All data bits are available in both parallel and serial form using either the internal or an external clock.

#### **Applications**

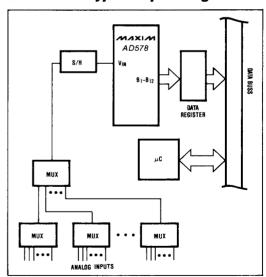

High Speed Data Acquisition Systems

Transient Recorders

Multichannel Data Loggers

Digital Signal Processing

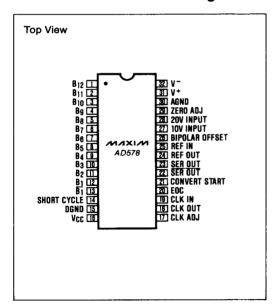

#### **Pin Configuration**

#### Features

- Pin-for-Pin Second Source

- ▶ Fast Conversion: 3μs (AD578L)

- ♦ Internal +10V Reference

- Low Gain TC: 30ppm/°C Max

- Linearity Error: 0.012% Max

- No Missing Codes Over Temperature

- Parallel and Serial Outputs

- ♦ Adjustable Internal Clock

- ♦ Short Cycle Capability

#### **Ordering Information**

| PART    | TEMP RANGE      | PACKAGE             |  |  |

|---------|-----------------|---------------------|--|--|

| AD578JN | 0°C to +70°C    | 32 Lead Ceramic DIP |  |  |

| AD578KN | 0°C to +70°C    | 32 Lead Ceramic DIP |  |  |

| AD578LN | 0°C to +70°C    | 32 Lead Ceramic DIP |  |  |

| AD578SN | -55°C to +125°C | 32 Lead Ceramic DIP |  |  |

| AD578TN | -55°C to +125°C | 32 Lead Ceramic DIP |  |  |

For ±12V Supplies, Order AD578ZXX (For Hermetic Seal (D) Please Contact Factory.)

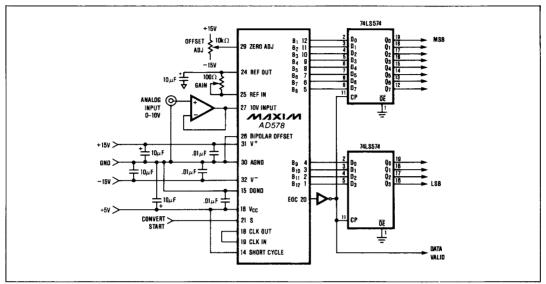

#### \_Typical Operating Circuit

NIXIN

**Maxim Integrated Products 1-107**

### High Speed 12 Bit A/D Converter

#### **ABSOLUTE MAXIMUM RATINGS**

| Positive Supply Voltage, V <sup>+</sup> (pin 31 to GND) +18V    | Analog Inputs (pins 25, 26, 27) ±12V              |

|-----------------------------------------------------------------|---------------------------------------------------|

| Negative Supply Voltage, V (pin 32 to GND)18V                   | (pins 28, 29) ±24V                                |

| Digital Supply Voltage, V <sub>CC</sub> (pin 16 to GND)+7V      | Ref Out Indefinite Short to AGND                  |

| Digital Input Voltage                                           | Momentary Short to V <sup>+</sup>                 |

| (pins 14, 17, 19, 21) GND - $0.5V \le V_{IN} \le V_{CC} + 0.5V$ | Power Dissipation 2W @ 100°C                      |

| Analog GND to Digital GND ±0.5V                                 | Storage Temperature65°C ≤ T <sub>A</sub> ≤ +160°C |

| · · · · · · · · · · · · · · · · · · ·                           | Lead Temperature (Soldering, 10 sec.) +300°C      |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS** (V<sup>+</sup> = +15V, V<sup>-</sup> = -15V, $V_{CC}$ = +5V, $T_A$ = +25°C, unless noted—Note 4)

| PARAMETER                    | CONDITIONS                                                                               | MIN                         | TYP              | MAX            | UNITS           |  |

|------------------------------|------------------------------------------------------------------------------------------|-----------------------------|------------------|----------------|-----------------|--|

| Offset (Note 1)              | Unipolar, T <sub>A</sub> = 25°C                                                          |                             | ±0.1             | ±0.25          | %FSR            |  |

|                              | $T_{MIN} \le T_A \le T_{MAX}$ ; AD578L,K,J,T                                             |                             | ±3               | ±10            | ppm/°C          |  |

|                              | AD578S                                                                                   |                             | ±3               | ±15            | ppm/°C          |  |

|                              | Bipolar (Note 1, 2), $T_A = 25^{\circ}C$<br>$T_{MIN} \le T_A \le T_{MAX}$ , AD578L,K,J,T |                             | ±0.1<br>±8       | ±0.25<br>±20   | %FSR<br>ppm/°C  |  |

|                              | AD578S                                                                                   |                             | ±8               | ±25            | ppm/°C          |  |

|                              | T <sub>A</sub> = 25°C                                                                    |                             | ±0.1             | ±0.25          | %FSR            |  |

| Gain Error (Note 1, 3)       | $T_{MIN} \le T_A \le T_{MAX}$ ; AD578L,K,J,T                                             |                             | ±15              | ±30            | ppm/°C          |  |

|                              | AD578S                                                                                   |                             | ±15              | ±50            | ppm/°C          |  |

|                              | T <sub>A</sub> = 25°C                                                                    |                             |                  | 1/2            |                 |  |

| Linearity                    | $T_{MIN} \le T_A \le T_{MAX}$ ; AD578L,K,J<br>AD578S.T                                   |                             | 3/4              | 3/4            | LSB             |  |

| Differential Linearity Error | $T_{MIN} \le T_A \le T_{MAX}$                                                            | <u> </u>                    | no missing codes |                |                 |  |

| Differential Linearity Drift | $T_{MIN} \le T_A \le T_{MAX}$                                                            |                             | ±2               |                |                 |  |

|                              |                                                                                          | <del>-  </del>              |                  | +100           | ppm/°C          |  |

| Reference Voltage Accuracy   | V <sub>nominal</sub> = 10.000V                                                           |                             | ±10              | ±100           | mV              |  |

| Reference Voltage Drift      | $T_{MIN} \le T_A \le T_{MAX}$                                                            |                             | ±10              | ±30            | ppm/°C          |  |

| Reference Output Current     | <del></del>                                                                              | ±1                          |                  |                | mA              |  |

| Power Supply Rejection Ratio | V <sup>+</sup> = +13.5 to +16.5V                                                         |                             |                  | 0.005          |                 |  |

| (Note 5)                     | V <sup>-</sup> = -13.5 to -16.5V<br>V <sub>CC</sub> = +4.5 to +5.5V                      |                             |                  | 0.005<br>0.005 | %/%∆V           |  |

|                              | AD578L                                                                                   | 3.0                         |                  |                |                 |  |

| Conversion Speed             | AD578K,T                                                                                 | 4.5                         |                  |                | μS              |  |

|                              | AD578J,S                                                                                 | 6.0                         |                  |                |                 |  |

|                              | 0V to +10V range                                                                         |                             | 5                |                |                 |  |

| Input Impedance              | 0V to +20V range                                                                         |                             | 10               |                | kΩ              |  |

| ,                            | -5V to +5V range<br>-10V to +10V range                                                   |                             | 5<br>10          |                |                 |  |

|                              | V+                                                                                       | 10.5                        | 10               | 10.5           | -               |  |

| Power Supply Range           | V-                                                                                       | 13.5<br>-13.5               |                  | 16.5<br>-16.5  | V               |  |

| (Note 5)                     | V <sub>CC</sub>                                                                          | 4.75                        |                  | 5.25           |                 |  |

|                              | V+                                                                                       |                             | 11               | 15             | <del> </del>    |  |

| Power Supply Current         | v-                                                                                       |                             | 21               | 35             | mA              |  |

| S <b></b>                    | Vcc                                                                                      |                             | 45               | 80             |                 |  |

| Power Dissipation            |                                                                                          |                             | 0.7              | 1.15           | w               |  |

| Operating Temperature Range  | AD578L,K,J                                                                               | 0                           |                  | +70            | °C              |  |

|                              | AD578S,T                                                                                 | -55                         |                  | +125           |                 |  |

| Logic Output Drive           | B <sub>1</sub> -B <sub>12</sub> , B <sub>1</sub> , CLOCK OUT                             |                             | 2                |                | LOTTI           |  |

|                              | SER OUT, SER OUT<br>EOC                                                                  | 1                           | 2<br>8           |                | LS TTL<br>Loads |  |

| Logic Input Load             | CLOCK IN, CONVERT START                                                                  |                             | 1                |                | Loads           |  |

|                              | Unipolar                                                                                 | Binary                      |                  |                | 1               |  |

| Parallel Output Code         | Bipolar                                                                                  |                             | ary/Two's Com    | olement        |                 |  |

| Serial Output Code           | Unipolar                                                                                 | Binary/Complementary Binary |                  |                |                 |  |

| SS SSIPAL GOOD               | Bipolar                                                                                  | Offset Bina                 | ary/Compleme     | ntary Offset B | inary           |  |

Note 1: Adjustable to zero.

1-108\_

Note 2:  $50\Omega$ , 1% resistor between pins 24 and 26.

Note 3:  $50\Omega$ , 1% resistor between pins 24 and 25.

Note 4: AD578ZXX models, V\* = +12V, V<sup>-</sup> + -12V Note 5: 'Z' models, V+ = 11.6V to 12.6V, V<sup>-</sup> = -11.6V to -12.6V

NIXIN

### High Speed 12 Bit A/D Converter

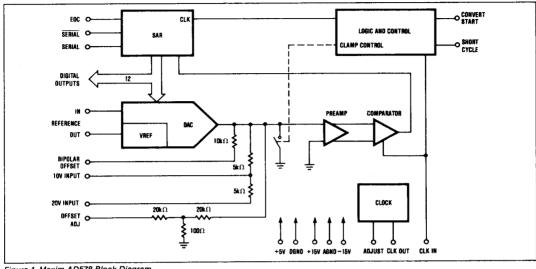

Figure 1, Maxim AD578 Block Diagram.

#### **Detailed Description**

The AD578 is a 12-bit successive approximation A/D converter in which the analog input is compared to the output of a high speed D/A converter (Figure 1). The D/A is binarily stepped until its output matches the analog input. The digital code from the successive approximation register (SAR) appears on the outputs as the binary value of the input voltage. The conversion processs consists of twelve successive tests, starting with the D/A set to half Full Scale (FS). The comparator determines whether the D/A output is higher or lower than the analog input and either sets or resets Bit 1 (MSB). On the next test, the D/A is incremented up or down ¼ FS, based on the last decision, and is again compared to the input. The result is stored as BIT 2. Each comparator decision is clocked into the SAR for the remaining bits until all twelve have been tested.

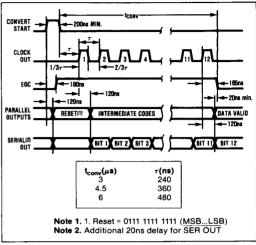

A positive going pulse on Convert Start resets the D/A Converter to ½ FS and sets the End-Of-Convert (EOC) high indicating that a conversion is in progress (Figure 7). The internal clock is enabled and the conversion begins on the trailing edge of the Start Convert (S) pulse. After the last bit has been tested, EOC goes LOW indicating that the output data is valid.

#### **Calibration Procedure**

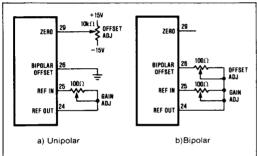

For a large number of AD578 applications no user calibration is needed. The performance limits for an uncalibrated device are given in the Electrical Characteristics section. If more precision is required then offset and gain adjustments can be made as follows.

**Table 1. Calibration Chart**

|                              |                    | ANALOG INPUT VOLTAGE |                    |                     | OUTPUT CODE(1) |      |  |

|------------------------------|--------------------|----------------------|--------------------|---------------------|----------------|------|--|

|                              | 0 TO +10V          | 0 TO +20V            | -5 TO +5V          | -10 TO +10V         | MSB            | LSB  |  |

| +FS -1LSB<br>+FS -1½LSB      | +9.9976<br>+9.9964 | +19.9951<br>+19.9927 | +4.9976<br>+4.9964 | +9.9951<br>+9.9927  | 1111 1111      | 1111 |  |

| Mid Scale +½LSB<br>Mid Scale | +5.0012<br>+5.0000 | +10.0024<br>+10.0000 | +0.0012<br>+0.0000 | +0.0024<br>+0.0000  | 1000 0000      |      |  |

| -FS +1/2LSB<br>-FS           | +0.0012<br>+0.0000 | +0.0024<br>+0.0000   | -4.9988<br>-5.0000 | -9.9976<br>-10.0000 | 0000 0000      |      |  |

Note 1: The symbol "@" indicates a 0 or 1 with equal probability.

1-109

### High Speed 12 Bit A/D Converter

Keeping in mind that the offset must always be adjusted before the gain, set the system into a mode of continuous conversions with a high repetition rate (>1kHz) while monitoring the output data lines using an oscilloscope, logic analyzer triggered on EOC, or LED's driven by latched data outputs clocked by EOC. Using a DVM, set the input voltage 1/2 LSB above -Full Scale (-FS) for the appropriate range (Table 1). Adjust the offset potentiometer (Figure 2) so that the LSB (B<sub>12</sub>) alternates between a "0" and "1" with a 50% duty cycle with all the other bits OFF. Using LED's, the LSB will appear at half intensity. The gain is similarly set by applying a voltage of +FS -1½LSB (Table 1) and adjusting the LSB for the same 50% ON condition with the exception that all the other bits are ON.

In bipolar mode, it is often desired to calibrate the bipolar zero condition at mid scale rather than the -FS offset. In this case set the input to MID SCALE +1/2LSB and adjust the LSB for 50% duty cycle with all bits off except B1 (MSB).

Figure 2. Unipolar and Bipolar Calibration Circuit.

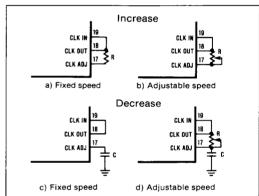

## c) Fixed speed Figure 5. Adjusting the Internal Clock. CLOCK ADJUST CAPACITANCE vs. CONVERSION TIME CLOCK ADJUST RESISTANCE vs. CONVERSION TIME 1000 900 ann 700

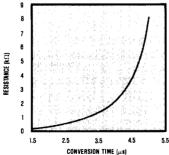

Figure 3. Speed vs. Resistance.

#### **Clock Adlust**

The internal clock on all grades is set for a nominal 5.8 us with tolerance of about +0.2 us with no external components connected to pin 17. To obtain 3.0 µs for the L grade, connect an 825Ω resistor as shown in Figure 5(a). For K and T grades, use a  $3.3k\Omega$  resistor for 4.5 \u03c4s. For J and S grades, it is recommended that no adjustment be made unless exactly 6.0 µs is required.

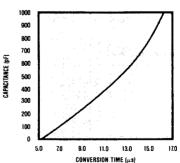

For faster conversion speeds, connect a resistor chosen from Figure 3 between pins 17 and 18. For slower conversions, connect a capacitor, Figure 4, from pin 17 to GND. A combination of both resistor and capacitor maybe used particularly for fine adjustment of slow clock settings (Figure 5).

Figure 4. Speed vs. Capacitance.

/VI/XI/VI

1-110\_

## High Speed 12 Bit

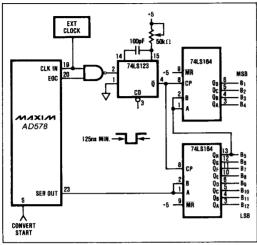

Figure 6. Serial Output with External Clock.

#### Short Cycle

For conversions of less than 12 bits, SHORT CYCLE, pin 14, must be connected to the next higher bit than the desired resolution. For example, connecting pin 14 to pin 2 will result in 10 bit conversions. When using an external clock, EOC must also be used to inhibit the CLK IN.

#### External Clock

The external clock can be used for synchronous applications, such as clocking the serial output data into a serial-to-parallel shift register (Figure 6). The clock should have a duty cycle between 30% and 70%. The main advantage of serial transmission is the reduction in the number of output lines from 12 to 1, which is particularly useful when using optical couplers or sending data over long distances.

## Application Hints Lavout

The Analog and Digital Grounds should be directly connected together as close as possible to the package and then tied to a quiet analog ground with no switching transients taking place during the conversion. A ground plane works best, but is not necessary if large traces are used. It is advisable to filter the supplies with  $10\mu$  electrolytic capacitors on the PC board along with  $0.1\mu$  bypassing capacitors as close to the supply pins on the AD578 as possible. Above all, separate the analog circuit connections, pins 24 through 32, away from the digital section. If a digital signal must cross an analog connection, make sure it crosses at a ninety degree angle on different sides of the board if at all possible.

Figure 7. Timing Diagram.

If using only the 20V input range, leave the 10V input (pin 27) completely unconnected since capacitance on this high impedance point can degrade dynamic performance. When relays or switches are used, mount them as close to the input pins as possible.

Although not necessary to achieve rated specifications, it is recommended that a  $10\mu F$  electrolytic capacitor be connected on REF OUT to GND for improved noise on the code transitions.

#### Interfacing

The digital outputs of the AD578 should be latched since they are constantly changing during the conversion. Edge triggered, rather than transparent latches are preferred, such as the 74LS574 (Figure 8), to prevent changing data lines feeding back into the analog portions of the A/D converter. Capacitive loading above 30pF as well as connections more than a few inches long should be avoided on the digital outputs of the A/D.

#### Input Signal Conditioning

The analog input should be driven by a wide bandwidth, low output impedance op amp or a fast sample-hold. Although  $V_{\rm IN}$  may not change during the conversion, the load current of the A/D abruptly changes with each clock cycle due to successive DAC codes (Figure 1). The amplifier must recover to the original value in time for the rest of the circuit to settle before the comparator can make a decision. An op amp which can settle to 0.01% in 50 to 100ns for a 0.5mA change in load current with no thermal tail and low offset voltage drift is recommended.

# High Speed 12 Bit A/D Converter

Figure 8. Typical Application for Unipolar 0-10V Range.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.