MC13001XP MC13002XP

# **Advance Information**

P.O. BOX 20912 • PHOENIX, ARIZONA 85036

### MONOMAX BLACK-AND-WHITE TV SUBSYSTEM

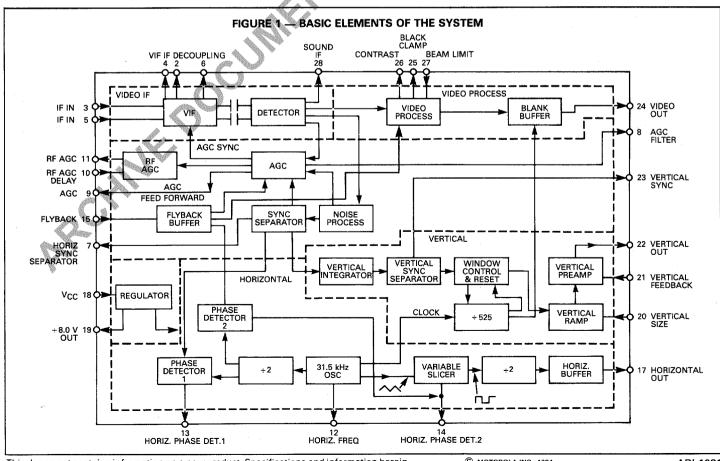

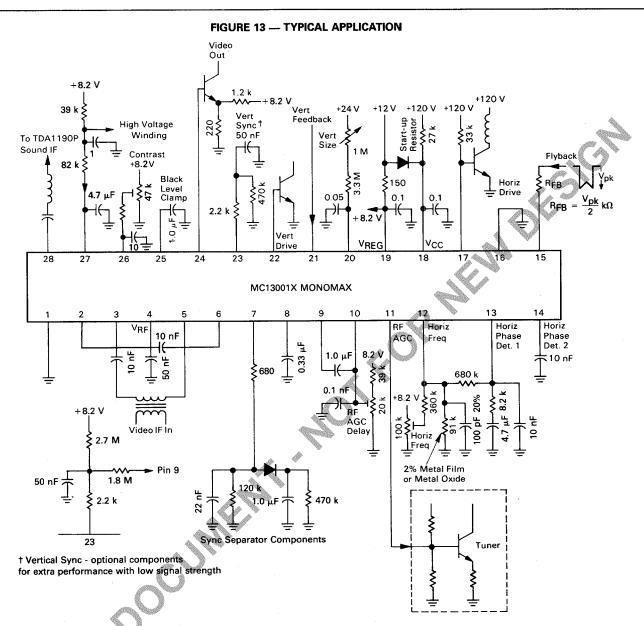

The MONOMAX is a single-chip IC that will perform the electronic functions of a monochrome TV receiver, with the exception of the tuner, sound channel, and power output stages. The MC13001XP and MC13002XP will function as drop-in replacements for MC13001P and MC13002P, but some external IF components can be removed for maximum benefit. IF AGC range has been increased, video output impedance lowered, and horizontal driver output current capability increased.

- Full Performance Monochrome Receiver with Noise and Video Processing — Black Level Clamp, DC Contrast, Beam Limiter

- Video IF Detection on Chip No Coils, No Pins, except Inputs

- Noise Filtering on Chip Minimum Pins and Externals

- Oscillator Components on Chip No Precision Capacitors Required

- MC13001XP for 525 Line NTSC and MC13002XP for 625 Line CCIR

- Low Dissipation in All Circuit Sections

- High-Performance Vertical Countdown

- 2-Loop Horizontal System with Low Power Start-Up Mode

- Noise Protected Sync and Gated AGC System

- Designed to work with TDA1190P or TDA3190P Sound IF and Audio Output Devices

- Reverse RF AGC Types are Available: MC13008XP, MC13009XP

MONOMAX BLACK-AND-WHITE TV SUBSYSTEM

SILICON MONOLITHIC INTEGRATED CIRCUITS

P SUFFIX PLASTIC PACKAGE CASE 710-02

# MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise noted)

| Rating                               | Symbol            | Value       | Unit  |

|--------------------------------------|-------------------|-------------|-------|

| Power Supply Voltage — Pin 18        | Vcc               | +16         | Vdc   |

| Power Dissipation                    | P <sub>D</sub>    | 1.0         | Watts |

| Horizontal Driver Current — Pin 17   | IHOR              | -20         | mA    |

| RF AGC Current — Pin 11              | IRFAGC            | 20          | mA    |

| Video Detector Current — Pin 24      | IVID              | 5.0         | mA    |

| Vertical Driver Current — Pin 22     | VERT              | 5.0         | mA    |

| Auxiliary Regulator Current — Pin 19 | IREG              | 35          | mA    |

| Thermal Resistance Junction-to-Case  | R <sub>Ø</sub> JC | 60          | °C/W  |

| Maximum Junction Temperature         | TJ                | 150         | °C    |

| Storage Temperature Range            | T <sub>stg</sub>  | -65 to +150 | °C    |

### **RECOMMENDED OPERATING CONDITIONS**

| Rating                          | Symbol | Value | Unit |

|---------------------------------|--------|-------|------|

| Horizontal Output Drive Current | HOR    | ≤10   | mA   |

| RF AGC Current                  | IRFAGC | ≤10   | mA   |

| Regulator Current               | IREG   | ≤20   | mA   |

# ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 11.3 V, T<sub>A</sub> = 25°C)

| Characteristics      |              | Symbol           | Min | Тур | Max | Unit |

|----------------------|--------------|------------------|-----|-----|-----|------|

| Power Supply Current | Pins 18 & 19 | Icc              | 44  | _   | 76  | mA   |

| Regulator Voltage    | Pin 19       | V <sub>REG</sub> | 7.2 | 8.2 | 8.8 | Vdc  |

## **HORIZONTAL SPECIFICATIONS**

| Oscillator Frequency (Nominal) Pin 12                                             | fHOR(NOM)             | 13           |                                | 19   | kHz   |

|-----------------------------------------------------------------------------------|-----------------------|--------------|--------------------------------|------|-------|

| Oscillator Sensitivity                                                            | A                     | _            | 230                            |      | Hz/μA |

| Start-Up Frequency<br>(I <sub>18</sub> = 4.0 mA)                                  | fHOR                  | <b>– 10</b>  |                                | + 10 | %     |

| Oscillator Temperature Stability<br>(0 ≤ TA ≤ 75°C)                               | fHOR                  | _            | 50                             | _    | Hz    |

| Phase Detector 1 (Charge/Discharge Current) (Non Standard Frame) (Standard Frame) | l <b>φ</b> 1          |              | ± 900<br>± 400                 |      | μΑ    |

| Phase Detector 1<br>(Output Voltage Limits)                                       | $v_{\phi^1}$          | <del>.</del> | 7.5 (Max)<br>2.5 (Min)         |      | Vdc   |

| Phase Detector 1<br>(Leakage Current)                                             |                       |              |                                | 2.0  | μΑ    |

| Phase Detector 2<br>(Charge/Discharge Current)                                    | $I_{\phi 2}$          |              | + 1.0<br>- 0.6                 |      | mA    |

| Phase Detector 2<br>(Output Voltage Limits)                                       | $V_{\phi2}$           |              | 7.7 (Max)<br>1.5 (Min)         |      | Vdc   |

| Phase Detector 2<br>(Leakage Current)                                             |                       | _            |                                | 3.0  | μΑ    |

| Horizontal Delay Range<br>(Sync to Flyback)                                       |                       |              | 18 (Max)<br>5.0 ( <b>M</b> in) |      | μs    |

| Horizontal Output Saturation Voltage (I <sub>17</sub> = 15 mA)                    | V <sub>17</sub> (SAT) | _            | _                              | 0.3  | Vdc   |

| Phase Detector 1 (Gain Constant)<br>(Out-of-Lock)<br>(In-Lock)                    | ·                     | _            | 5.0<br>10                      | _    | μA/μs |

| Horizontal Pull-In Range                                                          |                       | ± 500        | ±750                           |      | Hz    |

| Characteristics                                                         |                         | Symbol                             | Min          | Тур        | Max           | Unit              |

|-------------------------------------------------------------------------|-------------------------|------------------------------------|--------------|------------|---------------|-------------------|

| Output Current                                                          | Pin 22                  | 122                                | -0.6         |            | _             | mA                |

| Feedback Leakage Current                                                | Pin 21                  | l <sub>21</sub>                    |              |            | 6.0           | μΑ                |

| Ramp Retrace Current                                                    | Pin 20                  | l <sub>20</sub>                    | 500          | _          | 900           | μΑ                |

| Ramp Leakage Current                                                    | Pin 20                  |                                    |              |            | 0.3           | μΑ                |

| Feedback Maximum Voltage                                                |                         | V <sub>21</sub>                    | _            | 5.1        | _             | Vdc               |

| IF SPECIFICATIONS                                                       |                         |                                    |              |            | 4             | $T(G)^{*}$        |

| Regulator Voltage                                                       |                         | V <sub>4</sub>                     | _            | 7.5        | — <i>(</i> 2) | Vdc               |

| Input Bias Voltage                                                      |                         | V <sub>2,6</sub>                   | _            | 4.2        | 1             | Vdc               |

| Input Resistance Input Capacitance (VAGC Pin 8 = 4.0 V)                 |                         | R <sub>IN</sub><br>C <sub>IN</sub> |              | 6.0<br>2.0 |               | kΩ<br>pF          |

| Sensitivity<br>(V <sub>8</sub> = 0 V, 400 Hz 30% MOD, V <sub>28</sub> = | = 0.8 V <sub>pp</sub> ) |                                    | _            | 80         | <u> </u>      | <sup>μV</sup> RMS |

| Bandwidth                                                               |                         |                                    | _            | 75         | _             | MHz               |

| VIDEO SPECIFICATIONS                                                    |                         |                                    |              |            |               |                   |

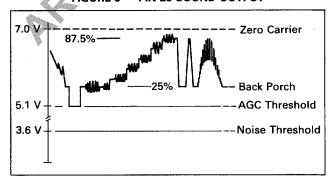

| Zero Carrier Voltage (See Figure 5)                                     | Pin 28                  |                                    | - (          | 7.0        |               | Vdc               |

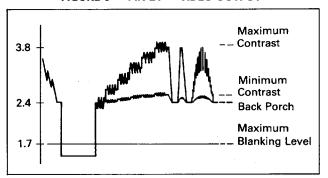

| Output Voltage (See Figure 6) White to Back Porch                       | Pin 24                  |                                    |              | 1.4        |               | ٧                 |

| Differential Gain<br>Differential Phase<br>(IRE Test Method)            |                         |                                    | <del>-</del> | 6<br>4     |               | %<br>Degrees      |

| Contrast Bias Current                                                   | Pin 26                  | 126                                | _            | 10         | _             | μΑ                |

| Contrast Control Range                                                  |                         | A 4                                | _            | 14:1       |               |                   |

| Beam Limiting Voltage                                                   | Pin 27                  | V <sub>27</sub>                    | _            | 1.0        | _             | Vdc               |

| AGC & SYNC                                                              |                         |                                    |              |            |               |                   |

| R.F. (Tuner) AGC Output Current (V <sub>11</sub> = 5.5 V)               |                         | 111                                | 5.0          |            | _             | mA                |

| AGC Delay Bias Current                                                  |                         | <sup> </sup> 10                    |              | <b>-10</b> |               | μΑ                |

| AGC Feedforward Current                                                 |                         | lg                                 | _            | 1.0        | _             | mA                |

| AGC Threshold<br>(Sync Tip at Pin 28)                                   |                         | V <sub>28</sub>                    | 4.7          | -          | 5.1           | Vdc               |

| Sync Separator Operating Point                                          |                         | V <sub>7</sub>                     | _            | 4.2        |               | Vdc               |

17

# FIGURE 2 — MONOMAX AGC CHARACTERISTICS

Sync Separator Charge Current

# 10 4.0 (qg) 4.0 (xg) 4.0 (xg)

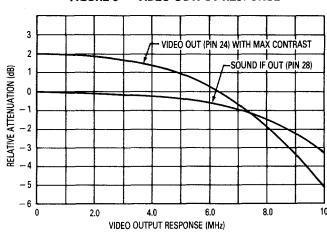

# FIGURE 3 — VIDEO OUTPUT RESPONSE

**MOTOROLA** Semiconductor Products Inc.

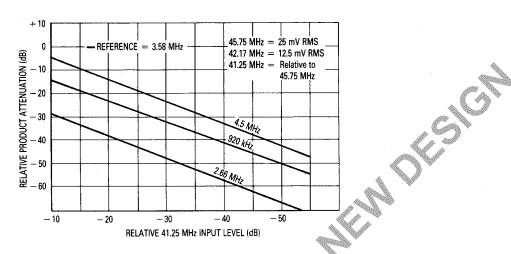

FIGURE 4 — DETECTOR PRODUCTS

### **GENERAL DESCRIPTION**

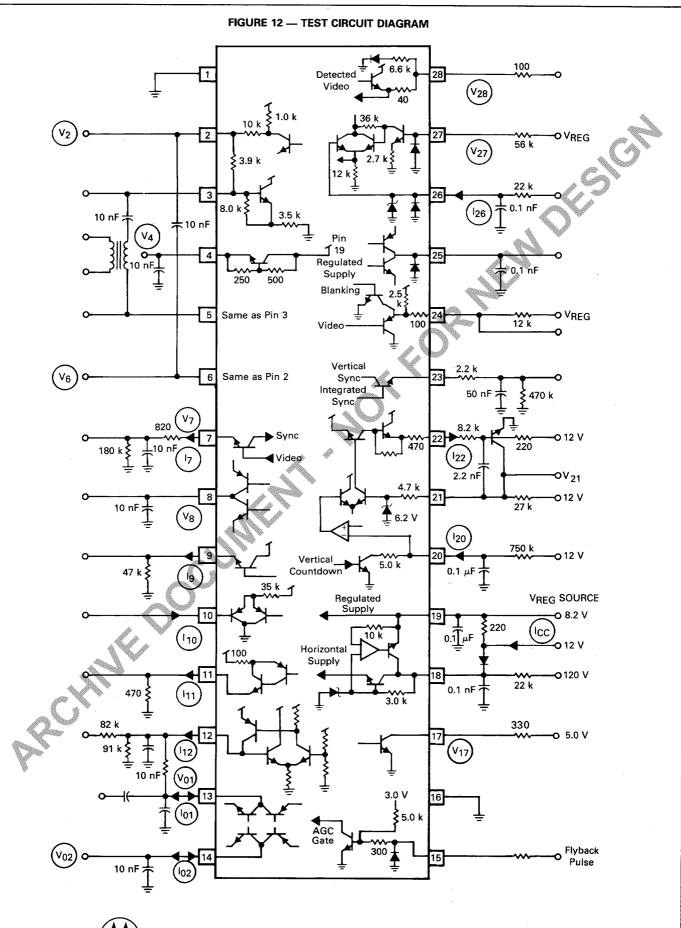

The Video IF Amplifier is a four-stage design with 80  $\mu$ V sensitivity. It uses a 6.2 V supply decoupled at Pin 4. The first two stages are gain controlled, and to ensure optimum noise performance, the first stage control is delayed until the second stage has been gain reduced by 15 dB. To bias the amplifier, balanced dc feedback is used which is decoupled at Pins 2 and 6 and then fed to the input Pins 3 and 5 by internal 3.9 k resistors. The nominal bias voltage at these input pins is approximately 4.2 Vdc. The input, because of the high IF gain, should be driven from a balanced differential source. For the same reason, care must be taken with the IF decoupling.

The IF output is rectified in a full wave envelope detector and detector nonlinearity is compensated by using a similar nonlinear element in a feedback output buffer amplifier. The detected 1.9 V<sub>p-p</sub> video at Pin 28 contains the sound intercarrier signal, and Pin 28 is normally used as the sound takeoff point. The video frequency response, detector to Pin 28, is shown in Figure 3 and the detector intermodulation performance can be seen by reference to Figure 4. Typical Pin 28 video waveforms and voltage levels are shown in Figure 5.

The video processing section of Monomax contains a contrast control, black level clamp, a beam current

limiter and composite blanking. The video signal first passes through the contrast control. This has a range of 14:1 for a 0 V to 5.0 V change of voltage on Pin 26, which corresponds to a change of video amplitude at Pin 24 of 1.4 V to 0.1 V (black to white level). The beam current limiter operates on the contrast control, reducing the video signal when the beam current exceeds the limit set by external components. As the beam current increases, the voltage at Pin 27 moves negatively from its normal value of 1.5 V, and at 1.0 V operates the contrast control, thus initiating beam limiting action. After the contrast control, the video is passed through a buffer amplifier and dc restored by the black level clamp circuit before being fed to Pin 24 where it is blanked. The black level clamp, which is gated "on" during the second half of the flyback, maintains the video black level at 2.4 V ± 0.1 V under all conditions, including changes in contrast, temperature and power supply. The loop integrating capacitor is at Pin 25 and is normally at a voltage of 3.3 V. The frequency response of the video at Pin 24 is shown in Figure 3 and it is blanked to within 0.5 V of ground.

The AGC loop is a gated system, and for all normal variations of the IF input signal maintains the sync tip of a noise filtered video signal at a reference voltage

FIGURE 5 — PIN 28 SOUND OUTPUT

FIGURE 6 — PIN 24 — VIDEO OUTPUT

(5.1 V Pin 28). The strobe for the AGC error amplifier is formed by gating together the flyback pulse with the separated sync pulse. Integration of the error signal is performed by the capacitor at Pin 8, which forms the dominant AGC time constant. Improved noise performance is obtained by the use of a gated AGC system, noise protected by a dc coupled noise canceling circuit. The false AGC lock conditions, which can result from this combination, are prevented by an anti lockout circuit connected to the sync separator at Pin 7. AGC lockout conditions, which occur due to large rapid changes of signal level are detected at Pin 7 and recovery is ensured under these conditions by changing the AGC into a mean level system. The voltage at Pin 10 sets the point at which tuner AGC takeover occurs and positive going tuner control, suitable for an NPN RF transistor, is available at Pin 11. The maximum output is 5.5 V at 5.0 mA. A feed-forward output is provided at Pin 9. This enables the AGC control voltage to be ac coupled into the tuner takeover control at Pin 10. The coupling allows additional IF gain reduction during signal transient conditions, thus compensating for variations of AGC loop gain at the tuner AGC takeover point. In this way the AGC system stability and response are not degraded.

The previously mentioned noise protection is effected by detecting negative-going noise spikes at the video detector output. A dc coupled detector is used which turns on when a noise spike exceeds the video sync tip by 1.4 V. This pulse is then stretched and used to cancel the noise present on the delayed video at the input to the sync separator. Cancellation is performed by blanking the video to ground. Complete cancellation of the noise spike results from the stretching of the blanking pulse and the delay of the noise spike at the input to the sync separator. Protection of both the horizontal PLL and the AGC stems from the fact that both circuits use the noise cancelled sync for gating.

The composite sync is stripped from a delayed and filtered video in a peak detecting type of sync separator. The components connected to Pin 7 determine the slice and tilt levels of the sync separator. For ideal horizontal sync separation and to ensure correct operation of AGC anti-lockup circuit, a relatively short time constant is required at Pin 7. This time constant is less than optimum for good noise free vertical separation, giving rise to a vertical slice level near sync tip. An additional, longer, time-constant is therefore coupled to the first via a diode. With the correct choice of time constants, the diode is non conducting during the horizontal sync period, but conducts during the longer vertical period. This connects the longer time constant to the sync separator for the vertical period and stops the slice level from moving up to the sync tip. The separated composite sync is integrated internally, and the time constant is such that only the longer period vertical pulses produce a significant output pulse. The output is then fed to the vertical sync separator, which further processes the vertical pulse and provides increased noise protection. The selection of the external components connected to the vertical separator at Pin 23 permits a wide range of performance options. A simple resistor divider from the 8.2 V regulated supply gives adequate performance for most conditions. The addition of an RC network will make the slice level adapt to varying sync amplitude and give improved weak signal performance. A resistor to the AGC voltage on Pin 9 enables the sync slice level to be changed as a function of signal level. This further improves the low signal level separation while at the same time giving increased impulse noise protection on strong signals.

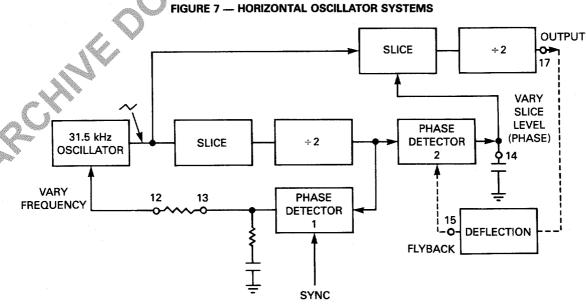

### HORIZONTAL OSCILLATOR

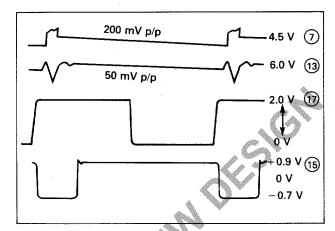

The horizontal PLL (see Figure 7) is a 2-loop system using a 31.5 kHz oscillator which after a divider stage is locked to the sync pulse using phase detector 1. The control signal derived from this phase detector on Pin 13 is fed via a high-value resistor to the frequencycontrol point on Pin 12. The same divided oscillator

frequency is also fed to phase detector 2, where the flyback pulse is compared with it and the resulting error used to change a variable slice level on the oscillator ramp waveform. This therefore changes the timing of the output square wave from the slicer and hence the timing of the buffered horizontal output on Pin 17 (see Figure 8). The error on phase detector 2 is reduced until the phasing of the flyback pulse is correct with respect to the divided oscillator waveform, and hence with respect to the sync pulse.

To improve the pull-in and noise characteristics of the first PLL, the phase detector current is increased when the vertical lock indicator signals an unlocked condition and is decreased when locked. This increases the loop bandwidth and pull-in range when out of lock and decreases the loop bandwidth when in lock, thus improving the noise performance. In addition, the phase detector current during the vertical period is reduced in order to minimize the disturbance to the horizontal caused by the longer period vertical phase detector pulses.

The oscillator itself is a novel design using an on-chip 50 pF silicon nitride capacitor which has a temperature drift of only 70 ppm/°C and negligible long term drift. This, in conjunction with an external resistor, gives a drift of horizontal frequency of less than 1Hz/°C — i.e., less than 100 Hz over the full operating temperature range of the chip. The pull-in range of the PLL is about ± 750 Hz, so normally this would eliminate the need for any customer adjustment of the frequency.

The second significant feature of this design is the use of a virtual ground at the frequency control point which floats at a potential derived from a divider across the power supply and this is the same divider which determines the end-points of the oscillator ramp. The frequency adjustment which is necessary to take up tolerances in the on-chip capacitor is fed in as a current to this virtual ground and when this adjustment current is derived from an external potentiometer across the same supply there is no frequency variation with supply voltage. Moreover, using the voltage from a potentiometer for the adjustment instead of the simple variable resistor normally used in RC oscillators makes the frequency independent of the value of the potentiometer and hence its temperature coefficient. The frequency control current from the first phase detector is fed into this same virtual ground and as the sensitivity of the control is about 230 Hz/ $\mu$ A a high value resistor can be used (680 k $\Omega$ ) and this can be directly connected to the phase detector filter without significant loading.

This oscillator operates with almost constant frequency to below 4.0 volts and as the total PLL system consumes less than 4.0 mA at this voltage, this gives an ideal start-up characteristic for receivers using deflection-derived power supplies.

The flyback gating input is on Pin 15 which is internally clamped to 0.7 V in both directions and requires a negative input current of 0.6 mA to operate the gate circuit. This input can be a raw flyback pulse simply fed via a suitable resistor.

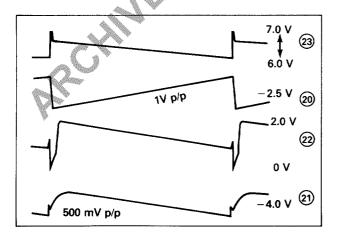

### FIGURE 8 — HORIZONTAL WAVEFORMS

### **VERTICAL SYSTEM**

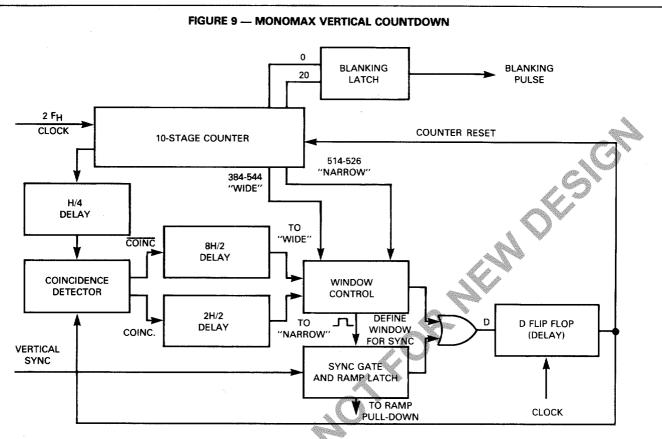

An output switching signal is taken from the 31.5 kHz oscillator to clock the vertical counter which is used in place of a conventional vertical oscillator circuit. The counter is reset by the vertical sync pulse but the period during which it is permitted to reset is controlled by the window control. Normally, when the counter is running synchronously, the window is narrow to give some protection against spurious noise pulses in the sync signal. If the counter output is not coincident with sync however, after a short period the window opens to give reset over a much wider count range, leading to a fast picture roll towards lock. At weak signal, i.e., less than 200  $\mu$ V IF input, the vertical system is forced to narrow mode to give a steadier picture for commonly occurring types of noise. The vertical sync, gated by the counter, then resets a ramp generator on Pin 20 and the 1.5 volt p-p ramp is buffered to Pin 22 by the vertical preamplifier. A differential input to the preamp on Pin 21 compares the signal generated across the resistor in series with the deflection coils with the generated ramp and thus controls shape and amplitude of the coil current.

The basic block diagram of the countdown system is shown in Figure 9. The 31.5 kHz (2 FH) clock from the horizontal oscillator drives a 10-stage counter circuit which is normally reset by the vertical sync pulse via the sync gate, OR gate and D flip-flop. This D input is also used to initiate discharge of the ramp capacitor and hence causes picture flyback.

The period during which sync can reset the counter and cause flyback is determined by the window control which defines a count range during which the gate is open. One of two ranges is selected according to the condition of the signal. The normal "narrow" range is 514 to 526 counts for a 525 line system and is selected after the coincidence detector indicates that the reset is coincident, twice in succession, with the 525 count from the counter. When the detector indicates non-coincidence 8 times in succession, then the window control switches to the "wide" mode (384 to 544 counts) to achieve rapid re-synchronization. For the 625 line version the counts are 614 to 626 for narrow mode and

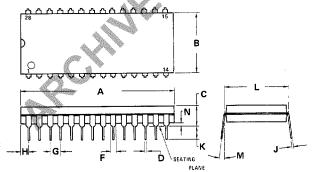

### **OUTLINE DIMENSIONS**

### NOTES:

- 1. POSITIONAL TOLERANCE OF LEADS (D), SHALL BE WITHIN 0.25mm(0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

- 2. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- 3. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

| ~ | CE | 71 | Λ. | <b>02</b> |

|---|----|----|----|-----------|

|     | MILLIMETERS |       | INC       | HES   |  |

|-----|-------------|-------|-----------|-------|--|

| DIM | MIN MAX     |       | MIN       | MAX   |  |

| Α   | 36.45       | 37.21 | 1.435     | 1.465 |  |

| В   | 13.72       | 14.22 | 0.540     | 0.560 |  |

| C   | 3.94        | 5.08  | 0.155     | 0.200 |  |

| D   | 0.36        | 0.56  | 0.014     | 0.022 |  |

| F   | 1.02        | 1.52  | 0.040     | 0.060 |  |

| G   | 2.54 BSC    |       | 0.100 BSC |       |  |

| Н   | 1.65        | 2.16  | 0.065     | 0.085 |  |

| J   | 0.20        | 0.38  | 0.008     | 0.015 |  |

| К   | 2.92        | 3.43  | 0.115     | 0.135 |  |

| L   | 15.24 BSC   |       | 0.600     | BSC   |  |

| M   | 00          | 15°   | 00        | 150   |  |

| N   | 0.51        | 1.02  | 0.020     | 0.040 |  |

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity/ Affirmative Action Employer.

MOTOROLA Semiconductor Products Inc.

484 to 644 for wide mode. Note that the OR gate after the sync gate is used to terminate the count at the end of the respective window if a sync pulse has not appeared.

This method accepts non-standard signals almost in the same way as a conventional triggered RC oscillator and has a similar fast lock-in time. However, the use of a window control on the counter reset ensures that when locked with a normal standard broadcast signal the counter will reject most spurious noise pulses.

The blanking output is provided from a latch which is set by the counter reset pulse and terminated by count 20 from the counter chain.

FIGURE 10 - VERTICAL WAVEFORMS

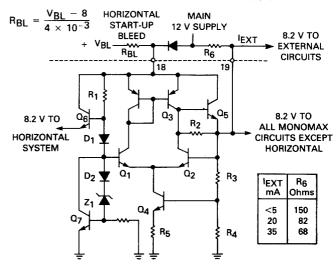

### **POWER SUPPLY**

The power supply regulator, although of simple design, provides two independent power supplies — one for the horizontal PLL section and the other for the remainder of the chip. The supplies share the same reference voltage but the design of the main regulator is such that it can be switched on independently to give minimum loading on the "bleed" voltage source during start-up phase of a deflection-derived supply system.

### FIGURE 11 - POWER SUPPLY CIRCUIT

**MOTOROLA** Semiconductor Products Inc.

ARCHINE DOCUMENT FRONT FOR A STATE OF THE PROPERTY OF THE PROP

**MOTOROLA** Semiconductor Products Inc.

BOX 20912 ● PHOENIX, ARIZONA 85036 ● A SUBSIDIARY OF MOTOROLA INC.