# **DUAL-GATE UNIDIRECTIONAL OVERVOLTAGE PROTECTOR**

# TISP83121D Unidirectional P & N-Gate Protector

Overvoltage Protection for Dual-Voltage Ringing SLICs

- Programmable Protection Configurations up to ±100 V

- Typically 5 Lines Protected by: Two TISP83121D + Diode Steering Networks

### **High Surge Current**

- 150 A, 10/1000 μs

- **250 A, 10/700** μs

- 500 A, 8/20 μs

#### Pin Compatible with the LCP3121

- 50 % more surge current

- Functional Replacement in Diode Steering Applications

#### **Small Outline Surface Mount Package**

### **Description**

The TISP83121D is a dual-gate reverse-blocking unidirectional thyristor designed for the protection of dual-voltage ringing SLICs (Subscriber Line Interface Circuits) against overvoltages on the telephone line caused by lightning, a.c. power contact and induction.

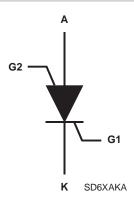

The device chip is a four-layer NPNP silicon thyristor structure which has an electrode connection to every layer. For negative overvoltage protection the TISP83121D is used in a common anode configuration with the voltage to be limited applied to the cathode (K) terminal and the negative reference potential applied to the gate 1 (G1) terminal. For positive overvoltage protection the TISP83121D is used in a common cathode configuration with the voltage to be limited applied to the anode (A) terminal and the positive reference potential applied to the gate 2 (G2) terminal.

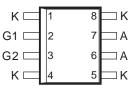

### 8-SOIC Package (Top View)

MD6XAYB

1

For operation at the rated current values connect pins 1, 4, 5 and 8 together.

### **Device Symbol**

The TISP83121D is a unidirectional protector and to prevent reverse bias, requires the use of a series diode between the protected line conductor and the protector. Further, the gate reference supply voltage requires an appropriately poled series diode to prevent the supply from

being shorted when the TISP83121D crowbars.

Under low level power cross conditions the TISP83121D gate current will charge the gate reference supply. If the reference supply cannot absorb the charging current its potential will increase, possibly to damaging levels. To avoid excessive voltage levels a clamp (zener or avalanche breakdown diode) may be added in shunt with the supply. Alternatively, a grounded collector emitter-follower may be used to reduce the charging current by the transistor's H<sub>FE</sub> value.

This monolithic protection device is made with an ion-implanted epitaxial-planar technology to give a consistent protection performance and be virtually transparent to the system in normal operation.

### **How To Order**

| Device             | Package                 | Carrier                  | Order as    |

|--------------------|-------------------------|--------------------------|-------------|

| TICD02121 D /0 pir | D (8-pin Small-Outline) | R (Embossed Tape Reeled) | TISP83121DR |

| 113503121          | b (o-pin Smail-Outline) | (Tube)                   | TISP83121D  |

# TISP83121D Unidirectional P & N-Gate Protector

# **BOURNS®**

### **Absolute Maximum Ratings**

| Rating                                                                                                                                         |                  | Value       | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|------|

| Repetitive peak off-state voltage, 0 °C to 70 °C                                                                                               | $V_{DRM}$        | 100         | V    |

| Non-repetitive peak on-state pulse current (see Notes 1 and 2)                                                                                 |                  |             |      |

| 10/1000 μs (GR-1089-CORE, open-circuit voltage wave shape 10/1000 μs) 5/310 μs (CCITT K20/21, open-circuit voltage wave shape 7 kV, 10/700 μs) |                  | 150         |      |

|                                                                                                                                                |                  | 250         | A    |

| 8/20 μs (ANSI C62.41, open-circuit voltage wave shape 1.2/50 μs)                                                                               |                  | 500         |      |

| Non-repetitive peak on-state current, 50 Hz, halfwave rectified sinewave, (see Notes 1 and 2)                                                  |                  |             |      |

| 100 ms                                                                                                                                         |                  | 22          |      |

| 1 s                                                                                                                                            |                  | 8           | Α    |

| 900 s                                                                                                                                          |                  | 3           |      |

| Junction temperature                                                                                                                           | T <sub>J</sub>   | -40 to +150 | °C   |

| Storage temperature range                                                                                                                      | T <sub>stg</sub> | -65 to +150 | °C   |

NOTES: 1. Initially the protector must be in thermal equilibrium with 0 °C < T<sub>J</sub> < 70 °C. The surge may be repeated after the device returns to its initial conditions. For operation at the rated current value, pins 1, 4, 5 and 8 must be connected together.

2. Above 70 °C, derate linearly to zero at 150 °C lead temperature.

## Electrical Characteristics, T<sub>J</sub> = 25 °C (Unless Otherwise Noted)

| Parameter        |                                         | Test Conditions                                                                                                                                       | Min      | Тур | Max  | Unit |

|------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|------|------|

| I <sub>D</sub>   | Off-state current                       | $V_{d} = 70 \text{ V}, I_{G} = 0$                                                                                                                     |          |     | 1    | μΑ   |

| I <sub>DRM</sub> | Repetitive peak off-<br>state current   | $V_d = V_{DRM} = 100 \text{ V}, I_G = 0, 0 ^{\circ}\text{C} \text{ to } 70 ^{\circ}\text{C}$                                                          |          |     | 10   | μА   |

| I <sub>H</sub>   | Holding current                         | $T_{J} = 0 \text{ to } 70 ^{\circ}\text{C}$ $I_{T} = 1 \text{ A, di/dt} = -1 \text{A/ms}$ $T_{J} = 25 ^{\circ}\text{C}$ $T_{J} = 70 ^{\circ}\text{C}$ | 90<br>60 |     | 300  | mA   |

| I <sub>R</sub>   | Reverse current                         | V <sub>R</sub> = 0.3 V                                                                                                                                |          |     | 1    | mA   |

| I <sub>G1T</sub> | Gate G1 trigger current                 | $I_T = +1 \text{ A}, t_{p(g)} = 20 \mu \text{s}$                                                                                                      |          |     | +200 | mA   |

| I <sub>G2T</sub> | Gate G2 trigger current                 | $I_T = +1 \text{ A, } t_{p(g)} = 20  \mu\text{s}$                                                                                                     |          |     | -180 | mA   |

| V <sub>G1T</sub> | G1-K trigger voltage                    | $I_T = +1 \text{ A}, t_{p(g)} = 20 \mu \text{s}$                                                                                                      |          |     | +1.8 | V    |

| V <sub>G2T</sub> | G2-A trigger voltage                    | $I_T = +1 \text{ A}, t_{p(g)} = 20 \mu \text{s}$                                                                                                      |          |     | -1.8 | V    |

| C <sub>AK</sub>  | Anode-cathode off-<br>state capacitance | $f = 1 \text{ MHz}, V_d = 1 \text{ V rms}, V_D = 5 \text{ V}, I_G = 0 \text{ (see Note 3)}$                                                           |          |     | 100  | pF   |

NOTE 3: These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The unmeasured device terminals are a.c. connected to the guard terminal of the bridge.

### **Thermal Characteristics**

|                 | Parameter                               | Test Conditions                                                                                               | Min | Тур | Max | Unit |

|-----------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $R_{\theta JA}$ | Junction to free air thermal resistance | T <sub>A</sub> = 25 °C, EIA/JESD51-3 PCB,<br>EIA/JESD51-2 environment, I <sub>T</sub> = I <sub>TSM(900)</sub> |     |     | 105 | °C/W |

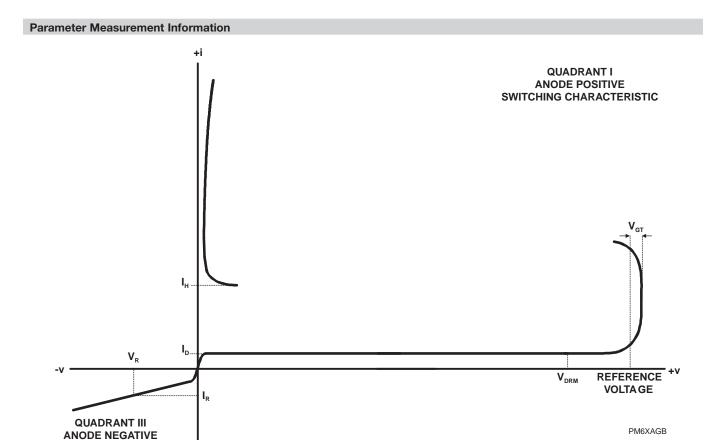

Figure 1. Voltage-Current Characteristic

REVERSE CHARACTERISTIC :

#### APPLICATIONS INFORMATION

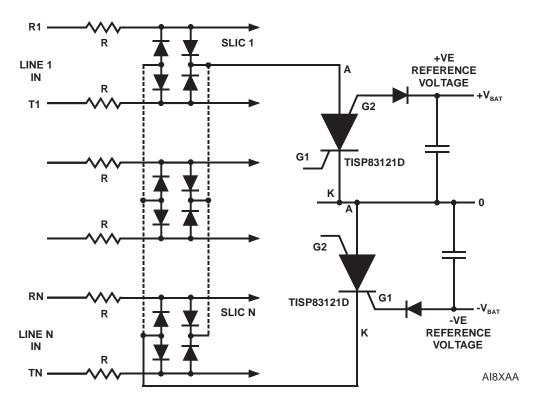

#### **Multiple Line Overvoltage Protection**

Figure 2 shows two TISP83121D devices protecting many lines. Line conductor positive overvoltage protection is given by the steering diode array connected to the anode of the upper TISP83121D and the TISP83121D itself. The TISP83121D gate reference voltage is the positive battery supply, +V<sub>BAT</sub>. The initial limiting voltage will be the sum of the voltages of the battery, the forward biased conductor diode, the gate trigger of the TISP83121D and the forward biased reference voltage blocking diode. Typically the conductor voltage will be initially limited at 2.5 V above the +V<sub>BAT</sub> value.

Figure 2. N Line Positive and Negative Overvoltage Protection

Line conductor negative overvoltage protection is given by the diode steering array connected to the cathode of the lower TISP83121D and the TISP83121D itself. The TISP83121D gate reference voltage is the negative battery supply, -V<sub>BAT</sub>. The initial limiting voltage will be the sum of the voltages of the battery, the forward biased conductor diode, the gate trigger of the TISP83121D and the forward biased reference voltage blocking diode. Typically the conductor voltage will be initially limited at 2.5 V below the -V<sub>BAT</sub> value.

When a TISP83121D crowbars and grounds all conductors of the appropriate polarity, the device current will be the sum of all the SLIC output currents. This will usually exceed the TISP83121D holding current. To switch off the TISP83121D and restore normal operation, the grounded condition of the SLIC output must be detected and the SLIC outputs turned off.

The 150 A rating of the TISP83121D allows a large number of lines to be protected against currents caused by lightning. For example, if a recommendation K.20 10/700 generator was connected to all lines, together with 350 V primary protection and a series conductor resistance (R) of 25  $\Omega$ , the maximum conductor current before the primary protection operated would be 350/25 = 14 A or 28 A per line. For a total return current of about 150 A the number of lines would be 150/28 = 5. At this current level, 5x28 = 140 A, the generator voltage would be 150/28 = 100 V. Another limitation is long term power cross. The long term power cross capability of the TISP83121D is 3 A peak or 2.1 A rms. If the line conductor overcurrent protection was given by a PTC thermistor which tripped at 0.2 A, the maximum number of conductors becomes 2.1/0.2 = 10 or 5 lines.

# TISP83121D Unidirectional P & N-Gate Protector

# BOURNS®

### **Battery Supply Impedance**

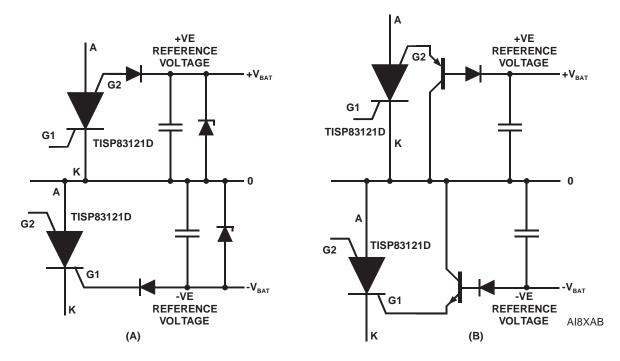

In many designs, the battery supply voltages are generated by switching mode power supplies. This type of power supply cannot be charged like a battery. Feeding a charging current to a switching mode power supply will usually cause the supply to stop switching and the voltage to rise. The gate current of the TISP83121D is a charging current for the supply. To avoid the supply voltage from rising and damaging the connected SLICs, an avalanche diode voltage clamp can be connected across the supply (Figure 3. (A)).

Another approach is to reduce the gate charging current for the supply by a transistor buffer (Figure 3. (B)). If the transistor gain was 50, a 200 mA gate current would be reduced to a supply charging current of 200/50 = 4 mA. In both cases, the dissipation in the control devices can be substantial and power capability needs to be taken into account in device selection.

Figure 3. Reference Voltage Control by (A) Breakdown Diodes or (B) by Transistor Buffers