# **Datasheet**

# SCA620-EF1V1B SINGLE AXIS ACCELEROMETER WITH ANALOG **INTERFACE**

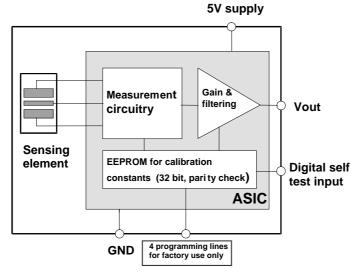

The SCA620 accelerometer consists of a silicon bulk micro machined sensing element chip and a signal conditioning ASIC. The chips are mounted on a pre-molded package and wire bonded to appropriate contacts. The sensing element and ASIC are protected with silicone gel and lid. The sensor has 8 SMD legs (Gull-wing type).

#### **Features**

- Single +5 V supply

- Current consumption 2.5 mA typical

- Ratiometric output in relation to supply voltage (Vdd = 4.75 V...5.25 V)

- Enhanced failure detection features

- Digitally activated, true self-test by proof mass deflection using electrostatic force

- Memory parity check during power up, and self-test cycle.

- Built in connection failure detection

- Digitally activated, true self-test by proof mass deflection using electrostatic force

- Wide load drive capability (max. 20 nF)

- True DC response

- Qualified according to AEC-Q100 standard

### **Applications**

SCA620 product family is targeted to automotive applications with high stability and reliability requirements. Typical applications include:

- Electronic Stability Control (ESC)

- **Engine Vibration Measurement**

- Roll Over

- Suspension

- Inclination

Figure 1. Functional block diagram.

## **Table of Contents**

| SCA                                          | .620-EF1V1B single axis accelerometer with analog interface                                                                                                               |                  | 1  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----|

| Appl                                         | JRESCATIONSE OF CONTENTS                                                                                                                                                  | 1                |    |

| 1.                                           | Electrical Specifications                                                                                                                                                 |                  | 3  |

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6. | ABSOLUTE MAXIMUM RATINGS.  PERFORMANCE CHARACTERISTICS  OFFSET ANS SENSITIVITY CALIBRATION.  ERROR CALCULATIONS  SUPPLY VOLTAGE.  ELECTRICAL CONNECTION  LIMITER FUNCTION | 3<br>4<br>5<br>6 |    |

| 2.                                           | Functional Description                                                                                                                                                    |                  | 8  |

| 2.1.<br>2.2.<br>2.3.<br>2.4.                 | MEASURING DIRECTIONS                                                                                                                                                      | 8<br>8           |    |

| 3.                                           | Mechanical Specification                                                                                                                                                  |                  | 10 |

| 3.1.                                         | DIMENSIONS                                                                                                                                                                | 10               |    |

| 4.                                           | Application information                                                                                                                                                   |                  | 11 |

| 4.1.                                         | RECOMMENDED PCB LAY-OUT                                                                                                                                                   |                  |    |

# 1. Electrical Specifications

# 1.1. Absolute Maximum Ratings

| Parameter                             | Value                         | Units |

|---------------------------------------|-------------------------------|-------|

| Acceleration (powered or non-powered) | 20 000 <sup>(1</sup>          | g     |

| Supply voltage                        | -0.3 to +7.0                  | V     |

| Voltage at input / output pins        | -0.3 to V <sub>DD</sub> + 0.3 | V     |

| ESD HBM (Human Body Model)            | ±2                            | kV    |

| ESD CDM (Charged Device Model)        | ±500 middle pins              | V     |

|                                       | ±750 corner pins              |       |

| Temperature range (storage)           | -50 to +125                   | °C    |

| Temperature range (operating)         | -40 to +125                   | °C    |

Equals to drop from 1 meter on a concrete surface.

#### 1.2. Performance Characteristics

$V_{\text{DD}}$  = 5.00 V and ambient temperature unless otherwise specified.

| KPC <sup>A)</sup> | Parameter                              | Condition              | Min. | Тур       | Max. | Units             |

|-------------------|----------------------------------------|------------------------|------|-----------|------|-------------------|

|                   | Measuring range                        | Nominal                | 0    |           | +2.0 | g                 |

|                   | Supply voltage Vdd                     |                        | 4.75 | 5.0       | 5.25 | V                 |

| <cc></cc>         | Current consumption                    | Vdd = 5 V; No load     |      | 2.5       | 4.0  | mA                |

|                   | Operating temperature                  |                        | -40  |           | +125 | °C                |

|                   | Resistive output load                  | Vout to Vdd or Vss     | 20   |           |      | kΩ                |

|                   | Capacitive load                        | Vout to Vdd or Vss     |      |           | 20   | nF                |

|                   | Min. output voltage; Vdd = 5 V         | 20k from Vout to Vdd   | 0    |           | 0.25 | V                 |

|                   | Max. output voltage; Vdd = 5 V         | 20k from Vout to Vss   | 4.75 |           | 5.00 | V                 |

|                   | Linear output voltage range            | Limiter function       | 0.5  |           | 4.5  | V                 |

|                   |                                        | enabled                |      |           |      |                   |

| <cc></cc>         | Offset (Output at +1 g)                | @ room temperature     |      | Vdd/2     |      | V                 |

| <cc></cc>         | Sensitivity                            | @ room temperature     |      | 2         |      | V/g               |

|                   |                                        |                        |      | (0.4*Vdd) |      |                   |

|                   | Offset Error (Output at +1 g)          | −40 °C105 °C           | -100 | 0         | +100 | mg                |

| <sc></sc>         |                                        | −40 °C125 °C           | -125 | 0         | +125 | mg                |

|                   | Sensitivity error                      | −40 °C105 °C           | -4   | 0         | +4   | %                 |

| <sc></sc>         |                                        | −40 °C125 °C           | -5   | 0         | +5   | %                 |

|                   | Typical non-linearity                  | Within the measuring   | -20  |           | +20  | mg                |

|                   |                                        | range                  |      |           |      |                   |

|                   | Amplitude response −3 dB <sup>B)</sup> |                        | 20   | 50        | 80   | Hz                |

|                   | Ratiometric error                      | Vdd = 4.75 V5.25 V     | -2   |           | +2   | %                 |

| <sc></sc>         | Cross-axis sensitivity                 | @ room temperature     |      |           | 3.9  | %                 |

|                   | Output noise                           | From DC4 kHz           |      |           | 5    | mV <sub>rms</sub> |

|                   | Start-up delay                         | Reset and parity check |      |           | 10   | ms                |

|                   | Self test pull down resistor           |                        | 44   | 62        | 80   | kΩ                |

|                   | (Internal)                             |                        |      |           |      |                   |

CC= Critical Characteristics. Must be 100% monitored during production

SC= Significant Characteristic. The process capability (Cpk) must be better than 1.33, which allows sample based testing. If process is not capable the part will be 100% tested

2. Output has true DC response

# 1.3. Offset ans sensitivity calibration

Vout offset is calibrated in 0g position:

Offset =

$$V_{out}(+1g)[V]$$

Nominal offset is Vdd/2:

$$Offset_{nom} = \frac{V_{dd}}{2}[V]$$

Sensitivity is calibrated as:

$$Sensitivity = \frac{V_{out}(+1g) - V_{out}(0g)}{1g} \text{ [V/g]}$$

Nominal sensitivity is:

$$Sensitivity_{nom} = 2$$

[V/g]

#### 1.4. Error calculations

Total error is the allowed maximum error, which include partial error sources. Total error over lifetime is specified as a sum of offset and sensitivity errors:

Offset error is specified as:

$$Offset \_Error = \frac{Vout(+1g) - \frac{V_{dd}}{2}}{Sensitivity}$$

[mg]

Sensitivity error percent is specified as:

$$Sensitivity\_Error\% = \frac{[Vout(+1g) - Vout(0g)]/1g - Sensitivity_{nom}}{Sensitivity_{nom}} \times 100\%$$

Sensitivity error is specified as:

$$Sensitivity\_Error = \frac{\big[Vout - Vout\big(+1g\big)\big] \times Sensitivity\_Error\%}{Sensitivity} \ [mg]$$

# 1.5. Supply voltage

Usage of external 100 nF power supply bypass capacitor is recommended.

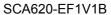

ASIC start-up should be tolerant to noise between Vdd and GND. Recommended power-up ramp is presented below.

| Parameter      | Min            | Max                     |

|----------------|----------------|-------------------------|

| T <sub>1</sub> | $T_0$ + 0.1 µs |                         |

| T <sub>2</sub> |                | T <sub>0</sub> + 100 µs |

| V <sub>1</sub> | -0.3 V         | 0.5 V                   |

| $V_2$          | 4.5 V          | 5.5 V                   |

Supply voltage ramp at startup.

**Figure 2.** V<sub>DD</sub> Start-up sequence.

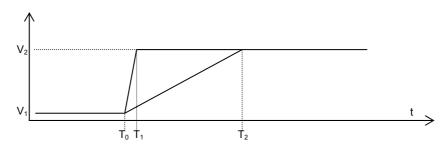

### 1.6. Electrical Connection

The following is minimum requirement for electrical interface to the SCA620. If over-voltage or reverse polarity protection is needed, please contact VTI Technologies Oy for application information.

Usage of external minimum 100 nF power supply bypass capacitor is recommended. Maximum rise time of  $V_{\text{DD}}$  is 100 ms.

If self-test (Pin 6) is not used it should be left floating.

Pins 1, 2, 3, and 5 are left floating.

**Figure 3.** Electrical connection of SCA620 component.

| Pin# | Pin Name | I/O    | Function                                   | Connection on PCB       |

|------|----------|--------|--------------------------------------------|-------------------------|

| 1    | CLK      |        |                                            | Float / Not connected   |

| 2    | C1       |        |                                            | Float / Not connected   |

| 3    | MODE     |        |                                            | Float / Not connected   |

| 4    | GND      | Supply | Negative supply voltage (VSS)              | Ground                  |

| 5    | PGM      |        |                                            | Float / Not connected   |

| 6    | ST       | Input  | Self-test control                          | Float when not used     |

| 7    | VOUT     | Output | Sensor output voltage                      | Measuring circuit input |

| 8    | VDD      | Supply | Positive supply voltage (V <sub>DD</sub> ) | Vdd (+5V)               |

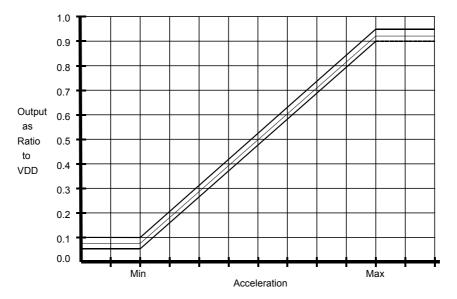

#### 1.7. Limiter function

The table below defines the limiter function.

| Parameter Condition    |                            | Min        | Max        | Unit |

|------------------------|----------------------------|------------|------------|------|

| Limiter cutoff voltage | Low voltage limit          | 0.05 × Vdd | 0.10 × Vdd | V    |

|                        | High voltage limit         | 0.90 × Vdd | 0.95 × Vdd | V    |

| Min output voltage     | Limiter enabled, VDD = 5 V | 0.25       |            | V    |

| Max output voltage     | Limiter enabled, VDD = 5 V |            | 4.75       | V    |

| Linear range           | Limiter enabled, VDD = 5 V | 0.5        | 4.5        | V    |

**Figure 4.** Limiter function.

Doc. nr. 82 507 00

Limiter function limits the output voltage between specified upper and lower limit. In normal operation ( $V_{DD}$  = 5.0 V), when limiter is enabled, the output voltage is valid between 0.5 V...4.5 V. Limiting activates between 0.25 V...0.5 V and 4.5 V...4.75 V. Only failures drive output voltage beyond cutoff voltages.

### 2. Functional Description

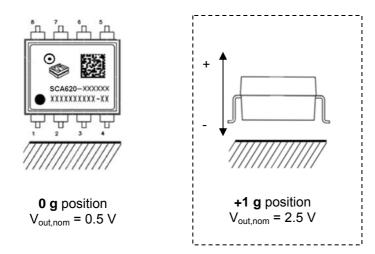

### 2.1. Measuring directions

# 2.2. Voltage to acceleration conversion

Analog output can be transferred to acceleration using the following equation for conversion:

$$Acceleration = \frac{V_{out} - V_{out}(0g)}{Sensitivity}$$

[g]

where:  $V_{out}(0g)$  = nominal output of the device at 0g position with 5 V supply voltage (ratiometric output), Sensitivity is the sensitivity of the device and  $V_{out}$  is the output of the sensor.

### 2.3. Ratiometric Output

Ratiometric output means that the zero offset point and sensitivity of the sensor are proportional to the supply voltage. If the SCA6X0 supply voltage is fluctuating the SCA6X0 output will also vary. When the same reference voltage for both the SCA6X0 sensor and the measuring part (A/D-converter) is used, the error caused by reference voltage variation is automatically compensated for.

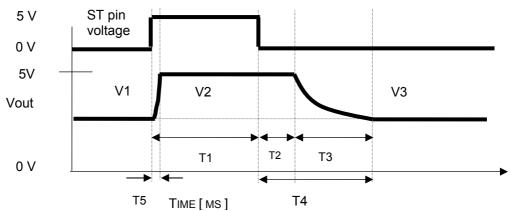

#### 2.4. Selftest and failure detection modes

To ensure reliable measurement results the SCA6X0 has continuous interconnection failure and calibration memory validity detection. A detected failure forces the output signal close to power supply ground or VDD level, outside the normal output range.

The calibration memory validity is verified by continuously running parity check for the control register memory content. In the case where a parity error is detected, the control register is automatically re-loaded from the EEPROM. If a new parity error is detected after re-loading data analog output voltage is forced to go close to ground level (<0.25 V).

The SCA6X0 also includes a separate self test mode. The true self test simulates acceleration, or deceleration, using an electrostatic force. The electrostatic force simulates acceleration that is high enough to deflect the proof mass to the extreme positive position, and this causes the output signal

to go to the maximum value. The self test function is activated by a separate on-off command on the self test input.

The self-test generates an electrostatic force, deflecting the sensing element's proof mass, thus checking the complete signal path. The true self test performs following checks:

- Sensing element movement check

- ASIC signal path check

- PCB signal path check

- Micro controller A/D and signal path check

The created deflection can be seen in analogue output. Self test can be activated applying logic"1" (positive supply voltage level) to ST pin (pins 6) of SCA6X0. The self test Input high voltage level is 4 - Vdd + 0.3 V and input low voltage level is 0.3 - 1 V.

Figure 7. Self test wave forms.

V1 = initial output voltage before the self test function is activated.

V2 = output voltage during the self test function.

V3 = output voltage after the self test function has been de-activated and after stabilization time Please note that the error band specified for V3 is to guarantee that the output is within 5% of the initial value after the specified stabilization time. After a longer time (max. 1 second) V1=V3.

T1 = Pulse length for Self test activation

T2 = Saturation delay

T3 = Recovery time

T4 = Stabilization time =T2+T3

T5 = Rise time during self test.

| T1 [ms] | T2 [ms] | T3 [ms] | T4 [ms] | T5 [ms] | V2:             | V3:      |

|---------|---------|---------|---------|---------|-----------------|----------|

| 10-100  | Typ. 20 | Typ. 50 | Typ. 70 | Typ. 10 | Min 0.95*VDD    | 0.95*V1- |

|         |         |         |         |         | (4.75V @Vdd=5V) | 1.05*V1  |

Self test characteristics.

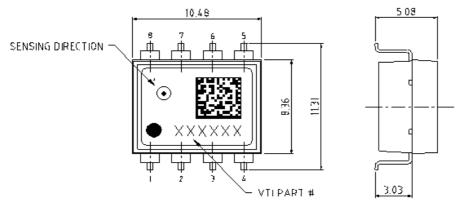

# 3. Mechanical Specification

Lead frame material: Copper

Plating: Nickel followed by Gold

Solderability: JEDEC standard: JESD22-B102-C

Co-planarity: 0.1 mm max.

The part weights: ~0.73 g

## 3.1. Dimensions

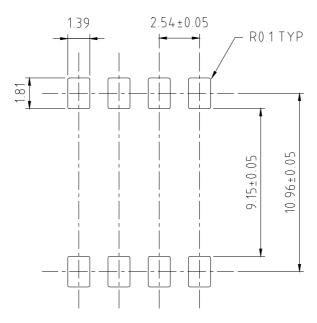

Figure 8. Mechanical dimensions [mm].

#### 4. Application information

The SCA6X0 should be powered from a well regulated 5 V DC power supply. Coupling of digital noise to the power supply line should be minimized. 100nF filtering capacitor between VDD pin 8 and GND plane must be used. If regulator is placed far from component for example other PCB it is recommend adding more capacitance between VDD and GND to ensure current drive capability of the system. For example 470 pF and 1uF capacitor can be used.

The SCA6X0 has a ratiometric output. To get the best performance use the same reference voltage for both the SCA6X0 and Analog/Digital converter.

Locate the 100nF power supply filtering capacitor close to VDD pin 8. Use as short a trace length as possible. Connect the other end of capacitor directly to the ground plane. Connect the GND pin 4 to underlying ground plane. Use as wide ground and power supply planes as possible. Avoid narrow power supply or GND connection strips on PCB.

### 4.1. Recommended PCB lay-out

Figure 9. Recommended PCB lay-out [mm].

#### Notes:

- It is important that the part is parallel to the PCB plane and that there is no angular alignment error from intended measuring direction during assembly process.

- 1° mounting alignment error will increase the cross-axis sensitivity by 1.7%

- 1° mounting alignment error will change the output by 17 mg

- · Wave soldering is not recommended

- · Ultrasonic cleaning is not allowed

- A supply voltage by-pass capacitor (> 100 nF) is recommended

### 4.2. Reflow soldering

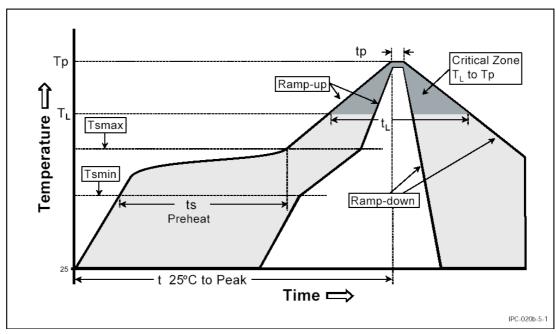

The SCA6X0 is suitable for Sn-Pb eutectic and Pb- free soldering process and mounting with normal SMD pick-and-place equipment. Recommended <u>body</u> temperature profile during reflow soldering:

**Figure 10.** Recommended body temperature profile during reflow soldering. Ref. IPC/JEDEC J-STD-020D.

| Profile feature                                                         | Sn-Pb Eutectic<br>Assembly | Pb-free Assembly |

|-------------------------------------------------------------------------|----------------------------|------------------|

| Average ramp-up rate (T <sub>L</sub> to T <sub>P</sub> )                | 3 °C/second max.           | 3 °C/second max. |

| Preheat                                                                 |                            |                  |

| - Temperature min (T <sub>smin</sub> )                                  | 100 °C                     | 150 °C           |

| - Temperature max (T <sub>smax</sub> )                                  | 150 °C                     | 200 °C           |

| - Time (min to max) (ts)                                                | 60-120 seconds             | 60-180 seconds   |

| Tsmax to T <sub>L</sub>                                                 |                            | 3°C/second max   |

| - Ramp up rate                                                          |                            |                  |

| Time maintained above:                                                  |                            |                  |

| - Temperature (T <sub>L</sub> )                                         | 183 °C                     | 217 °C           |

| - Time (t <sub>L</sub> )                                                | 60-150 seconds             | 60-150 seconds   |

| Peak temperature (T <sub>P</sub> )                                      | 240 +0/−5 °C               | 250 +0/−5 °C     |

| Time within 5 $^{\circ}$ C of actual Peak Temperature (T <sub>P</sub> ) | 10-30 seconds              | 20-40 seconds    |

| Ramp-down rate                                                          | 6 °C/second max            | 6 °C/second max  |

| Time 25 °C to Peak temperature                                          | 6 minutes max              | 8 minutes max    |

The Moisture Sensitivity Level of the part is 3 according to the IPC/JEDEC J-STD-020D. The part should be delivered in a dry pack. The manufacturing floor time (out of bag) in the customer's end is 168 hours.

#### Notes:

- Preheating time and temperatures according to guidance from solder paste manufacturer.

- It is important that the part is parallel to the PCB plane and that there is no angular alignment error from intended measuring direction during assembly process.

- Wave soldering is not recommended.

- **Ultrasonic cleaning is not allowed**. The sensing element may be damaged by an ultrasonic cleaning process

The Moisture Sensitivity Level of the part is 3 according to the IPC/JEDEC J-STD-020B. The part should be delivered in a dry pack. The manufacturing floor time (out of bag) in the customer's end is 168 hours. Maximum soldering temperature is  $250~^{\circ}\text{C}/40~\text{sec}$ .

Rework after the initial soldering process is not recommended. Rework can cause heat build-up to the leg and this heat build-up will cause the housing material to get soft thus allowing the leg to move. The movement can cause bond wire disconnection inside the part.