**SCANSWITCH™****NPN Bipolar Power Deflection Transistor

For High and Very High Resolution

Monitors**

The MJW16212 is a state-of-the-art SWITCHMODE™ bipolar power transistor. It is specifically designed for use in horizontal deflection circuits for 20 mm diameter neck, high and very high resolution, full page, monochrome monitors.

- 1500 Volt Collector-Emitter Breakdown Capability

- Typical Dynamic Desaturation Specified (New Turn-Off Characteristic)

- Application Specific State-of-the-Art Die Design

- Fast Switching:

- 200 ns Inductive Fall Time (Typ)

- 2000 ns Inductive Storage Time (Typ)

- Low Saturation Voltage:

- 0.15 Volts at 5.5 Amps Collector Current and 2.5 A Base Drive

- Low Collector-Emitter Leakage Current —

- 250  $\mu$ A Max at 1500 Volts —  $V_{CES}$

- High Emitter-Base Breakdown Capability For High Voltage Off Drive Circuits —

- 8.0 Volts (Min)

**MAXIMUM RATINGS**

| Rating                                                                                                                      | Symbol            | Value             | Unit                         |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------------------|

| Collector-Emitter Breakdown Voltage                                                                                         | $V_{CES}$         | 1500              | Vdc                          |

| Collector-Emitter Sustaining Voltage                                                                                        | $V_{CEO(sus)}$    | 650               | Vdc                          |

| Emitter-Base Voltage                                                                                                        | $V_{EBO}$         | 8.0               | Vdc                          |

| RMS Isolation Voltage (2)<br>(for 1 sec, $T_A = 25^\circ\text{C}$ ,<br>Rel. Humidity < 30%)                                 | $V_{ISOL}$        | —                 | V                            |

| Per Fig. 14                                                                                                                 |                   | —                 |                              |

| Per Fig. 15                                                                                                                 |                   | —                 |                              |

| Collector Current — Continuous<br>— Pulsed (1)                                                                              | $I_C$<br>$I_{CM}$ | 10<br>15          | Adc                          |

| Base Current — Continuous<br>— Pulsed (1)                                                                                   | $I_B$<br>$I_{BM}$ | 5.0<br>10         | Adc                          |

| Maximum Repetitive Emitter-Base<br>Avalanche Energy                                                                         | W (BER)           | 0.2               | mJ                           |

| Total Power Dissipation @ $T_C = 25^\circ\text{C}$<br>@ $T_C = 100^\circ\text{C}$<br>Derated above $T_C = 25^\circ\text{C}$ | $P_D$             | 150<br>39<br>1.49 | Watts<br>W/ $^\circ\text{C}$ |

| Operating and Storage Temperature Range                                                                                     | $T_J, T_{stg}$    | -55 to 125        | $^\circ\text{C}$             |

**MJW16212\***

\*ON Semiconductor Preferred Device

**POWER TRANSISTOR

10 AMPERES

1500 VOLTS —  $V_{CES}$

50 AND 150 WATTS**

**CASE 340K-01

TO-247AE**

**Preferred** devices are ON Semiconductor recommended choices for future use and best overall value.

**THERMAL CHARACTERISTICS**

| Characteristic                                                              | Symbol          | Max  | Unit |

|-----------------------------------------------------------------------------|-----------------|------|------|

| Thermal Resistance — Junction to Case                                       | $R_{\theta JC}$ | 0.67 | °C/W |

| Lead Temperature for Soldering Purposes<br>1/8" from the case for 5 seconds | $T_L$           | 275  | °C   |

(1) Pulse Test: Pulse Width = 5.0 ms, Duty Cycle  $\leq$  10%.

(2) Proper strike and creepage distance must be provided.

**ELECTRICAL CHARACTERISTICS (T<sub>C</sub> = 25°C unless otherwise noted)**

| Characteristic | Symbol | Min | Typ | Max | Unit |

|----------------|--------|-----|-----|-----|------|

|----------------|--------|-----|-----|-----|------|

**OFF CHARACTERISTICS (2)**

|                                                                                                                                 |                |     |    |           |      |

|---------------------------------------------------------------------------------------------------------------------------------|----------------|-----|----|-----------|------|

| Collector Cutoff Current (V <sub>CE</sub> = 1500 V, V <sub>BE</sub> = 0 V)<br>(V <sub>CE</sub> = 1200 V, V <sub>BE</sub> = 0 V) | $I_{CES}$      | —   | —  | 250<br>25 | μAdc |

| Emitter-Base Leakage (V <sub>EB</sub> = 8.0 Vdc, I <sub>C</sub> = 0)                                                            | $I_{EBO}$      | —   | —  | 25        | μAdc |

| Emitter-Base Breakdown Voltage (I <sub>E</sub> = 1.0 mA, I <sub>C</sub> = 0)                                                    | $V_{(BR)EBO}$  | 8.0 | 11 | —         | Vdc  |

| Collector-Emitter Sustaining Voltage (Table 1) (I <sub>C</sub> = 10 mAdc, I <sub>B</sub> = 0)                                   | $V_{CEO(sus)}$ | 650 | —  | —         | Vdc  |

**ON CHARACTERISTICS (2)**

|                                                                                                                                                    |               |   |              |            |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---|--------------|------------|---------|

| Collector-Emitter Saturation Voltage (I <sub>C</sub> = 5.5 Adc, I <sub>B</sub> = 2.2 Adc)<br>(I <sub>C</sub> = 3.0 Adc, I <sub>B</sub> = 400 mAdc) | $V_{CE(sat)}$ | — | 0.15<br>0.14 | 1.0<br>1.0 | Vdc     |

| Base-Emitter Saturation Voltage (I <sub>C</sub> = 5.5 Adc, I <sub>B</sub> = 2.2 Adc)                                                               | $V_{BE(sat)}$ | — | 0.9          | 1.5        | Vdc     |

| DC Current Gain (I <sub>C</sub> = 1.0 A, V <sub>CE</sub> = 5.0 Vdc)<br>(I <sub>C</sub> = 10 A, V <sub>CE</sub> = 5.0 Vdc)                          | $h_{FE}$      | — | 24<br>4.0    | —<br>6.0   | —<br>10 |

**DYNAMIC CHARACTERISTICS**

|                                                                                                                                                                |                     |   |      |     |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---|------|-----|-----|

| Dynamic Desaturation Interval (I <sub>C</sub> = 5.5 A, I <sub>B1</sub> = 2.2 A, LB = 1.5 μH)                                                                   | $t_{ds}$            | — | 350  | —   | ns  |

| Output Capacitance<br>(V <sub>CE</sub> = 10 Vdc, I <sub>E</sub> = 0, f <sub>test</sub> = 100 kHz)                                                              | $C_{ob}$            | — | 180  | 350 | pF  |

| Gain Bandwidth Product<br>(V <sub>CE</sub> = 10 Vdc, I <sub>C</sub> = 0.5 A, f <sub>test</sub> = 1.0 MHz)                                                      | $f_T$               | — | 2.75 | —   | MHz |

| Emitter-Base Turn-Off Energy<br>(EB <sub>(avalanche)</sub> = 500 ns, R <sub>BE</sub> = 22 Ω)                                                                   | EB <sub>(off)</sub> | — | 35   | —   | μJ  |

| Collector-Heatsink Capacitance — MJF16212 Isolated Package<br>(Mounted on a 1" x 2" x 1/16" Copper Heatsink, V <sub>CE</sub> = 0, f <sub>test</sub> = 100 kHz) | $C_{c-hs}$          | — | 5.0  | —   | pF  |

**SWITCHING CHARACTERISTICS**

|                                                                                                                                                  |                      |   |             |             |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---|-------------|-------------|----|

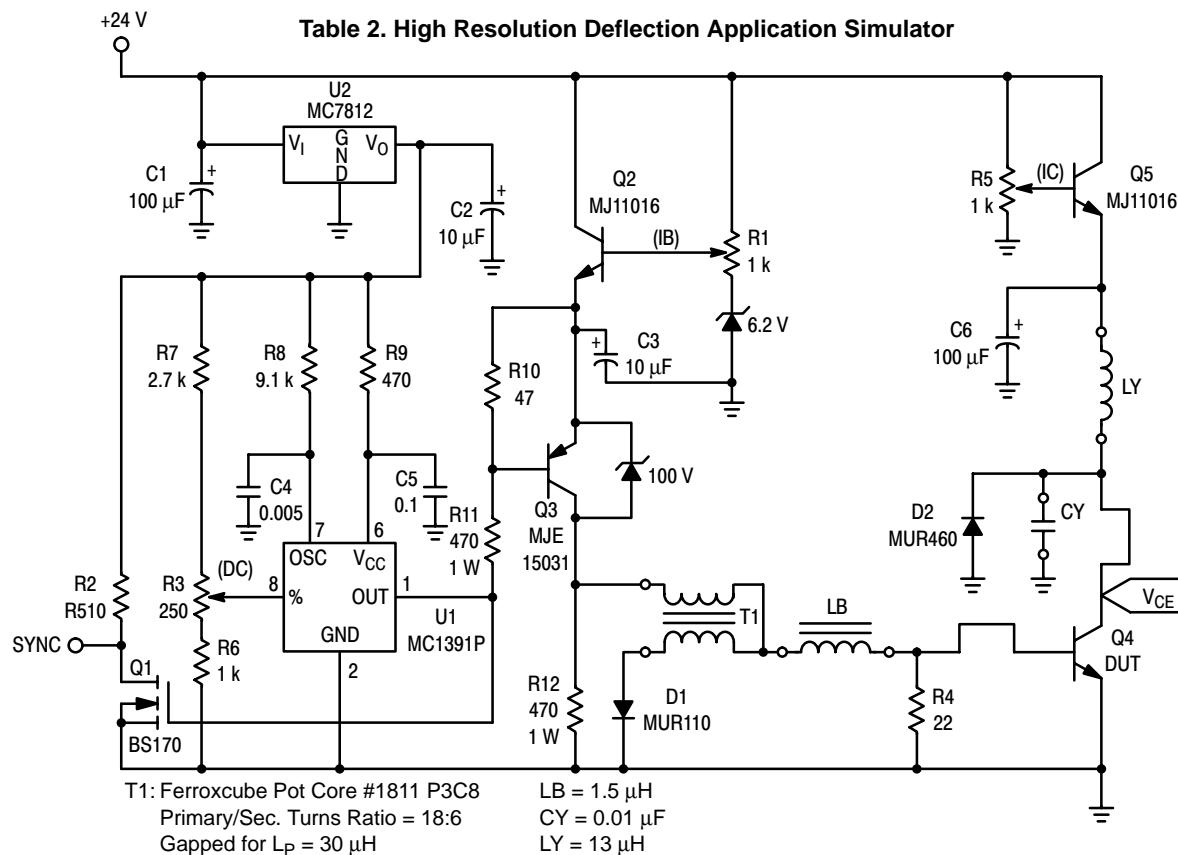

| Inductive Load (I <sub>C</sub> = 5.5 A, I <sub>B</sub> = 2.2 A), High Resolution Deflection<br>Simulator Circuit Table 2<br>Storage<br>Fall Time | $t_{sv}$<br>$t_{fi}$ | — | 2000<br>200 | 4000<br>350 | ns |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---|-------------|-------------|----|

(2) Pulse Test: Pulse Width = 300 μs, Duty Cycle  $\leq$  2.0%.

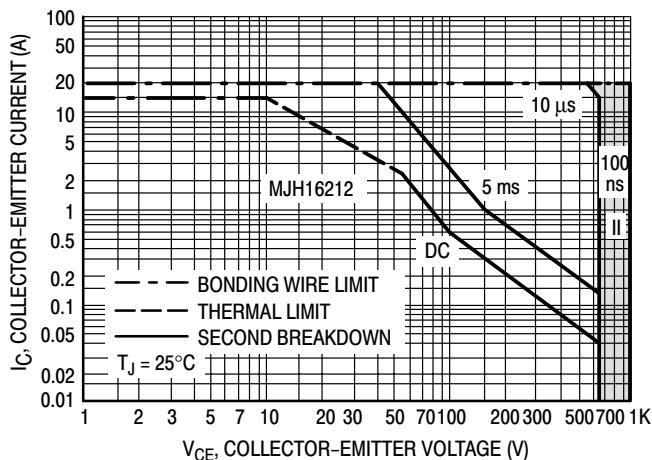

## SAFE OPERATING AREA

**Figure 1. Maximum Forward Bias

Safe Operating Area**

## FORWARD BIAS

There are two limitations on the power handling ability of a transistor: average junction temperature and second breakdown. Safe operating area curves indicate  $I_C - V_{CE}$  limits of the transistor that must be observed for reliable operation; i.e., the transistor must not be subjected to greater dissipation than the curves indicate.

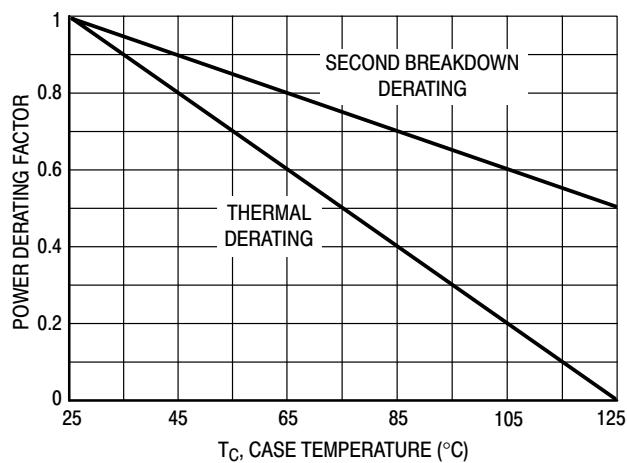

The data of Figure 1 is based on  $T_C = 25^\circ\text{C}$ ;  $T_{J(pk)}$  is variable depending on power level. Second breakdown pulse limits are valid for duty cycles to 10% but must be derated when  $T_C \geq 25^\circ\text{C}$ . Second breakdown limitations do not derate the same as thermal limitations. Allowable current at the voltages shown on Figure 1 may be found at any case temperature by using the appropriate curve on Figure 3.

At high case temperatures, thermal limitations will reduce the power that can be handled to values less than the limitations imposed by second breakdown.

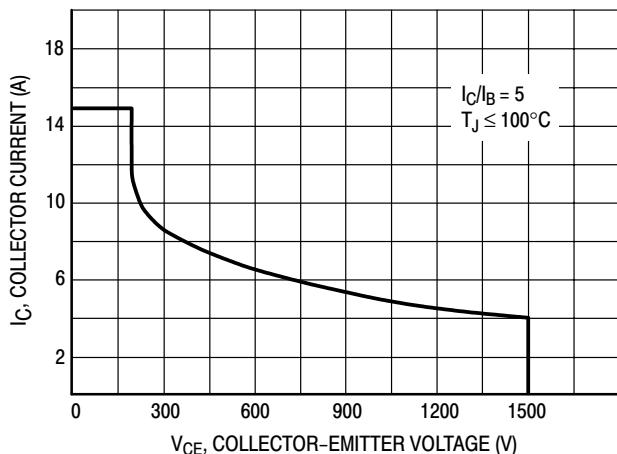

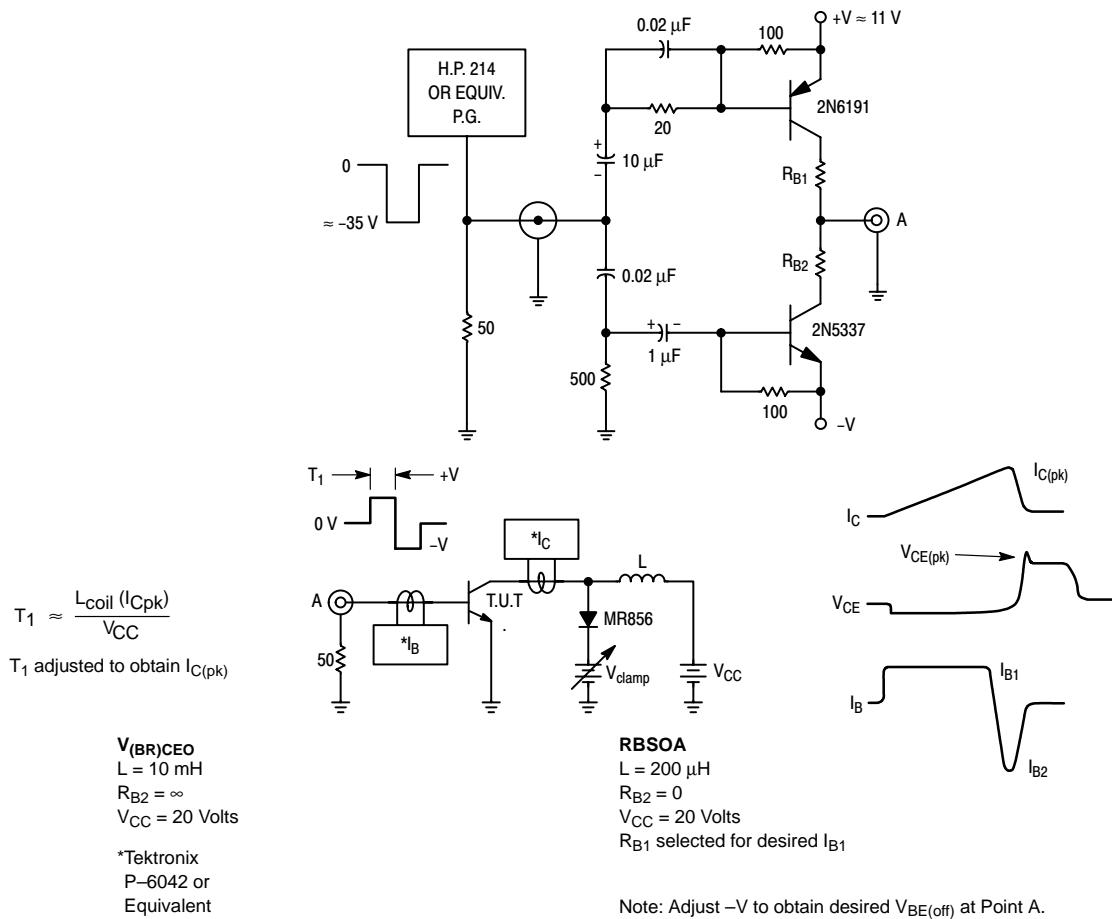

## REVERSE BIAS

For inductive loads, high voltage and high current must be sustained simultaneously during turn-off, in most cases, with the base-to-emitter junction reverse biased. Under these conditions the collector voltage must be held to a safe level at or below a specific value of collector current. This can be accomplished by several means such as active clamping, RC snubbing, load line shaping, etc.

**Figure 2. Maximum Reverse Bias

Safe Operating Area**

**Figure 3. Power Derating**

The safe level for these devices is specified as Reverse Biased Safe Operating Area and represents the voltage-current condition allowable during reverse biased turnoff. This rating is verified under clamped conditions so that the device is never subjected to an avalanche mode. Figure 2 gives the RBSOA characteristics.

# MJW16212

**Table 1. RBSOA/V<sub>(BR)CEO(SUS)</sub> Test Circuit**

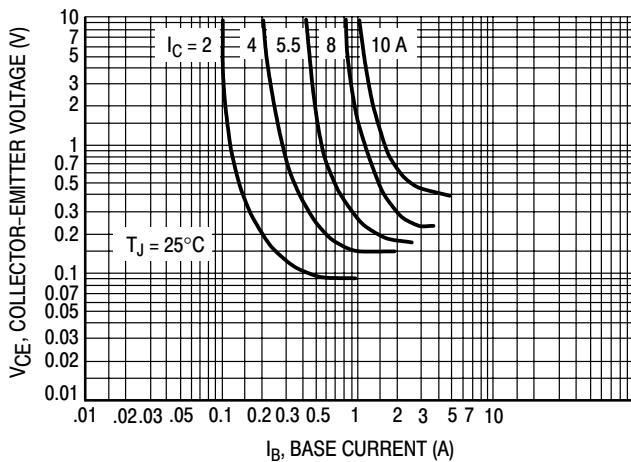

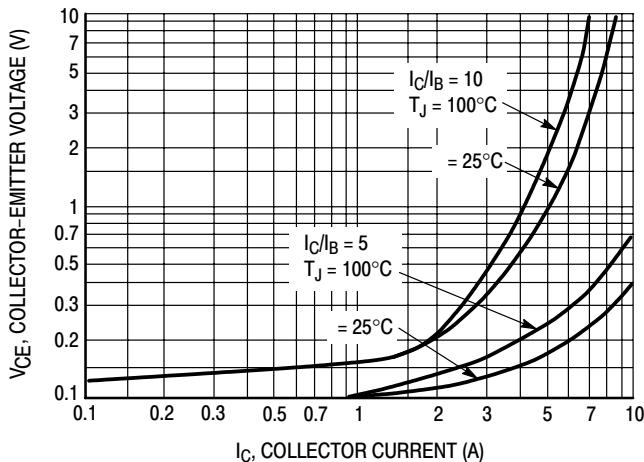

**Figure 4. Typical Collector-Emitter Saturation Region**

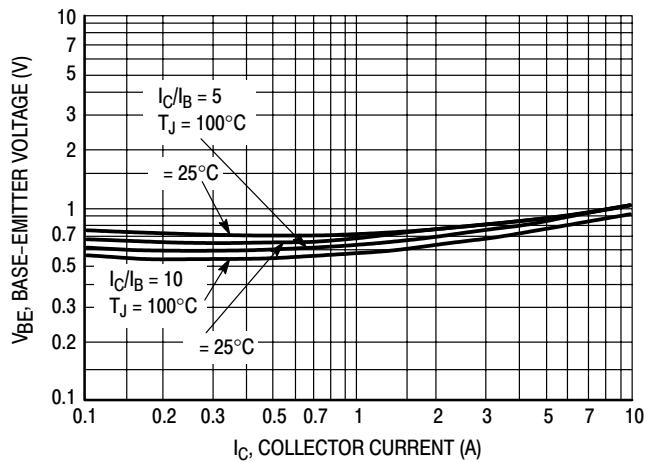

**Figure 6. Typical Emitter-Base Saturation Voltage**

**Figure 5. Typical Collector-Emitter Saturation Voltage**

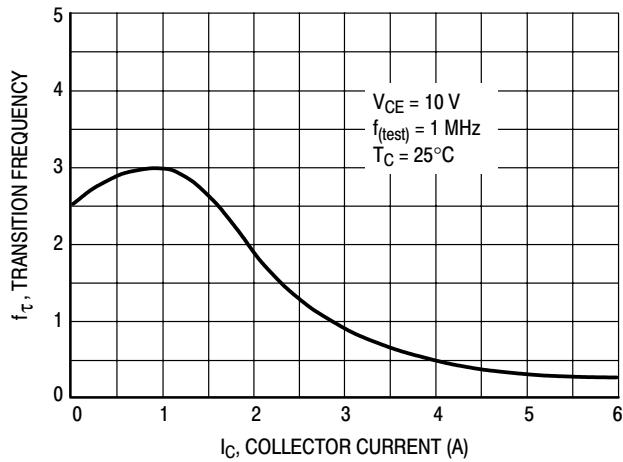

**Figure 7. Typical Transition Frequency**

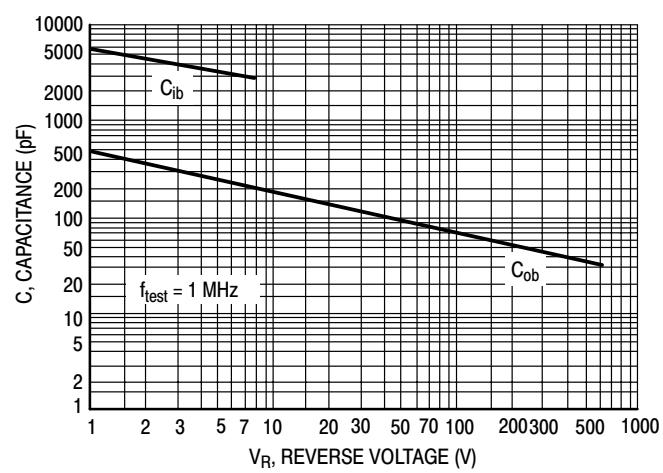

**Figure 8. Typical Capacitance**

## DYNAMIC DESATURATION

The SCANSWITCH series of bipolar power transistors are specifically designed to meet the unique requirements of horizontal deflection circuits in computer monitor applications. Historically, deflection transistor design was focused on minimizing collector current fall time. While fall time is a valid figure of merit, a more important indicator of circuit performance as scan rates are increased is a new characteristic, "dynamic desaturation." In order to assure a linear collector current ramp, the output transistor must remain in hard saturation during storage time and exhibit a rapid turn-off transition. A sluggish transition results in serious consequences. As the saturation voltage of the output transistor increases, the voltage across the yoke

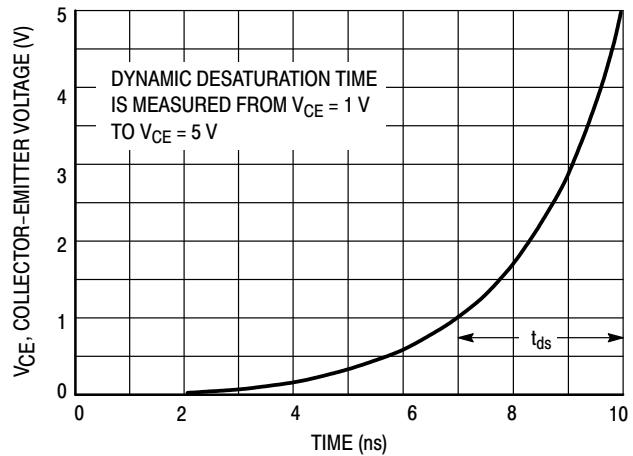

drops. Roll off in the collector current ramp results in improper beam deflection and distortion of the image at the right edge of the screen. Design changes have been made in the structure of the SCANSWITCH series of devices which minimize the dynamic desaturation interval. Dynamic desaturation has been defined in terms of the time required for the  $V_{CE}$  to rise from 1.0 to 5.0 volts (Figures 9 and 10) and typical performance at optimized drive conditions has been specified. Optimization of device structure results in a linear collector current ramp, excellent turn-off switching performance, and significantly lower overall power dissipation.

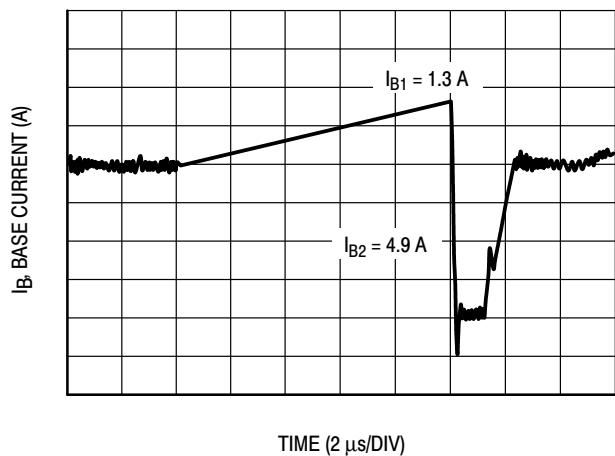

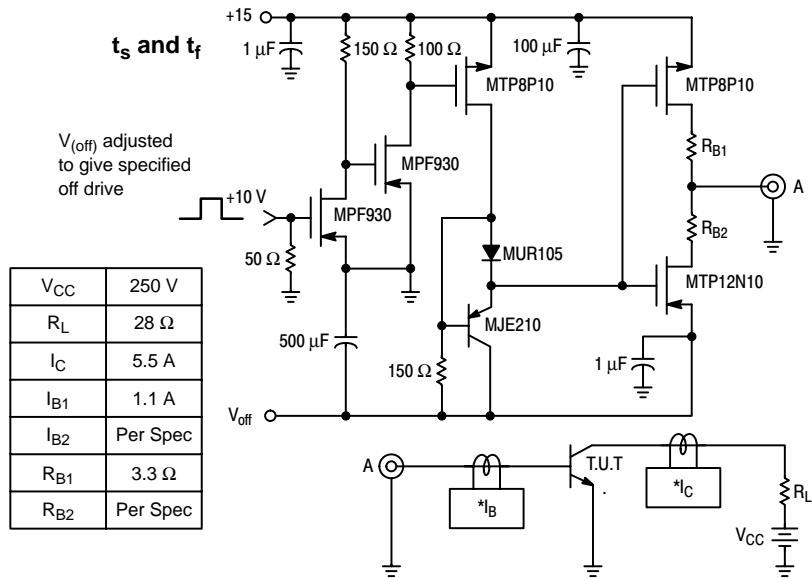

**Figure 9. Deflection Simulator Circuit Base Drive Waveform**

**Figure 10. Definition of Dynamic Desaturation Measurement**

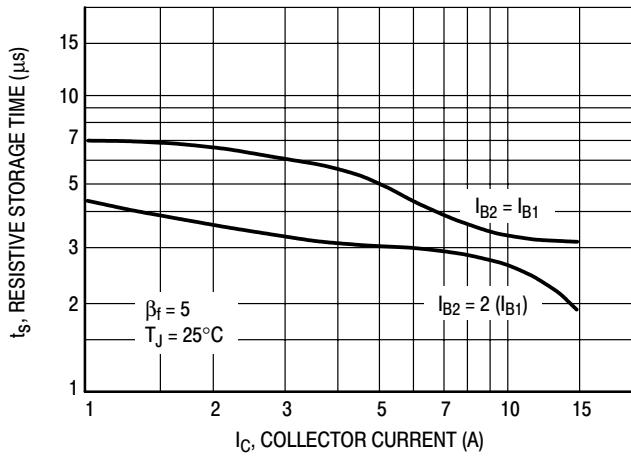

**Figure 11. Typical Resistive Storage Time**

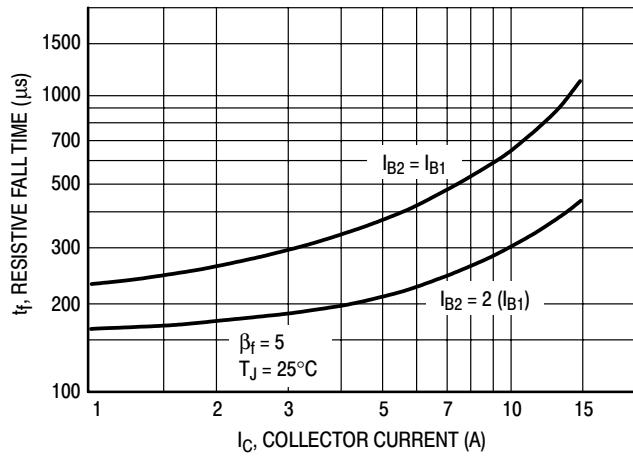

**Figure 12. Typical Resistive Fall Time**

**Table 3. Resistive Load Switching**

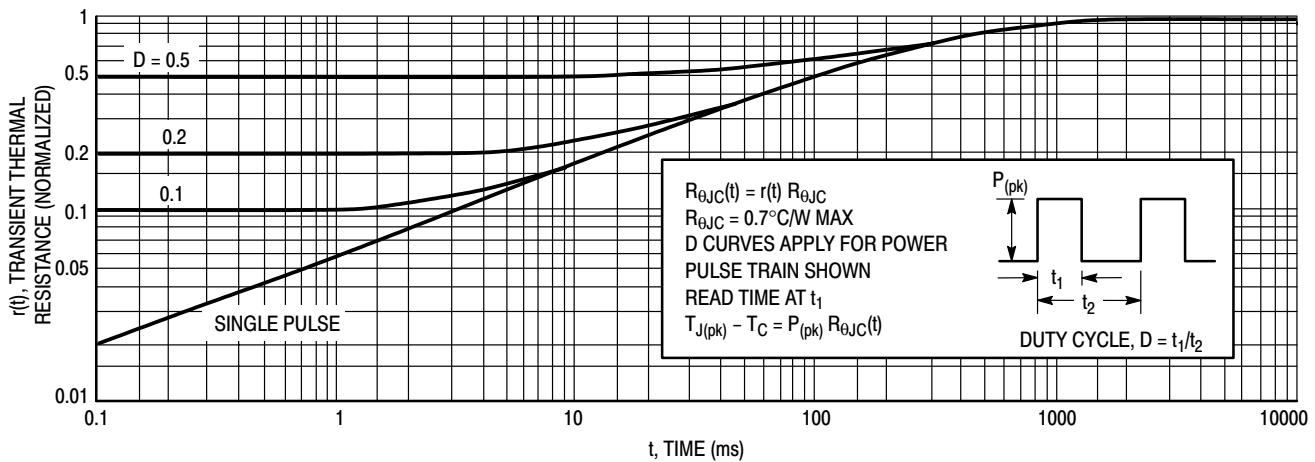

**Figure 13. Thermal Response**

**EMITTER-BASE TURN-OFF ENERGY,  $EB_{(off)}$**

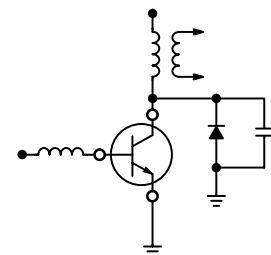

Emitter-base turn-off energy is a new specification included on the SCANSWITCH data sheets. Typical techniques for driving horizontal outputs rely on a pulse transformer to supply forward base current, and a turnoff network that includes a series base inductor to limit the rate of transition from forward to reverse. An alternate drive scheme has been used to characterize the SCANSWITCH series of devices (see Figure 2). This circuit ramps the base drive to eliminate the heavy overdrive at the beginning of the collector current ramp and underdrive just prior to turn-off observed in typical drive topologies. This high performance drive has two additional important advantages. First, the

configuration of T1 allows  $L_b$  to be placed outside the path of forward base current making it unnecessary to expend energy to reverse the current flow as in a series based inductor. Second, there is no base resistor to limit forward base current and hence no power loss associated with setting the value of the forward base current. The ramp generating process stores rather than dissipates energy. Tailoring the amount of energy stored in T1 to the amount of energy,  $EB_{(off)}$ , that is required to turn the output transistor off results in essentially lossless operation. [Note:  $B_+$  and the primary inductance of T1 ( $L_p$ ) are chosen such that  $1/2L_p I_b^2 = EB_{(off)}$ .]

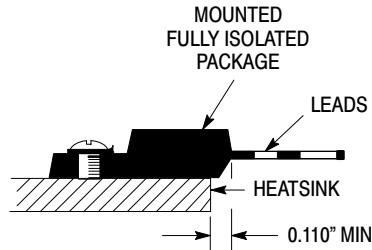

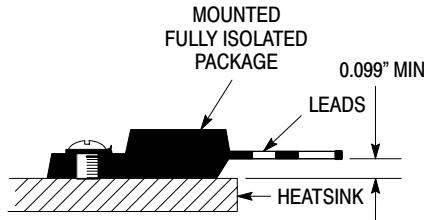

**TEST CONDITIONS FOR ISOLATION TESTS\* (MJF16212 ONLY)**

**Figure 14. Screw or Clip Mounting Position for Isolation Test Number 1**

**Figure 15. Screw or Clip Mounting Position for Isolation Test Number 2**

\*Measurement made between leads and heatsink with all leads shorted together

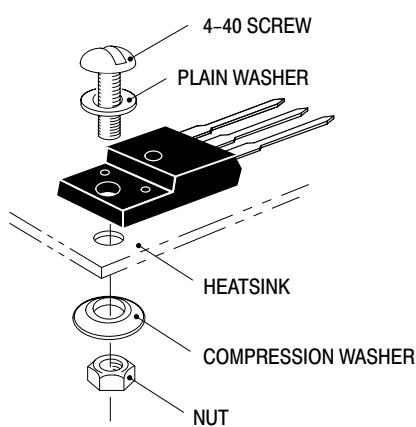

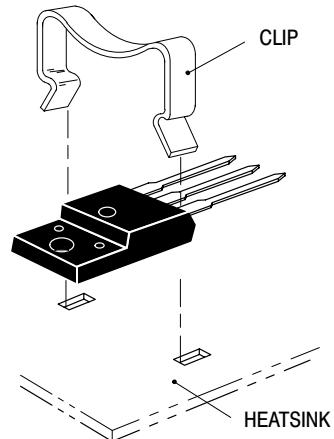

**MOUNTING INFORMATION\*\* (MJF16212 ONLY)**

**Figure 16a. Screw-Mounted**

**Figure 16b. Clip-Mounted**

**Figure 16. Typical Mounting Techniques\***

Laboratory tests on a limited number of samples indicate, when using the screw and compression washer mounting technique, a screw torque of 6 to 8 in · lbs is sufficient to provide maximum power dissipation capability. The compression washer helps to maintain a constant pressure on the package over time and during large temperature excursions.

Destructive laboratory tests show that using a hex head 4-40 screw, without washers, and applying a torque in excess of 20 in · lbs will cause the plastic to crack around the mounting hole, resulting in a loss of isolation capability.

Additional tests on slotted 4-40 screws indicate that the screw slot fails between 15 to 20 in · lbs without adversely affecting the package. However, in order to positively ensure the package integrity of the fully isolated device, ON Semiconductor does not recommend exceeding 10 in · lbs of mounting torque under any mounting conditions.

\*\* For more information about mounting power semiconductors see Application Note AN1040.

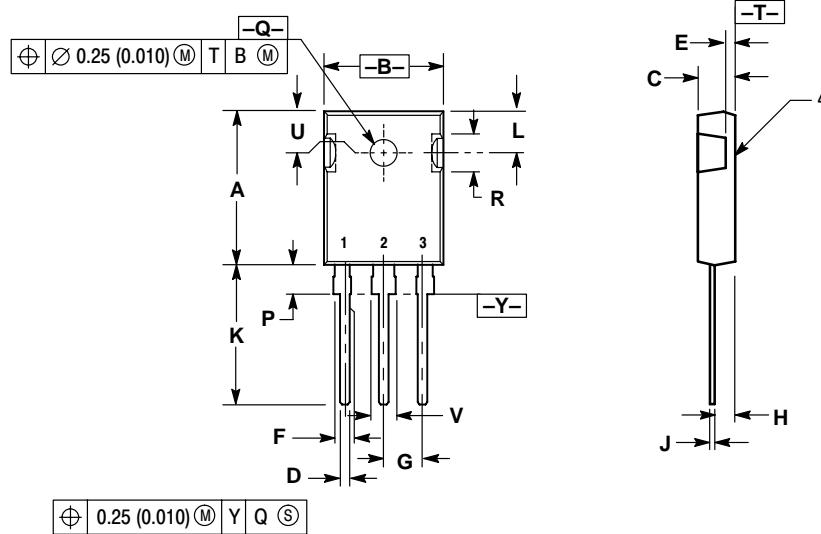

**PACKAGE DIMENSIONS**

**TO-247AE

CASE 340K-01

ISSUE C**

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

| DIM | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

|     | MIN         | MAX  | MIN       | MAX   |

| A   | 19.7        | 20.3 | 0.776     | 0.799 |

| B   | 15.3        | 15.9 | 0.602     | 0.626 |

| C   | 4.7         | 5.3  | 0.185     | 0.209 |

| D   | 1.0         | 1.4  | 0.039     | 0.055 |

| E   | 1.27 REF    |      | 0.050 REF |       |

| F   | 2.0         | 2.4  | 0.079     | 0.094 |

| G   | 5.5 BSC     |      | 0.216 BSC |       |

| H   | 2.2         | 2.6  | 0.087     | 0.102 |

| J   | 0.4         | 0.8  | 0.016     | 0.031 |

| K   | 14.2        | 14.8 | 0.559     | 0.583 |

| L   | 5.5 NOM     |      | 0.217 NOM |       |

| P   | 3.7         | 4.3  | 0.146     | 0.169 |

| Q   | 3.55        | 3.65 | 0.140     | 0.144 |

| R   | 5.0 NOM     |      | 0.197 NOM |       |

| U   | 5.5 BSC     |      | 0.217 BSC |       |

| V   | 3.0         | 3.4  | 0.118     | 0.134 |

## **Notes**

SWITCHMODE is a trademark of Semiconductor Components Industries, LLC.

SCANSWITCH is a trademark of Semiconductor Components Industries, LLC.

**ON Semiconductor** and  are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

## PUBLICATION ORDERING INFORMATION

### **NORTH AMERICA Literature Fulfillment:**

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

**Phone:** 303-675-2175 or 800-344-3860 Toll Free USA/Canada

**Fax:** 303-675-2176 or 800-344-3867 Toll Free USA/Canada

**Email:** ONlit@hibbertco.com

Fax Response Line: 303-675-2167 or 800-344-3810 Toll Free USA/Canada

### **N. American Technical Support:** 800-282-9855 Toll Free USA/Canada

**EUROPE:** LDC for ON Semiconductor – European Support

**German Phone:** (+1) 303-308-7140 (Mon-Fri 2:30pm to 7:00pm CET)

**Email:** ONlit-german@hibbertco.com

**French Phone:** (+1) 303-308-7141 (Mon-Fri 2:00pm to 7:00pm CET)

**Email:** ONlit-french@hibbertco.com

**English Phone:** (+1) 303-308-7142 (Mon-Fri 12:00pm to 5:00pm GMT)

**Email:** ONlit@hibbertco.com

### **EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781**

\*Available from Germany, France, Italy, UK, Ireland

### **CENTRAL/SOUTH AMERICA:**

**Spanish Phone:** 303-308-7143 (Mon-Fri 8:00am to 5:00pm MST)

**Email:** ONlit-spanish@hibbertco.com

**Toll-Free from Mexico:** Dial 01-800-288-2872 for Access –

then Dial 866-297-9322

**ASIA/PACIFIC:** LDC for ON Semiconductor – Asia Support

**Phone:** 1-303-675-2121 (Tue-Fri 9:00am to 1:00pm, Hong Kong Time)

**Toll Free from Hong Kong & Singapore:**

**001-800-4422-3781**

**Email:** ONlit-asia@hibbertco.com

**JAPAN:** ON Semiconductor, Japan Customer Focus Center

4-32-1 Nishi-Gotanda, Shinagawa-ku, Tokyo, Japan 141-0031

**Phone:** 81-3-5740-2700

**Email:** r14525@onsemi.com

**ON Semiconductor Website:** <http://onsemi.com>

For additional information, please contact your local

Sales Representative.