DGY High Efficiency, Multi-Chemistry Battery Charger with PowerPath Control

#### **FEATURES**

- General Purpose Battery Charger Controller

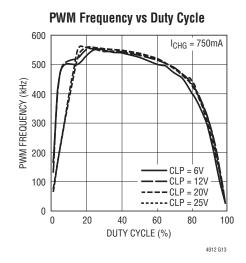

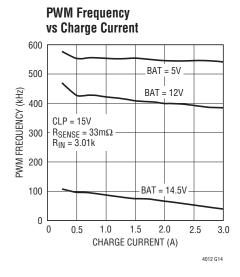

- Efficient 550kHz Synchronous Buck PWM Topology

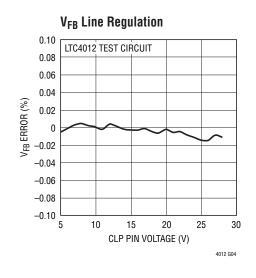

- ±0.5% Output Float Voltage Accuracy

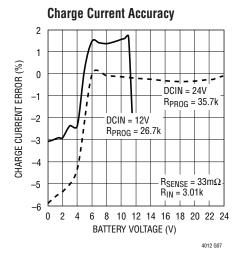

- Programmable Charge Current: 4% Accuracy

- Programmable AC Adapter Current Limit: 3% Accuracy

- No Audible Noise with Ceramic Capacitors

- INFET Low Loss Ideal Diode PowerPath™ Control

- Wide Input Voltage Range: 6V to 28V

- Wide Output Voltage Range: 2V to 28V

- Indicator Outputs for AC Adapter Present, Charging, C/10 Current Detection and Input Current Limiting

- Analog Charge Current Monitor

- Micropower Shutdown

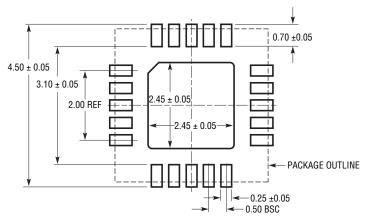

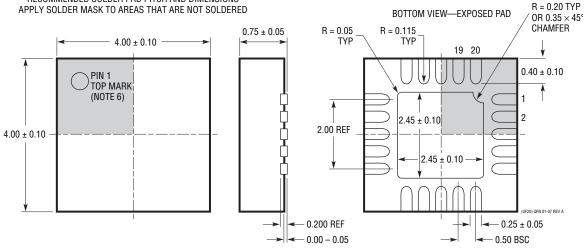

- 20-Pin 4mm × 4mm × 0.75mm QFN Package

#### **APPLICATIONS**

- Notebook Computers

- Portable Instruments

- Battery Backup Systems

∠T, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and PowerPath and ThinSOT are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 5723970.

#### DESCRIPTION

The LTC4012 is a constant-current/constant-voltage battery charger controller. It uses a synchronous quasi-constant frequency PWM control architecture that will not generate audible noise with ceramic bulk capacitors. Charge current is set by external resistors and can be monitored as an output voltage. With no built-in termination, the LTC4012 family charges a wide range of batteries under external control.

The LTC4012 features fully adjustable output voltage, while the LTC4012-1 and LTC4012-2 can be pin-programmed for Lithium-Ion/Polymer battery packs of 1-, 2-, 3- or 4-series cells. The LTC4012-1 provides output voltage of 4.1V/cell and the LTC4012-2 is a 4.2V/cell version.

The device includes AC adapter input current limiting, which maximizes charge rate for a fixed input power level. An external sense resistor programs the input current limit, and the  $\overline{ICL}$  status pin indicates reduced charge current as a result of AC adapter current limiting. Ideal diode control at the adaptor input improves charger efficiency.

The CHRG status pin is active during all charging modes, including special indication for low charge current.

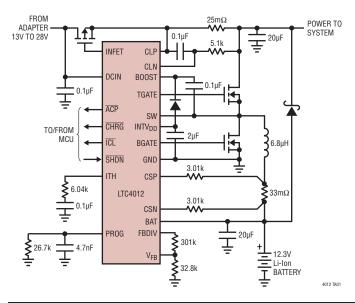

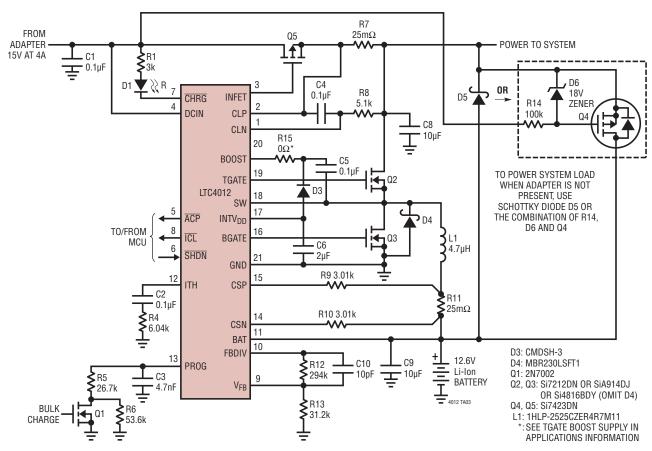

# TYPICAL APPLICATION

4012fa

# **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)               |             |

|------------------------|-------------|

| DCIN                   | 14V to 30V  |

| DCIN to CLP            | 32V to 20V  |

| CLP, CLN or SW to GND  | 0.3V to 30V |

| CLP to CLN             | ±0.3V       |

| CSP, CSN or BAT to GND | 0.3V to 28V |

| CSP to CSN             | ±0.3V       |

| BOOST to GND           | 0.3V to 36V |

| BOOST to SW            | 0.3V to 7V  |

|                        |             |

| SHDN, FVS0, FVS1 or V <sub>FB</sub> to |               |

|----------------------------------------|---------------|

| ACP, CHRG or ICL to GND                | 0.3V to 30V   |

| Operating Temperature Rang             | je            |

| (Note 2)                               | 40°C to 125°C |

| Junction Temperature (Note             | 3) 125°C      |

| Storage Temperature Range              | 65°C to 150°C |

|                                        |               |

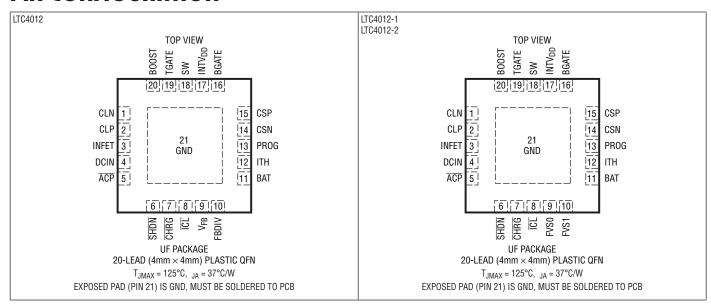

### PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------|-------------------|

| LTC4012CUF#PBF   | LTC4012CUF#TRPBF   | 4012          | 20-Lead (4mm × 4mm) Plastic QFN | 0°C to 85°C       |

| LTC4012CUF-1#PBF | LTC4012CUF-1#TRPBF | 40121         | 20-Lead (4mm × 4mm) Plastic QFN | 0°C to 85°C       |

| LTC4012CUF-2#PBF | LTC4012CUF-2#TRPBF | 40122         | 20-Lead (4mm × 4mm) Plastic QFN | 0°C to 85°C       |

| LTC4012IUF#PBF   | LTC4012IUF#TRPBF   | 4012          | 20-Lead (4mm × 4mm) Plastic QFN | -40°C to 125°C    |

| LTC4012IUF-1#PBF | LTC4012IUF-1#TRPBF | 40121         | 20-Lead (4mm × 4mm) Plastic QFN | -40°C to 125°C    |

| LTC4012IUF-2#PBF | LTC4012IUF-2#TRPBF | 40122         | 20-Lead (4mm × 4mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . DCIN = 20V, BAT = 12V, GND = 0V unless otherwise noted. (Note 2)

| SYMBOL                       | PARAMETER                                                                                                                                   | CONDITIONS                                                                                                                                                         |   | MIN                                             | TYP        | MAX                                       | UNITS            |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------------|------------|-------------------------------------------|------------------|

| Charge Vol                   | tage Regulation                                                                                                                             |                                                                                                                                                                    |   |                                                 |            |                                           |                  |

| V <sub>TOL</sub>             | V <sub>BAT</sub> Accuracy (See Test Circuits)                                                                                               | LTC4012<br>C-Grade<br>I-Grade                                                                                                                                      | • | -0.5<br>-0.8<br>-1.0                            |            | 0.5<br>0.8<br>1.0                         | %<br>%<br>%      |

|                              |                                                                                                                                             | LTC4012-1/LTC4012-2<br>C-Grade<br>FVS1 = 0V, FVS0 = 0V, I-Grade<br>FVS1 = 0V, FVS1 = 5V, I-Grade<br>FVS1 = 5V, FVS0 = 0V, I-Grade<br>FVS1 = 5V, FVS1 = 5V, I-Grade | • | -0.6<br>-0.8<br>-1.1<br>-1.15<br>-1.25<br>-1.35 |            | 0.6<br>0.8<br>1.1<br>1.15<br>1.25<br>1.35 | %<br>%<br>%<br>% |

| I <sub>VFB</sub>             | V <sub>FB</sub> Input Bias Current                                                                                                          | V <sub>FB</sub> = 1.2V                                                                                                                                             |   |                                                 | ±20        |                                           | nA               |

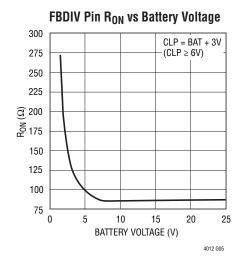

| R <sub>ON</sub>              | FBDIV On Resistance                                                                                                                         | $I_{LOAD} = 100 \mu A$                                                                                                                                             | • |                                                 | 85         | 190                                       | Ω                |

| I <sub>LEAK-FBDIV</sub>      | FBDIV Output Leakage Current                                                                                                                | SHDN = 0V, FBDIV = 0V                                                                                                                                              | • | -1                                              | 0          | 1                                         | μА               |

| $V_{BOV}$                    | V <sub>FB</sub> Overvoltage Threshold                                                                                                       | LTC4012                                                                                                                                                            | • | 1.235                                           | 1.281      | 1.32                                      | V                |

|                              | BAT Overvoltage Threshold                                                                                                                   | LTC4012-1/LTC4012-2, Relative to<br>Selected Output Voltage                                                                                                        | • | 103                                             | 106        | 109                                       | %                |

| Charge Cur                   | rent Regulation                                                                                                                             |                                                                                                                                                                    |   |                                                 |            |                                           |                  |

| I <sub>TOL</sub>             | Charge Current Accuracy with R <sub>IN</sub> = 3.01k,<br>6V < BAT < 18V (LTC4012)<br>6V < BAT < 15V (LTC4012-1, LTC4012-2)                  | R <sub>PROG</sub> = 26.7k<br>C-Grade<br>I-Grade                                                                                                                    | • | -4<br>-5<br>-9.5                                |            | 4<br>5<br>9.5                             | %<br>%<br>%      |

|                              |                                                                                                                                             | V <sub>SENSE</sub> = 0mV, PROG = 1.2V                                                                                                                              |   | -12.75                                          | -11.67     | -10.95                                    | μА               |

| A <sub>I</sub>               | Current Sense Amplifier Gain (PROG $\Delta$ I) with R <sub>IN</sub> = 3.01k, 6V < BAT < 18V (LTC4012) 6V < BAT < 15V (LTC4012-1, LTC4012-2) | V <sub>SENSE</sub> Step from 0mV to 5mV,<br>PROG = 1.2V                                                                                                            |   | -1.78                                           | -1.66      | -1.54                                     | μА               |

| V <sub>CS-MAX</sub>          | Maximum Peak Current Sense Threshold Voltage per Cycle (R <sub>IN</sub> = 3.01k)                                                            | ITH = 2V, C-Grade<br>ITH = 2V, I-Grade<br>ITH = 5V                                                                                                                 | • | 140<br>125                                      | 195<br>325 | 250<br>265<br>430                         | mV<br>mV<br>mV   |

| V <sub>C10</sub>             | C/10 Indicator Threshold Voltage                                                                                                            | PROG Falling                                                                                                                                                       |   | 340                                             | 400        | 460                                       | mV               |

| V <sub>REV</sub>             | Reverse Current Threshold Voltage                                                                                                           | PROG Falling                                                                                                                                                       |   | 180                                             | 253        | 295                                       | mV               |

| Input Curre                  | ent Regulation                                                                                                                              | ·                                                                                                                                                                  |   |                                                 |            |                                           |                  |

| V <sub>CL</sub>              | Current Limit Threshold                                                                                                                     | CLP – CLN<br>C-Grade<br>I-Grade                                                                                                                                    | • | 97<br>96<br>92                                  | 100<br>100 | 103<br>104<br>108                         | mV<br>mV<br>mV   |

| I <sub>CLN</sub>             | CLN Input Bias Current                                                                                                                      | CLN = CLP                                                                                                                                                          |   |                                                 | ±100       |                                           | nA               |

| V <sub>ICL</sub>             | ICL Indicator Threshold                                                                                                                     | (CLP – CLN) – V <sub>CL</sub>                                                                                                                                      |   | -8                                              | -5         | -2                                        | mV               |

| CLP Supply                   |                                                                                                                                             | , , , , , ,                                                                                                                                                        |   | l                                               |            |                                           | L                |

| OVR                          | Operating Voltage Range                                                                                                                     |                                                                                                                                                                    |   | 6                                               |            | 28                                        | V                |

| $\overline{V_{\text{UVLO}}}$ | CLP Undervoltage Lockout Threshold                                                                                                          | CLP Increasing                                                                                                                                                     | • | 4.65                                            | 4.85       | 5.25                                      | V                |

| V <sub>UV(HYST)</sub>        | UVLO Threshold Hysteresis                                                                                                                   |                                                                                                                                                                    |   |                                                 | 200        |                                           | mV               |

| I <sub>CLPO</sub>            | CLP Operating Current                                                                                                                       | CLP = 20V, No Gate Loads                                                                                                                                           |   |                                                 | 2          | 3                                         | mA               |

| Shutdown                     |                                                                                                                                             | ·                                                                                                                                                                  |   | ,                                               |            |                                           |                  |

| V <sub>ACP</sub>             | AC Present Threshold Voltage                                                                                                                | DCIN – BAT, DCIN Rising<br>C-Grade<br>I-Grade                                                                                                                      | • | 350<br>300                                      | 500        | 650<br>700                                | mV<br>mV         |

| V <sub>ACP(HYST)</sub>       | ACP Threshold Hysteresis Voltage                                                                                                            |                                                                                                                                                                    |   |                                                 | 200        |                                           | mV               |

| $V_{IL}$                     | SHDN Input Voltage Low                                                                                                                      |                                                                                                                                                                    | • |                                                 |            | 300                                       | mV               |

| $\overline{V_{IH}}$          | SHDN Input Voltage High                                                                                                                     |                                                                                                                                                                    | • | 1.4                                             |            |                                           | V                |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . DCIN = 20V, BAT = 12V, GND = 0V unless otherwise noted. (Note 2)

| SYMBOL                 | PARAMETER                                          | CONDITIONS                                                                       |   | MIN  | TYP       | MAX        | UNITS    |

|------------------------|----------------------------------------------------|----------------------------------------------------------------------------------|---|------|-----------|------------|----------|

| R <sub>IN</sub>        | SHDN Pull-Down Resistance                          |                                                                                  |   |      | 40        |            | kΩ       |

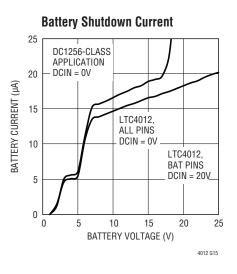

| I <sub>CLPS</sub>      | CLP Shutdown Current                               | CLP = 12V, DCIN = 0V<br>SHDN = 0V                                                | • |      | 15<br>350 | 26<br>500  | μA<br>μA |

| I <sub>LEAK-BAT</sub>  | BAT Leakage Current                                | $\overline{SHDN} = 0V \text{ or DCIN} = 0V,$<br>$0V \le CSP = CSN = BAT \le 18V$ | • | -1.5 | 0         | 1.5        | μА       |

| I <sub>LEAK-CSN</sub>  | CSN Leakage Current                                | $\overline{SHDN} = 0V \text{ or DCIN} = 0V,$<br>$0V \le CSP = CSN = BAT \le 20V$ | • | -1.5 | 0         | 1.5        | μА       |

| I <sub>LEAK-CSP</sub>  | CSP Leakage Current                                | $\overline{SHDN}$ = 0V or DCIN = 0V,<br>0V $\leq$ CSP = CSN = BAT $\leq$ 20V     | • | -1.5 | 0         | 1.5        | μА       |

| I <sub>LEAK-SW</sub>   | SW Leakage Current                                 | SHDN = 0V or DCIN = 0V,<br>0V ≤ SW ≤ 20V                                         | • | -1   | 0         | 2          | μА       |

| INTV <sub>DD</sub> Reg | gulator                                            | 1                                                                                |   |      |           |            |          |

| INTV <sub>DD</sub>     | Output Voltage                                     | No Load                                                                          | • | 4.85 | 5         | 5.15       | V        |

| $\Delta V_{DD}$        | Load Regulation                                    | I <sub>DD</sub> = 20mA                                                           |   |      | -0.4      | -1         | %        |

| $I_{DD}$               | Short-Circuit Current (Note 5)                     | INTV <sub>DD</sub> = 0V                                                          |   | 50   | 85        | 130        | mA       |

| Switching F            | Regulator                                          |                                                                                  |   |      |           |            |          |

| I <sub>ITH</sub>       | ITH Current                                        | ITH = 1.4V                                                                       |   |      | -40/+90   |            | μА       |

| $f_{TYP}$              | Typical Switching Frequency                        |                                                                                  |   | 467  | 550       | 633        | kHz      |

| f <sub>MIN</sub>       | Minimum Switching Frequency                        | C <sub>LOAD</sub> = 3.3nF                                                        |   | 20   | 25        |            | kHz      |

| DC <sub>MAX</sub>      | Maximum Duty Cycle                                 | C <sub>LOAD</sub> = 3.3nF                                                        |   | 98   | 99        |            | %        |

| t <sub>R-TG</sub>      | TGATE Rise Time                                    | C <sub>LOAD</sub> = 3.3nF, 10% – 90%                                             |   |      | 60        | 110        | ns       |

| t <sub>F-TG</sub>      | TGATE Fall Time                                    | C <sub>LOAD</sub> = 3.3nF, 90% – 10%                                             |   |      | 50        | 110        | ns       |

| t <sub>R-BG</sub>      | BGATE Rise Time                                    | C <sub>LOAD</sub> = 3.3nF, 10% – 90%                                             |   |      | 60        | 110        | ns       |

| t <sub>F-BG</sub>      | BGATE Fall Time                                    | C <sub>LOAD</sub> = 3.3nF, 90% – 10%                                             |   |      | 60        | 110        | ns       |

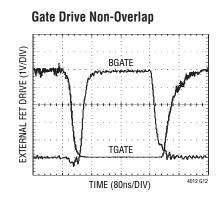

| $t_{NO}$               | TGATE, BGATE Non-Overlap Time                      | C <sub>LOAD</sub> = 3.3nF, 10% – 10%                                             |   |      | 110       |            | ns       |

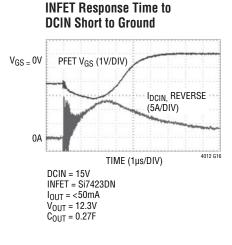

| PowerPath              | Control                                            |                                                                                  | • |      |           |            |          |

| I <sub>DCIN</sub>      | DCIN Input Current                                 | 0V ≤ DCIN ≤ CLP                                                                  | • | -10  |           | 60         | μА       |

| V <sub>FT0</sub>       | Forward Turn-On Voltage (DCIN Detection Threshold) | DCIN-CLP, DCIN rising                                                            | • | 15   |           | 60         | mV       |

| $\overline{V_{FR}}$    | Forward Regulation Voltage                         | DCIN-CLP                                                                         | • | 15   | 25        | 35         | mV       |

| $\overline{V_{RT0}}$   | Reverse Turn-Off Voltage                           | DCIN-CLP, DCIN falling                                                           | • | -45  | -25       | -15        | mV       |

| V <sub>OL(INFET)</sub> | INFET Output Low Voltage, Relative to CLP          | DCIN-CLP = 0.1V, I <sub>INFET</sub> =1µA                                         |   | -6.5 |           | <b>-</b> 5 | V        |

| V <sub>OH(INFET)</sub> | INFET Output High Voltage, Relative to CLP         | DCIN-CLP = $-0.1V$ , $I_{INFET} = -5\mu A$                                       |   | -250 |           | 250        | mV       |

| t <sub>IF(ON)</sub>    | INFET Turn-On Time                                 | To CLP-INFET > 3V, C <sub>INFET</sub> = 1nF                                      |   |      | 85        | 180        | μs       |

| t <sub>IF(OFF)</sub>   | INFET Turn-Off Time                                | To CLP-INFET < 1.5V, C <sub>INFET</sub> = 1nF                                    |   |      | 2.5       | 6          | μs       |

| Float Volta            | ge Select Inputs (LTC4012-1/LTC4012-2 Only)        |                                                                                  |   |      |           |            |          |

| $\overline{V_{IL}}$    | Input Voltage Low                                  |                                                                                  |   |      |           | 0.5        | V        |

| $V_{IH}$               | Input Voltage High                                 |                                                                                  |   | 3.5  |           |            | V        |

| I <sub>IN</sub>        | Input Current                                      | $0V \le V_{IN} \le 5V$                                                           |   | -10  |           | 10         | μА       |

| Indicator O            | utputs                                             |                                                                                  |   |      |           |            |          |

| $\overline{V_{0L}}$    | Output Voltage Low                                 | I <sub>LOAD</sub> = 100μA, PROG = 1.2V                                           |   |      |           | 500        | mV       |

| I <sub>LEAK</sub>      | Output Leakage                                     | SHDN = 0V, DCDIV = 0V,<br>V <sub>OUT</sub> = 20V                                 | • | -10  |           | 10         | μA       |

| I <sub>C10</sub>       | CHRG C/10 Current Sink                             | <u>CHRG</u> = 2.5V                                                               | • | 15   | 25        | 38         | μА       |

|                        | •                                                  | •                                                                                |   |      |           |            |          |

LINEAR TECHNOLOGY

4012fa

### **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC4012C is guaranteed to meet performance specifications over the 0°C to 85°C operating temperature range. The LTC4012I is guaranteed to meet performance specifications over the –40°C to 125°C operating temperature range.

**Note 3:** Operating junction temperature  $T_J$  (in °C) is calculated from the ambient temperature  $T_A$  and the total continuous package power dissipation  $P_D$  (in watts) by the formula  $T_J = T_A + (\theta_{JA} \cdot PD)$ . Refer to the Applications Information section for details.

**Note 4:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to GND, unless otherwise specified.

**Note 5:** Output current may be limited by internal power dissipation. Refer to the Applications Information section for details.

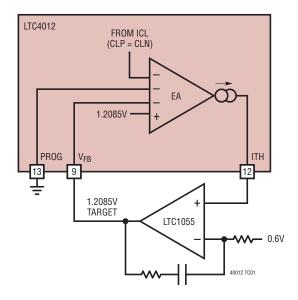

## **TEST CIRCUITS**

### TYPICAL PERFORMANCE CHARACTERISTICS

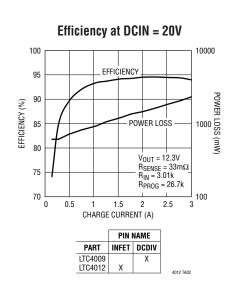

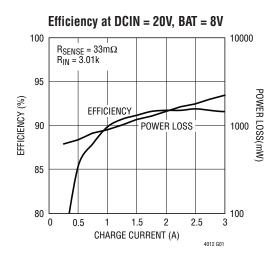

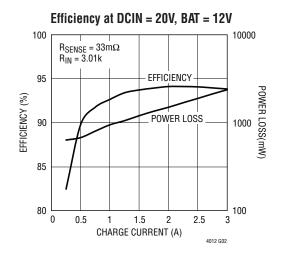

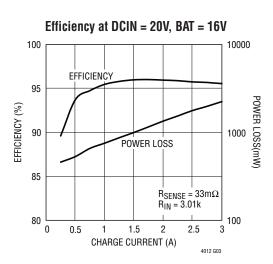

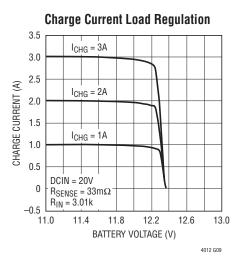

$(T_A = 25^{\circ}C \text{ unless otherwise noted. L} = IHLP-2525 6.8 \mu H)$

4012fa

### TYPICAL PERFORMANCE CHARACTERISTICS

4012 G08

$(T_A = 25^{\circ}C \text{ unless otherwise noted. } L = IHLP-2525 6.8 \mu\text{H})$

#### **Charge Current Line Regulation** 0.5 BAT = 6V $R_{SENSE} = 33m\Omega$ $R_{IN} = 3.01k$ 0.4 CHARGE CURRENT ERROR (%) 0.3 $I_{CHG} = 1A$ 0.2 0.1 I<sub>CHG</sub> = 2A 0 -0.1 $I_{CHG} = 3A$ -0.2 -0.3 -0.4-0.55 10 15 20 25 DCIN PIN VOLTAGE (V)

### PIN FUNCTIONS

**CLN (Pin 1):** Adapter Input Current Limit Negative Input. The LTC4012 senses voltage on this pin to determine if less charge current should be sourced to limit total input current. The threshold is set 100mV below the CLP pin. An external filter should be used to remove switching noise. This input should be tied to CLP if not used. Operating voltage range is (CLP – 110mV) to CLP.

**CLP (Pin 2):** Adapter Input Current Limit Positive Input. The LTC4012 also draws power from this pin, including a small amount for some shutdown functions. Operating voltage range is GND to 28V.

**INFET (Pin 3):** PowerPath Control Output. This output drives the gate of a PMOS pass transistor connected between the DC input (DCIN) and the raw system supply rail (CLP) to maintain a forward voltage of 25mV when a DC input source is present. INFET is internally clamped about 6V below CLP. Maximum operating voltage is CLP, which is used to turn off the input PMOS transistor when the DC input is removed.

**DCIN (Pin 4):** DC Sense Input. One of two voltage sense inputs to the internal PowerPath controller (the other input to the controller is CLP). This input is usually supplied from an input DC power source. Operating voltage ranges from GND to 28.2V.

**ACP** (**Pin 5**): Active-Low AC Adapter Present Indicator Output. This open-drain output pulls to GND when adequate AC adapter (DCIN) voltage is present. This output should be left floating if not used.

**SHDN** (**Pin 6**): Active-low Shutdown Input. Driving SHDN below 300mV unconditionally forces the LTC4012 into the shutdown state. This input has a  $40k\Omega$  internal pulldown to GND. Operating voltage range is GND to INTV<sub>DD</sub>.

**CHRG (Pin 7):** Active-Low Charge Indicator Output. This open-drain output provides three levels of information about charge status using a strong pull-down, 25µA weak pull-down or high impedance. Refer to the Operation and Applications Information sections for further details. This output should be left floating if not used.

**ICL** (**Pin 8**): Active-Low Input Current Limit Indicator Output. This open-drain output pulls to GND when the charge current is reduced because of AC adapter input current limiting. This output should be left floating if not used.

$V_{FB}$  (Pin 9, LTC4012): Battery Voltage Feedback Input. An external resistor divider between FBDIV and GND with the center tap connected to  $V_{FB}$  programs the charger output voltage. In constant voltage mode, this pin is nominally at 1.2085V. Refer to the Applications Information section for complete details on programming battery voltage. Operating voltage range is GND to 1.25V.

**FVSO** (Pin 9, LTC4012-1/LTC4012-2): Battery Voltage Select Input (LSB). This pin is one of two pins used on the LTC4012-1 or LTC4012-2 to select one of four preset battery voltages. Selection is done by connecting to either GND or INTV<sub>DD</sub>. Operating voltage range is GND to INTV<sub>DD</sub>.

**FBDIV** (Pin 10, LTC4012): Battery Voltage Feedback Resistor Divider Source. The LTC4012 connects this pin to BAT when charging is in progress. FBDIV is an opendrain PFET output to BAT with an operating voltage range of GND to BAT.

**FVS1 (Pin 10, LTC4012-1/LTC4012-2):** Battery Voltage Select Input (MSB). This pin is one of two pins used on the LTC4012-1 or LTC4012-2 to select one of four preset battery voltages. Selection is done by connecting to either GND or INTV<sub>DD</sub>. Operating voltage range is GND to INTV<sub>DD</sub>.

**BAT (Pin 11):** Battery Pack Connection. The LTC4012 uses the voltage on this pin to control PWM operation when charging. Operating voltage range is GND to CLN.

ITH (Pin 12): PWM Control Voltage and Compensation Node. The LTC4012 develops a voltage on this pin to control cycle-by-cycle peak inductor current. An external R-C network connected to ITH provides PWM loop compensation. Refer to the Applications Information section for further details on establishing loop stability. Operating voltage range is GND to INTV<sub>DD</sub>.

LINEAD TECHNOLOGY

### PIN FUNCTIONS

**PROG (Pin 13):** Charge Current Programming and Monitoring Pin. An external resistance connected between PROG and GND, along with the current sense and PWM input resistors, programs the maximum charge current. The voltage on this pin can also provide a linearized indicator of charge current. Refer to the Applications Information section for complete details on current programming and monitoring. Operating voltage range is GND to INTV<sub>DD</sub>.

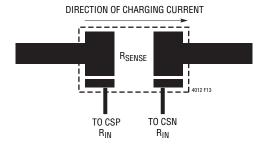

**CSN (Pin 14):** Charge Current Sense Negative Input. Place an external input resistor ( $R_{IN}$ , Figure 1) between this pin and the negative side of the charge current sense resistor. Operating voltage ranges from (BAT – 50mV) to (BAT + 200mV).

**CSP** (**Pin 15**): Charge Current Sense Positive Input. Place an external input resistor ( $R_{IN}$ , Figure 1) between this pin and the positive side of the charge current sense resistor. Operating voltage ranges from (BAT – 50mV) to (BAT + 200mV).

**BGATE (Pin 16):** External Synchronous NFET Gate Control Output. This output provides gate drive to an external NMOS power transistor switch used for synchronous rectification to increase efficiency in the step-down DC/DC converter. Operating voltage is GND to INTV<sub>DD</sub>. BGATE should be left floating if not used.

**INTV**<sub>DD</sub> (**Pin 17**): Internal 5V Regulator Output. This pin provides a means of bypassing the internal 5V regulator used to power the LTC4012 PWM FET drivers. This supply shuts down when the LTC4012 shuts down. Refer to the Application Information section for details if additional power is drawn from this pin by the application circuit.

**SW** (Pin 18): PWM Switch Node. The LTC4012 uses the voltage on this pin as the source reference for its topside NFET (PWM switch) driver. Refer to the Applications Information section for additional PCB layout suggestions related to this critical circuit node. Operating voltage range is GND to CLN.

**TGATE (Pin 19):** External NFET Switch Gate Control Output. This output provides gate drive to an external NMOS power transistor switch used in the DC/DC converter. Operating voltage range is GND to (CLN + 5V).

**BOOST (Pin 20):** TGATE Driver Supply Input. A bootstrap capacitor is returned to this pin from a charge network connected to SW and INTV<sub>DD</sub>. Refer to the Applications Information section for complete details on circuit topology and component values. Operating voltage ranges from (INTV<sub>DD</sub> - 1V) to (CLN + 5V).

**GND** (Exposed Pad Pin 21): Ground. The package paddle provides a single-point ground for the internal voltage reference and other critical LTC4012 circuits. It must be soldered to a suitable PCB copper ground pad for proper electrical operation and to obtain the specified package thermal resistance.

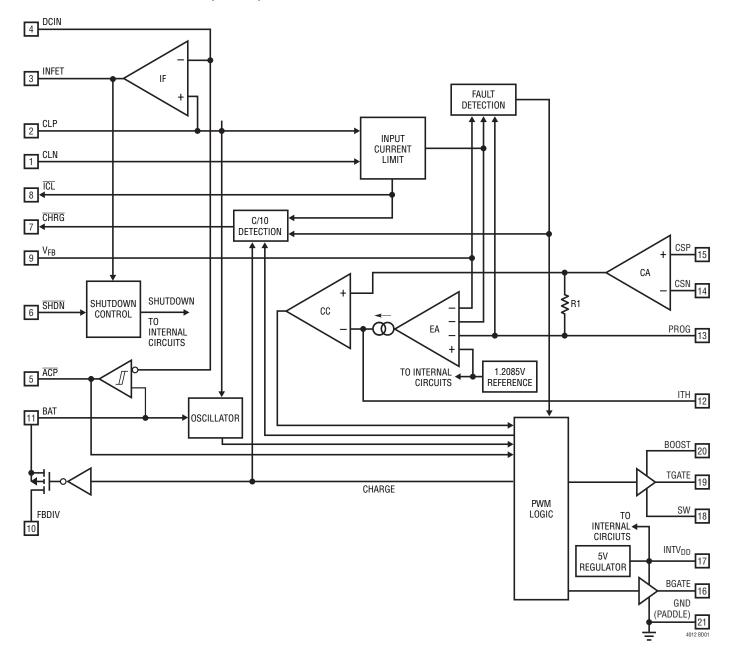

# **BLOCK DIAGRAM** (LTC4012)

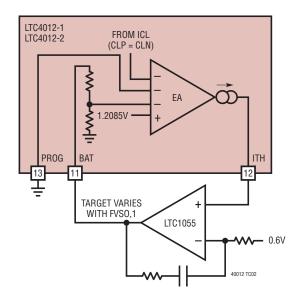

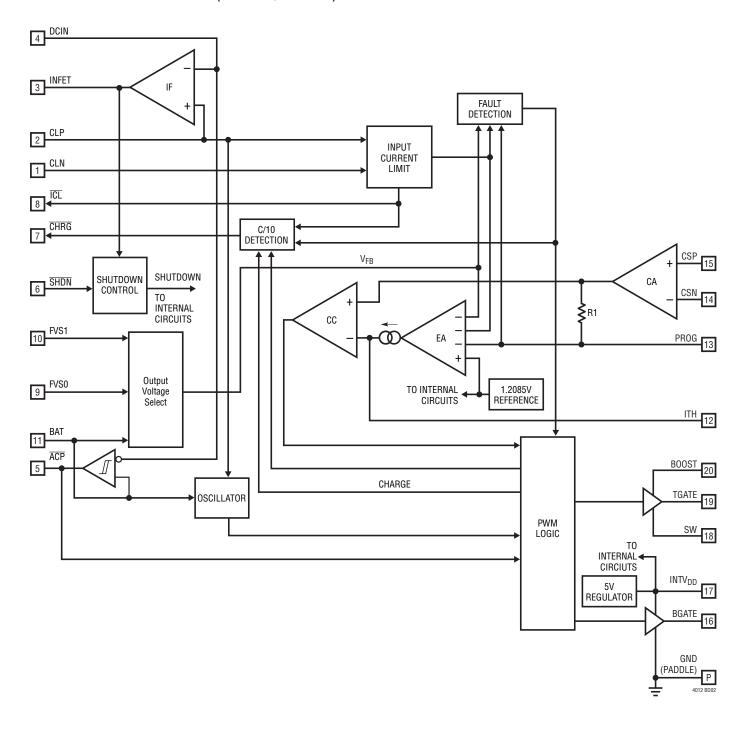

# **BLOCK DIAGRAM** (LTC4012-1/LTC4012-2)

#### **Overview**

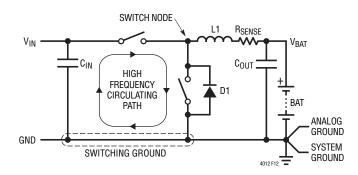

The LTC4012 is a synchronous step-down (buck) current mode PWM battery charger controller. The maximum charge current is programmed by the combination of a charge current sense resistor ( $R_{SENSE}$ ), matched input resistors ( $R_{IN}$ , Figure 1), and a programming resistor ( $R_{PROG}$ ) between the PROG and GND pins. Battery voltage is programmed with an external resistor divider between FBDIV and GND (LTC4012) or two digital battery voltage select pins (LTC4012-1/LTC4012-2). In addition, the PROG pin provides a linearized voltage output of the actual charge current.

The LTC4012 family does not have built-in charge termination and is flexible enough for charging any type of battery chemistry. These are building block ICs intended for use with an external circuit, such as a microcontroller, capable of managing the entire algorithm required for the specific battery being charged. Each member of the LTC4012 family features a shutdown input and various state indicator outputs, allowing easy and direct management by a wide range of external (digital) charge controllers. Due to the popularity of rechargeable Lithium-Ion chemistries, the LTC4012-1 and LTC4012-2 also offer internal precision resistors that can be digitally selected to produce one of four preset output voltages for simplified design of those charger types.

#### Shutdown

The LTC4012 remains in shutdown until DCIN is greater than 5.1V and exceeds CLP by 60mV and  $\overline{SHDN}$  is driven above 1.4V. In shutdown, current drain from the battery is reduced to the lowest possible level, thereby increasing standby time. When in shutdown, the ITH pin is pulled to GND and  $\overline{CHRG}$ ,  $\overline{ICL}$ , FET gate drivers and  $\overline{INTV_{DD}}$  output are all disabled. The charging can be stopped at any time by forcing  $\overline{SHDN}$  below 300mV.

#### **AC Present Indication**

The ACP status output correctly indicates sensed adapter input voltage during all LTC4012 states. AC present is indicated (ACP output low) as soon as DCIN exceeds BAT by at least 500mV. Charging is not enabled until this condition is first met. After this event, charging is no longer

gated by AC present detection. If battery voltage rises due to ESR, or DCIN droops due to current load, AC present may no longer be indicated by the IC if charging was started with very low input overhead. However, charging will remain enabled unless DCIN falls below the supply voltage on CLP.

#### **Input PowerPath Control**

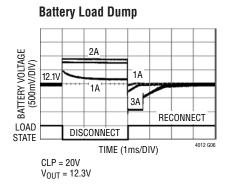

The input PFET controller performs many important functions. First, it monitors DCIN and enables the charger when this input voltage is higher than the raw CLP system supply. Next, it controls the gate of an external input power PFET to maintain a low forward voltage drop when charging, creating improved efficiency. It also prevents reverse current flow through this same PFET, providing a suitable input blocking function. Finally, it helps avoid synchronous boost operation during invalid operating conditions by detecting elevated CLP voltage and forcing the charger off.

If DCIN voltage is less than CLP, then DCIN must rise 60mV higher than CLP to enable the charger and activate the ideal diode control. At this point, the ACPb status output also transitions to low impedance to indicate to the host system that an external adapter is present. The gate of the input PFET is driven to a voltage sufficient to regulate a forward drop between DCIN and CLP of about 25mV. If the input voltage differential drops below this point, the FET is turned off slowly. If the voltage between DCIN and CLP drops to less than –25mV, the input FET is turned off in less than 6µs to prevent significant reverse current from flowing back through the PFET. In this case, ACPb also switches back to high impedance and the charger is disabled.

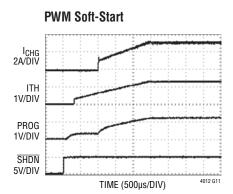

#### **Soft-Start**

Exiting the shutdown state enables the charger and releases the ITH pin. When enabled, switching will not begin until DCIN exceeds BAT by 500mV and ITH exceeds a threshold that assures initial current will be positive (about 5% to 25% of the maximum programmed current). To limit inrush current, soft-start delay is created with the compensation values used on the ITH pin. Longer soft-start times can be realized by increasing the filter capacitor on ITH, if reduced loop bandwidth is acceptable. The actual charge current at

12

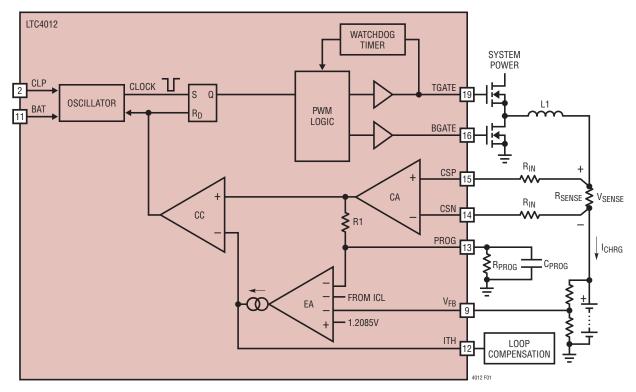

Figure 1. PWM Circuit Diagram

the end of soft-start will depend on which loop (current, voltage or adapter limit) is in control of the PWM. If this current is below that required by the ITH start-up threshold, the resulting charge current transient duration depends on loop compensation but is typically less than 100µs.

#### **Bulk Charge**

When soft-start is complete, the LTC4012 begins sourcing the current programmed by the external components connected to CSP, CSN and PROG. Some batteries may require a small conditioning trickle current if they are heavily discharged. As shown in the Applications Information section, the LT4012 can address this need through a variety of low current circuit techniques on the PROG pin. Once a suitable cell voltage has been reached, charge current can be switched to a higher, bulk charge value.

#### End of Charge and CHRG Output

As the battery approaches the programmed output voltage, charge current will begin to decrease. The open-drain CHRG output can indicate when the current drops to 10% of its programmed full-scale value by turning off the strong

pull-down (open-drain FET) and turning on a weak  $25\mu A$  pull-down current. This weak pull-down state is latched until the part enters shutdown or the sensed current rises to roughly C/6. C/10 indication will not be set if charge current has been reduced due to adapter input current limiting. As the charge current approaches OA, the PWM continues to operate in full continuous mode. This avoids generation of audible noise, allowing bulk ceramic capacitors to be used in the application.

#### **Charge Current Monitoring**

When the LTC4012 is charging, the voltage on the PROG pin varies in direct proportion to the charge current. Referring to Figure 1, the nominal PROG voltage is given by

$$V_{PROG} = \frac{I_{CHRG} \bullet R_{SENSE} \bullet R_{PROG}}{R_{IN}} + 11.67 \mu A \bullet R_{PROG}$$

Voltage tolerance on PROG is limited by the charge current accuracy specified in the Electrical Characteristics table. Refer to the Applications Information section on programming charge current for additional details.

#### **Adapter Input Current Limit**

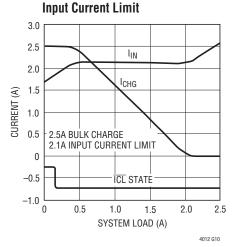

The LTC4012 can monitor and limit current from the input DC supply, which is normally an AC adapter. When the programmed adapter input current is reached, charge current is reduced to maintain the desired maximum input current. The ITH and PROG pins will reflect the reduced charge current. This limit function avoids overloading the DC input source, allowing the product to operate at the same time the battery is charging without complex load management algorithms. The battery will automatically be charged at the maximum possible rate that the adapter will support, given the application's operating condition. The LTC4012 can only limit input current by reducing charge current, and in this case the charger uses nonsynchronous PWM operation to prevent boosting if the average charge current falls below about 25% of the maximum programmed current. Note that the ICL indicator output becomes active (low) at an adapter input current level just slightly less than that required for the internal amplifier to begin to assert control over the PWM loop.

#### **Charger Status Indicator Outputs**

The LTC4012 open-drain indicator outputs provide valuable information about the IC's operating state and can be used for a variety of purposes in applications. Table 1 summarizes the state of the three indicator outputs as a function of LTC4012 operation.

Table 1. LTC4012 Open-Drain Indicator Outputs

| ACP | CHRG          | ĪCL          | CHARGER STATE                                                                            |

|-----|---------------|--------------|------------------------------------------------------------------------------------------|

| Off | Off           | Off          | No DC Input (Shutdown)                                                                   |

| On  | Off           | Off          | Shutdown or Reverse Current                                                              |

| On  | On            | Off          | Bulk Charge                                                                              |

| On  | 25μΑ          | Off          | Low Current Charge or Initial<br>DCIN – BAT <500mV                                       |

| On  | On            | On           | Input Current Limit During Bulk<br>Charge                                                |

| On  | 25μΑ          | On           | Input Current Limit During Low<br>Current Charge                                         |

| Off | On or<br>25µA | On or<br>Off | Indicated Charge with DCIN - BAT < 300mV. Bulk charge may be less than programmed value. |

#### **PWM Controller**

The LTC4012 uses a synchronous step-down architecture to produce high operating efficiency. The nominal operating frequency of 550kHz allows use of small filter components. The following conceptual discussion of basic PWM operation references Figure 1.

The voltage across the external charge current sense resistor  $R_{SENSE}$  is measured by current amplifier CA. This instantaneous current ( $V_{SENSE}/R_{IN}$ ) is fed to the PROG pin where it is averaged by an external capacitor and converted to a voltage by the programming resistor  $R_{PROG}$  between PROG and GND. The PROG voltage becomes the average charge current input signal to error amplifier EA. EA also receives loop control information from the battery voltage feedback input  $V_{FB}$  and the adapter input current limit circuit.

4012fa

The ITH output of the error amplifier is a scaled control voltage for one input of the PWM comparator CC. ITH sets a peak inductor current threshold, sensed by R1, to maintain the desired average current through  $R_{SENSE}$ . The current comparator output does this by switching the state of the RS latch at the appropriate time.

At the beginning of each oscillator cycle, the PWM clock sets the RS latch and turns on the external top-side NFET (bottom-side synchronous NFET off) to refresh the current carried by the external inductor L1. The inductor current and voltage across R<sub>SENSE</sub> begin to rise linearly. CA buffers this instantaneous voltage rise and applies it to CC with gain supplied by R1. When the voltage across R1 exceeds the peak level set by the ITH output of EA, the top FET turns off and the bottom FET turns on. The inductor current then ramps down linearly until the next rising PWM clock edge. This closes the loop and sources the correct inductor current to maintain the desired parameter (charge current, battery voltage, or input current). To produce a near constant frequency, the PWM oscillator implements the equation:

$$t_{OFF} = \frac{CLP - BAT}{CLP \bullet 550 \text{kHz}}$$

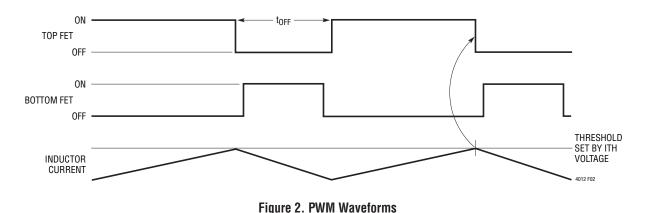

Repetitive, closed-loop waveforms for stable PWM operation appear in Figure 2.

#### **PWM Watchdog Timer**

As input and output conditions vary, the LTC4012 may need to utilize PWM duty cycles approaching 100%. In this case, operating frequency may be reduced well below 550kHz. An internal watchdog timer observes the activity on the TGATE pin. If TGATE is on for more than 40µs, the watchdog activates and forces the bottom NFET on (top NFET off)

for about 100ns. This avoids a potential source of audible noise when using ceramic input or output capacitors and prevents the boost supply capacitor for the top gate driver from discharging. In low drop out operation, the actual charge current may not be able to reach the programmed full-scale value due to the watchdog function.

#### **Overvoltage Protection**

The LTC4012 also contains overvoltage detection that prevents transient battery voltage overshoots of more than about 6% above the programmed output voltage. When battery overvoltage is detected, both external MOSFETs are turned off until the overvoltage condition clears, at which time a new soft start sequence begins. This is useful for properly charging battery packs that use an internal switch to disconnect themselves for performing functions such as calibration or pulse mode charging.

#### **Reverse Charge Current Protection (Anti-Boost)**

Because the LTC4012 always attempts to operate synchronously in full continuous mode (to avoid audible noise from ceramic capacitors), reverse average charge current can occur during some invalid operating conditions. INFET PowerPath control avoids boosting a lightly loaded system supply during reverse operation. However, under heavier system loads, CLP may not boost above DCIN, even though reverse average current is flowing. In this case a second circuit monitors indication of reverse average current on PROG.

If either of these circuits detects boost operation, The LTC4012 turns off both external MOSFETs until the reverse current condition clears. At that point, a new soft-start sequence begins.

#### **Programming Charge Current**

The formula for charge current is:

$$I_{CHRG} = \frac{R_{IN}}{R_{SENSE}} \bullet \left( \frac{1.2085V}{R_{PROG}} - 11.67\mu A \right)$$

The LTC4012 operates best with 3.01k input resistors, although other resistors near this value can be used to accommodate standard sense resistor values. Refer to the subsequent discussion on inductor selection for other considerations that come into play when selecting input resistors  $R_{\text{IN}}$ .

R<sub>SENSE</sub> should be chosen according to the following equation:

$$R_{SENSE} = \frac{100mV}{I_{MAX}}$$

where  $I_{MAX}$  is the desired maximum charge current  $I_{CHRG}$ . The 100mV target can be adjusted to some degree to obtain standard  $R_{SENSE}$  values and/or a desired  $R_{PROG}$  value, but target voltages lower than 100mV will cause a proportional reduction in current regulation accuracy.

The required minimum resistance between PROG and GND can be determined by applying the suggested expression for  $R_{SENSE}$  while solving the first equation given above for charge current with  $I_{CHRG} = I_{MAX}$ :

$$R_{PROG(MIN)} = \frac{1.2085V \cdot R_{IN}}{0.1V + 11.67\mu A \cdot R_{IN}}$$

If  $R_{IN}$  is chosen to be 3.01k with a sense voltage of 100mV, this equation indicates a minimum value for  $R_{PROG}$  of 26.9k. Table 6 gives some examples of recommended charge current programming component values based on these equations.

The resistance between PROG and GND can simply be set with a single a resistor, if only maximum charge current needs to be controlled during the desired charging algorithm.

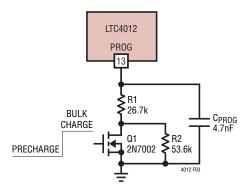

However, some batteries require a low charge current for initial conditioning when they are heavily discharged. The charge current can then be safely switched to a higher level after conditioning is complete. Figure 3 illustrates one method of doing this with 2-level control of the PROG pin resistance. Turning Q1 off reduces the charge current to  $I_{MAX}/10$  for battery conditioning. When Q1 is on, the LTC4012 is programmed to allow full  $I_{MAX}$  current for bulk charge. This technique can be expanded through the use of additional digital control inputs for an arbitrary number of pre-programmed current values.

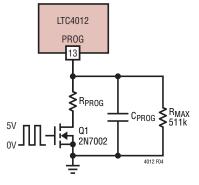

For a truly continuous range of maximum charge current control, pulse width modulation can be used as shown in Figure 4.

Figure 3. Programming 2-Level Charge Current

Figure 4. Programming PWM Current

The value of R<sub>PROG</sub> controls the maximum value of charge current which can be programmed (Q1 continuously on). PWM of the Q1 gate voltage changes the value of R<sub>PROG</sub> to produce lower currents. The frequency of this modulation should be higher than a few kHz, and C<sub>PROG</sub> must be increased to reduce the ripple caused by switching Q1. In addition, it may be necessary to increase loop compensation capacitance connected to ITH to maintain stability or prevent large current overshoot during start-up. Selecting a higher Q1 PWM frequency ( $\approx$ 10kHz) will reduce the need to change C<sub>PROG</sub> or other compensation values. Charge current will be proportional to the duty cycle of the PWM input on the gate of Q1.

#### **Programming LTC4012 Output Voltage**

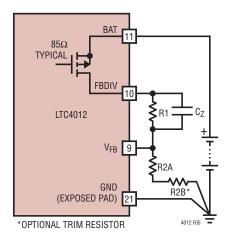

Figure 5 shows the external circuit for programming the charger voltage when using the LTC4012. The voltage is then governed by the following equation:

$$V_{BAT} = \frac{1.2085V \cdot (R1 + R2)}{R2}, R2 = R2A + R2B$$

Figure 5. Programming Output Voltage

See Table 2 for approximate resistor values for R2.

$$R1 = R2 \left( \frac{V_{BAT}}{1.2085V} - 1 \right), R2 = R2A + R2B$$

Selecting R2 to be less than 50k and the sum of R1 and R2 at least 200k or above, achieves the lowest possible error at the V<sub>FR</sub> sense input. Note that sources of error such as R1 and R2 tolerance, FBDIV R<sub>ON</sub> or V<sub>FB</sub> input impedance are not included in the specifications given in the Electrical Characteristics. This leads to the possibility that very accurate (0.1%) external resistors might be required. Actually, the temperature rise of the LTC4012 will rarely exceed 50°C at the end of charge, because charge current will have tapered to a low level. This means that 0.25% resistors will normally provide the required level of overall accuracy. Table 2 gives recommended values for R1 and R2 for popular lithium-ion battery voltages. For values of R1 above 200k, addition of capacitor C7 may improve transient response and loop stability. A value of 10pF is normally adequate.

Table 2. Programming Output Voltage

| _                       |                    |                     |                  |

|-------------------------|--------------------|---------------------|------------------|

| V <sub>BAT</sub><br>(V) | R1 (0.25%)<br>(kΩ) | R2A (0.25%)<br>(kΩ) | R2B (1%)*<br>(Ω) |

| 4.1                     | 165                | 69                  | _                |

| 4.2                     | 167                | 67.3                | 200              |

| 8.2                     | 162                | 28                  | -                |

| 8.4                     | 169                | 28.4                | _                |

| 12.3                    | 301                | 32.8                | _                |

| 12.6                    | 294                | 31.2                | -                |

| 16.4                    | 284                | 22.6                | -                |

| 16.8                    | 271                | 21                  | _                |

| 20.5                    | 316                | 19.8                | -                |

| 21                      | 298                | 18.2                | -                |

| 24.6                    | 298                | 15.4                | -                |

| 25.2                    | 397                | 20                  | -                |

<sup>\*</sup>To Obtain Desired Accuracy Requires Series Resistors For R2.

#### Programming LTC4012-1/LTC4012-2 Output Voltage

The LTC4012-1/LTC4012-2 feature precision internal battery voltage feedback resistor taps configured for common lithium-ion voltages. All that is required to program the desired voltage is proper pin programming of FVS0 and FVS1 as shown in Table 3.

Table 3. LTC4012-1/LTC4012-2 Output Voltage Programming

| V <sub>BAT</sub> VOLTAGE |           |                    |                    |

|--------------------------|-----------|--------------------|--------------------|

| LTC4012-1                | LTC4012-2 | FVS1               | FVS0               |

| 4.1V                     | 4.2V      | GND                | GND                |

| 8.2V                     | 8.4V      | GND                | INTV <sub>DD</sub> |

| 12.3V                    | 12.6V     | INTV <sub>DD</sub> | GND                |

| 16.4V                    | 16.8V     | INTV <sub>DD</sub> | INTV <sub>DD</sub> |

#### **Programming Input Current Limit**

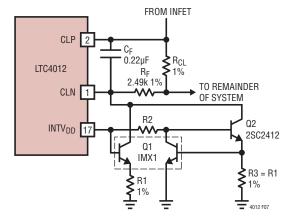

To set the input current limit  $I_{LIM}$ , the minimum wall adapter current rating must be known. To account for the tolerance of the LTC4012 input current sense circuit, 5% should be subtracted from the adapter's minimum rated output. Refer to Figure 6 and program the input current limit function with the following equation.

$$R_{CL} = \frac{100mV}{I_{LIM}}$$

where  $I_{LIM}$  is the desired maximum current draw from the DC (adapter) input, including adjustments for tolerance, if any.

Figure 6. Programming Input Current Limit

Often an AC adapter will include a rated current output margin of at least +10%. This can allow the adapter current limit value to simply be programmed to the actual minimum rated adapter output current. Table 4 shows some common  $R_{Cl}$  current limit programming values.

A lowpass filter formed by  $R_F$  (5.1k) and  $C_F$  (0.1 $\mu F)$  is required to eliminate switching noise from the LTC4012 PWM and other system components. If input current limiting is not desired, CLN should be shorted to CLP while CLP remains connected to power.

Table 4. Common R<sub>CL</sub> Values

| ADAPTER<br>Rating<br>(A) | R <sub>CL</sub> VALUE (1%)<br>(Ω) | R <sub>CL</sub> POWER<br>DISSIPATION<br>(W) | R <sub>CL</sub> POWER<br>Rating<br>(W) |

|--------------------------|-----------------------------------|---------------------------------------------|----------------------------------------|

| 1.00                     | 0.100                             | 0.100                                       | 0.25                                   |

| 1.25                     | 0.080                             | 0.125                                       | 0.25                                   |

| 1.50                     | 0.068                             | 0.150                                       | 0.25                                   |

| 1.75                     | 0.056                             | 0.175                                       | 0.25                                   |

| 2.00                     | 0.050                             | 0.200                                       | 0.25                                   |

| 2.50                     | 0.039                             | 0.244                                       | 0.50                                   |

| 3.00                     | 0.033                             | 0.297                                       | 0.50                                   |

| 3.50                     | 0.027                             | 0.331                                       | 0.50                                   |

| 4.00                     | 0.025                             | 0.400                                       | 0.50                                   |

Figure 7 shows an optional circuit that can influence the parameters of the input current limit in two ways.

Figure 7. Adjusting Input Current Limit

LINEAD

The first option is to lower the power dissipation of  $R_{CL}$  at the expense of accuracy without changing the input current limit value. The second is to make the input current limit value programmable.

The overall accuracy of this circuit needs to be better than the power source current tolerance or be margined such that the worse-case error remains under the power source limits.

The accuracy of the Figure 7 circuit is a function of the INTV<sub>DD</sub>, V<sub>BE</sub>, R<sub>CL</sub>, R<sub>F</sub>, R1 and R3 tolerances. To improve accuracy, the tolerance of R<sub>F</sub> should be changed from 5.1k, 5% to a 2.49k 1% resistor. R<sub>CL</sub> and the programming resistors R1 and R3 should also be 1% tolerance such that the dominant error is INTV<sub>DD</sub> (±3%). Bias resistor R2 can be 5%. When choosing NPN transistors, both need to have good gain (>100) at 10 $\mu$ A levels. Low gain NPNs will increase programming errors. Q1 must be a matched NPN pair. Since R<sub>F</sub> has been reduced in value by half, the capacitor value of C<sub>F</sub> should double to 0.22 $\mu$ F to remain effective at filtering out any noise.

If you wish to reduce R<sub>CL</sub> power dissipation for a given current limit, the programming equation becomes:

$$R_{CL} = \frac{100\text{mV} - \left(\frac{5 \cdot 2.49\text{k}}{\text{R1}}\right)}{I_{LIM}}$$

If you wish to make the input current limit programmable, the equation becomes:

$$I_{LIM} = \frac{100\text{mV} - \left(\frac{5 \cdot 2.49\text{k}}{\text{R1}}\right)}{R_{CI}}$$

The equation governing R2 for both applications is based on the value of R1. R3 should always be equal to R1.

$$R2 = 0.875 \cdot R1$$

In many notebook applications, there are situations where two different  $I_{LIM}$  values are needed to allow two different power adapters or power sources to be used. In such cases, start by setting  $R_{LIM}$  for the high power  $I_{LIM}$  configuration and then use Figure 7 to set the lower  $I_{LIM}$  value. To toggle between the two  $I_{LIM}$  values, take the three ground connections shown in Figure 7, combine them into one common connection and use a small-signal NFET (2N7002) to open or close that common connection to circuit ground. When the NFET is off, the circuit is defeated (floating) allowing  $I_{LIM}$  to be the maximum value. When the NFET is on, the circuit will become active and  $I_{LIM}$  will drop to the lower set value.

#### **Monitoring Charge Current**

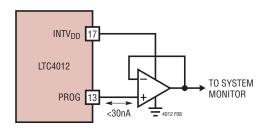

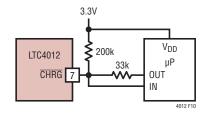

The PROG pin voltage can be used to indicate charge current where 1.2085V indicates full programmed current (1C) and zero charge current is approximately equal to  $R_{PROG} \bullet 11.67 \mu A$ . PROG voltage varies in direct proportion to the charge current between this zero-current (offset) value and 1.2085V. When monitoring the PROG pin voltage, using a buffer amplifier as shown in Figure 8 will minimize charge current errors. The buffer amplifier may be powered from the INTV\_DD pin or any supply that is always on when the charger is on.

Figure 8. PROG Voltage Buffer

#### C/10 CHRG Indicator

The value chosen for  $R_{PROG}$  has a strong influence on charge current monitoring and the accuracy of the C/10 charge indicator output (CHRG). The LTC4012 uses the voltage on the PROG pin to determine when charge current has dropped to the C/10 threshold. The nominal threshold of 400mV produces an accurate low charge current indication of C/10 as long as  $R_{PROG} = 26.7 k$ , independent of all other current programming considerations. However, it may sometimes be necessary to deviate from this value to satisfy other application design goals.

If  $R_{PROG}$  is greater than 26.7k, the actual level at which low charge current is detected will be less than C/10. The highest value of  $R_{PROG}$  that can be used while reliably indicating low charge current before reaching final  $V_{BAT}$  is 30.1k.  $R_{PROG}$  can safely be set to values higher than this, but low current indication will be lost.

If  $R_{PROG}$  is less than 26.7k, low charge current detection occurs at a level higher than C/10. More importantly, the LTC4012 becomes increasingly sensitive to reverse current. The lowest value of  $R_{PROG}$  that can be used without the risk of erroneous boost operation detection at end of charge is 26.1k. Values of  $R_{PROG}$  less than this should not be used. See the Operation section for more information about reverse current.

The nominal fractional value of  $I_{MAX}$  at which C/10 indication occurs is given by:

$$\frac{I_{C10}}{I_{MAX}} = \frac{400 \text{mV} - \left(R_{PROG} \bullet 11.67 \mu A\right)}{1.2085 \text{V} - \left(R_{PROG} \bullet 11.67 \mu A\right)}$$

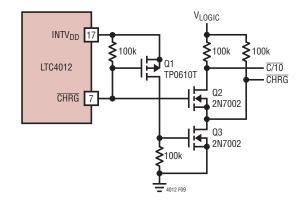

Direct digital monitoring of C/10 indication is possible with an external application circuit like the one shown in Figure 9.

By using two different value pull-up resistors, a microprocessor can detect three states from this pin (charging, C/10 and not charging). See Figure 10. When a digital output port (OUT) from the microprocessor drives one of the resistors and a second digital input port polls the network, the charge state can be determined as shown in Table 5.

Table 5. Digital Read Back State (IN, Figure 10)

| LTC4012       | OUT  | STATE |

|---------------|------|-------|

| CHARGER STATE | Hi-Z | 1     |

| Off           | 1    | 1     |

| C/10 Charge   | 0    | 1     |

| Bulk Charge   | 0    | 0     |

#### **Input and Output Capacitors**

In addition to typical input supply bypassing  $(0.1\mu F)$  on DCIN, the relatively high ESR of aluminum electrolytic capacitors is helpful for reducing ringing when hot-plugging the charger to the AC adapter. Refer to LTC Application Note 88 for more information.

The input capacitor between system power (drain of top FET, Figure 1) and GND is required to absorb all input PWM ripple current, therefore it must have adequate ripple current rating. Maximum RMS ripple current is typically one-half of the average battery charge current. Actual capacitance value is not critical, but using the highest possible voltage rating on PWM input capacitors will minimize problems. Consult with the manufacturer before use.

Figure 9. Digital C/10 Indicator

Figure 10. Microprocessor Status Interface

4012fa

The output capacitor shown across the battery and ground must also absorb PWM output ripple current. The general formula for this capacitor current is:

$$I_{RMS} = \frac{0.29 \bullet V_{BAT} \bullet \left(1 - \frac{V_{BAT}}{V_{CLP}}\right)}{L1 \bullet f_{PWM}}$$

For example,  $I_{RMS} = 0.22A$  with:

$V_{BAT} = 12.6V$

$V_{CIP} = 19V$

$L1 = 10 \mu H$

$f_{PWM} = 550kHz$

High capacity ceramic capacitors ( $20\mu\text{F}$  or more) available from a variety of manufacturers can be used for input/output capacitors. Other alternatives include OS-CON and POSCAP capacitors from Sanyo.

Low ESR solid tantalum capacitors have high ripple current rating in a relatively small surface mount package, but exercise caution when using tantalum for input or output bulk capacitors. High input surge current can be created when the adapter is hot-plugged to the charger or when a battery is connected to the charger. Solid tantalum capacitors have a known failure mechanism when subjected to very high surge currents. Select tantalum capacitors that have high surge current ratings or have been surge tested.

EMI considerations usually make it desirable to minimize ripple current in battery leads. Adding Ferrite beads or inductors can increase battery impedance at the nominal 550KHz switching frequency. Switching ripple current splits between the battery and the output capacitor in inverse relation to capacitor ESR and the battery impedance. If the ESR of the output capacitor is  $0.2\Omega$  and the battery impedance is raised to  $4\Omega$  with a ferrite bead, only 5% of the current ripple will flow to the battery.

#### **Inductor Selection**

Higher switching frequency generally results in lower efficiency because of MOSFET gate charge losses, but it allows smaller inductor and capacitor values to be used. A primary effect of the inductor value L1 is the amplitude of ripple current created. The inductor ripple current  $\Delta I_L$  decreases with higher inductance and PWM operating frequency:

$$\Delta I_{L} = \frac{V_{BAT} \cdot \left(1 - \frac{V_{BAT}}{V_{CLP}}\right)}{L1 \cdot f_{PWM}}$$

Accepting larger values of  $\Delta I_L$  allows the use of low inductance, but results in higher output voltage ripple and greater core losses. Lower charge currents generally call for larger inductor values.

The LTC4012 limits maximum instantaneous peak inductor current during every PWM cycle. To avoid unstable switch waveforms, the ripple current must satisfy:

$$\Delta I_{L} < 2 \bullet \left( \frac{150 \text{mV}}{R_{SENSE}} - I_{MAX} \right)$$

so choose:

$$L1 > \frac{0.125 \bullet V_{CLP}}{f_{PWM} \bullet \left(\frac{150 mV}{R_{SENSE}} - I_{MAX}\right)}$$

For C-grade parts, a reasonable starting point for setting ripple current is  $\Delta I_L = 0.4 \cdot I_{MAX}$ . For I-grade parts, use  $\Delta I_L = 0.2 \cdot I_{MAX}$  only if the IC will actually be used to charge batteries over the wider I-grade temperature range. The voltage compliance of internal LTC4012 circuits also imposes limits on ripple current. Select  $R_{IN}$  (in Figure 1) to avoid average current errors in high ripple designs. The following equation can be used for guidance:

$$\frac{R_{SENSE} \bullet \Delta I_L}{50 \mu A} \le R_{IN} \le \frac{R_{SENSE} \bullet \Delta I_L}{20 \mu A}$$

$R_{IN}$  should not be less than 2.37k or more than 6.04k. Values of  $R_{IN}$  greater than 3.01k may cause some reduction in programmed current accuracy. Use these equations and guidelines, as represented in Table 6, to help select the correct inductor value. This table was developed for C-grade parts to maintain maximum  $\Delta I_L$  near  $0.6 \cdot I_{MAX}$  with  $f_{PWM}$  at 550kHz and  $V_{BAT} = 0.5 \cdot V_{CLP}$  (the point of maximum  $\Delta I_L$ ), assuming that inductor value could also vary by 25% at  $I_{MAX}$ . For I-grade parts, reduce maximum  $\Delta I_L$  to less than  $0.4 \cdot I_{MAX}$ , but **only** if the IC will actually be used to charge batteries over the wider I-grade temperature range. In that case, a good starting point can be found by multiplying the inductor values shown in Table 6 by a factor of 1.6 and rounding up to the nearest standard value.

Table 6. Minimum Typical Inductor Values

| Table 0. Millimum Typical inductor values |             |                  |                     |                 |                   |  |  |

|-------------------------------------------|-------------|------------------|---------------------|-----------------|-------------------|--|--|

| V <sub>CLP</sub>                          | L1<br>(Typ) | I <sub>MAX</sub> | R <sub>SENSE</sub>  | R <sub>IN</sub> | R <sub>PROG</sub> |  |  |

| <10V                                      | ≥10µH       | 1A               | 100mΩ               | 3.01k           | 26.7k             |  |  |

| 10V to 20V                                | ≥20µH       | 1A               | 100mΩ               | 3.01k           | 26.7k             |  |  |

| >20V                                      | ≥28µH       | 1A               | 100mΩ               | 3.01k           | 26.7k             |  |  |

| <10V                                      | ≥5.1µH      | 2A               | 50mΩ                | 3.01k           | 26.7k             |  |  |

| 10V to 20V                                | ≥10µH       | 2A               | $50 \text{m}\Omega$ | 3.01k           | 26.7k             |  |  |

| >20V                                      | ≥14µH       | 2A               | $50 \text{m}\Omega$ | 3.01k           | 26.7k             |  |  |

| <10V                                      | ≥3.4µH      | 3A               | $33 \text{m}\Omega$ | 3.01k           | 26.7k             |  |  |

| 10V to 20V                                | ≥6.8µH      | 3A               | $33 \text{m}\Omega$ | 3.01k           | 26.7k             |  |  |

| >20V                                      | ≥9.5µH      | 3A               | $33 \text{m}\Omega$ | 3.01k           | 26.7k             |  |  |

| <10V                                      | ≥2.5µH      | 4A               | $25 \text{m}\Omega$ | 3.01k           | 26.7k             |  |  |

| 10V to 20V                                | ≥5.1µH      | 4A               | $25 \text{m}\Omega$ | 3.01k           | 26.7k             |  |  |

| >20V                                      | ≥7.1µH      | 4A               | $25 \text{m}\Omega$ | 3.01k           | 26.7k             |  |  |

To guarantee that a chosen inductor is optimized in any given application, use the design equations provided and perform bench evaluation in the target application, particularly at duty cycles below 20% or above 80% where PWM frequency can be much less than the nominal value of 550kHz.

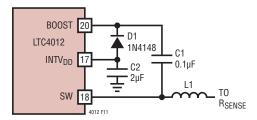

#### **TGATE BOOST Supply**

Use the external components shown in Figure 11 to develop a bootstrapped BOOST supply for the TGATE FET driver. A good set of equations governing selection of the two capacitors is:

$$C1 = \frac{20 \cdot Q_G}{4.5 \text{ V}}, C2 = 20 \cdot C1$$

where  $Q_G$  is the rated gate charge of the top external NFET with  $V_{GS} = 4.5V$ . The maximum average diode current is then given by:

$$I_D = Q_G \bullet 665 \text{kHz}$$

To improve efficiency by increasing  $V_{GS}$  applied to the top FET, substitute a Schottky diode with low reverse leakage for D1.

PWM jitter has been observed in some designs operating at higher  $V_{IN}/V_{OUT}$  ratios. This jitter does not substantially affect DC charge current accuracy. A series resistor with a value of  $5\Omega$  to  $20\Omega$  can be inserted between the cathode of D1 and the BOOST pin to remove this jitter, if present. A resistor case size of 0603 or larger is recommended to lower ESL and achieve the best results.

Figure 11. TGATE Boost Supply

#### FET Selection

Two external power MOSFETs must be selected for use with the charger: an N-channel power switch (top FET) and an N-channel synchronous rectifier (bottom FET). Peak gate-to-source drive levels are internally set to about 5V. Consequently, logic-level FETs must be used. In addition to the fundamental DC current, selection criteria for these MOSFETs also include channel resistance  $R_{DS(ON)}$ , total gate charge  $Q_G$ , reverse transfer capacitance  $C_{RSS}$ , maximum rated drain-source voltage  $BV_{DSS}$  and switching characteristics such as  $t_{d(ON/OFF)}$ . Power dissipation for each external FET is given by:

$$\begin{split} P_{D(TOP)} = & \frac{V_{BAT} \bullet I_{MAX}^2 \bullet \left(1 + \delta \Delta T\right) R_{DS(ON)}}{V_{CLP}} \\ & + k \bullet V_{CLP}^2 \bullet I_{MAX} \bullet C_{RSS} \bullet 665 \text{kHz} \\ P_{D(BOT)} = & \frac{\left(V_{CLP} - V_{BAT}\right) \bullet I_{MAX}^2 \bullet \left(1 + \delta \Delta T\right) R_{DS(ON)}}{V_{CLP}} \end{split}$$

where  $\delta$  is the temperature dependency of  $R_{DS(ON)}, \Delta T$  is the temperature rise above the point specified in the FET data sheet for  $R_{DS(ON)}$  and k is a constant inversely related to the internal LTC4012 top gate driver. The term (1 +  $\delta\Delta T$ ) is generally given for a MOSFET in the form of a normalized  $R_{DS(ON)}$  curve versus temperature, but  $\delta$  of 0.005/°C can be used as a suitable approximation for logic-level FETs if other data is not available.  $C_{RSS} = \Delta Q_{GD}/\Delta V_{DS}$  is usually specified in the MOSFET characteristics. The constant k = 2 can be used in estimating top FET dissipation. The LTC4012 is designed to work best with external FET switches with a total gate charge at 5V of 15nC or less.

For  $V_{CLP}$  < 20V, high charge current efficiency generally improves with larger FETs, while for  $V_{CLP}$  > 20V, top gate transition losses increase rapidly to the point that using a topside NFET with higher  $R_{DS(ON)}$  but lower  $C_{RSS}$  can actually provide higher efficiency. If the charger will be operated with a duty cycle above 85%, overall efficiency is normally improved by using a larger top FET.

The synchronous (bottom) FET losses are greatest at high input voltage or during a short circuit, which forces a low side duty cycle of nearly 100%. Increasing the size of this FET lowers its losses but increases power dissipation in the LTC4012. Using asymmetrical FETs will normally achieve cost savings while allowing optimum efficiency.

Select FETs with  $BV_{DSS}$  that exceeds the maximum  $V_{CLP}$  voltage that will occur. Both FETs are subjected to this level of stress during operation. Many logic-level MOSFETs are limited to 30V or less.

The LTC4012 uses an improved adaptive TGATE and BGATE drive that is insensitive to MOSFET inertial delays,  $t_{d(ON/OFF)}$ , to avoid overlap conduction losses. Switching characteristics from power MOSFET data sheets apply only to a specific test fixture, so there is no substitute for bench evaluation of external FETs in the target application. In general, MOSFETs with lower inertial delays will yield higher efficiency.

#### **Diode Selection**

A Schottky diode in parallel with the bottom FET and/or top FET in an LTC4012 application clamps SW during the non-overlap times between conduction of the top and bottom FET switches. This prevents the body diode of the MOSFETs from forward biasing and storing charge, which could reduce efficiency as much as 1%. One or both diodes can be omitted if the efficiency loss can be tolerated. A 1A Schottky is generally a good size for 3A chargers due to the low duty cycle of the non-overlap times. Larger diodes can actually result in additional efficiency (transition) losses due to larger junction capacitance.

#### **Loop Compensation and Soft-Start**