# **STV2050A**

# AUTOMATIC MULTISCAN DIGITAL CONVERGENCE PROCESSOR

- Multiscan 1H, 2H, HDTV and SVGA applications

- 6 Convergence channels

- 14-bit embedded DACs

- 1 Focus channel

- Second order interpolation in vertical direction

- Digital filtering in horizontal direction

- On-chip PLL

- On-chip video pattern generator

- Automatic compensation of temperature drift and aging of external components

- Pattern and synchronisation signals for optional optical sensor support

- Adjustable horizontal and vertical size

- Up to 7 different data sets

- Self-controlled power-on sequence

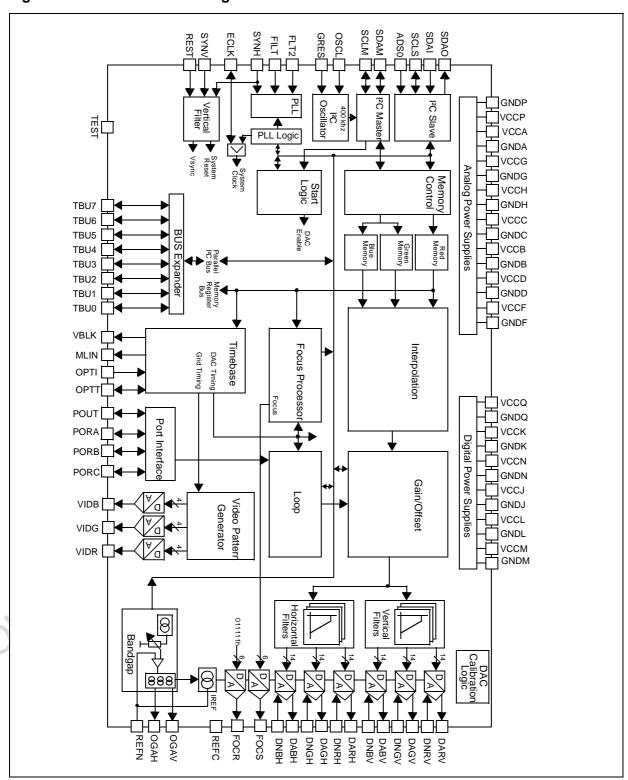

Figure 1. Functional Block Diagram

September 2003

# Table of Contents —

| 1 | GEN  | ERAL OVERVIEW                              | . 5 |

|---|------|--------------------------------------------|-----|

|   | 1.1  | SYSTEM BLOCK DIAGRAM                       | . 5 |

|   | 1.2  | DEVICE BLOCK DIAGRAM                       | . 6 |

|   | 1.3  | APPLICATION CIRCUIT                        | . 7 |

|   | 1.4  | PIN DESCRIPTION AND PINOUT DIAGRAM         | . 8 |

| 2 | STRU | JCTURE OF THE PROGRAMMING SYSTEM           | 11  |

|   | 2.1  | DATA STORAGE                               | 11  |

|   | 2.2  | OVERVIEW OF EMBEDDED RAM ORGANIZATION      | 12  |

|   | 2.3  | ADJUSTMENT DATA SETS                       | 13  |

| 3 | SLA  | /E I <sup>2</sup> C BUS INTERFACE          | 14  |

|   | 3.1  | FEATURES                                   | 14  |

|   |      | 3.1.1 ADS0: IC Address and PLL Mode        | 14  |

|   |      | 3.1.2 SCLS Bus Clock                       |     |

|   |      | 3.1.3 SDAI Bus Data Input                  |     |

|   | 2.2  | 3.1.4 SDAO Bus Data Output                 |     |

|   |      | WRITE COMMANDS                             |     |

|   |      | READ COMMANDS                              |     |

|   |      |                                            |     |

| 4 |      | I <sup>2</sup> C I/O LINES                 |     |

| 4 |      | ALLOCATION                                 |     |

|   | 4.1  |                                            |     |

|   |      | 4.1.1 Dynamic Correction Values            |     |

|   | 4.2  | I <sup>2</sup> C REGISTERS                 |     |

|   |      | 4.2.1 Registers Storable in the EEPROM     |     |

|   |      | 4.2.2 Registers Not Storable in the EEPROM |     |

| 5 |      | BASES                                      |     |

|   | 5.1  | LINE LOCKED PLL AND SYSTEM CLOCK           | 21  |

|   | 5.2  | SYNCHRONIZATION INPUTS                     | 22  |

|   | 5.3  | HORIZONTAL TIMEBASE                        | 22  |

|   |      | 5.3.1 Horizontal DAC Phase                 | 22  |

|   |      | 5.3.2 Horizontal Width Adjustment          |     |

|   | E 1  | 5.3.3 Auto-Calibration of DACs             |     |

|   | 5.4  |                                            |     |

|   |      | 5.4.1 Vertical Synchronization Signal      |     |

|   |      | 5.4.3 Field Counter                        |     |

|   |      | 5.4.4 Convergence Correction Frame Retrace |     |

| 6 | MAS  | TER I <sup>2</sup> C BUS INTERFACE         | 27  |

|   | 6.1  | READ OPERATION MODES                       | 28  |

|   | 6.2  | WRITE OPERATION MODES                      | 28  |

|   | 6.3  | POWER-ON SEQUENCE                          | 28  |

|   | 6.4  | SECURITY FEATURE DURING DATA TRANFERS      | 28  |

|   | 6.5  | STATUS INFORMATION                         | 28  |

# Table of Contents

| 6.6   | DATA TRANSFER BETWEEN RAM AND EEPROM                | 29 |

|-------|-----------------------------------------------------|----|

| 6.7   | MASTER CLOCK FREQUENCY                              | 30 |

| 7 VID | EO PATTERN GENERATOR                                | 31 |

| 7.1   | GENERAL FUNCTIONS                                   | 32 |

|       | 7.1.1 Pattern Selection                             | 32 |

|       | 7.1.2 Pattern Visibility Adjustment                 | 33 |

| 7.2   | CROSS-HATCH GRID                                    | 34 |

|       | 7.2.1 Horizontal Grid Adjustment                    | 34 |

|       | 7.2.2 Vertical Grid Adjustment                      |    |

| 7.3   | CURSOR                                              |    |

|       | 7.3.1 Cursor Size                                   |    |

|       | 7.3.2 Cursor Position                               |    |

| 7.4   | BORDER LINES                                        |    |

|       | 7.4.1 Border Lines: Left / Right                    |    |

| 7.5   | 7.4.2 Border Lines: Bottom / Top                    |    |

| 7.5   | GAIN ADJUSTMENT LINES                               |    |

|       | 7.5.1 Video Pattern for Horizontal Gain Cursor      |    |

| 7.6   | AUTO-ALIGNMENT PATTERN                              |    |

|       | NKING OF VIDEO SIGNALS                              |    |

|       | HORIZONTAL BLANKING                                 |    |

|       | VERTICAL BLANKING                                   |    |

|       | BLANKING FOR AUTO-ALIGNMENT PATTERN                 |    |

|       | FAST BLANKING                                       |    |

|       |                                                     |    |

|       | NVERGENCE                                           |    |

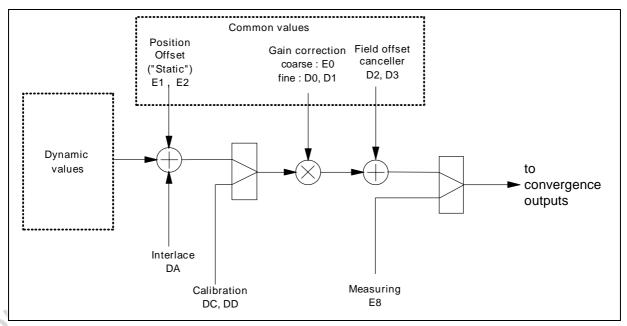

| 9.1   | GLOBAL ADJUSTMENTS - COMMON PARAMETERS              |    |

|       | 9.1.1 Position Offset (also called "static")        |    |

|       | 9.1.2 Gain Correction                               |    |

| 92    | DYNAMIC VALUES                                      |    |

|       | INTERLACE                                           |    |

|       | CALIBRATION                                         |    |

|       | INTERPOLATION                                       |    |

| 9.5   | 9.5.1 Vertical Filter                               |    |

|       | 9.5.2 Horizontal Filter                             |    |

| 9.6   |                                                     |    |

| 1     | MANUFACTURING, AFTER-SALES SERVICE, LAB TRIAL MODES |    |

| 5.7   | 9.7.1 Output of Field Offset Values                 |    |

|       | 9.7.2 Gain and Offset Measuring Line                |    |

|       | 9.7.3 Gain Cursor Mode                              |    |

|       | 9.7.4 Field Offset Cursor Mode                      |    |

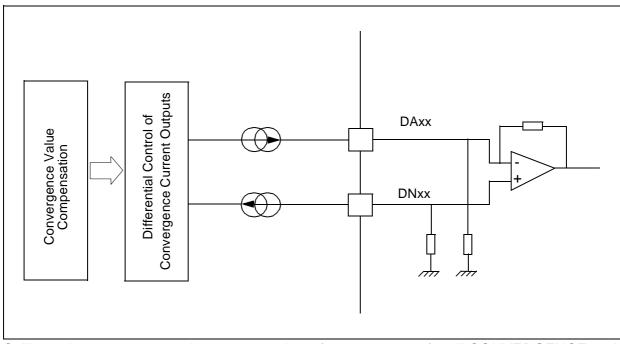

| 9.8   | CONVERGENCE OUTPUTS                                 | 50 |

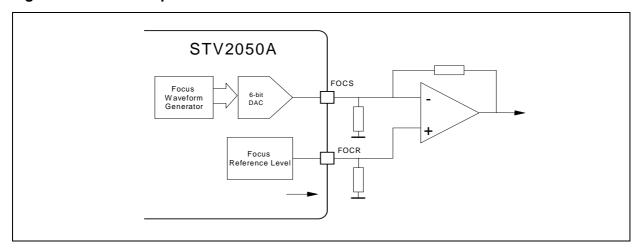

| 10 DY | NAMIC FOCUS                                         | 52 |

| 10.   | 1 PARABOLA CURVE                                    | 52 |

# STV2050A -

| 10.2 FOCUS OUTPUTS                                                       |  |

|--------------------------------------------------------------------------|--|

| 11 ELECTRICAL LOOP                                                       |  |

| 11.1 PRINCIPLE OF OPERATION                                              |  |

| 11.2 LOOP PARAMETER REGISTER                                             |  |

| 11.3 LOOP STATUS REGISTER                                                |  |

| 11.4 OPERATION OF THE ELECTRICAL LOOP                                    |  |

| 11.5 OUTPUT/INPUT PADS                                                   |  |

| 11.5.1PORA, PORB and PORC Pins                                           |  |

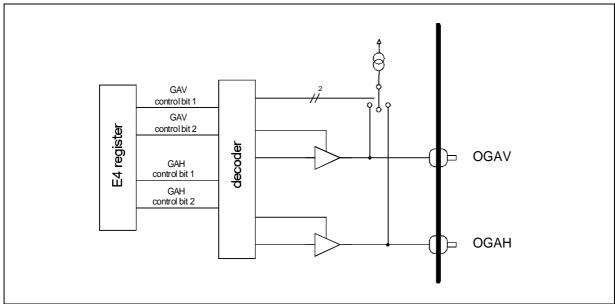

| 11.5.20GAH and OGAV Pins                                                 |  |

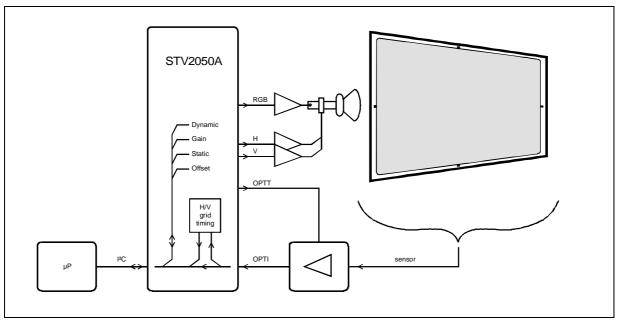

| 12 OPTICAL LOOP                                                          |  |

| 12.1 PRINCIPAL OF OPERATION                                              |  |

| 12.2 OPTT SENSOR PORT CONTROL                                            |  |

| 12.2.1OPTT Pin used as an Input                                          |  |

| 12.2.2OPTT Pin used as an Output                                         |  |

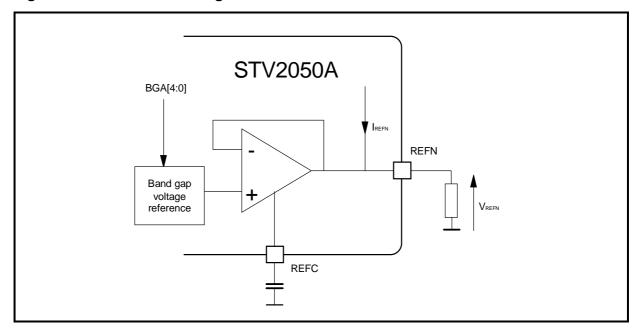

| 13 CURRENT REFERENCE                                                     |  |

| 14 SECURITIES                                                            |  |

| 14.1 OVERVIEW                                                            |  |

| 14.2 HAMMING ENCODING                                                    |  |

| 14.3 SECURITY OUTPUT                                                     |  |

| 15 BOOT SEQUENCE                                                         |  |

| 16 IC STATUS REGISTERS                                                   |  |

| 17 BUS EXPANDER                                                          |  |

| 18 ABSOLUTE MAXIMUM RATINGS                                              |  |

| 19 RECOMMANDED OPERATING CONDITIONS                                      |  |

| 20 ELECTRICAL CHARACTERISTICS                                            |  |

| 20.1 GENERAL                                                             |  |

| 20.2 CURRENT REFERENCE                                                   |  |

| 20.3 VIDEO PATTERN OUTPUTS                                               |  |

| 20.3.1DACs for RGB                                                       |  |

| 20.3.2FBLK Output                                                        |  |

| 20.4 FOCUS DACS                                                          |  |

| 20.4.1 Focus Reference                                                   |  |

| 20.4.2Focus Signal                                                       |  |

| 20.6 PLL                                                                 |  |

| 20.7 MASTER I <sup>2</sup> C TIME BASE                                   |  |

| 20.8 HORIZONTAL AND VERTICAL SYNCHRONIZATION INPUTS                      |  |

| 20.9 TBU OUTPUTS                                                         |  |

| 20.10ELECTRICAL LOOP PADS                                                |  |

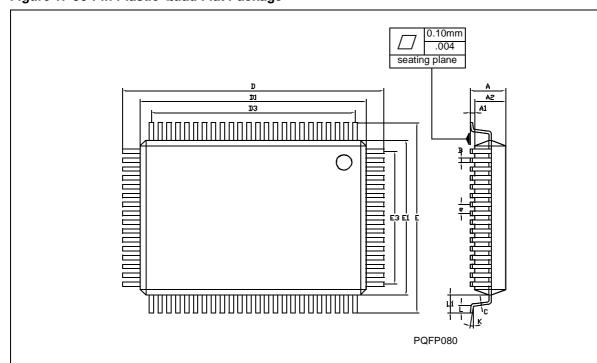

| 21 PACKAGE MECHANICAL DATA                                               |  |

| 22 ELECTRICAL PIN CONFIGURATION                                          |  |

| 23 I <sup>2</sup> C BUS REGISTER VARIABLE GLOSSARY AND REGISTER LOCATION |  |

| _  |    | - | _ | _ | _ | _                |  |

|----|----|---|---|---|---|------------------|--|

| 95 | ΓV | • | n | _ | n | Λ                |  |

| Э. | ıv | _ | u |   | u | $\boldsymbol{H}$ |  |

# **1 GENERAL OVERVIEW**

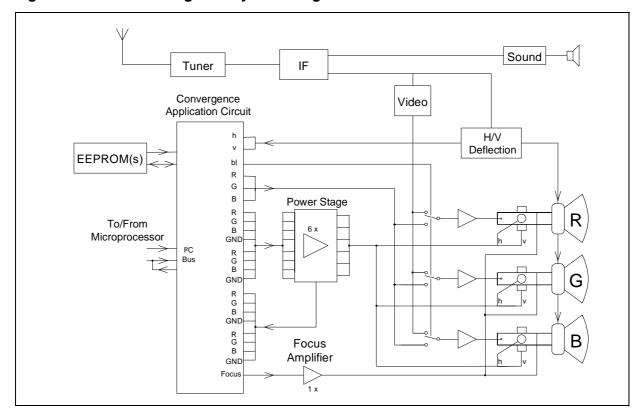

# 1.1 SYSTEM BLOCK DIAGRAM

Figure 2. TV Set Convergence System Diagram

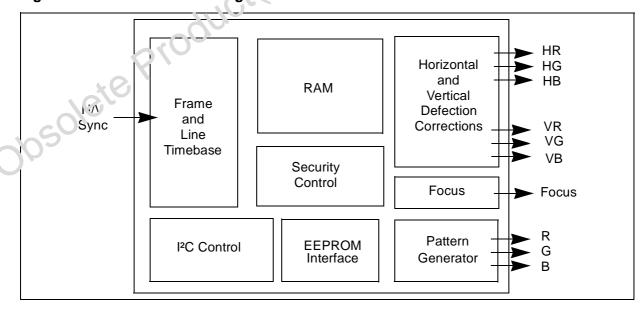

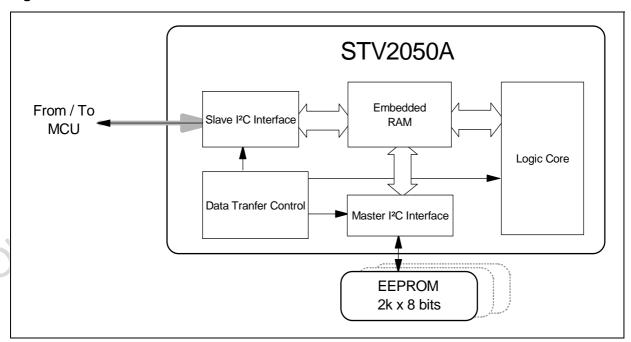

# 1.2 DEVICE BLOCK DIAGRAM

Figure 3. STV2050A Block Diagram

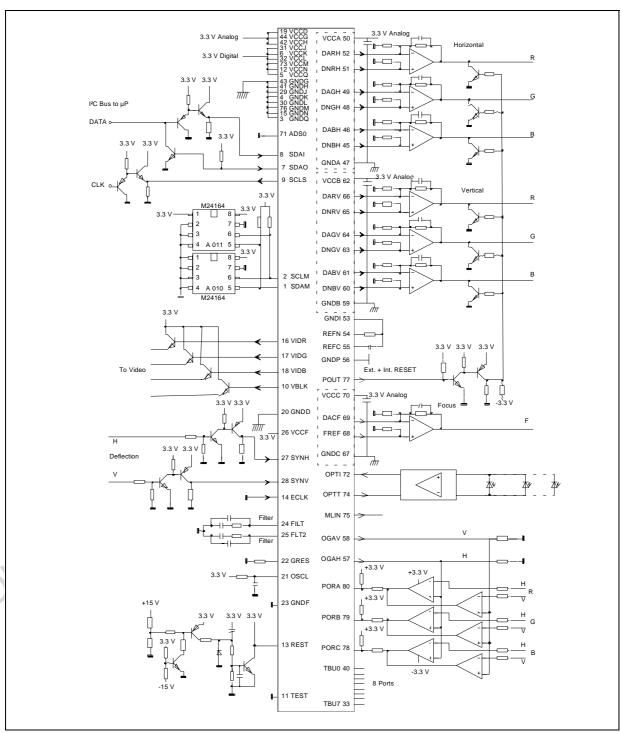

# 1.3 APPLICATION CIRCUIT

An application circuit with 2nd EEPROM, Electrical Offset and Gain Adjustment Loop and Optical Sensors is shown in the following figure.

Figure 4. Application Circuit

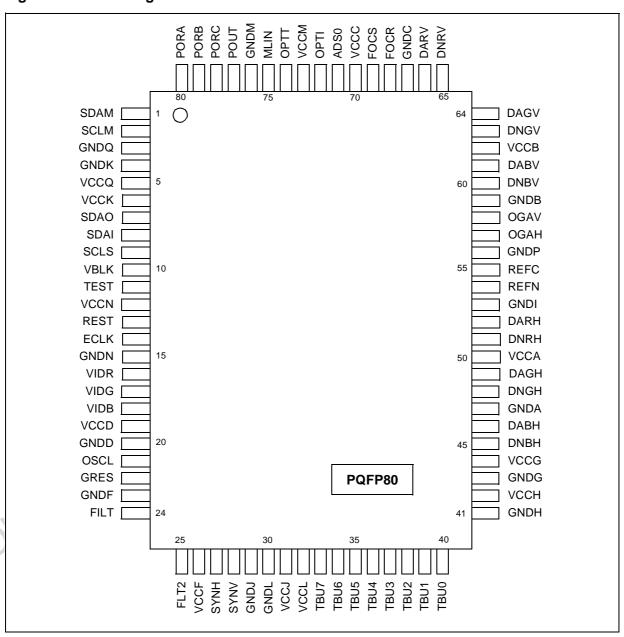

# 1.4 PIN DESCRIPTION AND PINOUT DIAGRAM

The following legend applies to the Pin Description Table below:

X = Undefined HZ = High Impedance

"0" = Low Level Output "1" = High Level Output

# **Table 1. Pin Description**

| Pin No. | Pin Name | Reset Status and Remarks | Description                         |

|---------|----------|--------------------------|-------------------------------------|

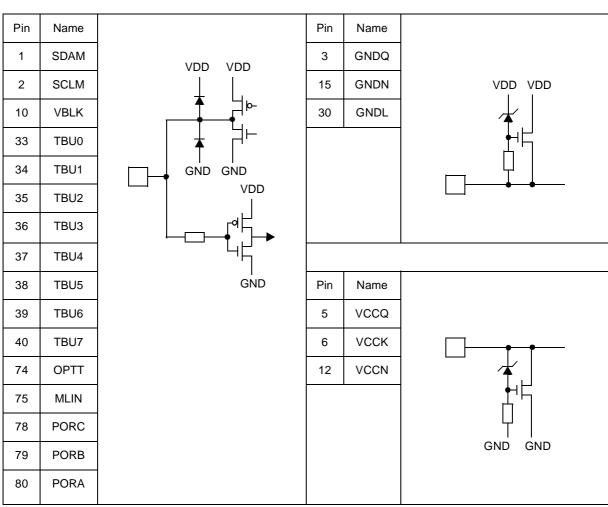

| 1       | SDAM     | HZ                       | Master Bus: "Data"                  |

| 2       | SCLM     |                          | Master Bus: "Clock"                 |

| 3       | GNDQ     |                          | Digital Supply: Ground              |

| 4       | GNDK     |                          | Digital Supply: Ground              |

| 5       | VCCQ     |                          | Core / RAM Digital Supply: 3.3 V    |

| 6       | VCCK     |                          | Core / Digital Supply: 3.3 V        |

| 7       | SDAO     | "0"                      | Slave Bus: "Data" output            |

| 8       | SDAI     |                          | Slave Bus: "Data" input             |

| 9       | SCLS     |                          | Slave Bus: "Clock"                  |

| 10      | VBLK     |                          | Video Pattern Blanking              |

| 11      | TEST     | Must be grounded         | Reserved                            |

| 12      | VCCN     |                          | Shield Supply Digital Supply: 3.3 V |

| 13      | REST     | "0"                      | Reset                               |

| 14      | ECLK     | Must be grounded         | Reserved                            |

| 15      | GNDN     |                          | Digital Supply: "Ground"            |

| 16      | VIDR     | 0 Volts                  | Video Pattern Output: "Red"         |

| 17      | VIDG     | 0 Volts                  | Video Pattern Output: "Green"       |

| 18      | VIDB     | 0 Volts                  | Video Pattern Output: "Blue"        |

| 19      | VCCD     |                          | Video Generator Supply: 3.3 V       |

| 20      | GNDD     |                          | Video Generator Supply: Ground      |

| 21      | OSCL     | HZ                       | RC for internal oscillator          |

| 22      | GRES     | HZ                       | R for internal oscillator           |

| 23      | GNDF     |                          | PLL Supply: Ground                  |

| 24      | FILT     | HZ                       | Filter for PLL                      |

| 25      | FLT2     | HZ                       | Filter for PLL                      |

| 26      | VCCF     |                          | Supply PLL: 3.3 V                   |

| 27      | SYNH     |                          | Horizontal Synchronization input    |

| 28      | SYNV     |                          | Vertical Synchronization input      |

| 29      | GNDJ     |                          | Digital Supply: Ground              |

| 30      | GNDL     |                          | Digital Supply: Ground              |

| 31      | VCCJ     |                          | Core Digital Supply: 3.3 V          |

| 32      | VCCL     |                          | Ring / Buffer Digital Supply: 3.3 V |

| 33      | TBU7     | Х                        | I <sup>2</sup> C BUS Expander       |

| 34      | TBU6     | X                        | I <sup>2</sup> C BUS Expander       |

| 35      | TBU5     | X                        | I <sup>2</sup> C BUS Expander       |

| 36      | TBU4     | X                        | I <sup>2</sup> C BUS Expander       |

<u>57</u>

# **STV2050A - GENERAL OVERVIEW**

| Pin No. | Pin Name | Reset Status and Remarks         | Description                                                                                                           |

|---------|----------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 37      | TBU3     | Х                                | I <sup>2</sup> C BUS Expander                                                                                         |

| 38      | TBU2     | Х                                | I <sup>2</sup> C BUS Expander                                                                                         |

| 39      | TBU1     | Х                                | I <sup>2</sup> C BUS Expander                                                                                         |

| 40      | TBU0     | Х                                | I <sup>2</sup> C BUS Expander                                                                                         |

| 41      | GNDH     |                                  | Analog Supply: Ground                                                                                                 |

| 42      | VCCH     |                                  | D/A Interface Analog Supply: 3.3 V                                                                                    |

| 43      | GNDG     |                                  | Analog Supply: Ground                                                                                                 |

| 44      | VCCG     |                                  | Analog Supply: 3.3 V                                                                                                  |

| 45      | DNBH     | HZ                               | Horiz. Convergence Output: Blue, negative                                                                             |

| 46      | DABH     | HZ                               | Horiz. Convergence Output: Blue, positive                                                                             |

| 47      | GNDA     |                                  | Horiz. Convergence Output Supply: Ground                                                                              |

| 48      | DNGH     | HZ                               | Horiz. Convergence Output: Green, negative                                                                            |

| 49      | DAGH     | HZ                               | Horiz. Convergence Output: Green, positive                                                                            |

| 50      | VCCA     | HZ                               | Horiz. Convergence Output Supply: 3.3 V                                                                               |

| 51      | DNRH     | HZ                               | Horiz. Convergence Output: Red, negative                                                                              |

| 52      | DARH     | HZ                               | Horiz. Convergence Output: Red, positive                                                                              |

| 53      | GNDI     |                                  | Floating GND for bandgap filter                                                                                       |

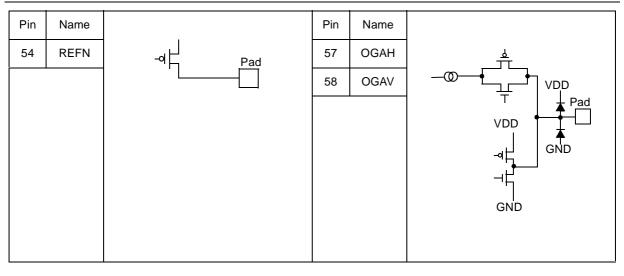

| 54      | REFN     | Reference Current<br>Code 0(hex) | I <sub>REF</sub> Loop for H&V Convergence & Focus                                                                     |

| 55      | REFC     | X                                | Filter pin for I <sub>REF</sub> current                                                                               |

| 56      | GNDP     |                                  | I <sub>REF</sub> GND for Bandgap                                                                                      |

| 57      | OGAH     | HZ                               | Horiz. Reference output for electrical loop                                                                           |

| 58      | OGAV     | HZ                               | Vert. Reference output for electrical loop                                                                            |

| 59      | GNDB     | HZ                               | Vert. Convergence Output Supply: Ground                                                                               |

| 60      | DNBV     | HZ                               | Vert. Convergence Output: Blue, negative                                                                              |

| 61      | DABV     | HZ                               | Vert. Convergence Output: Blue, positive                                                                              |

| 62      | VCCB     |                                  | Vert. Convergence Output Supply: 3.3 V                                                                                |

| 63      | DNGV     | HZ                               | Vert. Convergence Output: Green, negative                                                                             |

| 64      | DAGV     | HZ                               | Vert. Convergence Output: Green, positive                                                                             |

| 65      | DNRV     | HZ                               | Vert. Convergence Output: Red, negative                                                                               |

| 66      | DARV     | HZ                               | Vert. Convergence Output: Red, positive                                                                               |

| 67      | GNDC     |                                  | Focus Supply: Ground                                                                                                  |

| 68      | FOCR     |                                  | Focus Reference Output                                                                                                |

| 69      | FOCS     |                                  | Focus Signal Output                                                                                                   |

| 70      | VCCC     |                                  | Focus Supply                                                                                                          |

| 71      | ADS0     |                                  | I <sup>2</sup> C Slave Bus Address Selection                                                                          |

| 72      | OPTI     |                                  | Input for optical sensor support                                                                                      |

| 73      | VCCM     |                                  | Ring / Inputs Digital Supply: 3.3 V                                                                                   |

| 74      | OPTT     | Input                            | I pin: Latched at measuring line or with sys. clock;<br>O pin: Push/pull, output can be switched to high<br>impedance |

| 75      | MLIN     | "0"                              | Measuring Line Signal Output                                                                                          |

| 76      | GNDM     |                                  | Digital Supply: Ground                                                                                                |

| Pin No. | Pin Name | Reset Status<br>and Remarks | Description                                                                                      |

|---------|----------|-----------------------------|--------------------------------------------------------------------------------------------------|

| 77      | POUT     | HZ                          | Protection Pin Control                                                                           |

| 78      | PORC     |                             | Name allowed for all attitudes for all and a second                                              |

| 79      | PORB     | Input                       | Normally used for electrical loop feedback detection. Can also be set as an inpout or an output. |

| 80      | PORA     |                             | tion. Our also so set as an inpout of an output.                                                 |

Figure 5. Pinout Diagram

#### 2 STRUCTURE OF THE PROGRAMMING SYSTEM

#### 2.1 DATA STORAGE

The STV2050A is a programmable device. Some of the data, mainly the convergence parameters, must be able to be easily changed during TV set alignment or by the user, and must be memorized when the TV set is switched off in order to be recovered when switched back on. This data must therefore be stored in EEPROM.

The STV2050A has an **embedded RAM** for storing data used "in real time" at a high speed. In order to simplify the microcontroller software, and to ensure a quick startup, the STV2050A directly controls one or more (or up to seven) EEPROMs.

The STV2050A has 2 ports for I2C connections:

- The first one is used only for "SLAVE" connections: it is used to interface with a microcontroller in order to control the IC (customer adjustments,...). The microcontroller can write and read the embedded RAM via this slave port.

- The second one is used only for "MASTER" connections: it is used to interface the STV2050A with the EEPROM that stores the convergence data and some user adjustments. The transfer of data between the EEPROM and the embedded RAM is fully managed by the STV2050A.

Figure 6. I<sup>2</sup>C BUS Data Transfer

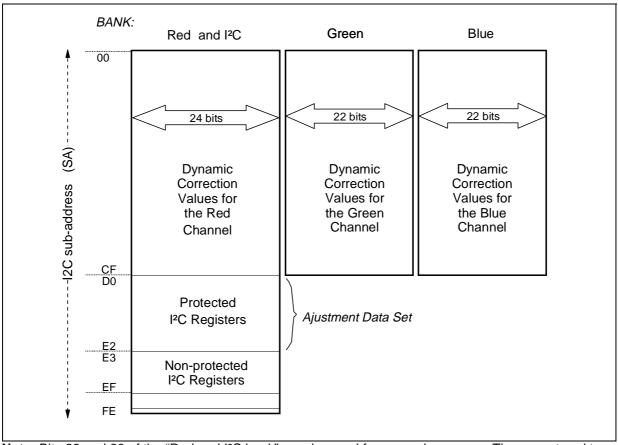

# 2.2 OVERVIEW OF EMBEDDED RAM ORGANIZATION

The RAM consists of 3 banks:

The first one, the "Red and I<sup>2</sup>C Bank", uses 24-bit words. The two other banks, the "Green Bank" and "Blue Bank", both use 22-bit words. Each bank has 208 words with addresses from 00(hex) to CF(hex).

These 3 x 208 words are allocated to the "dynamic" convergence parameters. (Refer to Section 4.1 "CONVERGENCE CORRECTION VALUES" on page 18.)

The "Red and I<sup>2</sup>C Bank" has 33 additional words: addresses from D0(hex) to EF(hex) and FE(hex). These words are used to buffer the I<sup>2</sup>C Bus registers.

As shown in this figure, each word can be pointed to by a sub-address (SA). Thus, each sub-address points to 24- (or 22-, depending on the bank) bit wide words. A word virtually consists of three bytes (24-bits) named D0, D1 and D2 as shown in the following figure. The bit order is named as follows: D0[7] is the MSB and D2[0] is the LSB

|     | MSB     |   |   |   |   |   |   |         |   |   |   |   |   |   |   | _       |   |   |   |   |   |   | LS | В |

|-----|---------|---|---|---|---|---|---|---------|---|---|---|---|---|---|---|---------|---|---|---|---|---|---|----|---|

|     | D0 Byte |   |   |   |   |   |   | D1 Byte |   |   |   |   |   |   |   | D2 Byte |   |   |   |   |   |   |    |   |

| Bit | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0       | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0 |

**Note**: Bit D0[7:6] is not physically implemented in the "Green" and "Blue" banks.

#### STV2050A - STRUCTURE OF THE PROGRAMMING SYSTEM

Figure 7. Color Banks

**Note:** Bits 22 and 23 of the "Red and I<sup>2</sup>C bank" may be used for general purposes. They are stored together with the convergence data in the external EEPROM.

# 2.3 ADJUSTMENT DATA SETS

The set of data stored at addresses D0 to E2 is called an ADS (Adjustment Data Set).

The STV2050A can store up to three ADSs in one standard EEPROM. Refer to Section 6 "MASTER I2C BUS INTERFACE" on page 28.

# 3 SLAVE I2C BUS INTERFACE

#### 3.1 FEATURES

The I2C interface is controlled by 4 pins:

#### 3.1.1 ADS0: IC Address and PLL Mode

The level at this pin corresponds to bit 1 in the first byte in bus transmissions.

- If ADS0 is connected to GND, the analog outputs will be automatically switched on after the reset sequence, and once the internal PLL is activated.

- If the pin is connected to VCC, the DACs will remain in high impedance. The internal PLL is inhibited, and the IC must use an external PLL.

#### 3.1.2 SCLS Bus Clock

The polarity and timing for this pin comply with I<sup>2</sup>C Bus specifications.

#### 3.1.3 SDAI Bus Data Input

The polarity and timing for this pin comply with I<sup>2</sup>C Bus specifications.

# 3.1.4 SDAO Bus Data Output

The polarity reversal and timing for this pin comply with I<sup>2</sup>C Bus specifications.

Abbreviations used:

S = Start condition

P = Stop condition

DA = Device address

DR = Device address for read

DW = Device address for write

SA = Sub-address

D0, D1,... Dn= Data bytes

The slave accepts the following DA subaddresses depending on the hardware configuration defined on pin ADS0.

| ADS0 0 (grounded, internal PLL only) DR = 39, DW = 38<br>1 (3.3 Volt, external PLL only) DR = 3B, DW = 3A |  |

|-----------------------------------------------------------------------------------------------------------|--|

|-----------------------------------------------------------------------------------------------------------|--|

For the 00 to CF address range (RAM), an autoincrement function can be enabled using the AIE (Auto Increment Enable) bit in the E7 register.

| AIE | 0 = Autoincrement disabled<br>1 = Autoincrement enabled |

|-----|---------------------------------------------------------|

|-----|---------------------------------------------------------|

#### STV2050A - SLAVE I2C BUS INTERFACE

If the autoincrement function is enabled, the internal address is automatically incremented after 3 bytes are either written or read. When the autoincrement counter reaches the CF address, the counter stops counting and any additional data will be written to or read from the CF address.

#### 3.2 COLOR BANK SELECTION

As previously mentioned, the embedded RAM is mapped in 3 banks called the "Red and I<sup>2</sup>C Bank", "Green Bank" and the "Blue Bank". A bank is selected using the CBS[1:0] (Color Bank Selection) bits located in the E7 register address.

| CBS[1:0] | 00 = Red and I <sup>2</sup> C bank selected<br>01 = Green bank selected<br>10 = Blue bank selected<br>11 = Red and I <sup>2</sup> C bank selected |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

However, sub-addresses D0 to EF and FE (physically mapped in the "Red and I<sup>2</sup>C Bank") are independent of the actual bank selection.

#### 3.3 WRITE COMMANDS

Three formats of write commands are supported:

- 5-byte write commands to any valid sub-address

S DW SA D0 D1 D2 P

If the auto-increment function is enabled, the internal address is at SA+1 after the command, otherwise it is still at SA.

2-byte write commands for defining a sub-address cursor position or for changing the current sub-address without transmitting data.

S DW SA P

The sub-address is at SA after the command.

- Auto-increment write commands for sub-address range 00 to CF

If the auto-increment function is enabled, the internal address counter is incremented each time 3 bytes are written:

S DW SA<sub>i</sub> D<sub>i</sub>0 D<sub>i</sub>1 D<sub>i</sub>2 D<sub>i+1</sub>0 D<sub>i+1</sub>1 D<sub>i+1</sub>2... Dn P

otherwise every group of 3 bytes is written to SA and the sub-address does not change.

When a group of three data bytes within the 00 to E2 address range has been received, the slave will store them in the appropriate embedded RAM location. Only complete groups of three data bytes are stored. I<sup>2</sup>C registers start to be updated when the first data byte is received. Only complete bytes are written.

All write commands which do not comply with the formats described above are rejected.

#### 3.4 READ COMMANDS

Read commands may access the IC internal RAM as well as all I<sup>2</sup>C registers. Read commands in the 00 to CF range read from the RAM bank that is defined by the two CBS bits that have been previously transmitted to the E7 register by a write command.

Addresses in the D0 to E2 range are mapped to the corresponding section of the red color RAM if the RRP bit in the EF register is '0'. Otherwise the corresponding internal register values are transmitted.

If the SA is in the 00 to CF address range, the position of the cursor is implicitly defined by the SA. An access to any other SAs will switch off the cursor. It will be switched on again if an address in the 00 to CF range is selected.

Three formats of read commands are supported:

# - Random read commands from any valid IC internal address

S DW SA S DR SA D0 D1 D2 P

If the auto-increment function is enabled, the internal address is at the SA+1 after the command, otherwise it is still at the SA.

# - Read commands from the actual internal address

S DR SA D0 D1 D2 P

If the auto-increment function is enabled, the internal address is at the SA+1 after the command, otherwise it is still at the SA.

# Auto-increment read commands from addresses within the 00 to CF address range with random start address.

S DW SA S DR SA D0 D1 D2..... Dn P

If the auto-increment function is enabled, the internal address counter is incremented after 3 bytes are read, otherwise the SA is always read and the internal address does not change.

When the last byte of the CF address has been transmitted, the IC internal auto-increment address counter stops counting and the CF value will be read out again.

#### 3.5 I2C I/O LINES

Digital filters suppress pulses that are less than 1 or 2 clock pulses at the SDAI and SCLS inputs.

#### **4 RAM ALLOCATION**

#### **4.1 CONVERGENCE CORRECTION VALUES**

The convergence correction values are either dedicated to each correction point of each red/blue/green channel, or common for all points of each channel. (Refer to Section 9 "CONVERGENCE" on page 45.)

The values are grouped into 2 families:

- Dynamic correction values

- Common correction values

# 4.1.1 Dynamic Correction Values

The dynamic values are stored as described in Section 2.2 "Overview OF EMBEDDED RAM ORGANIZATION" on page 13.

For each Red, Green and Blue channel, the following can be stored in the embedded RAM:

- 13 horizontal "dynamic" correction values on 10 bits, plus 1 parity bit

- Up to 16 vertical "dynamic" correction values on 10 bits, plus 1 parity bit

For each correction point there is one corresponding word in the 00(hex) to CF(hex) sub-address range. Bits are stored in the corresponding "Red Bank", "Green Bank" and "Blue Bank" as follows:

|     | M       | ISB                        |   |   |   |   |   |         |   |   |   |   |   |   |   |         |     |       |    |       |       |      | LS | SB |

|-----|---------|----------------------------|---|---|---|---|---|---------|---|---|---|---|---|---|---|---------|-----|-------|----|-------|-------|------|----|----|

|     | BYTE D0 |                            |   |   |   |   |   | BYTE D1 |   |   |   |   |   |   |   | BYTE D2 |     |       |    |       |       |      |    |    |

| Bit | 7       | 6                          | 5 | 4 | 3 | 2 | 1 | 0       | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       | 7   | 6     | 5  | 4     | 3     | 2    | 1  | 0  |

|     |         | Horizontal Correction[9:0] |   |   |   |   |   |         |   |   |   |   |   |   |   |         | Vei | tical | Co | rrect | tion[ | 9:0] |    |    |

- Bit D1[3] is the horizontal correction parity bit

- Bit D1[2] is the vertical correction parity bit

- Bits D1[3:2] are generated by the STV2050A. Their value can be read out only.

**Note**: The STV2050A automatically checks the parity bits of each convergence value before applying them to the DACs. Refer to Section 14 "SECURITIES" on page 62.

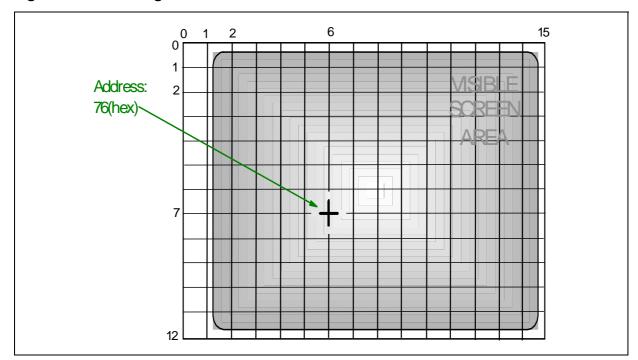

The sub-address corresponds to the coordinates of the point on the screen where the vertical and horizontal lines meet, as shown in the following figure:

Figure 8. Addressing a Correction Point

# **4.1.2 Common Correction Values**

The common correction values are stored in the "adjustment data sets" of the Red and I<sup>2</sup>C channel. See Figure 7 "Color Banks" on page 14 and Section 9.1 "GLOBAL ADJUSTMENTS - COMMON PARAMETERS" on page 45.

#### 4.2 I2C REGISTERS

All I<sup>2</sup>C registers are implemented in the "Red and I<sup>2</sup>C Bank" of the embedded RAM. As it can be useful to store some of the I<sup>2</sup>C register content in the EEPROM, the embedded RAM allocation is divided into two parts:

- From sub-address D0 to E2 (included), contents can be stored in the EEPROM, and can then be restored.

- From sub-addresses E3 to EF and FE, contents are lost when the STV2050A is switched off.

# **4.2.1 Registers Storable in the EEPROM**

|    | М                     | SB            |               |         |       |      |                   |         |                          |          |          |       |                   |     |           |          |          |          |         |       |       |        | LS | SB |

|----|-----------------------|---------------|---------------|---------|-------|------|-------------------|---------|--------------------------|----------|----------|-------|-------------------|-----|-----------|----------|----------|----------|---------|-------|-------|--------|----|----|

|    |                       |               | В             | YTI     | E D   | 0    |                   |         |                          |          | Е        | BYT   | E D               | 1   |           |          | BYTE D2  |          |         |       |       |        |    |    |

| SA | 7                     | 6             | 5             | 4       | 3     | 2    | 1                 | 0       | 7                        | 6        | 5        | 4     | 3                 | 2   | 1         | 0        | 7        | 6        | 5       | 4     | 3     | 2      | 1  | 0  |

| D0 |                       |               |               | RFH     | [7:0] |      |                   |         | GFH[7:0]                 |          |          |       |                   |     | BFH[7:0]  |          |          |          |         |       |       |        |    |    |

| D1 | RFV[7:0]              |               |               |         |       |      |                   |         |                          |          | GFV      | [7:0] |                   |     |           |          |          |          | BF      | V[7:0 | ]     |        |    |    |

| D2 |                       |               | (             | ORH     | [7:0] |      |                   |         |                          |          |          | OGF   | ·[7:0]            |     |           |          |          |          |         | ОВ    | H[7:0 | ]      |    |    |

| D3 | ORV[7:0]              |               |               |         |       |      |                   |         |                          |          |          | OGV   | /[7:0]            |     |           |          |          |          |         | ОВ    | V[7:0 | ]      |    |    |

| D4 | х                     | PD<br>C       | PD<br>B       | PD<br>A | х     | РОС  | PO<br>B           | PO<br>A | X PL GO HV GAV GAH [1:0] |          |          |       |                   |     | Х         | Х        | Х        | Х        | Х       | Х     | Х     | Х      |    |    |

| D5 | PR<br>S               | 0             | 0 AM BGA[4:0] |         |       |      |                   |         | PM<br>H                  | PM<br>V  | Х        | Х     | Х                 | Х   | ML<br>E   |          | MLN[8:0] |          |         |       |       |        |    |    |

| D6 | PBH[3:0] PBV[3:0]     |               |               |         |       |      | HB<br>E           | HA<br>E |                          |          | HVB      | [5:0] |                   | •   | VB<br>E   | VA<br>E  | VVB[5:0] |          |         |       |       |        |    |    |

| D7 | х                     | x HGP[6:0]    |               |         |       |      |                   |         | TV<br>H                  | TV<br>V  | BPH[5:0] |       |                   |     |           | FA<br>S  | ST<br>A  | BPV[5:0] |         |       |       |        |    |    |

| D8 | AC<br>W               | AC x HGD[5:0] |               |         |       |      |                   | ACL     | _[1:0<br>]               | HRD[5:0] |          |       |                   | AFS | [1:0<br>] | AS       | SP[      | 2:0]     | FS<br>O | HIF   | [1:0] |        |    |    |

| D9 |                       |               | ,             | VGP     | [7:0] |      |                   |         | VG<br>P                  | VF<br>P  | VGD[5:0] |       |                   |     |           |          | VFP[7:0] |          |         |       |       |        |    |    |

| DA | IIE                   | IFA           | х             |         | IC    | V[5: | 0]                |         | VST[7:0]                 |          |          |       |                   |     |           | FSB[7:0] |          |          |         |       |       |        |    |    |

| DB | DC<br>T[8]            |               |               | НΩ      | OP[6  | :0]  |                   |         | DCT[7:0]                 |          |          |       |                   |     |           | DCB[7:0] |          |          |         |       |       |        |    |    |

| DC |                       |               | (             | CRH     | [7:0] |      |                   |         | CGH[7:0]                 |          |          |       |                   |     |           | CBH[7:0] |          |          |         |       |       |        |    |    |

| DD |                       |               |               | CRV     | [7:0] |      |                   |         | CGV[7:0]                 |          |          |       |                   |     |           |          | CBV[7:0] |          |         |       |       |        |    |    |

| DE |                       |               | FV1           | [5:0]   |       |      |                   |         | FV2                      | [5:0]    |          |       |                   |     | FV3       | [5:0]    |          |          |         |       | FVF   | R[5:0] |    |    |

| DF | OL GL FIN DI DI X X X |               |               |         |       |      |                   | х       | NOM[7:0]                 |          |          |       |                   |     |           | TOL[7:0] |          |          |         |       |       |        |    |    |

| E0 | RCH[3:0] RCV[3:0]     |               |               |         |       |      | GCH[3:0] GCV[3:0] |         |                          |          |          |       | BCH[3:0] BCV[3:0] |     |           |          |          |          |         |       |       |        |    |    |

| E1 | SRH[7:0]              |               |               |         |       |      | SGH[7:0]          |         |                          |          |          |       | SBH[7:0]          |     |           |          |          |          |         |       |       |        |    |    |

| E2 |                       |               |               | SRV     | [7:0] |      |                   |         |                          |          |          | SGV   | /[7:0]            |     |           |          | SBV[7:0] |          |         |       |       |        |    |    |

# 4.2.2 Registers Not Storable in the EEPROM

|     | M        | ISB           |            |         |         |         |          |            |                      |         |       |         |                |         |         |           |          |          |          |     |       |     | LS      | 3B      |  |

|-----|----------|---------------|------------|---------|---------|---------|----------|------------|----------------------|---------|-------|---------|----------------|---------|---------|-----------|----------|----------|----------|-----|-------|-----|---------|---------|--|

|     |          |               | В          | YT      | E D     | 0       |          |            |                      |         | В     | YT      | E D            | 1       |         |           | BYTE D2  |          |          |     |       |     |         |         |  |

| ADD | 7        | 6             | 5          | 4       | 3       | 2       | 1        | 0          | 7 6 5 4              |         |       |         | 3              | 2       | 1       | 0         | 7        | 6        | 5        | 4   | 3     | 2   | 1       | 0       |  |

| E3  | ST<br>L  | X             | X          | GC<br>D | DH<br>V | PP<br>L | CD<br>O  | CD<br>N    |                      | STV     | 2050  | ОА со   | code = 30(hex) |         |         |           | S0<br>1  | S1<br>9  | R        | ESE | RVED  |     | S0<br>2 | S0<br>3 |  |

| E4  | X        | PD<br>C       | PD<br>B    | PD<br>A | X       | PO<br>C | PO<br>B  | PO<br>A    |                      |         |       |         | G/<br>[1       |         |         | AH<br>:0] | S0<br>1  | S1<br>9  | MS<br>Y  | ELO | Х     | PIC | PIB     | PIA     |  |

| E5  | OP<br>I  | OD<br>S       | 00<br>S    | OD<br>T | Х       | Х       | Х        | Х          | S09 [3:0]            |         |       |         |                | S10     |         | S0<br>1   | S1<br>9  | S0<br>5  | S1<br>1  |     |       |     |         |         |  |

| E6  | Х        | Х             | Х          | Х       | Х       | Х       | Х        | Х          |                      |         |       | S13     | [7:0]          |         |         |           |          |          |          | S14 | [7:0] |     |         |         |  |

| E7  | AIE      | Х             | Х          | Х       | Х       | х       | CI<br>[1 | 3S<br>:0]  | x x x x              |         |       |         | Х              | Х       | Х       | Х         | Х        | Х        | х        | Х   | Х     | Х   | Х       | TE<br>1 |  |

| E8  | MVR[7:0] |               |            |         |         |         |          |            |                      | MVG     | [7:0] |         |                |         |         |           |          | MVB      | [7:0     | ]   |       |     |         |         |  |

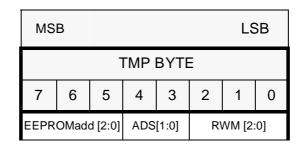

| E9  |          | EPRO<br>dd [2 |            | Х       | Х       | Х       | ADS      | S[1:0<br>] | RWM [2:0] X HAM[3:0] |         |       |         |                | S0<br>1 | S1<br>9 | Х         | Х        | STX[3:0] |          |     |       |     |         |         |  |

| EA  | Х        | Х             | Х          | Х       | VD<br>C | C       | OV[2     | :0]        | GC<br>P              | VH<br>V | Х     |         | PAS[4:0]       |         |         |           | Х        | Х        | Х        | Х   | Х     | Х   | Х       | Х       |  |

| EB  | Х        | Х             |            |         | HO1     | [5:0]   | ]        |            |                      | HG1     | [3:0] |         | Х              | Х       |         |           | HO2      | [5:0]    |          |     |       | HG2 | [3:0]   |         |  |

| EC  | Х        | Х             |            |         | VO1     | [5:0]   |          |            |                      | VG1     | [3:0] |         | Х              | Х       |         |           | VO2      | [5:0]    |          |     |       | VG2 | [3:0]   |         |  |

| ED  | Х        | Х             |            |         | НОЗ     | [5:0]   |          |            |                      | HG3     | [3:0] |         | Х              | Х       |         |           | HO4      | [5:0]    |          |     |       | HG4 | [3:0]   |         |  |

| EE  | Х        | Х             | X VO3[5:0] |         |         |         |          |            | VG3[3:0] X X         |         |       |         |                |         | VO4     | [5:0]     |          |          | VG4[3:0] |     |       |     |         |         |  |

| EF  | Х        | Х             | Х          | Х       | X       | RU<br>E | RU<br>1  | RU<br>2    | x x x x              |         |       | TE<br>2 | TE<br>3        | TE<br>4 | RR<br>P | Х         | Х        | Х        | Х        | Х   | Х     | 0   | 0       |         |  |

| FE  | Х        | SS<br>E       | DT<br>E    | 0       | 0       | 0       | 0        | 0          | 0 0 0 0              |         |       |         | 0              | 0       | 0       | 0         | TBU[7:0] |          |          |     |       |     |         |         |  |

**Note**: X = Don't care, 0 or 1: The corresponding bit MUST be set to this value for normal operation.

# **5 TIMEBASES**

#### 5.1 LINE LOCKED PLL AND SYSTEM CLOCK

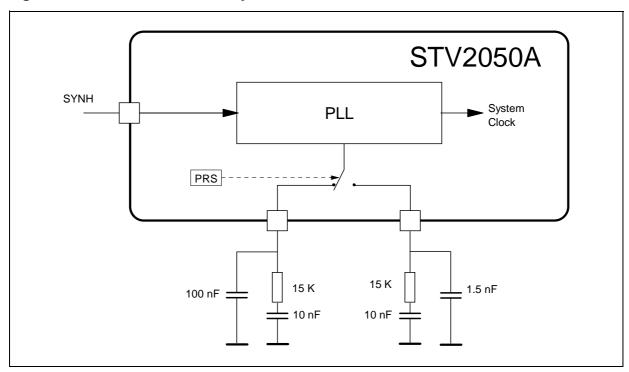

A frequency-multiplying PLL derives the internal *system clock* from the incoming signal at the SYNH pin. This signal is derived from horizontal deflection.

Figure 9. Line-Locked PLL and System Clock

The PLL is designed to drive 1H, 2H, HDTV and SVGA applications. Two loop filters can be implemented using the FILT (pin 24) and FLT2 (pin 25) pads. The selection can be forced by the PRS bit in the D5 register.

| PRS | 0 = FILT selected (2H and above range operation recommended)<br>1 = FLT2 selected (1H range operation recommended) |

|-----|--------------------------------------------------------------------------------------------------------------------|

|-----|--------------------------------------------------------------------------------------------------------------------|

The horizontal deflection is often turned off when switching TV set modes. Therefore the PLL provides a base frequency when the external sync signal is missing (both H and V sync signals are missing).

The  $N_{(clk/line)}$  ratio between the system clock and the incoming sync signal is calculated using the HGD[5:0] and HRD[5:0] values in the D8 register. (Refer to Section 7.2.1 "Horizontal Grid Adjustment" on page 35):

$$N_{(clk/line)} = 14*(HGD+1) + 2*(HRD+1)$$

where:

$$N_{(clk/line)} < 512$$

$$HGD > 15$$

$$HRD > 15$$

For all modes, in normal operation, the incoming timing signal at the SYNH pin will not have a phase deviation greater than  $\pm$  2 µs from line to line. Greater phase deviations may occur when switching modes or changing channels. The PLL is expected to recover from these events and lock within one vertical field of consistent phase that is within the normal horizontal operation limits.

#### **5.2 SYNCHRONIZATION INPUTS**

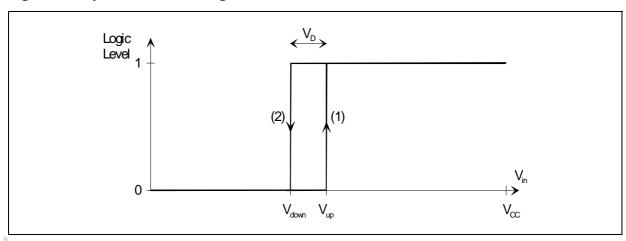

The two synchronization inputs, SYNH (pin 27) and SYNV (pin 28) slice the Line or the Frame Flyback, respectively, via a Schmitt trigger.

This also ensures a very stable detection of the synchronization signals, regardless of the temperature.

Figure 10. Synchronisation Signals

# **5.3 HORIZONTAL TIMEBASE**

The horizontal timing is based on the built-in PLL.

#### 5.3.1 Horizontal DAC Phase

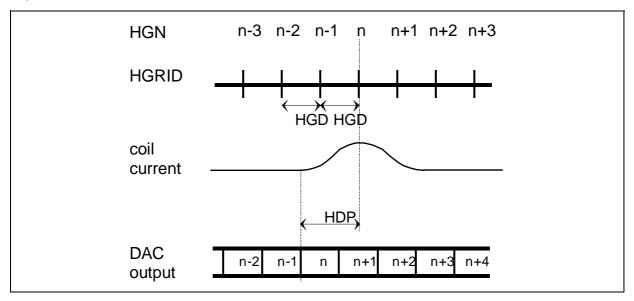

In order to compensate the delay of the external amplifiers and the response time of the convergence coils (t<sub>d</sub>), the values for convergence correction are given out prior to the corresponding horizontal video position. The time delay between video position and the output of

#### STV2050A - TIMEBASES

the corresponding convergence correction value is defined by the Horizontal DAC phase HDP[6:0] value in the DB register.

The following range for the horizontal DAC phase is allowed:

$$0 \le HDP \le 2 \times HGD$$

The timing of the DAC output leads the most if HDP is equal to zero.

Figure 11. Horizontal DAC Phase

# 5.3.2 Horizontal Width Adjustment

In order to fit the video pattern into the full visible area of the screen, the width of the pattern may be adjusted. Horizontal width adjustment is done by changing the number of clock cycles between the vertical grid lines during retrace and the visible grid. The timing for the corresponding DAC values is changed accordingly. Refer to Section 7.2.1 "Horizontal Grid Adjustment" on page 35.

#### 5.3.3 Auto-Calibration of DACs

All the DACs of the STV2050A can be automatically calibrated. This feature ensures a high matching stability in both time and temperature. The process involves the sequential calibration of 120 cells.

To ensure optimal results, each cell must be calibrated at least every 4 ms.

The duration of one cell calibration must be greater than 2us. This duration is controlled by the internal "calibration clock". The calibration clock is generated using a divider of the system clock. (Refer to Section 5.1 "LINE LOCKED PLL AND SYSTEM CLOCK" on page 22). The division ratio is programmable via the ACL[1:0] bits in D8.

| ACL[1:0] | 00: No calibration 01: Division by 16 10: Division by 32 11: Division by 48 |

|----------|-----------------------------------------------------------------------------|

|----------|-----------------------------------------------------------------------------|

Autocalibration can take place either during the full line, or during the line retrace only. This is controlled by the ACW bit in the D8 register.

| ACW | 0: During line retrace only 1: During the full line |

|-----|-----------------------------------------------------|

|-----|-----------------------------------------------------|

If the "During Line Retrace Only" autocalibration is selected, the number of DAC cells calibrated during each line retrace is defined by the AFS[1:0] value in the D8 register.

| AFS[1:0] | 00: 1 cell / line 01: 2 cells / line 10: 3 cells / line 11: 4 cells / line |

|----------|----------------------------------------------------------------------------|

|          | 11: 4 cells / line                                                         |

Two autocalibration modes can be selected by the AMS[0] bit in the D5 register.

| AMS[0] | 0: The autocalibration process is not synchronized to vertical timing 1: The autocalibration is synchronized to vertical IC timing. The counter which selects the DAC cells that are to be calibrated is reset on each frame retrace. |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

The time interval for auto-calibration is normally centred to the retrace. But it is possible to adjust the start point by programming the ASP[2:0] bits in the D8 register. One step corresponds to one system clock cycle.

# **5.4 VERTICAL TIME BASE**

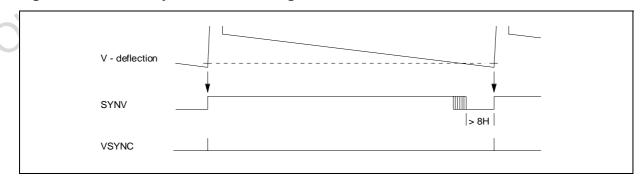

# 5.4.1 Vertical Synchronization Signal

The vertical timing is based on the vertical deflection signal. A debounce filter is implemented to prevent interference on the SYNV signal caused by crosstalk, mainly from horizontal deflection. This filter accepts a rising edge of the SYNV signal only when SYNV is 'LOW' for a time  $\geq$  8 TV lines (determined by 8 pulses at the SYNH input).

Figure 12. Vertical Synchronization Signal

<u> 577</u>

### 5.4.2 Field Parity Recognition

In the case of a standard STV2050A implementation, synchronization is achieved using signals extracted horizontally (Line Flyback) and vertically (Frame Flyback). Unfortunately, depending on the components and the configuration, the phase relationship between these signals is not the same in every TV chassis. In this case, field parity recognition can be unreliable unless special features are implemented. The STV2050A can achieve perfect field parity recognition using the "Vertical Sync shift" (VST).

When the VST[7:0] bits in the DA register are set to the optimum value, the STV2050A distinguishes perfectly between the two fields. This is used to control the interpolation of the convergence values and the video pattern generator according to the interlaced scanning scheme.

The correct VST value can be evaluated by measuring the timing of the vertical pulse. This timing is measured by the STV2050A, and the results are stored in the S13[7:0] and S14[7:0] bits in the E6 register.

In non-interlaced mode, field recognition can be switched off by the IIE bit in the DA register.

| IIE | 0 = Interlace OFF<br>1 = Interlace ON |

|-----|---------------------------------------|

|-----|---------------------------------------|

#### 5.4.3 Field Counter

A 4-bit field counter is implemented for controlling the optical alignment procedure. The counter value is stored in the S12[3:0] bits in the E5 register (read only).

This counter will be reset to 0000 at IC power-up and will be incremented after every vertical reset. The counter will overflow from 1111 to 0000. (The counter will not be reset when the E5 register is read.)

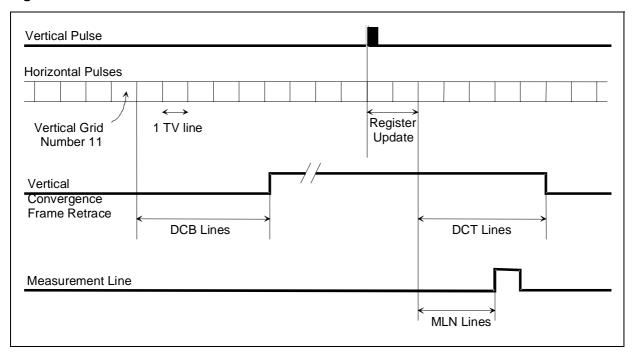

## 5.4.4 Convergence Correction Frame Retrace

This is the time interval defined as follows:

- Start at grid line number 11 + DCB[7:0] bits in the DB register,

- Stop at 2 TV lines after the frame pulse + DCT[8:0] bits in the DB register;

where DCB and DCT are the number of TV lines.

Figure 13. Vertical Time Base

#### **6 MASTER I<sup>2</sup>C BUS INTERFACE**

A master I<sup>2</sup>C bus implemented in the STV2050A is used to transfer data between the IC embedded RAM and the external 2K x 8-bit EEPROMs (for example, the 24164 manufactured by ST). The protocol supports up to 7 EEPROM addresses which can be selected using the 3 **EEPROMadd**[2:0] bits in the E9 register.

Master activities are initiated either by an external reset of the STV2050A, or by commands from an external MCU via the Slave I<sup>2</sup>C bus. The following features are implemented in the Master I<sup>2</sup>C Bus interface:

- Reset the I2C bus to the EEPROM

- Read a specified data range from EEPROM to RAM

- Write a specified data range from RAM to EEPROM

- Check if an EEPROM register is available

- Power-on sequence

- Security features

- Generate status information

The organization of data in the embedded RAM is completely different from that in the EEPROM register. Therefore, address transformations are required in both directions. This is carried out by the STV2050A in a way that is fully transparent for the user.

The external MCU initiates a master access to the EEPROM by writing a command to the E9 address. This command contains information about the type of access and specifies one of seven EEPROMs (refer to Section 6.6 "DATA TRANSFER BETWEEN RAM AND EEPROM" on page 30).

The embedded RAM contains convergence correction data and one adjustment data set (ADS) to control the various modes of the STV2050A. Three ADSs can be stored in the EEPROM. One of these three sets is selected by the two ADS[1:0] bits in the E9 command to be mapped to the register RAM area inside the IC.

Any command sent from the MCU to the E9 address while the master is active will be lost. Also, the EEPROM address which is included in this command will not be accepted.

Before addressing the E9 register, the MCU should check if the master is active. To do this, the RWM[2:0] bits in the E9 register must be set to "001" (bin). The corresponding status is given on the STX[2] bit.

If any error are detected during the transmission of data on the EEPROM I<sup>2</sup>C bus, the transmission is stopped and the corresponding STX[3] bit of the status section of the E9 register is set.

Read or Write modes can be selected by setting bit RWM[2] in the E9 register.

| RWM[2] | 0 = Read mode<br>1 = Write mode |

|--------|---------------------------------|

|--------|---------------------------------|

#### **6.1 READ OPERATION MODES**

Two modes of read sequences are implemented by selecting the RWM[1:0] bits.

| RWM[1:0] | 11 (bin): Read all convergence data and an ADS 10 (bin): Read an ADS only |  |

|----------|---------------------------------------------------------------------------|--|

|----------|---------------------------------------------------------------------------|--|

#### **6.2 WRITE OPERATION MODES**

Three modes of write sequences are implemented by selecting the RWM[1:0] bits.

| RWM[1:0] | 01 (bin): Write all convergence data and one of the three ADSs 00 (bin): Write only one of the ADSs 10 (bin): Write only the "static" (position offset) values |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### **6.3 POWER-ON SEQUENCE**

At power-on, the master interface runs a special sequence to build up the convergence correction data and the STV2050A RAM is loaded with data from a user-specified EEPROM.

#### **6.4 SECURITY FEATURE DURING DATA TRANFERS**

Since access to an EEPROM register is critical with respect to system performance, all EEPROM access commands in the E9 register, together with the corresponding addresses, are protected by the 2-bit, error-detecting Hamming code. If the circuit detects an error, the Master will not initiate an EEPROM access and an error bit will be set in the status register.

If any errors are detected during the transmission of data on the I<sup>2</sup>C bus, the transmission is stopped and the corresponding STX[3] bit in the status section of the E9 register is set.

#### **6.5 STATUS INFORMATION**

Four STX[3:0] bits are available in the status section of the E9 register. These bits continuously reflect the activity and the error status of the master I<sup>2</sup>C bus interface.

- STX[3] = 'TRANSMISSION ERROR'

- This bit is set to low if an error in the transmission of an EEPROM access command was detected. It remains low until the next error-free transmission to register E9 is completed.

- STX[2] = 'EEPROM ACCESS FINISHED'

- This bit is set to low when the master I<sup>2</sup>C-bus interface has completed bus activities. This bit does not display the completion of an EEPROM access. This bit is set high by the master at the start of a new bus sequence or by the slave after reading status register E9.

- -STX[1] = 'EEPROM R/W'

This bit is set to low when the master has initiated an access to the EEPROM. It remains low until the sequence is finished or the sequence is terminated by an access error.

#### STV2050A - MASTER I2C BUS INTERFACE

- STX[0] = 'EEPROM PROBLEM'

If A Read or Write sequence has been terminated with an access error, the STX[0] bit is set to low. It is set back to high when the master starts the next R/W sequence.

#### 6.6 DATA TRANSFER BETWEEN RAM AND EEPROM

Data is transfered using the following I<sup>2</sup>C BUS sequence after a bit in the E9 register has been read or written: S DW SA D0 D1 D2 P

#### Where:

- SA = E9: Selection of the E9 register, EEPROMadd[2:0] is the hardware EEPROM address used by the I<sup>2</sup>C Master,

- RWM[2:0] selects the Read or Write mode as previously described,

- HAM[2:0]: Hamming code used to protect the D0[7:0] and D1[7:4] data bits. Refer to Section 14.2 "HAMMING ENCODING" on page 62.

The total transfer lasts approximately 200 ms if the I<sup>2</sup>C master clock is operating at 70 kHz.

|     | M                    | ISB |   |   |   |          |           |    |       |         |   |          |   |   |   |   |         |   |   |   |     |       | LS | B |

|-----|----------------------|-----|---|---|---|----------|-----------|----|-------|---------|---|----------|---|---|---|---|---------|---|---|---|-----|-------|----|---|

|     | BYTE D0              |     |   |   |   |          |           |    |       | BYTE D1 |   |          |   |   |   |   | BYTE D2 |   |   |   |     |       |    |   |

| ADD | 7                    | 6   | 5 | 4 | 3 | 2        | 1         | 0  | 7     | 6       | 5 | 4        | 3 | 2 | 1 | 0 | 7       | 6 | 5 | 4 | 3   | 2     | 1  | 0 |

| E9  | EEPRO-<br>Madd [2:0] |     | Х | Х | Х | AE<br>1: | )S[<br>0] | RW | /M [2 | 2:0]    | Х | HAM[3:0] |   |   |   | Х | Х       | Х | Х |   | STX | [3:0] |    |   |

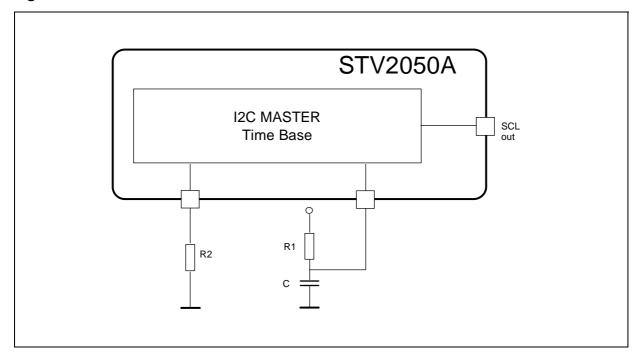

# **6.7 MASTER CLOCK FREQUENCY**

The I<sup>2</sup>C Master uses its own timebase with a local oscillator. The frequency is fixed by external filter (R1/C and R2) as shown in Figure 14 "Master I<sup>2</sup>C Clock" on page 31.

# Typical values are:

$-R1 = 82 k\Omega$

$-R2 = 10 k\Omega$

-C = 33 pF

Figure 14. Master I<sup>2</sup>C Clock

#### STV2050A - VIDEO PATTERN GENERATOR

#### **7 VIDEO PATTERN GENERATOR**

The STV2050A provides a built-in video pattern generator for convergence adjustments. The RGB signals are generated by 4-bit DACs with a voltage output. The FBLK signal is used to switch the RGB source inside the TV set. The FBLK is a fixed-voltage output. The video pattern generator delivers five types of video patterns:

#### – Cross-Hatch Grid:

Displays the physical locations corresponding to the stored correction values. Refer to Section 7.2 "CROSS-HATCH GRID" on page 35.

#### - Cursor:

A crosshair is displayed at the place corresponding to the current addressed memory location.

#### - Border Lines:

Used to adjust the convergence at the horizontal and vertical edges of the visible screen area. Refer to Section 7.4 "BORDER LINES" on page 37.

# - Gain Adjustment Lines:

Used to easily adjust the gain of the convergence channels and to optimize interlace mode.

## - Auto-alignment Pattern:

Supports an auto-alignment procedure.

The video generator also produces the control signals for the optional optical loop functions.

The patterns can be modified using several parameters in the registers of the STV2050A.

Programmable for H Zoom effect First two grids only

Figure 15. Auto-alignment Pattern

**Note**: It is not possible to display both cursors simultaneously as shown.

#### 7.1 GENERAL FUNCTIONS

# 7.1.1 Pattern Selection

The color components (RGB) for the video pattern can be separately switched on and off by the COV[2:0] bits in the EA register. If the control bit for one color is set to 0, the corresponding DAC output is switched to 0V.

| COV[2] | 0: Red = Off<br>1: Red = On     |

|--------|---------------------------------|

| COV[1] | 0: Green = Off<br>1: Green = On |

| COV[0] | 0: Blue = Off<br>1: Blue = On   |

The type of the pattern is selected by the PAS[4:0] bits in the EA register.

| PAS[4] | 0: Auto-alignment Pattern Off 1: Auto-alignment Pattern On |

|--------|------------------------------------------------------------|

| PAS[3] | 0: Small Cursor<br>1: Large Cursor                         |

| PAS[2] | 0: Cursor Off<br>1: Cursor On                              |

<u>57</u>

#### STV2050A - VIDEO PATTERN GENERATOR

| PAS[1] | 0: Grid Off<br>1: Grid On     |

|--------|-------------------------------|

| PAS[0] | 0: Border Off<br>1: Border On |

The FBLK output is switched to 'high' voltage when at least one color is activated by the COV bits in the EA register when the STA bit in the D7 register is activated. If no color is selected, the FBLK output is switched to 'low' voltage. For other features of the FBLK pin, refer to Section 8.4 "FAST BLANKING" on page 43.

The video signal representing a vertical line (grid, border, cursor) has the shape of a pulse with a width of one system clock cycle.

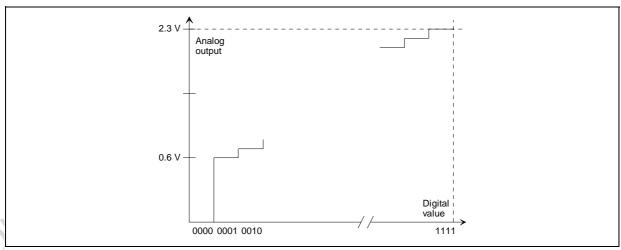

## 7.1.2 Pattern Visibility Adjustment

Since the bandwidth of the RGB signal path is limited, horizontal and vertical lines may appear on the screen with different brightness levels. To compensate for this effect, it is possible to adjust the brightness values for the horizontal line (PBH[3:0]) bits and the vertical line (PBV[3:0]) bits in the D6 register of the video pattern.

The video brightness has 4-bit resolution. The 0(hex) value corresponds to the 0.0 V output from the video DACs. The 1(hex) value corresponds to a typical 0.6 V output. All other steps are equidistant.

Figure 16. Pattern Visibility Adjustment

If the PBH bit is set to zero, the amplitude of the auto-alignment pattern is determined by the PBV bit.

Using the VDC bit in the EA register, the frequency compensation of the video DACs can be adapted according to the system clock.

| VDC | 0: Low Current<br>1: High Current |  |

|-----|-----------------------------------|--|

|-----|-----------------------------------|--|

#### 7.2 CROSS-HATCH GRID

The convergence values are adjusted and stored for an array of 16 x 13 points. These points can be displayed by the grid lines of the video generator. The deflection correction at the grid points corresponds to the digitally stored values. Several programming features are used to adapt the grid, and therefore the convergence adjustment, to the needs of the application. All parameters for the grid are included in the data set stored in the internal RAM.

# 7.2.1 Horizontal Grid Adjustment

The horizontal distance of the grid lines is determined by the values of the HGD[5:0] and HRD[5:0] bits in the D8 register. Refer to Figure 17 "Horizontal Grid Adjustment" on page 35.

Between each grid line, a minimum of 16 system clock cycles is required for calculating the convergence. (Refer to Section 5.1 "LINE LOCKED PLL AND SYSTEM CLOCK" on page 22). The geometrical distance between two vertical grid lines can be modified by adding clock cycles between the visible grid lines (HGD) or by adding clock cycles during the horizontal retrace (HRD).

- HGD: horizontal grid distance during active line.

- HRD: horizontal grid distance during line retrace.

The left-right position is controlled by the HGP[6:0] bits in the D7 register.

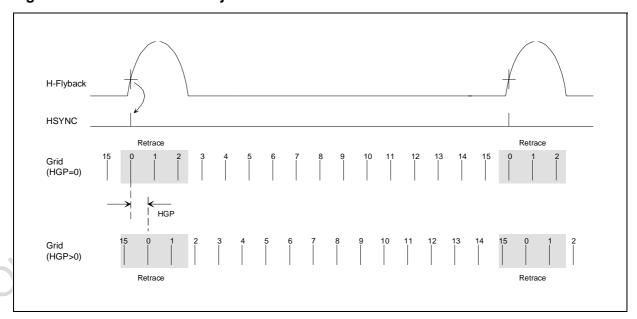

Figure 17. Horizontal Grid Adjustment

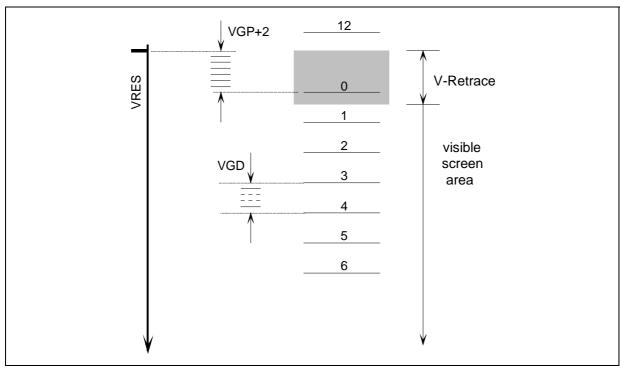

# 7.2.2 Vertical Grid Adjustment

In the same way, the vertical grid adjustment is done using the VGP[8:0] and VGD[5:0] bits in the D9 register.

Figure 18. Vertical Grid Adjustment

If the VGP bit is programmed to 0, the grid starts with the first line following the two lines that are reserved for the register update procedure.

The allowed range for the VGP is included between the 0 and 511 video lines.

#### 7.3 CURSOR

## 7.3.1 Cursor Size

The cursor is available in different shapes. The shape is selected by the PAS[3] cursor-type bit in the EA register.

| PAS[3] | 0: Small Cursor<br>1: Large Cursor |

|--------|------------------------------------|

|--------|------------------------------------|

#### 7.3.2 Cursor Position

The position of the cursor is determined by the most recent write command on the I<sup>2</sup>C bus.

The embedded RAM addresses of dynamic convergence correction values correspond directly to grid positions on the screen. They represent cursor positions as well.

If the CPV (Cursor Position Vertical) value exceeds the 0...C(hex) range, the cursor is not displayed.

If a new write address is within the accepted grid range (after having exceeded the range), the cursor pattern is re-displayed (unless the cursor display is turned off).

## 7.4 BORDER LINES

Convergence adjustments at the edges of the screen are more difficult because the grid points which are involved are not visible. Therefore, additional horizontal and vertical border lines are implemented for making adjustments at these positions.

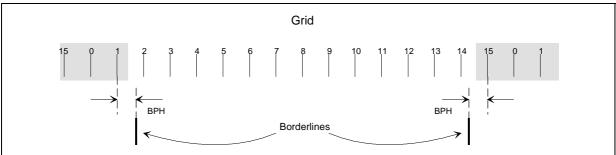

# 7.4.1 Border Lines: Left / Right

The horizontal position of the border lines is programmable by the BPH[5:0] bits in the D7 register.

| 00h        | The position of the border lines is identical to the vertical grid lines at horizontal grid positions 1 and 15                                                       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01h to 1Fh | The border lines move toward the centre of the screen in increments of BPH clock cycles. The range for the shift of the border line is one horizontal grid distance. |

Figure 19. Border Lines

Note: The BPH bit must be smaller than the HGD bit.

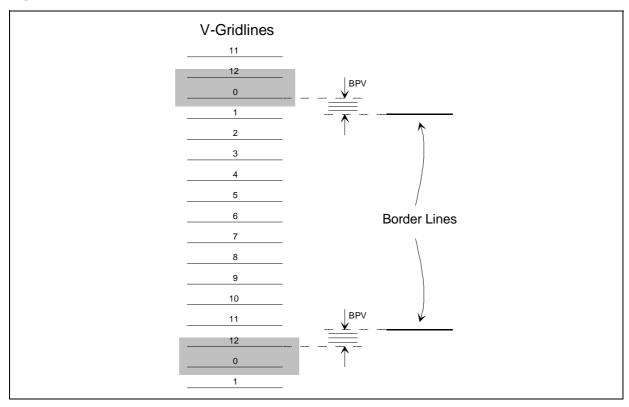

# 7.4.2 Border Lines: Bottom / Top

The vertical position of the border lines depends on bits BPV[5:0] in register D7.

| 00h        | The position of the horizontal border lines is identical to the horizontal grid lines at positions 0 and 12.                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01h to 1Fh | The horizontal border lines move toward the centre of the screen by BPV video lines. The allowed range for the BPV value is one vertical grid distance. |

Figure 20. Vertical Border Lines

Note: The value of the BPV bit must be smaller than that of the VGD bit.

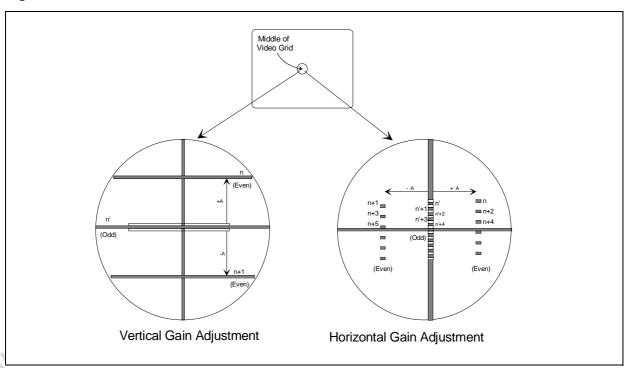

## 7.5 GAIN ADJUSTMENT LINES

The "Gain Adjustment Lines" pattern is used mainly for 2 purposes:

- To calibrate the convergence currents in order to achieve a consistent geometrical correction on the screens of a series of PTVs,

- To have an easy visual adjustment of the interlace mode.

The cursor has two different shapes, one for the adjustment of the vertical gain and another for the adjustment of the horizontal gain.

The video pattern for the gain cursor is defined in the EA register.

| GCP | Gain cursor video pattern off     Gain cursor video pattern on              |

|-----|-----------------------------------------------------------------------------|

| VHV | Horizontal gain cursor video pattern     Vertical gain cursor video pattern |

## 7.5.1 Video Pattern for Horizontal Gain Cursor

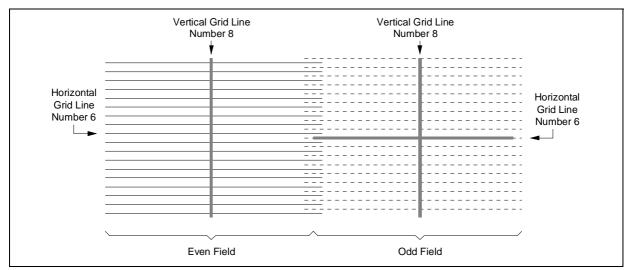

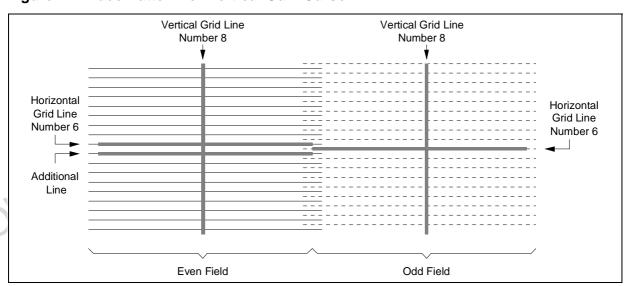

The horizontal gain cursor can be used for adjusting the horizontal convergence channels. The video pattern in the odd field is identical to the video pattern of the large cursor displayed at the centre of the visible grid.

Figure 21. Video Pattern for Horizontal Gain Cursor

Note that these controls only modify the video signals. They have no effect on the convergence signals. The dedicated controls of the convergence signals are described in Section 9.7 "MANUFACTURING, AFTER-SALES SERVICE, LAB TRIAL MODES" on page 49.

#### 7.5.2 Video Pattern for Vertical Gain Cursor

The video pattern for the vertical gain cursor is identical to video pattern for the horizontal gain cursor (displayed at the centre of the visible grid), except for one horizontal line which is added only in the even TV field.

Figure 22. Video Pattern for Vertical Gain Cursor

## STV2050A - VIDEO PATTERN GENERATOR

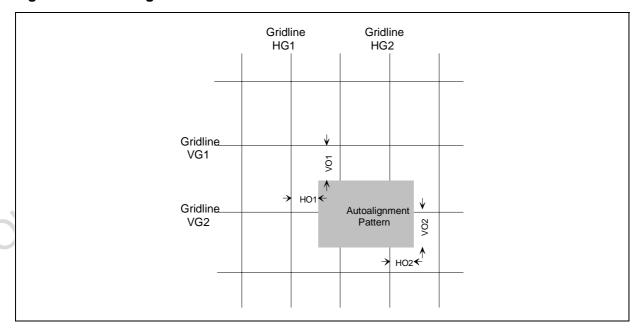

## 7.6 AUTO-ALIGNMENT PATTERN

The auto-alignment pattern is a rectangular, highlighted part of a screen with a constant brightness (horizontal brightness). See Figure 23 "Auto-alignment Video Pattern" on page 40.

The On/Off is controlled by the PAS[4] bit in the EA register

| PAS[4]  0: Auto-alignment pattern off 1: Auto-alignment pattern on |  |

|--------------------------------------------------------------------|--|

|--------------------------------------------------------------------|--|

The size and the position of the pattern can be controlled by the EB and EC registers. The pattern is defined by its horizontal and vertical start and stop values: HO1, HG1, HO2, HG2, VO1, VG1, VO2 and VG2.

| HG1[3:0] | Grid number of horizontal pattern start                                  |

|----------|--------------------------------------------------------------------------|

| HO1[5:0] | Offset of horizontal pattern start (number of clock cycles, 1 grid max.) |

| HG2[3:0] | Grid number of horizontal pattern end                                    |

| HO2[5:0] | Offset of horizontal pattern end (number of clock cycles, 1 grid max.)   |

| VG1[3:0] | Grid number of vertical pattern start                                    |

| VO1[5:0] | Offset of vertical pattern start (number of video lines, 1 grid max.)    |

| VG2[3:0] | Grid number of vertical pattern end                                      |

| VO2[5:0] | Offset of vertical pattern end (number of video lines, 1 grid max.)      |

Offset position values must be one grid distance smaller than the vertical grid numbers for start or stop positions.

Figure 23. Auto-alignment Video Pattern

The pattern may be defined so that an end value is less than the start value. In this case, the window will wrap around through the retrace without any interruptions (two or four rectangles will be highlighted on the screen).

The auto-alignment pattern signal is influenced by the horizontal or vertical blanking function.

## 8 BLANKING OF VIDEO SIGNALS

The output of the RGB signals can be set to 0V during the horizontal and vertical retrace. The function is controlled by the D6 register. The horizontal and vertical retrace blanking function can be enabled independently.

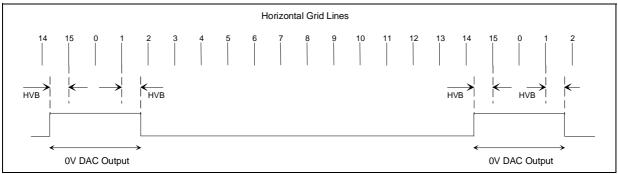

#### 8.1 HORIZONTAL BLANKING

The HBE bit in the D6 register is used to enable/disable the horizontal blanking.

| HBE | 0: Horizontal Blanking Off 1: Horizontal Blanking On |

|-----|------------------------------------------------------|

|-----|------------------------------------------------------|

The start and end edge positions are determined by the HVB[5:0] bits in the D6 register.

If the horizontal blanking is enabled, the video outputs are set to 0V from the HVB clock cycles before grid line number 15 until the HVB clock cycles after grid line number 1. The useful range for the HVB is one horizontal grid distance. This function is similar to the border line function.

If '0' is programmed, grid lines no. 15 and no. 1 are not blanked.

Figure 24. Horizontal Grid Lines

Note: If the HVB values are greater than the HGD values, unexpected effects will appear on the screen.

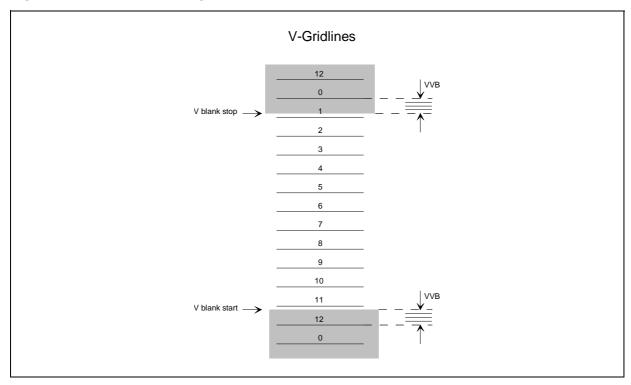

## **8.2 VERTICAL BLANKING**

The enable/disable control is the VBE bit in the D6 register.

|   | VBE | 0: Vertical Blanking Off |

|---|-----|--------------------------|

| 1 |     | 1: Vertical Blanking On  |

The start and end edge positions are determined using the VVB[5:0] bits in the D6 register.

The video blanking function ends when the programmed number of VVB video lines, following vertical grid line no. 0, are finished **and** the next video line following the end of the DAC retrace mode (DCT) has begun.