# Quad PLL Programmable Clock Generator with Spread Spectrum

#### **Features**

- Four fully integrated phase locked loops (PLLs)

- Input frequency range

- □ External crystal: 8 to 48 MHz for CY2544 and CY2546

- □ External reference: 8 to 166 MHz clock

- Reference clock input voltage range

- □ 2.5V, 3.0V, and 3.3V for CY2548

- □ 1.8V for CY2544 and CY2546

- Wide operating output frequency range ☐ 3 to 166 MHz

- Programmable spread spectrum with center and down spread option and Lexmark and Linear modulation profiles

- VDD supply voltage options:

□ 2.5V, 3.0V, and 3.3V for CY2544 and CY2548

□ 1.8V for CY2546

- Selectable output clock voltages:

□ 2.5V, 3.0V, and 3.3V for CY2544 and CY2548

□ 1.8V for CY2546

- Frequency select feature with option to select eight different frequencies over nine clock outputs

- Power down, output enable, and SS ON/OFF controls

- Low jitter, high accuracy outputs

- Ability to synthesize nonstandard frequencies with Fractional-N capability

- Up to nine clock outputs with programmable drive strength

- Glitch free outputs while frequency switching

- 24-pin QFN package

- Commercial and Industrial temperature ranges

#### **Benefits**

- Multiple high performance PLLs allow synthesis of unrelated frequencies

- Nonvolatile programming for personalization of PLL frequencies, spread spectrum characteristics, drive strength, crystal load capacitance, and output frequencies

- Application specific programmable EMI reduction using spread spectrum for clocks

- Programmable PLLs for system frequency margin tests

- Meets critical timing requirements in complex system designs

- Suitability for PC, consumer, portable, and networking applications

- Capable of Zero PPM frequency synthesis error

- Uninterrupted system operation during clock frequency switch

- Application compatibility in standard and low power systems

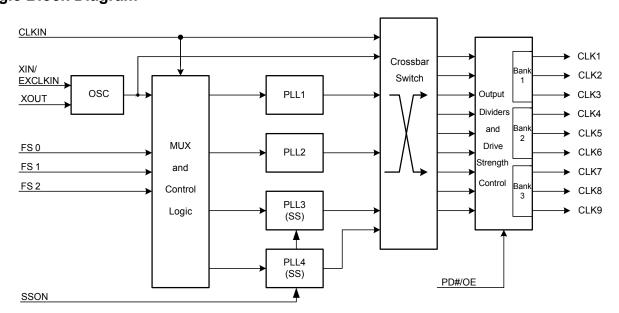

### Logic Block Diagram

### Contents

| General Description                               | . 5 |

|---------------------------------------------------|-----|

| Four Configurable PLLs                            |     |

| Input Reference Clocks                            |     |

| Multiple Power Supplies                           | . 5 |

| Output Bank Settings                              | . 5 |

| Output Source Selection                           | . 5 |

| Spread Spectrum Control                           | . 5 |

| Frequency Select                                  | . 6 |

| Glitch-Free Frequency Switch                      |     |

| PD#/OE Mode                                       | 6   |

| Output Drive Strength                             | . 6 |

| Generic Configuration and Custom Frequency        | 6   |

| Absolute Maximum Conditions                       | . 7 |

| Recommended Operating Conditions                  | . 7 |

| DC Electrical Specifications                      |     |

| AC Electrical Specifications                      |     |

| Recommended Crystal Specification for SMD Package | 9   |

| Test and Measurement Setup              | 10 |

|-----------------------------------------|----|

| Voltage and Timing Definitions          |    |

| Recommended Crystal Specification for   |    |

| Thru-Hole Package                       | 10 |

| Ordering Information                    | 11 |

| Possible Configurations                 | 11 |

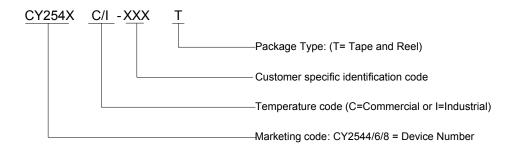

| Ordering Code Definition                | 12 |

| Package Drawing and Dimensions          |    |

| Acronyms                                | 14 |

| Document Conventions                    |    |

| Units of Measure                        |    |

| Document History Page                   | 15 |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      |    |

| Products                                |    |

| PSoC Solutions                          |    |

**Table 1. Device Selection Guide**

| Device | Crystal Input | EXCKLKIN Input             | CLKIN Input                | VDD                 | VDD_CLK_BX          |

|--------|---------------|----------------------------|----------------------------|---------------------|---------------------|

| CY2544 | Yes           | 1.8 V LVCMOS               | 2.5 V, 3.0 V, 3.3 V LVCMOS | 2.5 V, 3.0 V, 3.3 V | 2.5 V, 3.0 V, 3.3 V |

| CY2546 | Yes           | 1.8 V LVCMOS               | 1.8 V LVCMOS               | 1.8 V               | 1.8 V               |

| CY2548 | No            | 2.5 V, 3.0 V, 3.3 V LVCMOS | 2.5 V, 3.0 V, 3.3 V LVCMOS | 2.5 V, 3.0 V, 3.3 V | 2.5 V, 3.0 V, 3.3 V |

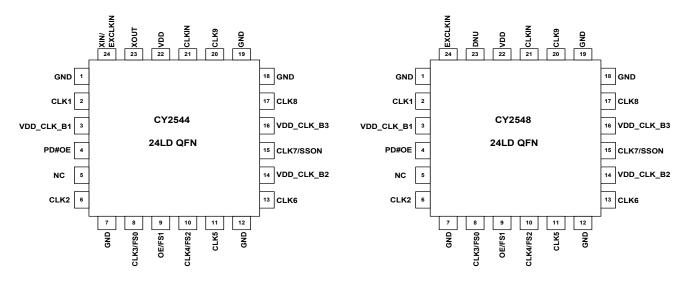

Figure 1. Pin Diagram - CY2544/CY2548 24 LD QFN

Table 2. Pin Definition - CY2544/CY2548 (VDD = 2.5 V, 3.0 V or 3.3 V Supply)

| Pin Number | Name       | 10           | Description                                                                                                                                            |

|------------|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| rin Number |            |              | Description                                                                                                                                            |

| 1          | GND        | Power        | Power supply ground                                                                                                                                    |

| 2          | CLK1       | Output       | Programmable clock output. Output voltage depends on VDD_CLK_B1 voltage                                                                                |

| 3          | VDD_CLK_B1 | Power        | Power supply for bank1, (CLK1, CLK2, CLK3) Outputs: 2.5 V/3.0 V/3.3 V                                                                                  |

| 4          | PD#/OE     | Input        | Multifunction programmable pin. Output enable or power-down mode                                                                                       |

| 5          | NC         | NC           | No Connect                                                                                                                                             |

| 6          | CLK2       | Output       | Programmable Clock Output. Output voltage depends on VDD_CLK_B1 voltage                                                                                |

| 7          | GND        | Power        | Power supply ground                                                                                                                                    |

| 8          | CLK3/FS0   | Output/input | <b>Multifunction programmable pin.</b> Programmable clock output clock or frequency select pin. Output voltage of CLK3 depends on VDD_CLK_B1 voltage   |

| 9          | OE/FS1     | Input        | Multifunction programmable pin. Output enable or frequency select pin                                                                                  |

| 10         | CLK4/FS2   | Output/input | <b>Multifunction programmable pin.</b> Programmable clock output or frequency select input pin. Output voltage of CLK4 depends on VDD_CLK_B2 voltage   |

| 11         | CLK5       | Output       | Programmable clock output. Output voltage depends on VDD_CLK_B2 voltage                                                                                |

| 12         | GND        | Power        | Power supply ground                                                                                                                                    |

| 13         | CLK6       | Output       | Programmable clock output. Output voltage depends on VDD_CLK_B2 voltage                                                                                |

| 14         | VDD_CLK_B2 | Power        | Power supply for bank2, (CLK4, CLK5, CLK6) Outputs. 2.5 V/3.0 V/3.3 V                                                                                  |

| 15         | CLK7/SSON  | Output/input | Multifunction programmable pin. Programmable clock output or spread spectrum ON/OFF control input pin. Output voltage of CLK7 depends on Bank3 voltage |

| 16         | VDD_CLK_B3 | Power        | Power supply for bank3, (CLK7, CLK8, CLK9) Outputs. 2.5 V/3.0 V/3.3 V                                                                                  |

Table 2. Pin Definition – CY2544/CY2548 (VDD = 2.5 V, 3.0 V or 3.3 V Supply) (continued)

| Pin Number | Name        | Ю      | Description                                                                                                            |

|------------|-------------|--------|------------------------------------------------------------------------------------------------------------------------|

| 17         | CLK8        | Output | Programmable output clock. Output voltage depends on Bank3 voltage                                                     |

| 18         | GND         | Power  | Power supply ground                                                                                                    |

| 19         | GND         | Power  | Power supply ground                                                                                                    |

| 20         | CLK9        | Output | Programmable clock output. Output voltage depends on VDD_CLK_B3 voltage                                                |

| 21         | CLKIN       | Input  | <b>2.5 V/3.0 V/3.3 V reference clock input.</b> The signal level of CLKIN input must track VDD power supply on pin 22. |

| 22         | VDD         | Power  | Power supply. 2.5 V/3.0 V/3.3 V                                                                                        |

| 23         | XOUT        | Output | Crystal output for CY2544                                                                                              |

|            | DNU         | Output | Do not use this pin for CY2548                                                                                         |

| 24         | XIN/EXCLKIN | Input  | Crystal input or 1.8 V external clock input for CY2544                                                                 |

|            | EXCLKIN     | Input  | 2.5 V/3.0 V/3.3 V external clock input for CY2548                                                                      |

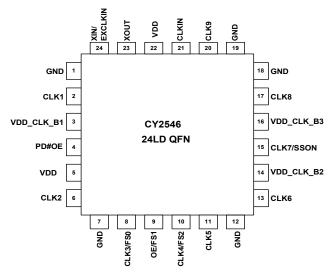

Figure 2. Pin Diagram - CY2546 24 LD QFN

Table 3. Pin Definition - CY2546 (VDD = 1.8 V Supply)

| Pin Number | Name       | Ю            | Description                                                                                                                                          |

|------------|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | GND        | Power        | Power supply ground                                                                                                                                  |

| 2          | CLK1       | Output       | Programmable clock output. Output voltage depends on VDD_CLK_B1 voltage                                                                              |

| 3          | VDD_CLK_B1 | Power        | Power supply for bank1, (CLK1, CLK2, CLK3) Outputs. 1.8V                                                                                             |

| 4          | PD#/OE     | Input        | Multifunction programmable pin. Output enable or power down mode                                                                                     |

| 5          | VDD        | Power        | Power supply. 1.8 V                                                                                                                                  |

| 6          | CLK2       | Output       | Programmable clock output. Output voltage depends on VDD_CLK_B1 voltage                                                                              |

| 7          | GND        | Power        | Power supply ground                                                                                                                                  |

| 8          | CLK3/FS0   | Output/Input | <b>Multifunction programmable pin.</b> Programmable clock output or frequency select input pin. Output voltage of CLK3 depends on VDD_CLK_B1 voltage |

| 9          | OE/FS1     | Input        | Multifunction programmable pin. Output enable or frequency select pin                                                                                |

| 10         | CLK4/FS2   | Output/Input | <b>Multifunction programmable pin.</b> Programmable clock output or frequency select input pin. Output voltage of CLK4 depends on VDD_CLK_B2 voltage |

| 11         | CLK5       | Output       | Programmable clock output. Output voltage depends on VDD_CLK_B2 voltage                                                                              |

| Pin Number | Name        | Ю            | Description                                                                                                                                                 |

|------------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12         | GND         | Power        | Power supply ground                                                                                                                                         |

| 13         | CLK6        | Output       | Programmable clock output. Output voltage depends on VDD_CLK_B2 voltage                                                                                     |

| 14         | VDD_CLK_B2  | Power        | Power supply for bank2, (CLK4, CLK5, CLK6) Outputs. 1.8 V                                                                                                   |

| 15         | CLK7/SSON   | Output/input | Multifunction programmable pin. Programmable clock output or spread spectrum ON/OFF control input pin. Output voltage of CLK7 depends on VDD_CLK_B3 voltage |

| 16         | VDD_CLK_B3  | Power        | Power supply for bank3, (CLK7, CLK8, CLK9) Outputs. 1.8 V                                                                                                   |

| 17         | CLK8        | Output       | Programmable clock output. Output voltage depends on VDD_CLK_B3 voltage                                                                                     |

| 18         | GND         | Power        | Power supply ground                                                                                                                                         |

| 19         | GND         | Power        | Power supply ground                                                                                                                                         |

| 20         | CLK9        | Output       | Programmable clock output. Output voltage depends on VDD_CLK_B3 voltage                                                                                     |

| 21         | CLKIN       | Input        | External 1.8 V low voltage reference clock input                                                                                                            |

| 22         | VDD         | Power        | Power supply. 1.8 V                                                                                                                                         |

| 23         | XOUT        | Output       | Crystal output                                                                                                                                              |

| 24         | XIN/EXCLKIN | Input        | Crystal input or 1.8 V external clock input                                                                                                                 |

### **General Description**

#### Four Configurable PLLs

The CY2544, CY2548 and CY2546 have four programmable PLLs that can be used to generate output frequencies ranging from 3 to 166 MHz. The advantage of having four PLLs is that a single device generates up to four independent frequencies from a single crystal.

### **Input Reference Clocks**

The input to the CY2544, CY2548 and CY2546 can be either a crystal or a clock signal. The input frequency range for crystal (XIN) is 8 MHz to 48 MHz and that for external reference clock (EXCLKIN) is 8 MHz to 166 MHz. The voltage range for the reference clock input of CY2548 is 2.5 V/3.0 V/3.3 V while that for CY2544 and CY2546 is 1.8 V. This gives user an option for this device to be compatible for different input clock voltage levels in the system.

There is provision for a secondary reference clock input, CLKIN with applied frequency range of 8 MHz to 166 MHz. When CLKIN signal at pin 21 is used as a reference input to the PLL, a valid signal at EXCLKIN (as specified in the AC and DC Electrical Specification table) must be present for the devices to operate properly.

#### **Multiple Power Supplies**

These devices are designed to operate at internal supply voltage of 1.8 V. In the case of the high voltage part (CY2544/CY2548), an internal regulator is used to generate 1.8 V from the 2.5 V/3.0 V/3.3 V VDD supply voltage at pin 22. For the low voltage part (CY2546), this internal regulator is bypassed and 1.8 V at VDD pin 22 is directly used.

#### **Output Bank Settings**

There are nine clock outputs grouped in three output driver banks. The Bank 1, Bank 2, and Bank 3 correspond to (CLK1, CLK2, CLK3), (CLK4, CLK5, CLK6), and (CLK7, CLK8, CLK9) respectively. Separate power supplies are used for each of these banks and they can be any of 2.5 V, 3.0 V, or 3.3 V for CY2544/CY2548 and 1.8 V for CY2546 giving user multiple choice of output clock voltage levels.

#### **Output Source Selection**

These devices have programmable input sources for each of its nine clock outputs (CLK1–9). There are six available clock sources for these outputs. These clock sources are: XIN/EXCLKIN, CLKIN, PLL1, PLL2, PLL3, or PLL4. Output clock source selection is done using four out of six crossbar switch. Thus, any one of these six available clock sources can be arbitrarily selected for the clock outputs. This gives user a flexibility to have up to four independent clock outputs.

### **Spread Spectrum Control**

Two of the four PLLs (PLL3 and PLL4) have spread spectrum capability for EMI reduction in the system. The device uses a Cypress proprietary PLL and spread spectrum clock (SSC) technology to synthesize and modulate the frequency of the PLL. The spread spectrum feature can be turned on or off using a multifunction control pin (CLK7/SSON). It can be programmed to either center spread range from ±0.125% to ±2.50% or down spread range from -0.25% to -5.0% with Lexmark or Linear profile.

### Frequency Select

There are three multifunction frequency select pins (FS0, FS1 and FS2) that provide an option to select eight different sets of frequencies among each of the four PLLs. Each output has programmable output divider options.

### Glitch-Free Frequency Switch

When the frequency select pin (FS) is used to switch frequency, the outputs are glitch-free provided frequency is switched using output dividers. This feature enables uninterrupted system operation while clock frequency is being switched.

#### PD#/OE Mode

PD#/OE (Pin 4) can be programmed to operate as either power down (PD#) or output enable (OE) mode. PD# is a low-true input. If activated it shuts off the entire chip, resulting in minimum power consumption for the device. Setting this signal high brings the device in the operational mode with default register settings.

When this pin is programmed as Output Enable (OE), clock outputs can be enabled or disabled using OE (pin 4). Individual clock outputs can be programmed to be sensitive to this OE pin.

#### **Output Drive Strength**

The DC drive strength of the individual clock output can be programmed for different values. Table 4 shows the typical rise and fall times for different drive strength settings.

Table 4. Output Drive Strength

| Output Drive Strength | Rise/Fall Time (ns)<br>(Typical Value) |

|-----------------------|----------------------------------------|

| Low                   | 6.8                                    |

**Table 4. Output Drive Strength**

| Output Drive Strength | Rise/Fall Time (ns)<br>(Typical Value) |

|-----------------------|----------------------------------------|

| Mid Low               | 3.4                                    |

| Mid High              | 2.0                                    |

| High                  | 1.0                                    |

#### **Generic Configuration and Custom Frequency**

There is a generic set of output frequencies available from the factory that can be used for the device evaluation purposes. The devices, CY2544, CY2548 and CY2546 can be custom programmed to any desired frequencies and listed features. For customer specific programming, please contact local Cypress Field application engineer (FAE) or sales representative.

### **Absolute Maximum Conditions**

| Parameter              | Description                       | Condition                   | Min  | Max                  | Unit  |

|------------------------|-----------------------------------|-----------------------------|------|----------------------|-------|

| $V_{DD}$               | Supply voltage for CY2544/CY2548  |                             | -0.5 | 4.5                  | V     |

| $V_{DD}$               | Supply voltage for CY2546         |                             | -0.5 | 2.6                  | V     |

| V <sub>DD_CLK_BX</sub> | Output bank supply voltage        |                             | -0.5 | 4.5                  | V     |

| V <sub>IN</sub>        | Input voltage for CY2544/CY2548   | Relative to V <sub>SS</sub> | -0.5 | V <sub>DD</sub> +0.5 | V     |

| V <sub>IN</sub>        | Input voltage for CY2546          | Relative to V <sub>SS</sub> | -0.5 | 2.2                  | V     |

| T <sub>S</sub>         | Temperature, storage              | Non runctional              | -65  | +150                 | °C    |

| ESD <sub>HBM</sub>     | ESD protection (Human body model) | JEDEC EIA/JESD22-A114-E     | 2000 | -                    | Volts |

| UL-94                  | Flammability rating               | V-0 at 1/8 in.              | -    | 10                   | ppm   |

| MSL                    | Moisture sensitivity level        |                             |      | 3                    |       |

### **Recommended Operating Conditions**

| Parameter              | Description                                                                                              | Min  | Тур | Max  | Unit |

|------------------------|----------------------------------------------------------------------------------------------------------|------|-----|------|------|

| $V_{DD}$               | VDD Operating voltage for CY2544/CY2548                                                                  | 2.25 | -   | 3.60 | V    |

| $V_{DD}$               | VDD Operating voltage for CY2546                                                                         | 1.65 | 1.8 | 1.95 | V    |

| V <sub>DD_CLK_BX</sub> | Output driver voltage for Bank 1, 2 and 3                                                                | 1.65 | -   | 3.60 | V    |

| T <sub>AC</sub>        | Commercial ambient temperature                                                                           | 0    | -   | +70  | °C   |

| T <sub>AI</sub>        | Industrial ambient temperature                                                                           | -40  |     | +85  | °C   |

| C <sub>LOAD</sub>      | Maximum load capacitance                                                                                 | _    | -   | 15   | pF   |

| t <sub>PU</sub>        | Power up time for all V <sub>DD</sub> to reach minimum specified voltage (power ramps must be monotonic) | 0.05 | -   | 500  | ms   |

### **DC Electrical Specifications**

| Parameter                       | Description                                                              | Conditions                                                      | Min                             | Тур | Max                   | Unit |

|---------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------|-----|-----------------------|------|

| V <sub>OL</sub>                 | Output low voltage                                                       | I <sub>OL</sub> = 2 mA, drive strength = [00]                   | _                               | -   | 0.4                   | V    |

|                                 |                                                                          | I <sub>OL</sub> = 3 mA, drive strength = [01]                   |                                 |     |                       |      |

|                                 |                                                                          | I <sub>OL</sub> = 7 mA, drive strength = [10]                   |                                 |     |                       |      |

|                                 |                                                                          | I <sub>OL</sub> = 12 mA, drive strength = [11]                  |                                 |     |                       |      |

| V <sub>OH</sub>                 | Output high voltage                                                      | $I_{OH} = -2 \text{ mA}$ , drive strength = [00]                | V <sub>DD_CLK_BX</sub><br>- 0.4 | -   | -                     | V    |

|                                 |                                                                          | $I_{OH} = -3 \text{ mA}$ , drive strength = [01]                | - 0.4                           |     |                       |      |

|                                 |                                                                          | $I_{OH} = -7 \text{ mA}$ , drive strength = [10]                |                                 |     |                       |      |

|                                 |                                                                          | $I_{OH} = -12 \text{ mA}$ , drive strength = [11]               |                                 |     |                       |      |

| V <sub>IL1</sub>                | Input low voltage of PD#/OE, FS0, FS1, FS2 and SSON                      | _                                                               | _                               | -   | 0.2 × V <sub>DD</sub> | V    |

| V <sub>IL2</sub>                | Input low voltage of CLKIN for CY2544/CY2548                             | -                                                               | -                               | -   | 0.1 × V <sub>DD</sub> | V    |

| V <sub>IL3</sub>                | Input low voltage of EXCLKIN for CY2544                                  | -                                                               | _                               | -   | 0.15                  | V    |

| V <sub>IL4</sub>                | Input low voltage of EXCLKIN for CY2548                                  | -                                                               | _                               | -   | 0.1 × V <sub>DD</sub> | V    |

| $V_{IL5}$                       | Input low voltage of CLKIN, EXCLKIN for CY2546                           | _                                                               | _                               | 1   | 0.1 × V <sub>DD</sub> | V    |

| V <sub>IH1</sub>                | Input high voltage of PD#/OE, FS0, FS1, FS2 and SSON                     | -                                                               | 0.8 × V <sub>DD</sub>           | -   | _                     | V    |

| V <sub>IH2</sub>                | Input high voltage of CLKIN for CY2544/CY2548                            | -                                                               | 0.9 × V <sub>DD</sub>           | -   | _                     | V    |

| V <sub>IH3</sub>                | Input high voltage of EXCLKIN for CY2544                                 | -                                                               | 1.6                             | -   | 2.2                   | V    |

| V <sub>IH4</sub>                | Input high voltage of EXCLKIN for CY2548                                 | -                                                               | 0.9 × V <sub>DD</sub>           | _   | -                     | V    |

| V <sub>IH5</sub>                | Input high voltage of CLKIN, EXCLKIN for CY2546                          | -                                                               | 0.9 × V <sub>DD</sub>           | _   | _                     | V    |

| I <sub>IL1</sub>                | Input low current of PD#/OE and FS1                                      | V <sub>IL</sub> = 0V                                            | _                               | _   | 10                    | μA   |

| I <sub>IH1</sub>                | Input high current of PD#/OE and FS1                                     | $V_{IH} = V_{DD}$                                               | _                               | -   | 10                    | μA   |

| I <sub>IL2</sub>                | Input low current of SSON, FS0, and FS2                                  | V <sub>IL</sub> = 0V (Internal pull dn = 160k typ)              | _                               | ı   | 10                    | μΑ   |

| I <sub>IH2</sub>                | Input high current of SSON, FS0, and FS2                                 | V <sub>IH</sub> = V <sub>DD</sub> (Internal pull dn = 160k typ) | 14                              | -   | 36                    | μΑ   |

| R <sub>DN</sub>                 | Pull down resistor of SSON, FS0, FS2 and clocks (CLK1-CLK9) in off-state | Clock outputs in off-state by setting PD# = Low                 | 100                             | 160 | 250                   | kΩ   |

| I <sub>DD</sub> [1,2]           | Supply current for CY2546                                                | PD# = High, No load                                             | _                               | 20  | _                     | mA   |

|                                 | Supply current for CY2544/CY2548                                         | PD# = High, No load                                             | _                               | 22  | _                     | mA   |

| I <sub>DDS</sub> <sup>[1]</sup> | Standby current                                                          | PD# = Low                                                       | _                               | 3   | -                     | μA   |

| C <sub>IN</sub> <sup>[1]</sup>  | Input capacitance                                                        | SSON, CLKIN, PD#/OE, FS0, FS1, and FS2 pins                     | _                               | _   | 7                     | pF   |

Notes

1. Guaranteed by design but not 100% tested.

2. Configuration dependent.

### **AC Electrical Specifications**

| Parameter                         | Description                                  | Conditions                                                                                                                | Min | Тур | Max | Unit |

|-----------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| F <sub>IN</sub> (crystal)         | Crystal frequency, XIN                       | rystal frequency, XIN                                                                                                     |     | _   | 48  | MHz  |

| F <sub>IN</sub> (clock)           | Input clock frequency (CLKIN or EXCLKIN)     | -                                                                                                                         | 8   | _   | 166 | MHz  |

| F <sub>CLK</sub>                  | Output clock frequency                       | -                                                                                                                         | 3   | _   | 166 | MHz  |

| DC1                               | Output duty cycle, All clocks except ref out | Duty cycle is defined in Figure 4; t <sub>1</sub> /t <sub>2</sub> , measured at 50% of V <sub>DD_CLK_BX</sub>             | 45  | 50  | 55  | %    |

| DC2                               | Ref Out clock duty cycle                     | Ref In Min 45%, Max 55%                                                                                                   | 40  | -   | 60  | %    |

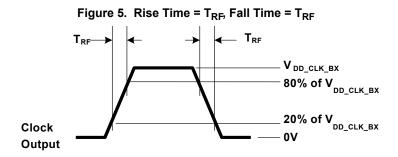

| T <sub>RF1</sub> <sup>[3]</sup>   | Output rise/fall Time                        | Measured from 20% to 80% of V <sub>DD_CLK BX</sub> , as shown in Figure 5, C <sub>LOAD</sub> = 15 pF, Drive strength [00] | ı   | 6.8 | _   | ns   |

| T <sub>RF2</sub> <sup>[3]</sup>   | Output rise/fall time                        | Measured from 20% to 80% of V <sub>DD_CLK BX</sub> , as shown in Figure 5, C <sub>LOAD</sub> = 15 pF, Drive strength [01] | -   | 3.4 | -   | ns   |

| T <sub>RF3</sub> <sup>[3]</sup>   | Output rise/fall time                        | Measured from 20% to 80% of V <sub>DD_CLK BX</sub> , as shown in Figure 5, C <sub>LOAD</sub> = 15 pF, Drive strength [10] | -   | 2.0 | _   | ns   |

| T <sub>RF4</sub> <sup>[3]</sup>   | Output rise/fall time                        | Measured from 20% to 80% of V <sub>DD_CLK BX</sub> , as shown in Figure 5, C <sub>LOAD</sub> = 15 pF, Drive strength [11] | -   | 1.0 | _   | ns   |

| T <sub>CCJ</sub> <sup>[3,4]</sup> | Cycle-to-cycle Jitter (peak)                 | Configuration dependent. See Table 5                                                                                      | _   | 150 | _   | ps   |

| T <sub>LOCK</sub> <sup>[3]</sup>  | PLL lock time                                | Measured from 90% of the applied power supply level                                                                       | -   | 1   | 3   | ms   |

### Table 5. Configuration Example for C-C Jitter

| Ref. Freq. | CLK1           | Output                 | CLK2           | Output                 | CLK3           | Output                 | CLK4           | Output                 | CLK5           | Output                 |

|------------|----------------|------------------------|----------------|------------------------|----------------|------------------------|----------------|------------------------|----------------|------------------------|

| (MHz)      | Freq.<br>(MHz) | C-C Jitter<br>Typ (ps) |

| 14.3181    | 8.0            | 134                    | 166            | 103                    | 48             | 92                     | 74.25          | 81                     | Not            | Used                   |

| 19.2       | 74.25          | 99                     | 166            | 94                     | 8              | 91                     | 27             | 110                    | 48             | 75                     |

| 27         | 48             | 67                     | 27             | 109                    | 166            | 103                    | 74.25          | 97                     | Not Used       |                        |

| 48         | 48             | 93                     | 27             | 123                    | 166            | 137                    | 166            | 138                    | 8              | 103                    |

### **Recommended Crystal Specification for SMD Package**

| Parameter       | Description                                  | Range 1 | Range 2 | Range 3 | Unit |

|-----------------|----------------------------------------------|---------|---------|---------|------|

| F <sub>IN</sub> | Crystal frequency                            | 8 – 14  | 14 – 28 | 28 – 48 | MHz  |

| R1              | Maximum motional resistance (ESR)            | 135     | 50      | 30      | Ω    |

| CL              | Parallel load capacitance (see Note 3 below) | 8 – 18  | 8 – 14  | 8 – 12  | pF   |

| DL(max)         | Maximum crystal drive level                  | 300     | 300     | 300     | μW   |

#### Notes

- 3. Guaranteed by design but not 100% tested4. Configuration dependent

### **Recommended Crystal Specification for Thru-Hole Package**

| Parameter <sup>[5]</sup> | Description                                  | Range 1 | Range 2 | Range 3 | Unit |

|--------------------------|----------------------------------------------|---------|---------|---------|------|

| F <sub>IN</sub>          | Crystal frequency                            | 8 – 14  | 14 – 24 | 24 – 32 | MHz  |

| R1                       | Maximum motional resistance (ESR)            | 90      | 50      | 30      | Ω    |

| CL                       | Parallel load capacitance (see Note 3 below) | 8 – 18  | 8 – 12  | 8 – 12  | pF   |

| DL(max)                  | Maximum crystal drive level                  | 1000    | 1000    | 1000    | μW   |

### **Test and Measurement Setup**

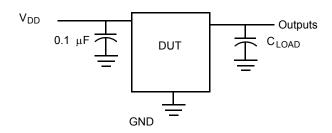

Figure 3. Test and Measurement Setup

### **Voltage and Timing Definitions**

Figure 4. Duty Cycle Definition  $t_1 - V_{DD\_CLK\_BX} - 50\% \text{ of V }_{DD\_CLK\_BX}$ Clock

Output

#### Note

<sup>5.</sup> CY2544, CY2548 and CY2546 have internal crystal load capacitance (CL) adjustment feature.

### **Ordering Information**

| Part Number   | Type <sup>[6]</sup> | Package                                                                | Supply Voltage        | Operating Range              |  |

|---------------|---------------------|------------------------------------------------------------------------|-----------------------|------------------------------|--|

| Pb-free       |                     |                                                                        |                       |                              |  |

| CY2544C       | Field Programmable  | 24-pin QFN                                                             | 2.5 V, 3.0 V or 3.3 V | Commercial, 0 °C to 70 °C    |  |

| CY2544CT      | Field Programmable  | 24-pin QFN -tape and reel                                              | 2.5 V, 3.0V or 3.3 V  | Commercial, 0 °C to 70 °C    |  |

| CY2548C       | Field Programmable  | 24-pin QFN                                                             | 2.5 V, 3.0V or 3.3 V  | Commercial, 0 °C to 70 °C    |  |

| CY2548CT      | Field Programmable  | 24-pin QFN -tape and reel                                              | 2.5 V, 3.0V or 3.3 V  | Commercial, 0 °C to 70 °C    |  |

| CY2546C       | Field Programmable  | 24-pin QFN                                                             | 1.8 V                 | Commercial, 0 °C to 70 °C    |  |

| CY2546CT      | Field Programmable  | 24-pin QFN -tape and reel                                              | 1.8 V                 | Commercial, 0 °C to 70 °C    |  |

| CY2544I       | Field Programmable  | 24-pin QFN                                                             | 2.5 V, 3.0 V or 3.3 V | Industrial, -40 °C to +85 °C |  |

| CY2544IT      | Field Programmable  | 24-pin QFN -tape and reel                                              | 2.5 V, 3.0 V or 3.3 V | Industrial, -40 °C to +85 °C |  |

| CY2548I       | Field Programmable  | 24-pin QFN                                                             | 2.5 V, 3.0 V or 3.3 V | Industrial, -40 °C to +85 °C |  |

| CY2548IT      | Field Programmable  | 24-pin QFN -tape and reel                                              | 2.5 V, 3.0 V or 3.3 V | Industrial, -40 °C to +85 °C |  |

| CY2546I       | Field Programmable  | 24-pin QFN                                                             | 1.8 V                 | Industrial, -40 °C to +85 °C |  |

| CY2546IT      | Field Programmable  | 24-pin QFN -tape and reel                                              | 1.8 V                 | Industrial, -40 °C to +85 °C |  |

| Programmer    | •                   |                                                                        | - '                   |                              |  |

| CY3675-CLKMA  | KER1                | Programming kit                                                        |                       |                              |  |

| CY3675-QFN24A | 1                   | Socket adapter board, for programming CY2544 and CY2548 <sup>[7]</sup> |                       |                              |  |

Some product offerings are factory programmed customer specific devices with customized part numbers.

The Possible Configurations table shows the available device types, but not complete part numbers. Contact your local Cypress FAE of Sales Representative for more information.

### **Possible Configurations**

| Part Number <sup>[8]</sup> | Type <sup>[6]</sup> | Package                   | Supply Voltage        | Operating Range              |

|----------------------------|---------------------|---------------------------|-----------------------|------------------------------|

| Pb-free                    |                     | •                         |                       |                              |

| CY2544Cxxx                 | Factory Programmed  | 24-pin QFN                | 2.5 V, 3.0 V or 3.3 V | Commercial, 0 °C to 70 °C    |

| CY2544CxxxT                | Factory Programmed  | 24-pin QFN -tape and reel | 2.5 V, 3.0 V or 3.3 V | Commercial, 0 °C to 70 °C    |

| CY2548Cxxx                 | Factory Programmed  | 24-pin QFN                | 2.5 V, 3.0 V or 3.3 V | Commercial, 0 °C to 70 °C    |

| CY2548CxxxT                | Factory Programmed  | 24-pin QFN -tape and reel | 2.5 V, 3.0 V or 3.3 V | Commercial, 0 °C to 70 °C    |

| CY2546Cxxx                 | Factory Programmed  | 24-pin QFN                | 1.8 V                 | Commercial, 0 °C to 70 °C    |

| CY2546CxxxT                | Factory Programmed  | 24-pin QFN -tape and reel | 1.8 V                 | Commercial, 0 °C to 70 °C    |

| CY2544Ixxx                 | Factory Programmed  | 24-pin QFN                | 2.5 V, 3.0 V or 3.3 V | Industrial, -40 °C to +85 °C |

| CY2544IxxxT                | Factory Programmed  | 24-pin QFN -tape and reel | 2.5 V, 3.0 V or 3.3 V | Industrial, -40 °C to +85 °C |

| CY2548lxxx                 | Factory Programmed  | 24-pin QFN                | 2.5 V, 3.0 V or 3.3 V | Industrial, -40 °C to +85 °C |

| CY2548IxxxT                | Factory Programmed  | 24-pin QFN -tape and reel | 2.5 V, 3.0 V or 3.3 V | Industrial, -40 °C to +85 °C |

| CY2546lxxx                 | Factory Programmed  | 24-pin QFN                | 1.8 V                 | Industrial, -40 °C to +85 °C |

| CY2546lxxxT                | Factory Programmed  | 24-pin QFN -tape and reel | 1.8 V                 | Industrial, -40 °C to +85 °C |

#### Notes

Field Programmable devices are shipped unprogrammed, and must be programmed before being installed on a board. Factory Programmed devices are shipped fully configured and ready to install on a board.

The CY3675-QFN24A cannot be used to program the CY2546.

"xxx" is a variable that denotes a specific device configuration. For more details, contact your local Cypress FAE or Cypress Sales Representative.

### **Ordering Code Definition**

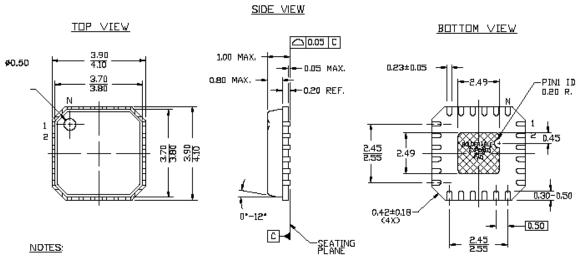

### **Package Drawing and Dimensions**

Figure 6. 24-LD QFN 4x4 mm (Subcon Punch Type Pkg with 2.49x2.49 EPAD) LF24A/LY24A

- 1. M HATCH IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT: 0.042g

- 4. ALL DIMENSIONS ARE IN MM [MIN/MAX]

- 5. PACKAGE CODE 51-85203 \*B

### **Acronyms**

| Acronym   | Description                                                                     |

|-----------|---------------------------------------------------------------------------------|

| DL        | drive level                                                                     |

| DNU       | do not use                                                                      |

| DUT       | device under test                                                               |

| EMI       | electromagnetic interference                                                    |

| ESD       | electrostatic discharge                                                         |

| FAE       | field application engineer                                                      |

| FS        | frequency select                                                                |

| JEDEC EIA | joint electron devices<br>engineering council electronic<br>industries alliance |

| LVCMOS    | low voltage complemetary metal oxide semiconductor                              |

| OE        | output enable                                                                   |

| OSC       | oscillator                                                                      |

| PD        | power down                                                                      |

| PLL       | phase locked loop                                                               |

| PPM       | parts per million                                                               |

| SS        | spread spectrum                                                                 |

| SSC       | spread spectrum clock                                                           |

| SSON      | spread spectrum on                                                              |

### **Document Conventions**

### **Units of Measure**

| Symbol | Unit of Measure   |

|--------|-------------------|

| °C     | degrees Celsius   |

| fF     | femtofarads       |

| mA     | milliampere       |

| MHz    | megahertz         |

| μS     | microseconds      |

| ms     | millisecond       |

| μW     | microwatts        |

| ns     | nanoseconds       |

| pF     | picofarads        |

| ppm    | parts per million |

| ps     | picoseconds       |

| V      | volts             |

| Ω      | ohms              |

| W      | watts             |

### **Document History Page**

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 690257  | RGL                | See ECN            | New Datasheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *A       | 790516  | RGL                | See ECN            | Separated the Pin Configuration drawing into two to show the difference between CY2544 and CY2546 pinouts. Changed the IDD from 22 mA maximum to 25 mA typical Changed I $_{ILSR}$ Internal pull down from 100K to 160K Changed I $_{IHSR}$ Internal pull down from 100K to 160K and changed the maximum value from 10 $\mu$ A to 25 $\mu$ A Changed I $_{ILPDOE}$ to No Internal pull up and changed the maximum value from 10 $\mu$ A to 1 $\mu$ A Changed I $_{IHPDOE}$ to no Internal pull up                                                                                                                                                                                                                                                                                             |

| *B       | 1508943 | RGL/AESA           | See ECN            | Changed the $I_{ILSR}$ maximum value to 10 uA Changed the $I_{ILPDOE}$ and $I_{IHPDOE}$ values to a minimum of 1 $\mu$ A to a maximum of 10 $\mu$ A Removed Preliminary from Title page Changed the $I_{IHPD}$ from 1 uA to 10 uA Changed the $I_{ILSR}$ from 1 uA to 10 uA Added new $I_{DDS}$ value = 3uA Added new C-C Jitter typical values, Deleted Long term Jitter values Deleted generic part numbers from Ordering Information Added new device and specification for high ref input voltage part, CY2548 Changed I2C Tsu specification from 100ns to 250 ns Changed ESD spec from MIL-STD to JEDEC Combined VDD operating condition spec for CY2545 to a single VDD spec In DC spec.: FS1 pin has no pull down resistor Added device selection table 1 Removed C0 from crystal spec |

| *C       | 2748211 | TSAI               | 08/10/09           | Posting to external web.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| *D       | 2764011 | CXQ                | 09/15/09           | Fixed typo in Ordering Information table – changed CY2548Cxxx and CY2548CxxxT to CY2548Ixxx and CY2548IxxxT for industrial temp parts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *E       | 2899758 | KVM                | 03/26/10           | Updated Ordering information table. Updated package diagram Updated copyright section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *F       | 2969587 | KVM                | 07/09/2010         | Minor change: Matched spec title on the first page to document history page. Added "WITH SPREAD SPECTRUM" in first page title.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *G       | 3115710 | BASH               | 12/21/2010         | Added Ordering Code Definition, Acronyms and Units of Measure table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Automotive cypress.com/go/automotive Clocks & Buffers cypress.com/go/clocks Interface cypress.com/go/interface cypress.com/go/powerpsoc cypress.com/go/plc

Memory cypress.com/go/memory

Optical & Image Sensing cypress.com/go/image

PSoC cypress.com/go/psoc

Touch Sensing cypress.com/go/touch

USB Controllers cypress.com/go/USB

Wireless/RF cypress.com/go/wireless

#### **PSoC Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5

© Cypress Semiconductor Corporation, 2007-2010. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 001-12563 Rev. \*G

Revised December 21, 2010

Page 16 of 16

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Cypress Semiconductor:

CY2546FC CY2548FCT CY2546FCT