TOSHIBA TC9331F

**TENTATIVE**

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC9331F

### **AUDIO DIGITAL SIGNAL PROCESSOR**

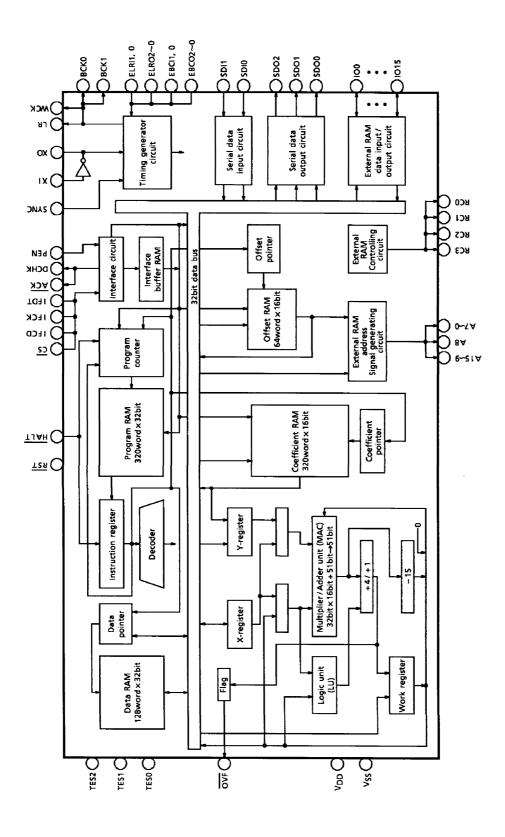

The TC9331F digital integrated circuit facilitates real time processing of digital signals in audio equipment for digital filters such as equalizers, dynamic range controllers for compressors and expanders, as well as acoustic field simulators that produce concert hall effects. The TC9331F is a-high speed, high-definition audio digital processor.

#### **FEATURES**

- The TC9331F features a 32bit main bus.

- The TC9331F is capable of both reading from and writing to external sources of RAM data and allows for the simultaneous accumulation, operation, and integration of the data that needs to be processed.

Multiplier / adder :  $32bit \times 16bit + 51bit \rightarrow 51bit$

Shifter: +4, +1bit shift

Accumulator: 51bit (code extension 4bit)

Work register: 2 registers (32 and 47bit)

Program RAM: 320 words x 32bit

Data RAM: 128 words x 32bit [Mode 1], (128 words x 16bit) x 2 [Mode 2]

Coefficient RAM: 320 words x 16bit Offset address RAM: 64 words x 16bit

• The interface parameters for external RAM sources are as follows:

Data word length: Both 16bit and 32bit

External RAM: 1M DRAM, 256K DRAM, 256K pseudo-static RAM (PSRAM)

• The following five ports have been made available for use as serial data ports.

Serial data input ports: 2 ports (SDI0, SDI1)

Serial data output ports: 3 ports (SDO0, SDO1, SDO2)

Data word length:

Both 16 and 32bit

2's complement, MSB first

- The program's settings, coefficient data, and offset data can be made converted through the microprocessor interface.

- The CMOS construction of the TC9331F makes high-speed processing possible.

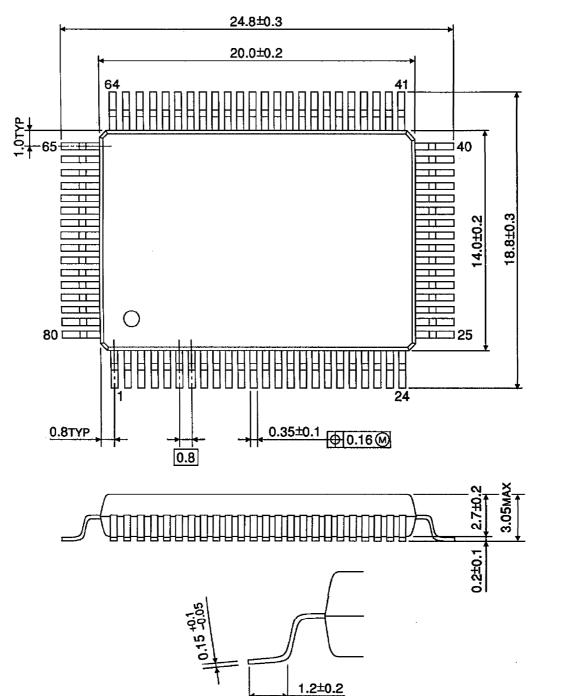

- The TC9331F features a flat, 80 pin package design.

Weight: 1.57g (Typ.)

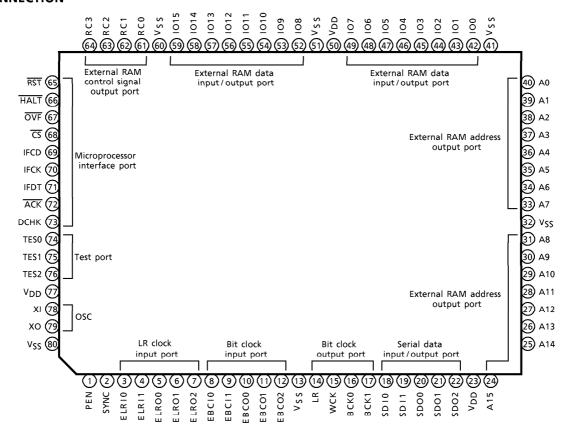

#### **PIN CONNECTION**

TC9331F-3

# **DESCRIPTION OF PIN FUNCTIONS**

| PIN<br>No.            | SYMBOL  | 1/0 | DESCRIPTION OF PIN F                                                                                                         | FUNCTION                  | REMARK                            |

|-----------------------|---------|-----|------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------------|

| 1                     | PEN     | ı   | Parity-check-function-enabling terminal Sets up the execution of the interface parity).                                      |                           | Pull-up resistor                  |

| 2                     | SYNC    | _   | Synchronous signal input terminal. The synchronous signal forcibly resets "zero", and the polarity is set by the controller. | . •                       | Schmidt input<br>Pull-up resistor |

| 3                     | ELRI0   |     | LR clock input terminal.                                                                                                     | For SDIO data input       |                                   |

| 4                     | ELRI1   | ı   | Input terminal for the SDIO/1 data processing LR clock.                                                                      | For SDI1 data input       | _                                 |

| 5                     | ELRO0   |     | LR clock input terminal.                                                                                                     | For SDO0 data output      |                                   |

| 6                     | ELRO1   | -   | Input terminal for the SDO0/1/2                                                                                              | For SDO1 data output      | <u> </u>                          |

| 7                     | ELRO2   |     | data processing LR clock.                                                                                                    | For SDO2 data output      |                                   |

| 8                     | EBCI0   | 1   | Bit clock input terminal. Input terminal for the SDIO/1 data                                                                 | For SDIO data input       |                                   |

| 9                     | EBCI1   | •   | processing shift clock.                                                                                                      | _                         |                                   |

| 10                    | EBCO0   |     | Bit clock input terminal.                                                                                                    | For SDO0 data output      |                                   |

| 11                    | EBCO1   | - 1 | Input terminal for the SDO0/1/2                                                                                              | For SDO1 data output      | _                                 |

| 12                    | EBCO2   |     | data processing shift clock.                                                                                                 | For SDO2 data output      |                                   |

| 14                    | LR      | 0   | LR clock output terminal. (1fs)                                                                                              |                           | <u> </u>                          |

| 15                    | WCK     | 0   | Word clock output terminal. (2fs)                                                                                            |                           | _                                 |

| 16                    | BCK0    | 0   | Bit clock output terminal. (32fs)                                                                                            |                           | _                                 |

| 17                    | BCK1    | 0   | Bit clock output terminal. (64fs)                                                                                            |                           | <u> </u>                          |

| 18                    | SDI0    |     | Serial data input terminals.                                                                                                 | 221-14 461-14 14          |                                   |

| 19                    | SDI1    | I   | The microcomputer controller allows 3 lengths to be selected.                                                                | szbit of Tobit Input data | _                                 |

| 20                    | SDO0    |     | Serial data output terminals.                                                                                                |                           |                                   |

| 21                    | SDO1    | 0   | The microcomputer controller allows data lengths to be selected.                                                             | s 32bit or 16bit output   | _                                 |

| 22                    | SDO2    | 0   | Serial data output terminal.                                                                                                 |                           | _                                 |

|                       |         |     | Outputs 16bit data.                                                                                                          | le .                      |                                   |

| 24                    | A15     |     | External RAM address output termina Generally used when in the pseudo-st                                                     |                           |                                   |

| 2 <del>4</del><br>  } | A 13    | 0   | dynamic RAM mode, this terminal is                                                                                           | _                         |                                   |

| 31                    | ,<br>A8 |     | Note, however, that A8 is used for c                                                                                         |                           |                                   |

|                       |         |     | purposes in the 1 M Dram (4bit×256                                                                                           |                           |                                   |

| 33                    | A7      |     | External RAM address output termina                                                                                          |                           |                                   |

| 5                     | \$      | 0   | In the dynamic RAM mode, both the                                                                                            | _                         |                                   |

| 40                    | A0      |     | addresses are output from these term                                                                                         | inals.                    |                                   |

| PIN<br>No.       | SYMBOL             | 1/0 |                                                               |                                                                                                                                                                                                     | REMARK                                                                     |       |                                                                                               |                                   |

|------------------|--------------------|-----|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------|-----------------------------------|

| 42               | 100                |     | Data input/output to and from the external RAM source.        |                                                                                                                                                                                                     |                                                                            |       |                                                                                               |                                   |

| \<br>\<br>\<br>\ | \<br>\<br>\<br>IO7 |     |                                                               | DATA<br>LENGTH                                                                                                                                                                                      | 1/00~1/07                                                                  |       | I/O8~I/O15                                                                                    |                                   |

| 52               | 107                | 1/0 |                                                               | 16bit                                                                                                                                                                                               | Low priority 8b<br>(D7-D <sub>0</sub> )                                    | it    | High priority 8bit<br>(D <sub>15</sub> -D <sub>8</sub> )                                      | Pull-up resistor                  |

| 52<br>59         | \<br>\<br>IO15     |     |                                                               | 32bit                                                                                                                                                                                               | Low priority 16t<br>(D <sub>23</sub> -D <sub>16</sub> )/(D <sub>7</sub> -D |       | High priority 16bit<br>(D <sub>31</sub> -D <sub>24</sub> )/(D <sub>15</sub> -D <sub>8</sub> ) |                                   |

|                  | 0~RC3              |     | ·                                                             | Psoudo-stati                                                                                                                                                                                        | ic RAM mode )                                                              |       | ( Dynamic RAM mode )                                                                          |                                   |

| 61               | RC0                | О   | CE                                                            |                                                                                                                                                                                                     | ole signal output                                                          | RAS   | 5: Low address strobe output terminal.                                                        | _                                 |

| 62               | RC1                | 0   | No <sup>-</sup>                                               | t in use.                                                                                                                                                                                           |                                                                            | CAS   | S: Column address strobe output terminal.                                                     | _                                 |

| 63               | RC2                | o   | ŌĒ                                                            |                                                                                                                                                                                                     | put enable /<br>esh signal output<br>ninal.                                | ŌĒ    | : Output enabling signal output terminal.                                                     | _                                 |

| 64               | RC3                | 0   | R/                                                            | R/W: Read/write signal output terminal. WTITE: Read/write signal output terminal.                                                                                                                   |                                                                            |       |                                                                                               | _                                 |

| 65               | RST                | I   | Res                                                           | Reset signal input terminal.                                                                                                                                                                        |                                                                            |       |                                                                                               | Pull-up resistor                  |

| 66               | HALT               | I   | Wh<br>inst                                                    | Halt signal input terminal.  When "L" is active, the program counter is stopped and nstructions are rendered as NOP.  Generally used in the emulation mode.                                         |                                                                            |       |                                                                                               | Schmidt input<br>Pull-up resistor |

| 67               | OVF                | 0   |                                                               | erflow outpu<br>ivates "L" w                                                                                                                                                                        |                                                                            | occu  | rs during operations.                                                                         | Open drain output.                |

| 68               | CS                 | I   | Wh                                                            |                                                                                                                                                                                                     | signal terminal.<br>is in an "L" 's ac                                     | tive, | data can be transferred                                                                       | Schmidt input.                    |

| 69               | IFCD               | -   | teri<br>con                                                   | Microcomputer command or data input mode selection terminal. When "H" is active, the terminal acts as a command selection terminal; when "L" is active, it acts as a data input selection terminal. |                                                                            |       |                                                                                               | Schmidt input.                    |

| 70               | IFCK               | I   | Shift clock input terminal for microcomputer data processing. |                                                                                                                                                                                                     |                                                                            |       | Schmidt input.                                                                                |                                   |

| 71               | IFDT               | 1   | Red                                                           | Microcomputer data processing input terminal. Receives commands and data to which one parity bit has been added at the LSB first.                                                                   |                                                                            |       |                                                                                               | Schmidt input.                    |

| 72               | ACK                | 0   | Ou                                                            | knowledge o<br>tputs an ack<br>rity are accer                                                                                                                                                       | Open drain output.<br>Pull-up resistor                                     |       |                                                                                               |                                   |

| PIN<br>No.                       | SYMBOL            | 1/0 | DESCRIPTION OF PIN FUNCTION                                                                                                                                                                                         | REMARK                                 |

|----------------------------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 73                               | DCHK              | 0   | Microcomputer return output terminal. At the same time that the IFCK is initiated, the terminal outputs the received data. In the emulation mode, the terminal also sends out an "L", the break acknowledge signal. | Open drain output.<br>Pull-up resistor |

| 74<br>\$<br>76                   | TESO<br>S<br>TES2 | I   | Test terminal. Usually used in an "H", or open, position.                                                                                                                                                           | Pull-up resistor                       |

| 78                               | ΧI                | _   | Crystal oscillator connection terminal.                                                                                                                                                                             |                                        |

| 79                               | хо                | 0   | crystal oscillator conflection terminal.                                                                                                                                                                            | <u> </u>                               |

| 23<br>50<br>77                   | V <sub>DD</sub>   |     | Power supply terminal.                                                                                                                                                                                              | _                                      |

| 13<br>32<br>41<br>51<br>60<br>80 | V <sub>SS</sub>   |     | Ground terminal.                                                                                                                                                                                                    | _                                      |

#### **OPERATING INSTRUCTIONS**

- 1. Timing sequence generating circuit.

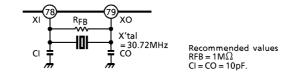

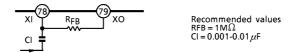

- (1) Crystal-controlled oscillator circuit

An internal operations clock can be created by connecting a crystal-controlled oscillator (30.72 MHz), condenser, and resistor in the manner shown in Figure 1 below.

An alternative method would be to connect a external clock to the XI terminal as shown in Figure 2 below.

Fig.1(a) Self excited crystal oscillator

For external clock purposes, a crystal with a good starting potential and low CI value is recommended.

Fig.1(b) External clock Input.

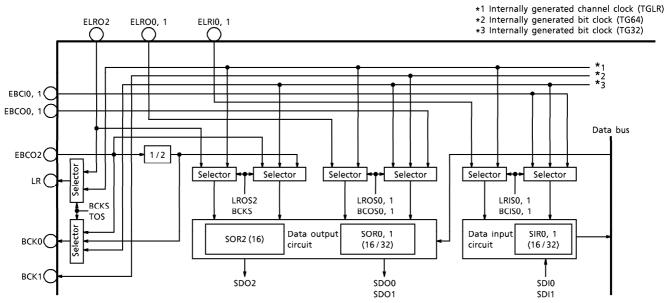

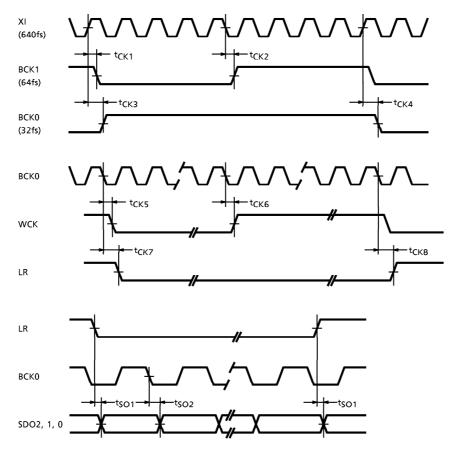

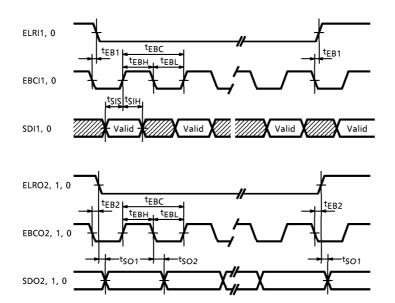

(2) The generating circuit for the audio data input/output clock (channel clock and bit clock)

Both internal generating and external input modes are available for 16/32bit serial data input/output channel (LR, ELRI0-1, and ELRO0-2) and bit (BCK0, EBCI0-1, EBCO0-2) clocks.

As shown in Figure 1(b), the channel clock is selected by LROS0-2 and LRIS0-1, and the bit clock by BCOS0-1, BCIS0-1, and BCKS of control register 2, respectively.

Both 16bit and 32bit outputs are available in internal clock generation mode (SDO2 is bypassed). The mode setup is accomplished through the microcomputer interface (control register 2).

(For further details please refer to the Explanation of the Microcomputer Interface Control Register Functions.)

The data input (SDI1 and SDI0) channel clock and bit clock are selected by LRIS1 and LRIS0, and BCIS1 and BCIS0 of control register 2, respectively.

Tables 1. (a) and 1. (b) below provide details regarding the data input (SDI1 and SDI0) modes.

|                                |       |       | , , , , , , , , , , , , , , , , , , , , |                |  |

|--------------------------------|-------|-------|-----------------------------------------|----------------|--|

| CONTROL REGISTER 2<br>(CNT-R2) |       |       | DATA INPUT APPLICATIONS (SDI1)          |                |  |

|                                | LRIS1 | BCIS1 | CHANNEL CLOCK/BIT CLOCK                 | DATA BIT COUNT |  |

|                                | 0     | 0     | Internally generated TGLR/(TG32/TG64)   | 16bit          |  |

|                                | 0     | 1     | Internally generated TGLR/(TG32/TG64)   | 32bit          |  |

|                                | 1     | Х     | External input ELRI1/EBCI1              | _              |  |

Table 1. (a) The (SDI1) data input channel clock and bit clock modes

Table 1. (b) The (SDI0) data input channel clock and bit clock modes

| CONTROL I<br>(CNT | REGISTER 2<br>-R2) | DATA INPUT APPLICATIONS (SDI0)        |                |  |

|-------------------|--------------------|---------------------------------------|----------------|--|

| LRIS0             | BCIS0              | CHANNEL CLOCK/BIT CLOCK               | DATA BIT COUNT |  |

| 0                 | 0                  | Internally generated TGLR/(TG32/TG64) | 16bit          |  |

| 0                 | 1                  | Internally generated TGLR/(TG32/TG64) | 32bit          |  |

| 1                 | Х                  | External input ELRIO/EBCIO            | _              |  |

The data output (SDO1 and SDO0) channel clock and bit clock are selected by LROS1 and LROS0, and BCOS1 and BCOS0 of control register 2, respectively.

Tables 2. (a) and 2. (b) below provide details regarding the data output (SDO1 and SDO0) modes.

Table 2. (a) The (SDO1) data output channel clock and bit clock modes

|       | REGISTER 2<br>-R2) | DATA INPUT APPLICATIONS (SDO1) |                |  |

|-------|--------------------|--------------------------------|----------------|--|

| LROS1 | BCOS1              | CHANNEL CLOCK/BIT CLOCK        | DATA BIT COUNT |  |

| 0     | 0                  | Internally generated TGLR/TG32 | 16bit          |  |

| 0     | 1                  | Internally generated TGLR/TG64 | 32bit          |  |

| 1     | Х                  | External input ELRO1/EBCO1     | _              |  |

Table 2. (b) The (SDO0) data output channel clock and bit clock modes

|       | REGISTER 2<br>T-R2) | DATA INPUT APPLICATIONS (SDO0) |                |  |

|-------|---------------------|--------------------------------|----------------|--|

| LROS0 | BCOS0               | CHANNEL CLOCK/BIT CLOCK        | DATA BIT COUNT |  |

| 0     | 0                   | Internally generated TGLR/TG32 | 16bit          |  |

| 0     | 1                   | Internally generated TGLR/TG64 | 32bit          |  |

| 1     | Х                   | External input ELRO0/EBCO0     | _              |  |

The LR and BCK terminals as well as the SDO2 channel clock and bit clock are selected from BCKS, TOS, and LROS2 of control register 2.

The data output (SDO2), LR, and BCK terminal output modes are shown in Table 3 below.

Table 3. LR and BCK terminal output, and (SDO2) data channel clock and bit clock modes

| CONTROL REGISTER 2<br>(CNT-R2) |     |       | LR TERMINAL OUTPUT /<br>BCKO TERMINAL OUTPUT | DATA OUTPUT (SDO2)             |                               |

|--------------------------------|-----|-------|----------------------------------------------|--------------------------------|-------------------------------|

| BCKS                           | TOS | LROS2 | CHANNEL CLOCK                                | (/BIT CLOCK                    |                               |

| 0                              | 0   | 0     | Internally generated TGLR/TG32               | Internally generated TGLR/TG32 |                               |

| 0                              | 0   | 1     | Internally generated TGLR/TG32               | External input ELRO2/EBCO2     |                               |

| 0                              | 1   | 0     | External input ELRO2/EBCO2                   | Internally generated TGLR/TG32 |                               |

| 0                              | 1   | 1     | External input ELRO2/EBCO2                   | External input ELRO2/EBCO2     |                               |

| 1                              | 0   | 0     | Internally generated TGLR/1/2                | Internally generated TGLR/1/2  |                               |

| <b>'</b>                       | U   | 0     | frequency of EBCO2                           | frequency of EBCO2             |                               |

| 1                              | 0   | 1     | Internally generated TGLR/1/2                | External input ELRO2/1/2       |                               |

| <u>'</u>                       | U   | '     | frequency of EBCO2                           | frequency of EBCO2             |                               |

| 1                              | 1   | 1     | 0                                            | External input ELRO2/1/2       | Internally generated TGLR/1/2 |

| '                              | -   | Ŭ     | frequency of EBCO2                           | frequency of EBCO2             |                               |

| 1                              | 1   | 1     | External input ELRO2/1/2                     | External input ELRO2/1/2       |                               |

|                                | 1   | '     | frequency of EBCO2                           | frequency of EBCO2             |                               |

Fig.2 The data input/output clock selection circuit

#### 2. The Data Input And Data Output Circuits

#### (1) Data Input Circuit

#### (1-1) Data input circuit

The input data is conveyed as a 2's complement expression and corresponds to the padding following the MSB first. The SIR1 and SIR0 input register can be selected for 16 or 32bit data count applications. The timing signals of the SDI1 and SDI0 input data can be input both independently and externally to the channel clock (LRCK) and bit clock (BCK). Note that internally generated modes are also available for the LRCK and BCK. The rising and falling of the LRCK trailing edge is first detected and then the input data is received internally.

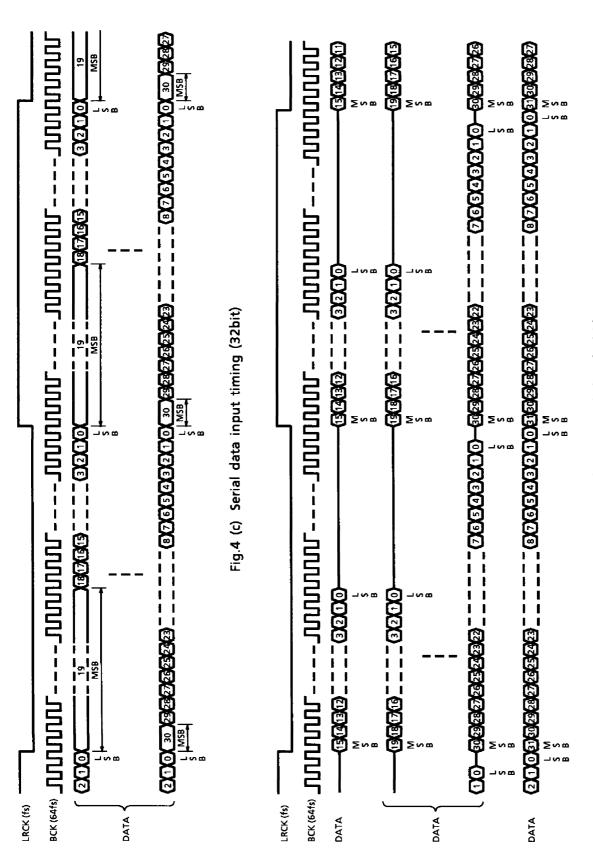

#### (1-2) Data input format

- Refer to Figures 3 and 4 (a) when the input data is 16bit/ch.

When the BCK is at least 32fs but not more than 64fs, the data is received later from the padding.

- When the input data is at least 17bit but not more than 32bit, refer to Figures 4(b) and 4(c).

The input register should be set up for 32bit processing. As shown in Figures 4 (b) and 4 (c), data is put into the padding and the priority bit modified before inputting. In order to input data before it is put into the padding, the input register must be set for 32bit and, as shown in Figure 5, the remaining data must be reset to "zero".

TC9331F- 10

Fig.5 Serial data input timing (32bit)

FC0334E \_ 11

#### (2) Data Output Circuit

#### (2-1) Data output circuit

The output data is conveyed as a 2's complement expression and is the pre-padded data of the MSB first. The SOR2 is a 16bit fixed register while the SOR1 and SOR0 can be selected as either 16bit or 32bit registers. The timing signals of the SDO2, SDO1 and SDO0 output data can be input both independently and externally to the channel clock (LRCK) and bit clock (BCK). Note that internally generated modes are also available for the LRCK and BCK. The rising and falling of the LRCK trailing edge is first detected and then the data is output to the PISO register.

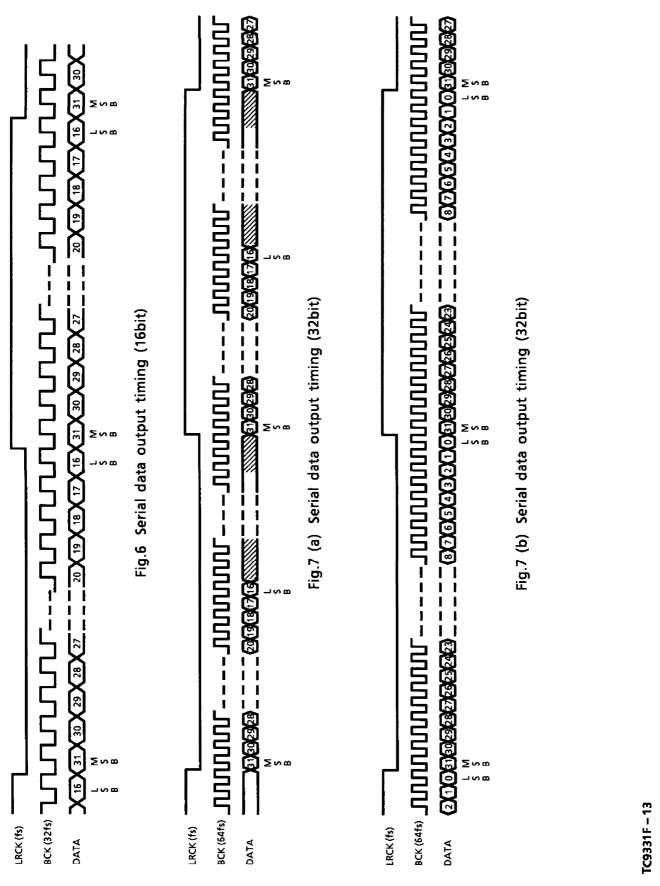

#### (2-2) Data output format

The output data from the MSB database is either 16 or 32bit. When the BCK is equal to 32fs, the output data is in the format shown in Figure 6. When the BCK is 64fs, as shown in Figure 7(a), data past the 16th bit of SDO2 is first modified then output by the LSB. Note that the data past the 16th bit may also be modified and output by the secondary channel data LSB, depending on the program's processing content. When the BCK input (EBCO2) of the SDO2 is set to 64s, a clock may be set to one half the value in the BCK. In this instance, the output format will be as shown in Figure 6. The output formats for SDO1 and SDO0 are as shown in Figure 7(b). The output for the LR and BCK0 terminals can be selected for either internally generated signals or externally inputted signals. Consequently, the LR and BCK0 output can be used as A/D and D/A converter timing signals.

When the DIR (digital audio I/F receiver) is in use, the LR and BCKO are set up to receive external input signals (ELRO2 and EBCO2) and to provide the D/A converter timing signals.

When the BCK of the DIR is 64fs, and an applicable BCK of 32fs is desired, the mode setting and BCK input are externally output from the BCK0 at 1/2 the clock rate. This BCK0 output can be used as a D/A converter timing signal by inputting the BCK0 output to the EBCO1 and EBCO0.

When an A/D converter is use, the internally generated signals are used as D/A converter timing signals.

#### 3. Microcomputer Interface Circuit

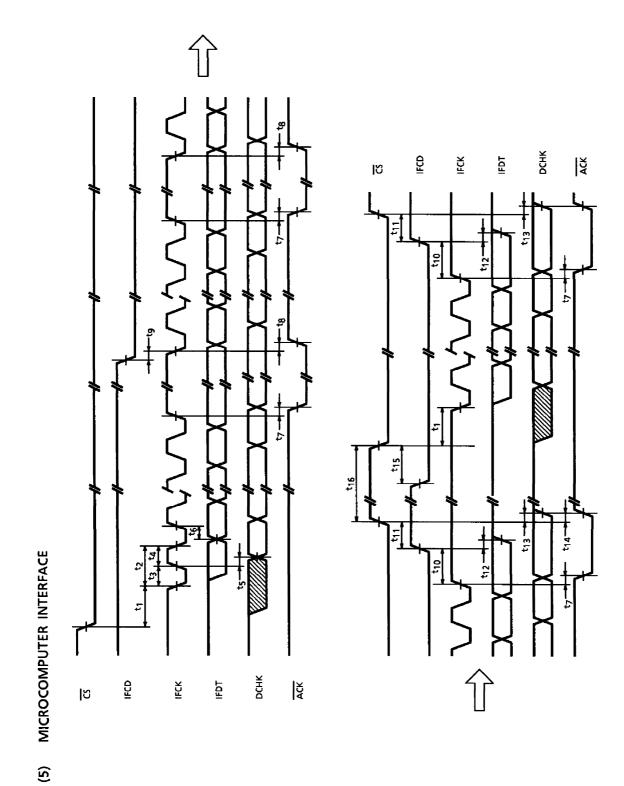

Through the  $\overline{\text{CS}}$ , IFCD, IFCK, IFDT, and ( $\overline{\text{ACK}}$  and DCHK) terminals, the TC9331F transfers synchronized serial data between itself and the host microcomputer.

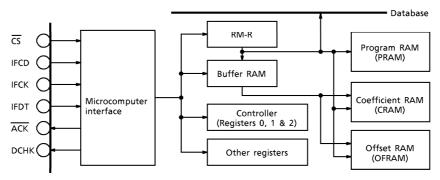

Fig.8 Microcomputer Interface Block Structure

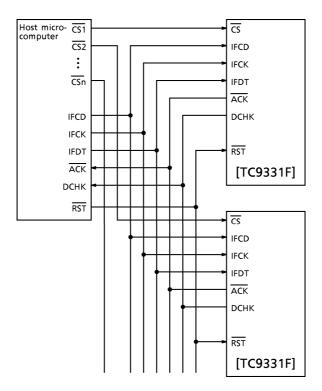

Fig.9 The relationship between the host microcomputer and the TC9331F

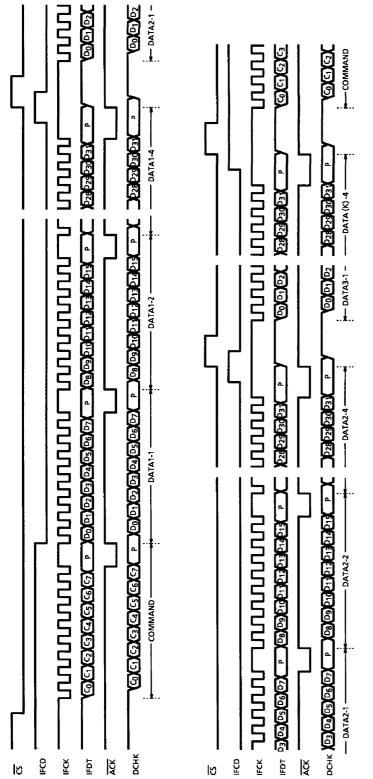

#### (1) Data Transfer Format

When idle, the  $\overline{\text{CS}}$ , IFCD, IFCK, and IFDT signals are set to "H". The standard unit of data transferred from the host microcomputer is an 8bit (1byte) unit to which an odd, 1bit parity has been added. However, when a parity check is not conducted, a dummy bit is substituted. There are two types of transfer data: single-byte command words and one to four-byte data words. The number of data word bytes depends on the command byte. The data is transferred from the LSB first and the dummy bit at the MSB end of the transferred data is set to "0". The microcomputer interface terminal signals and their functions are listed below.

CS signal (input) : Activation signal for TC9331F data reception

IFCD signal (input) : Signal used to differentiate command words from data words.

IFCK signal (input) : Shift clock for the data signal.

IFDT signal (input) : Data signal.

ACK signal (output) : The acknowledge signal for the results of the parity check.

DCHK signal (output) : Synchronizes the data signal with the TC9331F system clock and

outputs the data at the rise of the IFCK trailing edge.

The host microcomputer is able to check for data transfer errors using the ACK and DCHK signals.

The 12 different (write) commands that may be used by the host microcomputer to control the TC9331F are listed in Table 4 below.

DATA WORD (EXCLUDE PARITY) DATA IS WRITTEN TO COMMAND WORD THE FOLLOWING TRANSFER BYTE (HEX) LENGTH OF BIT USED **ADDRESS** LENGTH 0F 15 2 CNT-R2 0E 8 1 CNT-R1 0D 8 1 CNT-R0 0C 9 2 STAD-R 0B 5 TXW-R 1 0A 32 4 PRAM 2 09 16 **CRAM** 80 2 **OFRAM** 16 4 07 32 RM-R 06 3 1 XINT-R XRMD-R 05 5 1 9 2 **BRKA-R** 04 03 02 Not assigned 01 00

Table 4. Command Words

# (2) The Control Register and the I/F Dedicated Register

# (2-1) Control register 2 (CNT-R2)

(\* = Default value)

|            |            |              |                                                        |                             |                                     |                        | (* = Delault Value)             |  |

|------------|------------|--------------|--------------------------------------------------------|-----------------------------|-------------------------------------|------------------------|---------------------------------|--|

| BIT        | SYMBOL     |              |                                                        |                             | FUNCTION                            |                        |                                 |  |

| 14         | LRIS1      | Select       | ts the                                                 | channel clock and bi        | t clock for the audio               | 0*                     | Internally generated            |  |

| '4         | LNIST      | serial       | data                                                   | input from the SDI1 t       | erminal.                            | 1                      | Externally generated            |  |

| 13         | BCIS1      | Select       | ts the                                                 | bit count for the au        | dio serial data input               | 0*                     | 16bit                           |  |

| 13         | ВСІЗТ      | from         | the S                                                  | DI1 terminal.               |                                     | 1                      | 32bit                           |  |

| 12         | LRIS0      | Select       | ts the                                                 | channel clock and bi        | t clock for the audio               | 0*                     | Internally generated            |  |

| 12         | LNI30      | serial       | data                                                   | input from the SDI0 t       | erminal.                            | 1                      | Externally generated            |  |

| 11         | BCIS0      | Select       | ts the                                                 | bit count for the au        | dio serial data input               | 0*                     | 16bit                           |  |

| ' '        | ВСІЗО      | from         | the S                                                  | DI0 terminal.               |                                     | 1                      | 32bit                           |  |

| 10         | LROS2      | Select       | ts the                                                 | channel clock and bi        | t clock for the audio               | 0*                     | Internally generated            |  |

| '0         | LNO32      | serial       | data                                                   | output from the SDO2        | 2 terminal.                         | 1                      | Externally input                |  |

| 9          | LROS1      |              |                                                        | channel clock and bi        |                                     | 0*                     | Internally generated            |  |

| "          | LNO31      | serial       | data                                                   | output from the SDO         | 1 terminal.                         | 1                      | Externally input                |  |

| 8          | BCOS1      | Select       | ts the                                                 | bit clock for the aud       | lio serial data output              | 0*                     | 16bit (TG32)                    |  |

| l °        | ВСОЗТ      | from         | from the SDO1 terminal.                                |                             |                                     |                        | 32bit (TG64)                    |  |

| 7          | LROS0      | Select       | Selects the channel clock and bit clock for the audio  |                             |                                     |                        | Internally generated            |  |

| Ľ          | LKO30      | serial       | data                                                   | output from the SDO         | 1                                   | Externally input       |                                 |  |

| 6          | BCOS0      |              | Selects the bit clock for the audio serial data output |                             |                                     |                        | 16bit (TG32)                    |  |

| Ľ          | всозо      |              |                                                        | DO0 terminal.               | 1                                   | 32bit (TG64)           |                                 |  |

|            |            |              |                                                        |                             | erminal bit clock outpu             | ut for the LR terminal |                                 |  |

|            |            |              |                                                        | erminal output.             | 6000111111                          |                        |                                 |  |

|            |            | BCKS         | TOS                                                    | LR terminal output          | BCK terminal output                 |                        | SDO2 bit clock                  |  |

| 5          | BCKS       | 0*           | 0*                                                     | Internally generated (TGLR) | Internally generated (TG32)         | Sele                   | ction made at LROS2             |  |

| 4          | TOS        | 0            | 1                                                      | ELRO2 input signal          | EBCO2 input signal                  | Sele                   | ction made at LROS2             |  |

|            |            | 1            | 0                                                      | Internally generated (TGLR) | 1/2 frequency of EBCO2 input signal | I                      | frequency of EBCO2<br>at signal |  |

|            |            |              |                                                        | FIROS taranta de            | 1/2 frequency of                    |                        | frequency of EBCO2              |  |

|            |            | 1   1        | 1   1   ELRO2 input signal   FBCO2 input signal        |                             |                                     | I                      | ut signal                       |  |

| 3          | SYNCS      |              |                                                        | ect either an internall     |                                     | 0*                     | Internally generated (TGLR)     |  |

|            |            | exter        | nally i                                                | nput (SYNC terminal)        | mode.                               | 1                      | External input                  |  |

|            | 6) (1) (2) |              |                                                        | 0/010 1 1 1 1               |                                     | 0*                     | Rise                            |  |

| 2          | SYNCP      | Select       | Selects the SYNC signal polarity.                      |                             |                                     |                        | Fall                            |  |

|            | CVALCE     | Reset        | s the                                                  | coefficient pointer (CP     | ) at each SYNC                      | 0*                     | Run                             |  |

| 1          | SYNCR1     | NCR1 signal. |                                                        |                             |                                     |                        | Prohibit                        |  |

| 「 <u>、</u> | CVNICDO    | Reset        | s the                                                  | offset address pointer      | (OFP) at each SYNC                  | 0*                     | Run                             |  |

| 0          | SYNCR0     | signa        | l.                                                     | ·                           |                                     | 1                      | Prohibit                        |  |

|            |            | sigila       | 1.                                                     |                             |                                     | <u> </u>               | Frombit                         |  |

# (2-2) Control register 1 (CNT-R1)

(\* = Default value)

| ВІТ | SYMBOL                                 | FUNCTION                                                                                              |    |                               |

|-----|----------------------------------------|-------------------------------------------------------------------------------------------------------|----|-------------------------------|

| 7   | PCMON                                  | The program counter values are output at terminals                                                    | 0* | Prohibit                      |

| ′   | PCIVION                                | IO15~IO7. (The external RAM is placed on standby.)                                                    | 1  | Run                           |

| 6   | A CMD                                  | When the CRAM or OFRAM pointer values coincide                                                        | 0* | Prohibit                      |

| ľ   | ACMP                                   | with the rewrite counter address, data in both RAM are rewritten.                                     | 1  | Run                           |

| 5   | CKSL                                   | Sologie the VI escillation (input) sleek fraguency                                                    | 0* | XI = 640fs                    |

| '   | CK3L                                   | Selects the XI oscillation (input) clock frequency.                                                   |    | XI = 512fs                    |

| 4   | PS                                     | Selects the externally attached RAM type (PSRAM or DRAM).                                             | 0* | PSRAM                         |

| 4   | 4   13                                 |                                                                                                       | 1  | DRAM                          |

| 3   |                                        | Not assigned.                                                                                         |    | _                             |

| L   | _                                      | Not assigned.                                                                                         |    | _                             |

| 2   | DSL                                    | Selects the internal DBUS data that will access the externally attached RAM source (high priority 16/ | 0* | High priority<br>16bit (DB16) |

|     |                                        | 32bit).                                                                                               | 1  | 32bit (DB32)                  |

| 1   | IOS                                    | S Selects an 8bit or a 16bit access mode for the external RAM source.                                 | 0* | 16bit / access (IO16)         |

| ı   | 103                                    |                                                                                                       | 1  | 8bit/access (IO8)             |

| 0   | XSEP                                   | Partitions the externally attached RAM into delay and                                                 | 0* | Prohibit                      |

| ľ   | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | data table domains.                                                                                   | 1  | Run                           |

# (2-3) Control register 0 (CNT-R0)

(\* = Default value)

|     |          |                                                                                                                                                          |    | (" - Belault value) |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------|

| ВІТ | SYMBOL   | FUNCTION                                                                                                                                                 |    |                     |

| 7   | PRGALL   | The active switch is turned to the "on" position when the program is loaded. During this active state, instructions are placed in an NOP condition. When |    | On                  |

| ,   |          | the switch is turned from the "on" position to the "off" position, the XINT and RMRF ignore flags are reset.                                             | 1  | Off                 |

| 6   | C DDKDO  | Once the program break address (BRKA) has been established, setting BRKRQ to "1" will activate the break.                                                | 0* | Off                 |

| 0   | BRKRQ    |                                                                                                                                                          | 1  | On                  |

| 5   | INMT     | Sets the SDI0 and SDI1 terminal input to "0" mute.                                                                                                       | 0  | Mute off            |

| ٥   | IINIVII  |                                                                                                                                                          | 1* | Mute on             |

| 4   | OUTMT2   | Sets the SDO2 terminal output to "0" mute                                                                                                                | 0  | Mute off            |

|     | OUTIVITZ | Sets the SDO2 terminal output to "0" mute.                                                                                                               | 1* | Mute on             |

| 3   | OUTMT1   | Sets the SDO1 terminal output to "0" mute.                                                                                                               | 0  | Mute off            |

|     | COTIVITI | sets the 3001 terminal output to 0 mute.                                                                                                                 | 1* | Mute on             |

| 2   | OUTMT0   | Sets the SDOO terminal output to "O" mute                                                                                                                | 0  | Mute off            |

| Ľ   | OUTMIU   | MT0 Sets the SDO0 terminal output to "0" mute.                                                                                                           | 1* | Mute on             |

(\* = Default value)

| ВІТ | SYMBOL | FUNCTION                                                                                                 |    |             |

|-----|--------|----------------------------------------------------------------------------------------------------------|----|-------------|

| 1   | XCLR   | Trigger bit that clears the externally attached RAM delay domain to "0". Once the clearing operation has |    | Trigger off |

|     |        | been initiated, the bit is reset to a trigger "off" position (XCLR = 0).                                 | 1  | Trigger on  |

| 0   | VCTDV  | Places the externally attached RAM on standby.                                                           | 0  | Standby off |

| ľ   | VOIDI  |                                                                                                          | 1* | Standby on  |

<sup>\*</sup> The CNT-RO data is latched via a SYNC signal.

# (2-4) The I/F dedicated register

| SYMBOL | FUNCTION                                                                                                                                                                                                                                                                                                                                           |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STAD   | The STAD is a presentable up-counter used in setting the starting address for writing data and programs in the PRAM, CRAM, and OFRAM. (9bit)                                                                                                                                                                                                       |

| TXW    | The TXW register is responsible for setting the rewrite data count (max. 32 words) for the CRAM and OFRAM when ACMP is in the 1 (CNT-R1) mode. (5bit)                                                                                                                                                                                              |

| RMR    | The RMR register temporarily retains data to be written to the PRAM, CRAM, OFRAM until it receives subsequent data (32bit). The RMR also acts as the source register for the data bus.                                                                                                                                                             |

| XINT   | The XINT register sets up the IFF2~0, which act as conditional field flags. (3bit)                                                                                                                                                                                                                                                                 |

| XRMD   | <ul> <li>The XRMD register sets the following:</li> <li>(1) In the XSEP mode, sets the domains for the delay and table data partitions in the externally attached RAM.</li> <li>(2) Sets the access frequency for the externally attached RAM.</li> <li>(3) Sets set to use or not use the × 4bit 1M DRAM (5bit) to active or inactive.</li> </ul> |

<sup>\*</sup> The RMR and XINT data are latched via a SYNC signal.

#### (3) The Data Transmission Process.

When the  $\overline{\text{CS}}$  signal is set to "L" or activated, data is transmitted in command word (1 byte) and data word (1 to 4 byte) sets. Somewhat similar to the program, coefficient, and offset address processes, the command word becomes unnecessary when data bits using the same command word are transmitted successively; only the data word needs to be transmitted. In these situations, the IFCD signal is set to "L" prior to the  $\overline{\text{CS}}$  signal.

(4) The Internal RAM (PRAM, CRAM, OFRAM) Data Transmission Process

The STAD-R, which sets the starting address for the writing process, adds a +1 increment to the address after writing each data unit. The internal RAM units that can utilize the buffer RAM (32 words × 16bits) are the CRAM and OFRAM. For them to do so, the coefficient and offset addresses must be rewritten in successively increasing increments of +1. For example, the coefficient address of the secondary IIR in the equalizer must be successively arranged from 5 single-precision units to 10 multiple-precision units. The buffer RAM is used when altering the individual characteristics of the filter. These coefficients can be rewritten within a single sampling period.

Ex. Rewriting the offset data coefficient in the buffer RAM

When the targeted rewrite coefficient addresses are set at 30, 31, 32, 33, and 34, the following takes place.

When the targeted coefficient RAM addresses are arranged in succession, as shown in the example below, the buffer RAM can be rewritten.

```

..., 29, <u>30</u>, <u>31</u>, <u>32</u>, <u>33</u>, <u>34</u>, 35, 36, ... (or)

..., 29, <u>30</u>, 36, <u>31</u>, <u>32</u>, 28, 29, <u>33</u>, <u>34</u>, 35, 36, ...

```

When the targeted coefficient RAM addresses are randomly arranged, as shown in the example below, the buffer RAM cannot be rewritten.

```

..., 29, <u>30</u>, <u>31</u>, <u>34</u>, <u>33</u>, <u>32</u>, 35, 36, ...

```

- Setting up the data in the PRAM (Program RAM)

- ① The write starting address is set in the STAD-R (command: 0CH).

- ② An "OAH" command is transmitted and the PRAM write-to flag is triggered.

- 3 Only the 32bit program code data is continued and the necessary steps are transmitted.

- Setting up the data in the CRAM (coefficient RAM) and OFRAM (offset RAM)

- (a) The buffer RAM is not in use (The ACMP of the CNT-R1 is set to "0").

- ① The write starting address is set in the STAD-R (command: 0CH).

- ② An "09H" or "08H" command is transmitted and the CRAM or OFRAM writeto flag is triggered.

- ③ Only the 16bit coefficient or offset data is continued and the necessary steps are transmitted.

- (b) The buffer RAM is in use (the ACMP of the CNT-R1 is set to "1").

- ① The write starting address is set in the STAD-R (command: OCH).

- ② The data coefficient-1 stored in the buffer RAM is set to the TXW-R.

- ③ An "09H" or "08H" command is transmitted and the CRAM or OFRAM write-to flag is triggered.

- Only the 16bit coefficient or offset data is continued and the necessary steps are transmitted.

Fig.10 A sample of the microcomputer timing control

| REGISTER | REGISTER COMMAND WORD (HEX) | BIT LENGTH USED | TRANSMITTED BIT<br>LENGTH |

|----------|-----------------------------|-----------------|---------------------------|

| CNT-R2   | 40                          | 15              | 7                         |

| CNT-R1   | 30                          | 8               | l I                       |

| CNT-R0   | Q0                          | 8               | ı                         |

| STAD-R   | 00                          | 6               | 7                         |

| TXW-R    | 80                          | 5               | l                         |

| PRAM     | ¥0                          | 32              | 7                         |

| CRAM     | 60                          | 16              | 7                         |

| OFRAM    | 80                          | 16              | 2                         |

| RM-R     | 20                          | 32              | 7                         |

| XINT-R   | 90                          | 3               | ı                         |

| XRMD-R   | 90                          | 5               | ı                         |

| BRKA-R   | 04                          | 6               | 2                         |

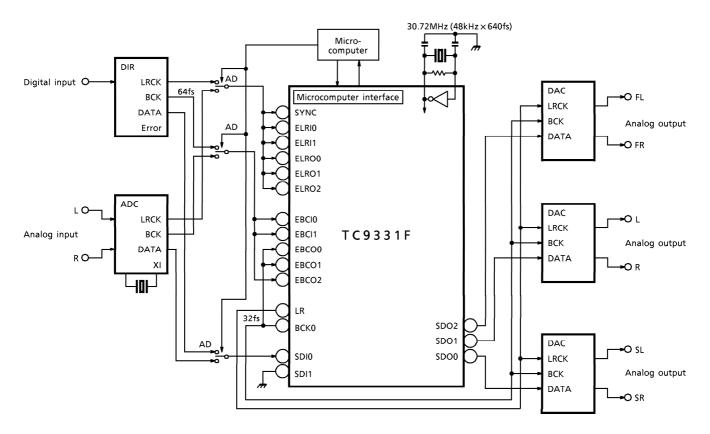

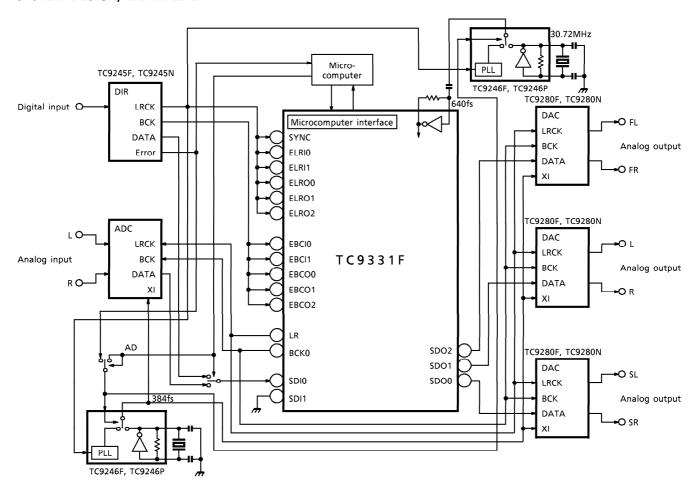

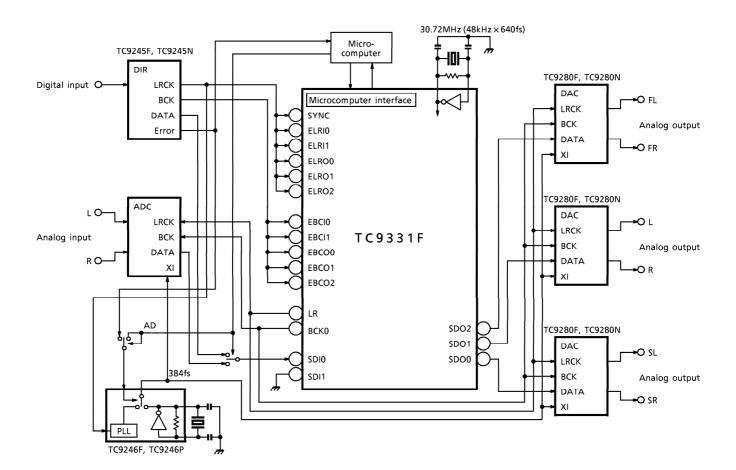

# SYSTEM DESIGN, EXAMPLE 1.

#### SYSTEM DESIGN, EXAMPLE 2.

#### SYSTEM DESIGN, EXAMPLE 3.

# MAXIMUM RATINGS (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL           | RATING                    | UNIT |

|-----------------------|------------------|---------------------------|------|

| Power Source Voltage  | $V_{DD}$         | -0.3~6.0                  | V    |

| Input Voltage         | V <sub>IN</sub>  | -0.3~V <sub>DD</sub> +0.3 | V    |

| Allowable Loss        | PD               | 1250                      | mW   |

| Operating Temperature | T <sub>opr</sub> | - 35~85                   | °C   |

| Storage Temperature   | T <sub>stg</sub> | <b>-</b> 55∼150           | °C   |

# **ELECTRICAL CHARACTERISTICS (1)** (Unless otherwise specified, $Ta = 25^{\circ}C$ , $V_{DD} = 5V$ )

| CHARACTERISTIC                                   | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION                             | MIN. | TYP. | MAX. | UNIT |

|--------------------------------------------------|------------------|----------------------|--------------------------------------------|------|------|------|------|

| Operating Source Voltage                         | $V_{DD}$         | _                    | Ta = −35~85°C                              | 4.5  | 5.0  | 5.5  | V    |

| Operating Source Current<br>(No-Load, During The | Inn              |                      | $f_{opr} = 30.72MHz (48kHz \times 640fs)$  | _    | 60   | 100  | mA   |

| Crystal Oscillation Period)                      | IDD              |                      | $f_{opr} = 24.576MHz (48kHz \times 512fs)$ | _    | 50   | 90   | mA   |

| Operating Frequency<br>Range                     | f <sub>opr</sub> | _                    | _                                          | 4.0  | _    | 32.0 | MHz  |

# CLOCK TERMINALS (XI, XO)

| Unput Voltage F | "H" Level | V <sub>IH1</sub> | _ | XI terminal              |             | 3.5 |   |     |         |

|-----------------|-----------|------------------|---|--------------------------|-------------|-----|---|-----|---------|

| input voitage   | "L" Level | V <sub>IL1</sub> | _ | Ai terminai              |             |     |   | 1.5 | \ \ \ \ |

| Output Valtage  | "H" Level | V <sub>OH1</sub> | _ | $I_{OH} = -2.5$ mA       | XO terminal | 2.4 |   |     | \ \     |

| Output Voltage  | "L" Level | V <sub>OL1</sub> | _ | $I_{OL} = 2.5 \text{mA}$ | AO terrimai | _   | _ | 0.4 |         |

#### INPUT TERMINAL

| Input Voltage | "H" Level | V <sub>IH2</sub> | _ | (*1)                 |         | 3.5   | _   |     |         |

|---------------|-----------|------------------|---|----------------------|---------|-------|-----|-----|---------|

| Imput voitage | "L" Level | V <sub>IL2</sub> | _ | (^1)                 |         |       | 1.5 | V   |         |

| Threshold     | "H" Level | V <sub>P</sub>   | _ | (*2)                 |         |       | 2.7 | _   | ]       |

| Voltage       | "L" Level | ٧N               | _ | (^2)                 |         | 1.6   | _   |     |         |

| Input Leakage | "H" Level | l <sub>IH1</sub> | _ | $V_{IN} = V_{DD}$    | (*1, 2) |       |     | 1.0 |         |

| Current       | "L" Level | l <sub>IL1</sub> | _ | V <sub>IN</sub> = 0V | ("1, 2) | - 1.0 |     | _   | $\mu$ A |

<sup>(\*1)</sup>ELRI0~1, ELRO0~2, EBCI0~1, EBCO0~2, SDI0~1, TESO~2

# **ELECTRICAL CHARACTERISTICS (2)** (Unless otherwise specified, $Ta = 25^{\circ}C$ , $V_{DD} = 5V$ )

| CHARACTERISTIC SYMBOL CIR-<br>CUIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT |

|------------------------------------|----------------|------|------|------|------|

|------------------------------------|----------------|------|------|------|------|

#### **OUTPUT TERMINAL**

| IOutnut Voltage I | "H" Level | V <sub>OH2</sub> | _ | I <sub>OH</sub> = - 1mA | (*3) | 2.4 | _ |     |          |

|-------------------|-----------|------------------|---|-------------------------|------|-----|---|-----|----------|

|                   | "L" Level | V <sub>OL2</sub> | _ | I <sub>OL</sub> = 1mA   | (*3) | _   | _ | 0.4 | ] ,, [   |

| Output Voltage    | "H" Level | V <sub>OH3</sub> | _ | $I_{OH} = -2mA$         | (*4) | 2.4 | _ |     | <b>'</b> |

|                   | "L" Level | V <sub>OL3</sub> | _ | I <sub>OL</sub> = 2mA   | (^4) | _   | _ | 0.4 |          |

(\*3)LR, WCK, BCK0~1, SDO0~2

(\*4)A0~A15, RC0~RC3

<sup>(\*2)</sup> SYNC, RST, HALT, PEN, CS, IFCD, IFCK, IFDT (Schmidt input terminal)

| CHARACTERISTIC SYMBOL CIR-<br>CUIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT | 1 |

|------------------------------------|----------------|------|------|------|------|---|

|------------------------------------|----------------|------|------|------|------|---|

#### THREE STATE INPUT/OUTPUT TERMINAL (IO0 - IO15)

| Input Voltage   | "H" Level | V <sub>IH4</sub> | _ |                      | 3.5   | _ | _   |         |

|-----------------|-----------|------------------|---|----------------------|-------|---|-----|---------|

| input voltage   | "L" Level | V <sub>IL4</sub> | _ |                      |       |   | 1.5 | V       |

| Output Voltage  | "H" Level | V <sub>OH4</sub> | _ | $I_{OH} = -2mA$      | 2.4   |   |     | "       |

|                 | "L" Level | V <sub>OL4</sub> | _ | $I_{OL} = 2mA$       | _     | _ | 0.4 | 1       |

| Output "Off"    | "H" Level | <sup>I</sup> OFH | _ | $V_{OH} = V_{DD}$    | _     |   | 5.0 |         |

| Leakage Current | "L" Level | lOFL             |   | V <sub>OL</sub> = 0V | - 5.0 | _ |     | $\mu$ A |

# OPEN DRAIN OUTPUT TERMINAL (OVF, ACK, DCHK)

| "L" Level Output Voltage | V <sub>OL5</sub> | _ | I <sub>OL</sub> = 1mA | _ | _ | 0.4 | V       |

|--------------------------|------------------|---|-----------------------|---|---|-----|---------|

| Output Open Leakage      | los              |   | Vo. 1 - Vo. 2         |   |   | 5.0 |         |

| Current                  | <sup>I</sup> OF  |   | VOH = VDD             | _ | _ | 3.0 | $\mu$ A |

# PULL-UP TERMINAL

| Pull-Up Resistor | RUP | _ | (*5) | 100 | kΩ |

|------------------|-----|---|------|-----|----|

(\*5)100~1015, RST, HALT, OVF, PEN, ACK, DCHK

# AC CHARACTERISTICS (1) (Unless otherwise specified, Ta = 25°C, V<sub>DD</sub> = 5V)

| CHARACTERISTIC | SYMBOL CUIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT |

|----------------|-------------|----------------|------|------|------|------|

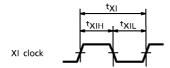

# EXTERNAL CLOCK INPUT TERMINAL (XI)

| XI Clock Periodicity          | tXI              | _ | _ | 32 | 36 | 250 |    |

|-------------------------------|------------------|---|---|----|----|-----|----|

| XI Clock "H" Period<br>Length | <sup>t</sup> XIH | _ | _ | 16 | 18 | 125 | ns |

| XI Clock "L" Period<br>Length | <sup>t</sup> XIL | _ |   | 16 | 18 | 125 |    |

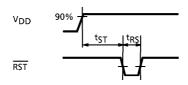

# Reset Terminal (RST)

| Stand-By Time      | tsT             |   | _ | 500 | _ | 1 | $\mu$ s |

|--------------------|-----------------|---|---|-----|---|---|---------|

| Reset Pulse Length | t <sub>RS</sub> | _ |   | 10  |   | _ | μs      |

| CHARACTERISTIC                 | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION        | MIN.     | TYP. | MAX. | UNIT |

|--------------------------------|------------------|----------------------|-----------------------|----------|------|------|------|

| AUDIO SERIAL INTERFACE         |                  |                      |                       |          |      |      |      |

| XI-BCK1 Transfer Time (1)      | t <sub>CK1</sub> |                      | C <sub>L</sub> = 10pF | _        | 25   | _    |      |

| XI-BCK1 Transfer Time (2)      | t <sub>CK2</sub> | _                    | C <sub>L</sub> = 10pF | _        | 25   | _    |      |

| XI-BCK0 Transfer Time (1)      | t <sub>CK3</sub> | _                    | C <sub>L</sub> = 10pF | -        | 25   | _    |      |

| XI-BCK0 Transfer Time (2)      | t <sub>CK4</sub> | _                    | C <sub>L</sub> = 10pF | -        | 25   | _    |      |

| BCK0-WCK Transfer Time (1)     | t <sub>CK5</sub> | _                    | C <sub>L</sub> = 10pF | -        | 5    | _    |      |

| BCK0-WCK Transfer Time (2)     | t <sub>CK6</sub> | _                    | C <sub>L</sub> = 10pF | <b>—</b> | 5    | _    |      |

| BCK0-LR Transfer Time (1)      | t <sub>CK7</sub> | _                    | C <sub>L</sub> = 10pF | _        | 5    | _    |      |

| BCK0-LR Transfer Time (2)      | t <sub>CK8</sub> | _                    | C <sub>L</sub> = 10pF | I -      | 5    | _    |      |

| LR-SDO Lag Time (1)            | tsO1             | _                    | C <sub>L</sub> = 10pF | 0        | _    | 40   | ns   |

| BCKO-SDO Transfer Time         | tsO2             | _                    | C <sub>L</sub> = 10pF | 0        | _    | 40   |      |

| ELRI-EBCI Lag Time             | t <sub>EB1</sub> | _                    | C <sub>L</sub> = 10pF | - 55     | _    | 55   |      |

| ELRO-EBCO Lag Time             | t <sub>EB2</sub> | _                    | C <sub>L</sub> = 10pF | - 55     | _    | 55   |      |

| EBCI/O Clock Period            | t <sub>EBC</sub> | _                    | C <sub>L</sub> = 10pF | <b>—</b> | 350  | _    |      |

| EBCI/O Clock "H" Period Length | t <sub>EBH</sub> | _                    | C <sub>L</sub> = 10pF | 100      | _    | _    |      |

| EBCI/O Clock "L" Period Length | t <sub>EBL</sub> | _                    | C <sub>L</sub> = 10pF | 100      | _    | _    |      |

| SDI Data Set Up Time           | tsis             | _                    | C <sub>L</sub> = 10pF | 100      | _    | _    |      |

| SDI Data Holding Time          | t <sub>SIH</sub> |                      | C <sub>L</sub> = 10pF | 100      | _    | _    |      |

# **AC CHARACTERISTICS (2)** (Unless otherwise specified, Ta = 25°C, $V_{DD} = 5V$ )

| CHARACTERISTIC | SYMBOL C | R- TEST CONDITION | MIN. | TYP. | MAX. | UNIT |  |

|----------------|----------|-------------------|------|------|------|------|--|

|----------------|----------|-------------------|------|------|------|------|--|

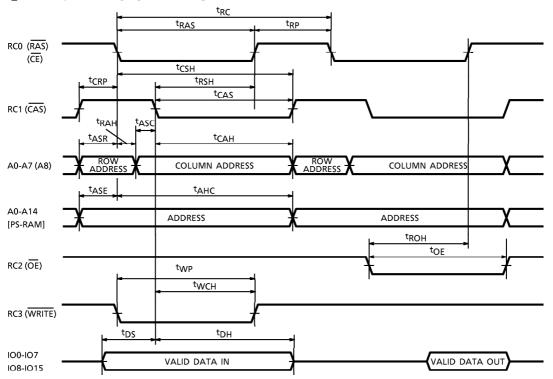

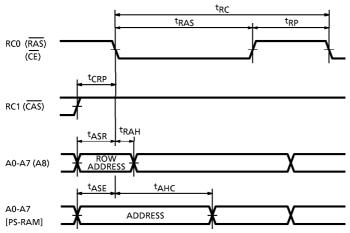

# EXTERNAL RAM INTERFACE

| Read/Write Cycling Time  | t <sub>RC</sub>  | _ | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 170 | 330 | _ |    |

|--------------------------|------------------|---|----------------------------------------|-----|-----|---|----|

| RAS Pulse Length         | tRAS             | _ | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 100 | 200 |   |    |

| RAS Precharging Time     | t <sub>RP</sub>  | _ | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 60  | 130 | 1 | ns |

| CAS-RAS Precharging Time | <sup>t</sup> CRP | _ | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 5   | 60  | _ |    |

| CAS Holding Time         | <sup>t</sup> CSH | _ | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 100 | 260 |   |    |

| CHARACTERISTIC                 | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION                         | MIN. | TYP. | MAX. | UNIT |

|--------------------------------|------------------|----------------------|----------------------------------------|------|------|------|------|

| RAS Holding Time               | t <sub>RSH</sub> |                      | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 40   | 130  | _    |      |

| CAS Pulse Length               | t <sub>CAS</sub> | _                    | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 40   | 190  | _    |      |

| Low Address Setup Time         | t <sub>ASR</sub> | _                    | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 0    | 60   | _    |      |

| Low Address Holding Time       | tRAH             | _                    | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 10   | 30   | _    |      |

| Column Address Setup Time      | tASC             | _                    | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 0    | 30   | _    |      |

| Column Address Holding Time    | <sup>t</sup> CAH | _                    | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 15   | 190  | _    |      |

| CE Address Setup Time          | tASE             | _                    | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 0    | 60   | _    | ns   |

| CE Holding Time                | <sup>t</sup> AHC | _                    | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 30   | 260  | _    | 115  |

| RAS Holding Time (OE Standard) | <sup>t</sup> ROH | _                    | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 20   | 130  | _    |      |

| OE Pulse Length                | tOE              | _                    | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | _    | 190  | _    |      |

| Write Command Pulse Length     | t <sub>WP</sub>  | _                    | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 15   | 190  | _    |      |

| Write Command Holding Time     | <sup>t</sup> WCH |                      | XI = 30.72MHz<br>$C_L = 20pF$          | 15   | 130  | _    |      |

| Data Input Setup Time          | t <sub>DS</sub>  |                      | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 0    | 30   | _    |      |

| Data Input Holding Time        | tDH              |                      | XI = 30.72MHz<br>C <sub>L</sub> = 20pF | 15   | 290  | _    |      |

# AC CHARACTERISTICS (3) (Unless otherwise specified, Ta = 25°C, $V_{DD} = 5V$ )

| CHARACTERISTIC | SYMBOL CIR-<br>CUIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT |

|----------------|---------------------|----------------|------|------|------|------|

|----------------|---------------------|----------------|------|------|------|------|

#### MICROCOMPUTER INTERFACE

| - INTEROCOUNT OTER INTERNACE   |                 |   |                                  |     |     |     |         |

|--------------------------------|-----------------|---|----------------------------------|-----|-----|-----|---------|

| CS-IFCK Delay Time             | t <sub>1</sub>  | _ | C <sub>L</sub> = 10pF            | 2.0 | 2.5 | _   |         |

| I/F Clock Periodity            | t <sub>2</sub>  | _ | C <sub>L</sub> = 10pF            | 4.0 | 5.0 | _   |         |

| I/F Clock "L" Period Length    | t <sub>3</sub>  | _ | C <sub>L</sub> = 10pF            | 2.0 | 2.5 | _   |         |

| I/F Clock "H" Period Length    | t <sub>4</sub>  | _ | C <sub>L</sub> = 10pF            | 2.0 | 2.5 | _   |         |

| CHK Data Transfer Time         | t <sub>5</sub>  | _ | C <sub>L</sub> = 10pF            | _   | 0.5 | _   |         |

| IFDT Data Setup Time           | t <sub>6</sub>  | _ | C <sub>L</sub> = 10pF            | 0.5 | 1.0 | _   | ]       |

| ACK Transfer Time (1)          | t <sub>7</sub>  | _ | C <sub>L</sub> = 10pF            | _   | _   | 0.5 | ]       |

| ACK Transfer Time (2)          | tg              | _ | C <sub>L</sub> = 10pF            | _   | _   | 0.5 | $\mu$ s |

| IFCD-IFCK Delay Time           | t9              | _ | C <sub>L</sub> = 10pF            | 0.0 | _   | _   |         |

| IFCK-IFCD Delay Time           | t <sub>10</sub> | _ | C <sub>L</sub> = 10pF            | 0.5 | 1.0 | _   | ]       |

| IFCD-CS Delay Time             | t <sub>11</sub> | _ | C <sub>L</sub> = 10pF            | 2.0 | 2.5 | _   | ]       |

| IFDT-"H" Level Transition Time | t <sub>12</sub> | _ | C <sub>L</sub> = 10pF            | 0.0 | _   | _   |         |

| CS-DCHK Transfer Time          | t <sub>13</sub> | _ | C <sub>L</sub> = 10pF            | _   | _   | 0.5 |         |

| CS-ACK Transfer Time           | t <sub>14</sub> | _ | C <sub>L</sub> = 10pF            | _   | _   | 0.5 | ]       |

| IFCD-CS Transfer Time          | t <sub>15</sub> | _ | C <sub>L</sub> = 10pF            | 2.0 | 2.5 | _   |         |

|                                | t <sub>r1</sub> | _ | LR, WCK, BCK0<br>BCK1, SDO0~SDO2 | _   | _   | 20  |         |

|                                | t <sub>f1</sub> | _ | C <sub>L</sub> = 10pF            | _   | _   | 10  |         |

| Rising Time (tr)               | t <sub>r2</sub> | _ | A0~A15, IO0~IO15<br>RC0~RC3      | _   | _   | 20  | nc      |

| Falling Time (tf)              | t <sub>f2</sub> | _ | $C_L = 20pF$                     | _   | _   | 10  | ns      |

|                                | t <sub>r3</sub> | _ | OVF, ACK, DCHK                   | _   | _   | 5   |         |

|                                | t <sub>f3</sub> | _ | C <sub>L</sub> = 10pF            |     |     | 60  |         |

CAUTION! An AC timing measurement of (VIH, VIL) (VOH, VOL) has been used as a standard.

# **AC Special Measurement Points**

# (1) External clock input terminal

# (2) Reset terminal

# (3) Audio serial interface

# (4) External RAM interface

# ① READ/WRITE CYCLE TIMING

# ② RAS (CE) REFRESH CYCLE TIMING ONLY

2001-06-19

32

# **PACKAGE DIMENSIONS**

QFP80-P-1420-0.80A Unit: mm

Weight: 1.57g (Typ.)

#### RESTRICTIONS ON PRODUCT USE

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- ◆ The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.