SBOS147A - SEPTEMBER 1986 - JULY 2005

# **Fast-Settling FET-Input INSTRUMENTATION AMPLIFIER**

#### **FEATURES**

● LOW BIAS CURRENT: 50pA max ● FAST SETTLING: 4µs to 0.01%

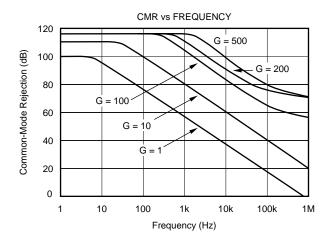

● HIGH CMR: 106dB min; 90dB at 10kHz ● INTERNAL GAINS: 1, 10, 100, 200, 500 VERY LOW GAIN DRIFT: 10 to 50ppm/°C

● LOW OFFSET DRIFT: 2μV/°C

LOW COST

PINOUT SIMILAR TO AD524 AND AD624

## **APPLICATIONS**

- MULTIPLEXED INPUT DATA **ACQUISITION SYSTEM**

- FAST DIFFERENTIAL PULSE AMPLIFIER

- HIGH SPEED GAIN BLOCK

- AMPLIFICATION OF HIGH IMPEDANCE **SOURCES**

#### DESCRIPTION

The INA110 is a versatile monolithic FET-input instrumentation amplifier. Its current-feedback circuit topology and laser trimmed input stage provide excellent dynamic performance and accuracy. The INA110 settles in 4µs to 0.01%, making it ideal for high speed or multiplexed-input data acquisition systems.

Internal gain-set resistors are provided for gains of 1, 10, 100, 200, and 500V/V. Inputs are protected for differential and common-mode voltages up to ±V<sub>CC</sub>. Its very high input impedance and low input bias current make the INA110 ideal for applications requiring input filters or input protection circuitry.

The INA110 is available in 16-pin plastic and ceramic DIPs, and in the SOL-16 surface-mount package. Military, industrial and commercial temperature range grades are available.

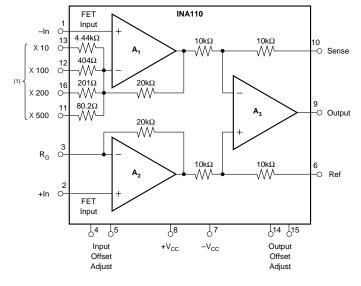

NOTE: (1) Connect to R<sub>G</sub> for desired gain.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### **ABSOLUTE MAXIMUM RATINGS(1)**

| Supply VoltageInput Voltage Range       |                      |

|-----------------------------------------|----------------------|

| Operating Temperature Range: G          |                      |

| P, U                                    | 25°C to +85°C        |

| Storage Temperature Range: G            | 65°C to +150°C       |

| P, U                                    | 40°C to +85°C        |

| Lead Temperature (soldering, 10s): G, P | +300°C               |

| (soldering, 3s): U                      | +260°C               |

| Output Short Circuit Duration           | Continuous to Common |

NOTE: (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability.

#### **PACKAGE/ORDERING INFORMATION**

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

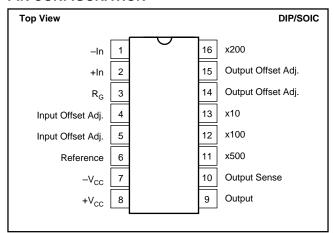

#### **PIN CONFIGURATION**

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# **ELECTRICAL CHARACTERISTICS**

At +25°C,  $\pm V_{CC}$  = 15VDC, and R  $_{L}$  = 2k $\!\Omega,$  unless otherwise specified.

|                                       |                                           |          | INA110AC               | 3               | IN          | A110BG,                | SG      | l IN | IA110KP, | KU       |                           |

|---------------------------------------|-------------------------------------------|----------|------------------------|-----------------|-------------|------------------------|---------|------|----------|----------|---------------------------|

| PARAMETER                             | CONDITIONS                                | MIN      | TYP                    | MAX             | MIN TYP MAX |                        |         | MIN  | TYP      | MAX      | UNITS                     |

| GAIN                                  |                                           |          |                        |                 |             |                        |         |      |          |          |                           |

| Range of Gain                         |                                           | 1        |                        | 800             | *           |                        | *       | *    |          | *        | V/V                       |

| Gain Equation <sup>(1)</sup>          |                                           |          | *                      |                 | G = 1 -     | + [40k/(R <sub>G</sub> | + 50Ω)] |      | *        |          | V/V                       |

| Gain Error, DC: G = 1                 |                                           |          | 0.002                  | 0.04            |             | *                      | 0.02    |      | *        | *        | %                         |

| G = 10                                |                                           |          | 0.01                   | 0.1             |             | 0.005                  | 0.05    |      | *        | *        | %                         |

| G = 100                               |                                           |          | 0.02                   | 0.2             |             | 0.01                   | 0.1     |      | *        | *        | %                         |

| G = 200                               |                                           |          | 0.04                   | 0.4             |             | 0.02                   | 0.2     |      | *        | *        | %                         |

| G = 500                               |                                           |          | 0.1                    | 1               |             | 0.05                   | 0.5     |      | *        | *        | %                         |

| Gain Temp. Coefficient: G = 1         |                                           |          | ±3                     | ±20             |             | *                      | ±10     |      | *        |          | ppm/°                     |

| G = 10                                |                                           |          | ±4                     | ±20             |             | ±2                     | ±10     |      | *        |          | ppm/°                     |

| G = 100                               |                                           |          | ±6                     | ±40             |             | ±3                     | ±20     |      | *        |          | ppm/°                     |

| G = 200                               |                                           |          | ±10                    | ±60             |             | ±5                     | ±30     |      | *        |          | ppm/°                     |

| G = 500                               |                                           |          | ±25                    | ±100            |             | ±10                    | ±50     |      | *        |          | ppm/°                     |

| Nonlinearity, DC: G = 1               |                                           |          | ±0.001                 | ±0.01           |             | ±0.0005                | ±0.005  |      | *        | *        | % of F                    |

| G = 10                                |                                           |          | ±0.002                 | ±0.01           |             | ±0.001                 | ±0.005  |      | *        | *        | % of F                    |

| G = 100                               |                                           |          | ±0.004                 | ±0.02           |             | ±0.002                 | ±0.01   |      | *        | *        | % of F                    |

| G = 200                               |                                           |          | ±0.004                 | ±0.02           |             | ±0.002                 | ±0.01   |      | *        | *        | % of F                    |

| G = 500                               |                                           |          | ±0.00                  | ±0.02           |             | ±0.005                 | ±0.02   |      | *        | *        | % of F                    |

|                                       |                                           |          | ±0.01                  | ±0.04           |             | ±0.003                 | ±0.02   |      |          |          | 76 UI I                   |

| OUTPUT                                |                                           |          |                        |                 |             |                        |         | 1    |          |          | l                         |

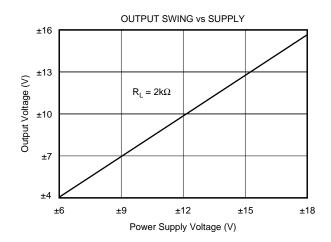

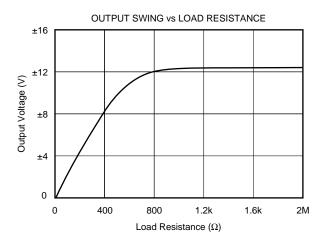

| Voltage, $R_L = 2k\Omega$             | Over Temperature                          | ±10      | ±12.7                  |                 | *           | *                      |         | *    | *        |          | V                         |

| Current                               | Over Temperature                          | ±5       | ±25                    | 1               | *           | *                      |         | *    | *        |          | mA                        |

| Short-Circuit Current                 |                                           |          | ±25                    |                 |             | *                      |         |      | *        |          | mA                        |

| Capacitive Load                       | Stability                                 |          | 5000                   |                 |             | *                      |         |      | *        |          | pF                        |

| INPUT OFFSET VOLTAGE <sup>(2)</sup>   |                                           |          |                        |                 |             |                        |         |      |          |          |                           |

| Initial Offset: G, P                  |                                           |          | ±(100 +                | ±(500 +         |             | ±(50 +                 | ±(250 + |      | *        | *        | μV                        |

| Illitial Oliset. G, P                 |                                           |          |                        | ±(500 + 5000/G) |             | ,                      | 3000/G) |      |          |          | μν                        |

|                                       |                                           |          | 1000/G)                | 5000/G)         |             | 600/G)                 | 3000/G) |      |          | . (4000  |                           |

| U                                     |                                           |          |                        |                 |             |                        |         |      | ±(200 +  | ±(1000 + | μV                        |

| <b>-</b>                              |                                           |          |                        |                 |             |                        |         |      | 2000/G)  | 5000/G)  | 1 1/100                   |

| vs Temperature                        |                                           |          | ±(2 +                  | ±(5 +           |             | ±(1 +                  | ±(2 +   |      |          |          | μV/°C                     |

|                                       |                                           |          | 20/G)                  | 100/G)          |             | 10/G)                  | 50/G)   |      |          |          |                           |

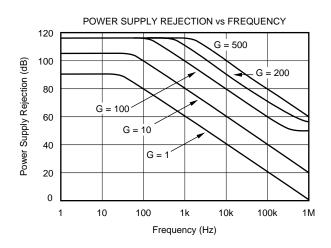

| vs Supply                             | $V_{CC} = \pm 6V \text{ to } \pm 18V$     |          | ±(4 +                  | ±(30 +          |             | ±(2 +                  | ±(10 +  |      | *        | *        | μV/V                      |

|                                       |                                           |          | 60/G)                  | 300/G)          |             | 30/G)                  | 180/G)  |      |          |          |                           |

| BIAS CURRENT                          |                                           |          |                        |                 |             |                        |         |      |          |          |                           |

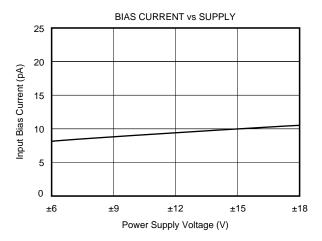

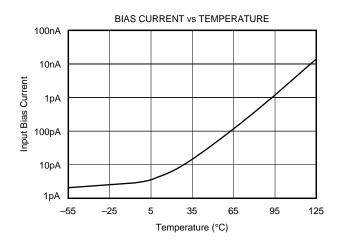

| Initial Bias Current                  | Each Input                                |          | 20                     | 100             |             | 10                     | 50      |      | *        | *        | pА                        |

| Initial Offset Current                |                                           |          | 2                      | 50              |             | 1                      | 25      |      | *        | *        | pA                        |

| Impedance: Differential               |                                           |          | 5x10 <sup>12</sup>   6 |                 |             | *                      |         |      | *        |          | Ω    pl                   |

| Common-Mode                           |                                           |          | 2x10 <sup>12</sup>   1 |                 |             | *                      |         |      | *        |          | Ω    pf                   |

|                                       |                                           | <u> </u> | 2/1.0                  |                 |             |                        |         |      |          |          |                           |

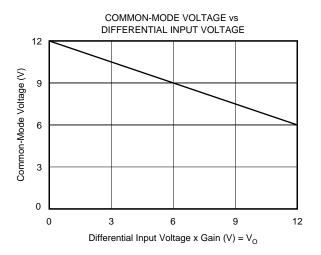

| VOLTAGE RANGE                         | V <sub>IN</sub> Diff. = 0V <sup>(3)</sup> |          |                        |                 |             |                        |         |      |          |          |                           |

| Range, Linear Response                |                                           | ±10      | ±12                    |                 |             |                        |         | *    | *        |          | V                         |

| CMR with $1k\Omega$ Source Imbalance: |                                           |          |                        |                 |             |                        |         |      |          |          |                           |

| G = 1                                 | DC                                        | 70       | 90                     |                 | 80          | 100                    |         | *    | *        |          | dB                        |

| G = 10                                | DC                                        | 87       | 104                    |                 | 96          | 112                    |         | *    | *        |          | dB                        |

| G = 100                               | DC                                        | 100      | 110                    |                 | 106         | 116                    |         | *    | *        |          | dB                        |

| G = 200                               | DC                                        | 100      | 110                    |                 | 106         | 116                    |         | *    | *        |          | dB                        |

| G = 500                               | DC                                        | 100      | 110                    |                 | 106         | 116                    |         | *    | *        |          | dB                        |

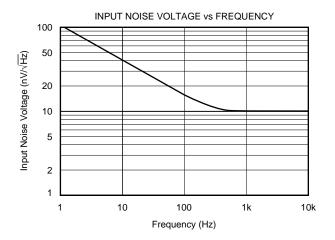

| INPUT NOISE(4)                        |                                           |          |                        |                 |             |                        |         |      |          |          |                           |

| Voltage, f <sub>O</sub> = 10kHz       |                                           | 1        | 10                     | 1               |             | *                      |         | 1    | *        |          | nV/√H                     |

| • •                                   |                                           | 1        | 10                     | 1               |             | *                      |         | 1    | *        |          |                           |

| $f_B = 0.1Hz$ to $10Hz$               |                                           |          | 1.8                    |                 |             | *                      |         |      | *        |          | μV <sub>PP</sub><br>fA/√H |

| Current, f <sub>O</sub> = 10kHz       |                                           | ļ        | 1.0                    |                 |             |                        |         |      |          |          | IAV VIII.                 |

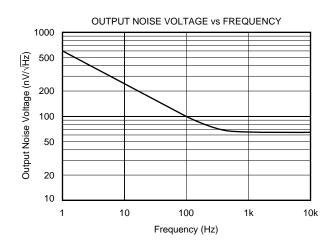

| OUTPUT NOISE(4)                       |                                           |          |                        |                 |             |                        |         |      |          |          | l .                       |

| Voltage, f <sub>O</sub> = 10kHz       |                                           |          | 65                     |                 |             | *                      |         |      | *        |          | nV/√H                     |

| $f_B = 0.1Hz$ to $10Hz$               |                                           |          | 8                      |                 |             | *                      |         | 1    | *        |          | $\mu V_{PP}$              |

| DYNAMIC RESPONSE                      |                                           |          |                        |                 |             |                        |         |      |          |          |                           |

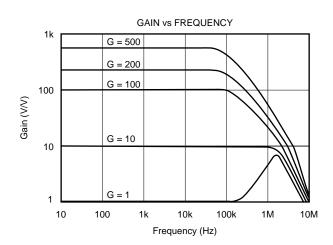

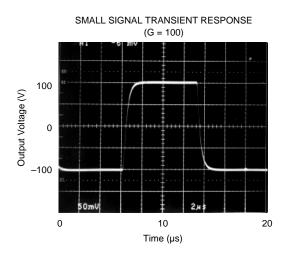

|                                       | −3dB                                      |          | 2.5                    |                 |             | *                      |         |      | *        |          | MHz                       |

| Small Signal: $G = 1$<br>G = 10       | -SUB                                      |          | 1                      |                 |             | *                      |         |      | *        |          | l .                       |

|                                       |                                           |          | 2.5                    |                 |             | *                      |         |      | *        |          | MHz                       |

| G = 100                               |                                           | 1        | 470                    | 1               |             |                        |         | 1    |          |          | kHz                       |

| G = 200                               |                                           | 1        | 240                    | 1               |             |                        |         | 1    |          |          | kHz                       |

| G = 500                               | ,,                                        | 1        | 100                    | 1               |             | *                      |         | 1    | *        |          | kHz                       |

| Full Power                            | $V_{OUT} = \pm 10V$ ,                     |          |                        | 1               |             | l .                    |         | 1    |          |          | 1 .                       |

|                                       | G = 2 to 100                              | 190      | 270                    | 1               | *           | *                      |         | 1    | *        | *        | kHz                       |

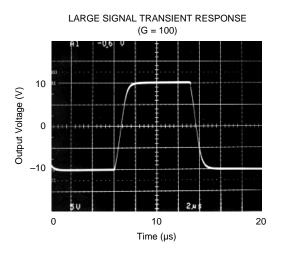

| Slew Rate                             | G = 2 to 100                              | 12       | 17                     | 1               | *           | *                      |         | 1    | *        | *        | V/μs                      |

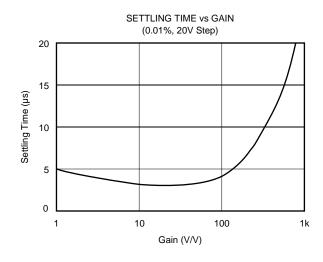

| Settling Time:                        |                                           | 1        |                        | 1               |             |                        |         | 1    |          |          | l                         |

| 0.1%, G = 1                           | V <sub>O</sub> = 20V Step                 | 1        | 4                      | 1               |             | *                      |         | 1    | *        |          | μs                        |

| G = 10                                |                                           | 1        | 2                      | 1               |             | *                      |         | 1    | *        |          | μs                        |

| G = 100                               |                                           | 1        | 3                      | 1               |             | *                      |         | 1    | *        |          | μs                        |

| 0 000                                 | 1                                         | 1        | 5                      | 1               | l           | *                      | 1       | I    | *        | 1        | μs                        |

| G = 200                               |                                           | 1        | _                      |                 |             |                        |         |      |          |          |                           |

# **ELECTRICAL CHARACTERISTICS (Cont)**

At +25°C,  $\pm V_{CC}$  15VDC, and R<sub>L</sub> = 2K $\Omega$ , unless otherwise specified.

|                         |                           |     | INA110AC | }    | IN  | A110BG, | SG   | IN. | A110KP, | KU  |       |

|-------------------------|---------------------------|-----|----------|------|-----|---------|------|-----|---------|-----|-------|

| PARAMETER               | CONDITIONS                | MIN | TYP      | MAX  | MIN | TYP     | MAX  | MIN | TYP     | MAX | UNITS |

| DYNAMIC RESPONSE (CONT) |                           |     |          |      |     |         |      |     |         |     |       |

| Settling Time:          |                           |     |          |      |     |         |      |     |         |     |       |

| 0.01%,G = 1             | V <sub>O</sub> = 20V Step |     | 5        | 12.5 |     | *       | *    |     | *       |     | μs    |

| G = 10                  |                           |     | 3        | 7.5  |     | *       | *    |     | *       |     | μs    |

| G = 100                 |                           |     | 4        | 7.5  |     | *       | *    |     | *       |     | μs    |

| G = 200                 |                           |     | 7        | 12.5 |     | *       | *    |     | *       |     | μs    |

| G = 500                 |                           |     | 16       | 25   |     | *       | *    |     | *       |     | μs    |

| Recovery <sup>(5)</sup> | 50% Overdrive             |     | 1        |      |     | *       |      |     | *       |     | μs    |

| POWER SUPPLY            |                           |     |          |      |     |         |      |     |         |     |       |

| Rated Voltage           |                           |     | ±15      |      |     | *       |      |     | *       |     | V     |

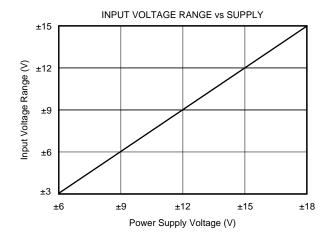

| Voltage Range           |                           | ±6  |          | ±18  | *   |         | *    | *   |         | *   | V     |

| Quiescent Current       | $V_O = 0V$                |     | ±3       | ±4.5 |     | *       | *    |     | *       | *   | mA    |

| TEMPERATURE RANGE       |                           |     |          |      |     |         |      |     |         |     |       |

| Specification: P, U     |                           | -25 |          | +85  | *   |         | *    | 0   |         | +70 | °C    |

| G                       |                           |     |          |      | -55 |         | +125 |     |         |     | °C    |

| Operation               |                           | -55 |          | +125 | *   |         | *    | -25 |         | +85 | °C    |

| Storage                 |                           | -65 |          | +150 | *   |         | *    | -40 |         | +85 | °C    |

| $	heta_{\sf JA}$        |                           |     | 100      |      |     | *       |      |     | *       |     | °C/W  |

<sup>\*</sup> Same as INA110AG

NOTES: (1) Gains other than 1, 10, 100, 200, and 500 can be set by adding an external resistor,  $R_G$ , between pin 3 and pins 11, 12 and 16. Gain accuracy is a function of  $R_G$  and the internal resistors which have a  $\pm 20\%$  tolerance with 20ppm/°C drift. (2) Adjustable to zero. (3) For differential input voltage other than zero, see Typical Characteristics. (4)  $V_{NOISE\,RTI} = \sqrt{V_N^2}_{INPUT} + (V_{NOUTPUT}/Gain)^2$ . (5) Time required for output to return from saturation to linear operation following the removal of an input overdrive voltage.

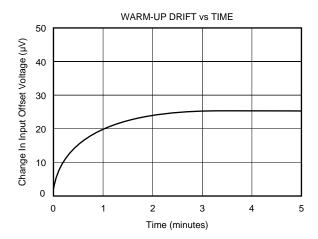

## TYPICAL CHARACTERISTICS

At  $T_A$  = +25°C and  $\pm V_{CC}$  = 15VDC, unless otherwise noted.

# **TYPICAL CHARACTERISTICS (Cont)**

At  $T_A$  = +25°C and  $\pm V_{CC}$  = 15VDC, unless otherwise noted.

# **TYPICAL CHARACTERISTICS (Cont)**

At  $T_A$  = +25°C and  $\pm V_{CC}$  = 15VDC, unless otherwise noted.

# DISCUSSION OF PERFORMANCE

A simplified diagram of the INA110 is shown on the first page. The design consists of the classical three operational amplifier configuration using current-feedback type op amps with precision FET buffers on the input. The result is an instrumentation amplifier with premium performance not normally found in integrated circuits.

The input section ( $A_1$  and  $A_2$ ) incorporates high performance, low bias current, and low drift amplifier circuitry. The amplifiers are connected in the noninverting configuration to provide high input impedance ( $10^{12}\Omega$ ). Laser-trimming is used to achieve low offset voltage. Input cascoding assures low bias current and high CMR. Thin-film resistors on the integrated circuit provide excellent gain accuracy and temperature stability.

The output section  $(A_3)$  is connected in a unity-gain difference amplifier configuration. Precision matching of the four  $10k\Omega$  resistors, especially over temperature and time, assures high common-mode rejection.

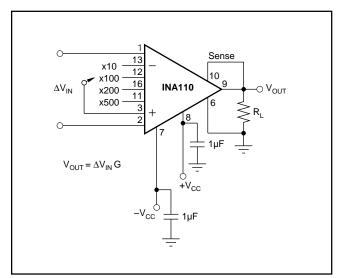

# BASIC POWER SUPPLY AND SIGNAL CONNECTIONS

Figure 1 shows the proper connections for power supply and signal. Supplies should be decoupled with 1µF tantalum capacitors as close to the amplifier as possible. To avoid gain and CMR errors introduced by the external circuit, connect grounds as indicated, being sure to minimize ground resistance. Resistance in series with the reference (pin 6) will degrade CMR. To maintain stability, avoid capacitance from the output to the gain set, offset adjust, and input pins.

FIGURE 1. Basic Circuit Connection.

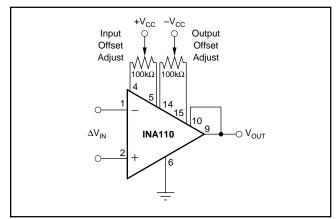

#### **OFFSET ADJUSTMENT**

Figure 2 shows the offset adjustment circuit for the INA110. Both the offset of the input stage and output stage can be adjusted separately. Notice that the offset referred to the

INA110's input (RTI) is the offset of the input stage plus the offset of the output stage divided by the gain of the input stage. This allows specification of offset independent of gain.

FIGURE 2. Offset Adjustment Circuit.

For systems using computer autozeroing techniques, neither offset nor offset drift are of concern. In many other applications, the factory-trimmed offset gives excellent results. When greater accuracy is desired, one adjustment is usually sufficient. In high gains (>100) adjust only the input offset, and in low gains the output offset. For higher precision in all gains, both can be adjusted by first selecting high gain and adjusting input offset and then low gain and adjusting output offset. The offset adjustment will, however, add to the drift by approximately  $0.33\mu V/^{\circ}C$  per  $100\mu V$  of input offset voltage that is adjusted. Therefore, care should be taken when considering use of adjustment.

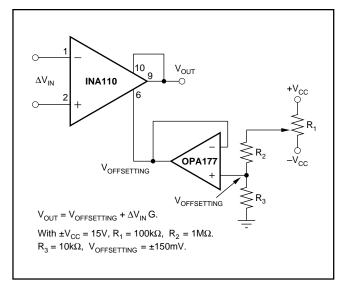

Output offsetting can be accomplished as shown in Figure 3 by applying a voltage to the reference (pin 6) through a buffer. This limits the resistance in series with pin 6 to minimize CMR error. Be certain to keep this resistance low. Note that the offset error can be adjusted at this reference point with no appreciable degradation in offset drift.

FIGURE 3. Output Offsetting.

#### **GAIN SELECTION**

Gain selection is accomplished by connecting the appropriate pins together on the INA110. Table I shows possible gains from the internal resistors. Keep the connections as short as possible to maintain accuracy.

| GAIN          | CONNECT PIN 3<br>TO PIN | GAIN<br>ACCURACY (%) | GAIN<br>DRIFT (ppm/°C) |

|---------------|-------------------------|----------------------|------------------------|

| The following | ng gains have assured   | d accuracy:          |                        |

| 1             | none                    | 0.02                 | 10                     |

| 10            | 13                      | 0.05                 | 10                     |

| 100           | 12                      | 0.1                  | 20                     |

| 200           | 16                      | 0.2                  | 30                     |

| 500           | 11                      | 0.5                  | 50                     |

| The following | ng gains have typical   | accuracy as shown:   |                        |

| 300           | 12, 16                  | 0.25                 | 10                     |

| 600           | 11, 12                  | 0.25                 | 40                     |

| 700           | 11, 16                  | 2                    | 40                     |

| 800           | 11, 12, 16              | 2                    | 80                     |

TABLE I. Internal Gain Connections.

Gains other than 1, 10, 100, 200, and 500 can be set by adding an external resistor,  $R_G$ , between pin 3 and pins 12, 16, and 11. Gain accuracy is a function of  $R_G$  and the internal resistors which have a  $\pm 20\%$  tolerance with  $20\text{ppm}/^{\circ}\text{C}$  drift. The equation for choosing  $R_G$  is shown below.

$$R_{G} = \frac{40k\Omega}{G-1} - 50\Omega$$

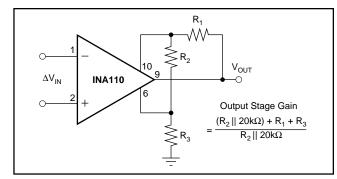

Gain can also be changed in the output stage by adding resistance to the feedback loop shown in Figure 4. This is useful for increasing the total gain or reducing the input stage gain to prevent saturation of input amplifiers.

The output gain can be changed as shown in Table II. Matching of  $R_1$  and  $R_3$  is required to maintain high CMR.  $R_2$  sets the gain with no effect on CMR.

| OUTPUT STAGE GAIN | R <sub>1</sub> AND R <sub>3</sub> | R <sub>2</sub> |  |  |

|-------------------|-----------------------------------|----------------|--|--|

| 2                 | 1.2kΩ                             | 2.74kΩ         |  |  |

| 5                 | 1kΩ                               | 511Ω           |  |  |

| 10                | 1.5kΩ                             | $340\Omega$    |  |  |

TABLE II. Output Stage Gain Control.

#### **COMMON-MODE INPUT RANGE**

It is important not to exceed the input amplifiers' dynamic range (see Typical Characteristics). The differential input signal and its associated common-mode voltage should not cause the output of  $A_1$  and  $A_2$  (input amplifiers) to exceed approximately  $\pm 10 V$  with  $\pm 15 V$  supplies or nonlinear operation will result. Such large common-mode voltages, when the INA110 is in high gain, can cause saturation of the input stage even though the differential input is very small. This can be avoided by reducing the input stage gain and increasing the output stage gain with an H pad attenuator (see Figure 4).

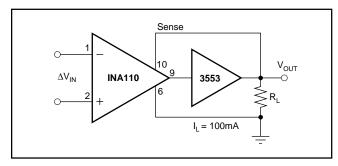

#### **OUTPUT SENSE**

An output sense has been provided to allow greater accuracy in connecting the load. By attaching this feedback point to the load at the load site, IR drops due to load currents that are eliminated since they are inside the feedback loop. Proper connection is shown in Figure 1. When more current is to be supplied, a power booster can be placed within the feedback loop as shown in Figure 5. Buffer errors are minimized by the loop gain of the output amplifier.

FIGURE 4. Gain Adjustment of Output Stage Using H Pad Attenuator.

FIGURE 5. Current Boosting the Output.

# LOW BIAS CURRENT OF FET INPUT ELIMINATES DC ERRORS

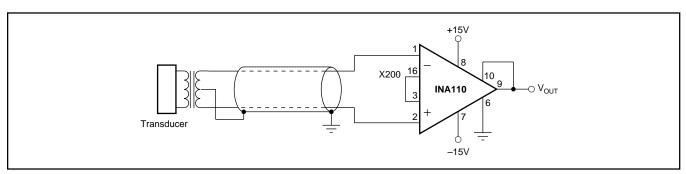

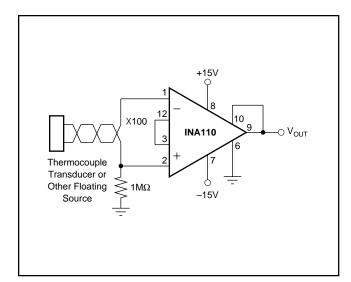

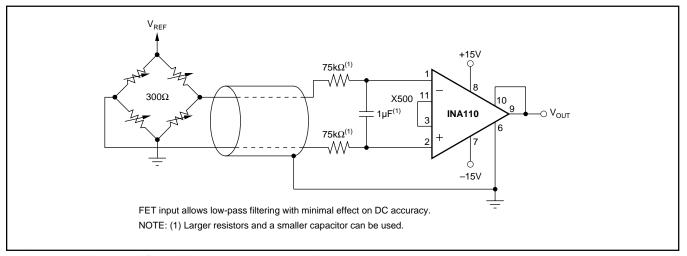

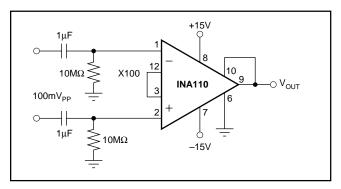

Because the INA110 has FET inputs, bias currents drawn through input source resistors have a negligible effect on DC accuracy. The picoamp levels produce no more than microvolts through megohm sources. Thus, input filtering and input series protection are readily achievable.

A return path for the input bias currents must always be provided to prevent charging of stray capacitance. Otherwise, the output can wander and saturate. A  $1M\Omega$  to  $10M\Omega$  resistor from the input to common will return floating sources such as transformers, thermocouples, and AC-coupled inputs (see Applications section).

#### **DYNAMIC PERFORMANCE**

The INA110 is a fast-settling FET input instrumentation amplifier. Therefore, careful attention to minimize stray capacitance is necessary to achieve specified performance. High source resistance will interact with input capacitance to reduce the overall bandwidth. Also, to maintain stability, avoid capacitance from the output to the gain set, offset adjust, and input pins.

Applications with balanced-source impedance will provide the best performance. In some applications, mismatched source impedances may be required. If the impedance in the negative input exceeds that in the positive input, stray capacitance from the output will create a net negative feedback and improve the circuit stability. If the impedance in the positive input is greater, the feedback due to stray capacitance will be positive and instability may result. The degree of positive feedback depends upon source impedance imbalance, operating gain, and board layout. The addition of a small bypass capacitor of 5pF to 50pF directly between the inputs of the IA will generally eliminate any positive feedback. CMR errors due to the input impedance mismatch will also be reduced by the capacitor.

The INA110 is designed for fast settling with easy gain selection. It has especially excellent settling in high gain. It can also be used in fast-settling unity-gain applications. As with all such amplifiers, the INA110 does exhibit significant gain peaking when set to a gain of 1. It is, however, unconditionally stable. The gain peaking can be cancelled by band-limiting the negative input to 400kHz with a simple external RC circuit for applications requiring flat response. CMR is not affected by the addition of the 400kHz RC in a gain of 1.

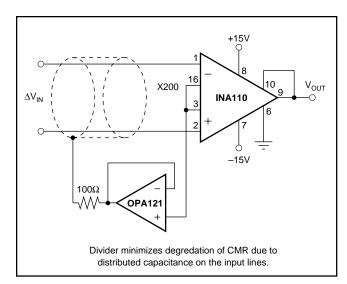

Another distinct advantage of the INA110 is the high frequency CMR response. High frequency noise and sharp common-mode transients will be rejected. To preserve AC CMR, be sure to minimize stray capacitance on the input lines. Matching the RCs in the two inputs will help to maintain high AC CMR.

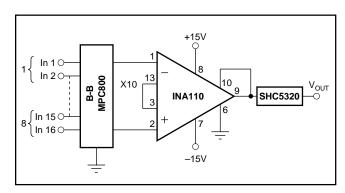

### **APPLICATIONS**

In addition to general purpose uses, the INA110 is designed to accurately handle two important and demanding applications: (1) inputs with high source impedances such as capacitance/crystal/photodetector sensors and low-pass filters and series-input protection devices, and (2) rapid-scanning data acquisition systems requiring fast settling time. Because the user has access to the output sense, current sources can also be constructed using a minimum of external components. Figures 6 through 19 show application circuits.

FIGURE 6. Transformer-Coupled Amplifier.

FIGURE 7. Floating Source Instrumentation Amplifier.

FIGURE 8. Instrumentation Amplifier with Shield Driver.

FIGURE 9. Bridge Amplifier with 1Hz Low-Pass Input Filter.

FIGURE 10. AC-Coupled Differential Amplifier for Frequencies Greater Than 0.016Hz.

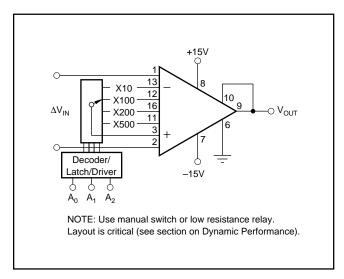

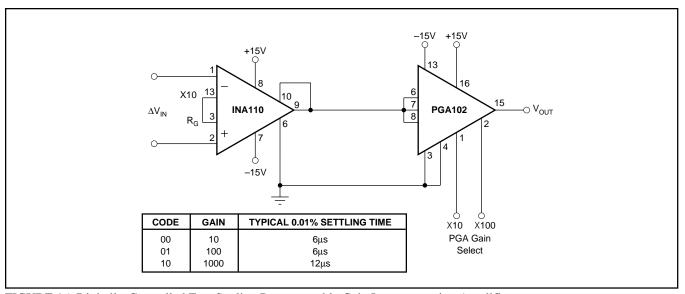

FIGURE 12. Rapid-Scanning-Rate Data Acquisition Channel with 5µs Settling to 0.01%.

FIGURE 11. Programmable-Gain Instrumentation Amplifier (Precision Noninverting or Inverting Buffer with Gain).

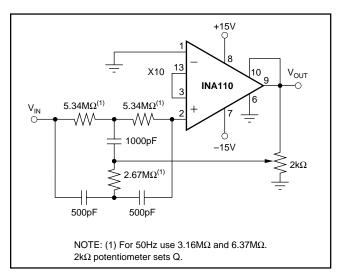

FIGURE 13. 60Hz Input Notch Filter.

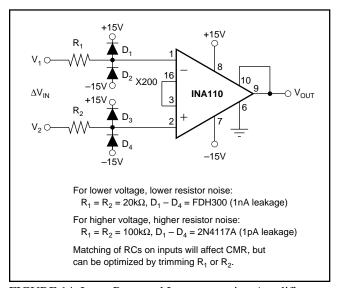

FIGURE 14. Input-Protected Instrumentation Amplifier.

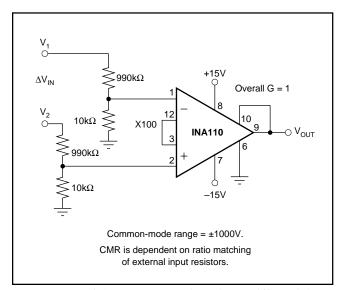

FIGURE 15. High Common-Mode Voltage Differential Amplifier.

FIGURE 16. Digitally-Controlled Fast-Settling Programmable Gain Instrumentation Amplifier.

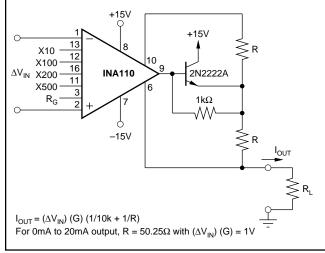

FIGURE 17. Differential Input FET Buffered Current Source.

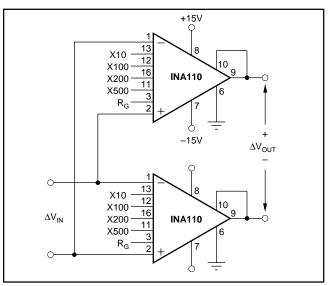

FIGURE 18. Differential Input/Differential Output Amplifier.

www.ti.com 23-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins    | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-------------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       | (1)    | (2)           |                   |                       | (5)  | (4)                           | (5)                        |              | (0)              |

| INA110KP              | Active | Production    | PDIP (N)   16     | 25   TUBE             | Yes  | NIPDAU                        | N/A for Pkg Type           | -55 to 125   | INA110KP         |

| INA110KP.A            | Active | Production    | PDIP (N)   16     | 25   TUBE             | Yes  | NIPDAU                        | N/A for Pkg Type           | -55 to 125   | INA110KP         |

| INA110KU              | Active | Production    | SOIC (DW)   16    | 40   TUBE             | Yes  | NIPDAU-DCC                    | Level-3-260C-168 HR        | -            | INA110KU         |

| INA110KU.A            | Active | Production    | SOIC (DW)   16    | 40   TUBE             | Yes  | NIPDAU-DCC                    | Level-3-260C-168 HR        | -55 to 125   | INA110KU         |

| INA110SG              | Active | Production    | CDIP SB (JD)   16 | 24   TUBE             | Yes  | AU                            | N/A for Pkg Type           | -            | INA110SG         |

| INA110SG.A            | Active | Production    | CDIP SB (JD)   16 | 24   TUBE             | Yes  | AU                            | N/A for Pkg Type           | -55 to 125   | INA110SG         |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 23-May-2025

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

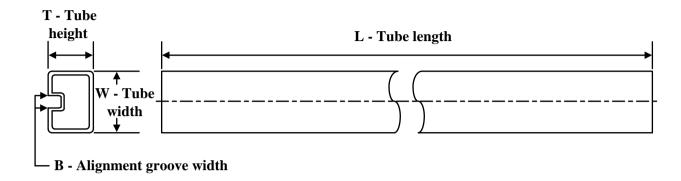

#### **TUBE**

\*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| INA110KP   | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| INA110KP.A | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| INA110KU   | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| INA110KU.A | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| INA110SG   | JD           | CDIP SB      | 16   | 24  | 506.98 | 15.24  | 12290  | NA     |

| INA110SG.A | JD           | CDIP SB      | 16   | 24  | 506.98 | 15.24  | 12290  | NA     |

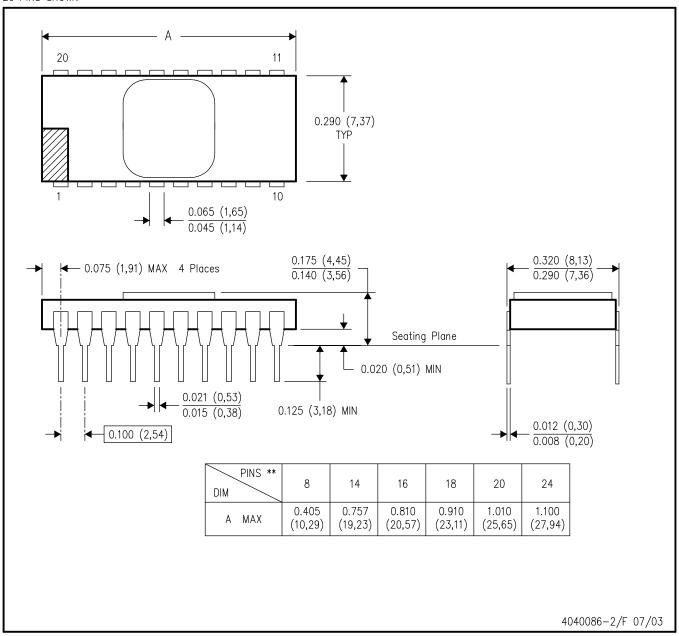

# JD (R-CDIP-T\*\*)

## CERAMIC SIDE-BRAZE DUAL-IN-LINE PACKAGE

20 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package is hermetically sealed with a metal lid.

- D. The terminals are gold plated.

- E. Falls within MIL STD 1835 CDIP2 T8, T14, T16, T18, T20 and T24 respectively.

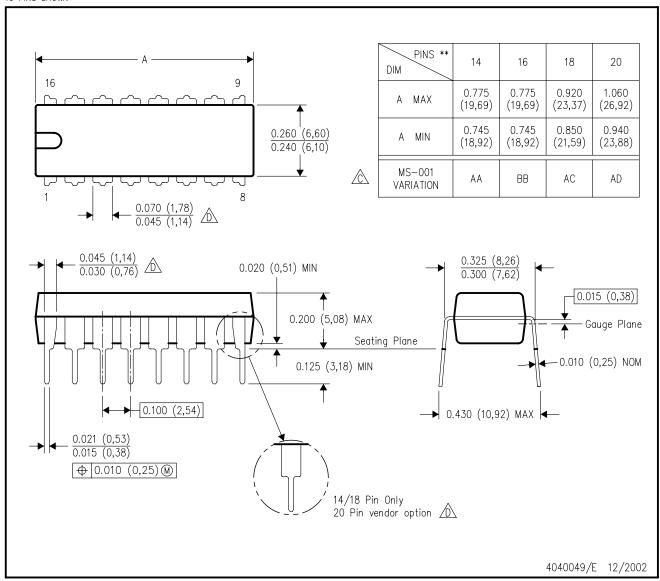

## N (R-PDIP-T\*\*)

## PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- The 20 pin end lead shoulder width is a vendor option, either half or full width.

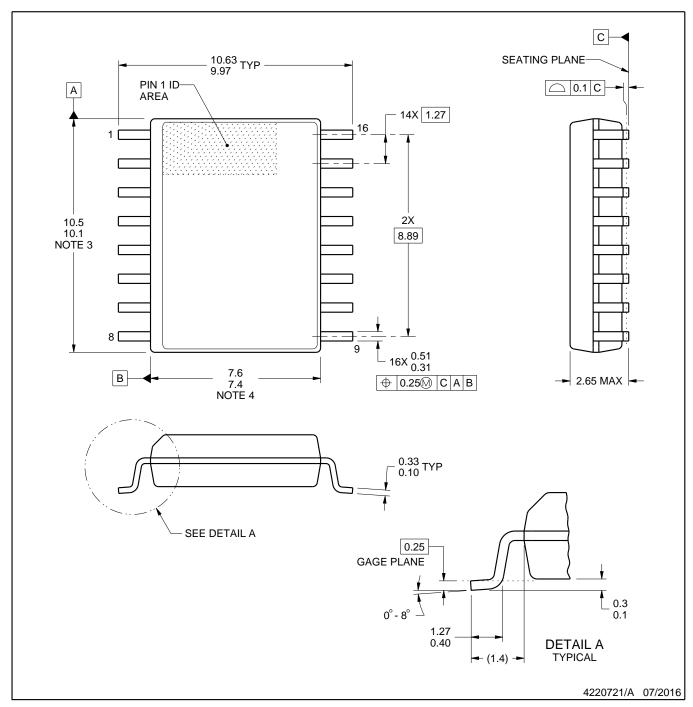

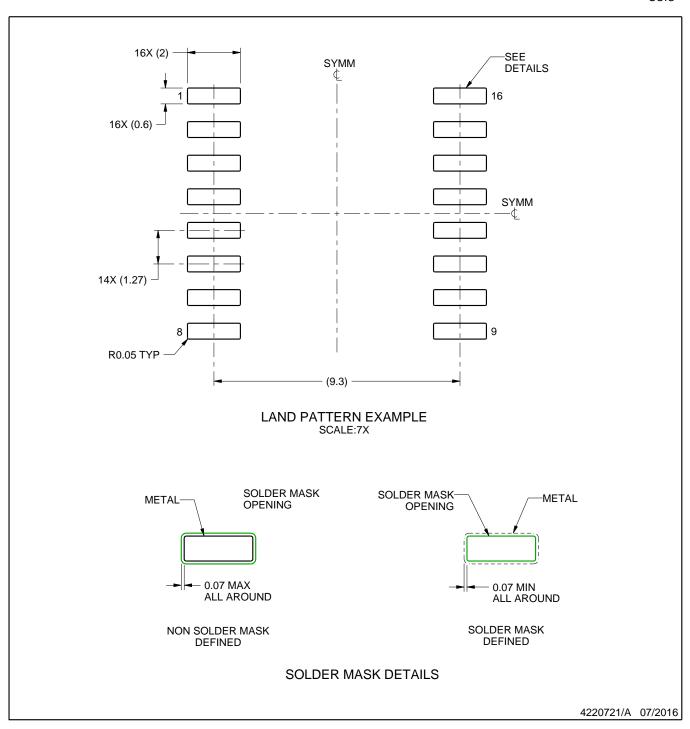

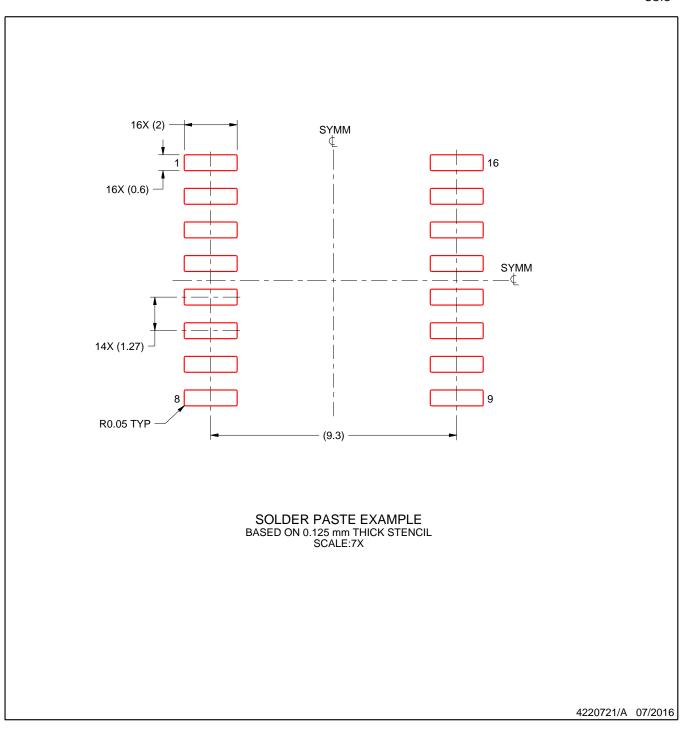

7.5 x 10.3, 1.27 mm pitch

SMALL OUTLINE INTEGRATED CIRCUIT

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

SOIC

#### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing

- per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm, per side.

- 5. Reference JEDEC registration MS-013.

SOIC

#### NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SOIC

#### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated