## SCANSTA101

### Low Voltage IEEE 1149.1 STA Master

#### General Description

The SCANSTA101 is designed to function as a test master for a IEEE 1149.1 test system. The minimal requirements to create a tester are a microcomputer (uP, RAM/ROM, clock, etc.), SCANEASE r2.0 software, and a STA101.

The SCANSTA101 is an enhanced version of, and replacement for, the SCANPSC100. The additional features of the STA101 further allow it to offload some of the processor overhead while remaining flexible. The device architecture supports IEEE 1149.1, BIST, and IEEE 1532. The flexibility will allow it to adapt to any changes that may occur in 1532 and support yet unknown variants.

The SCANSTA101 is useful in improving vector throughput when applying serial vectors to system test circuitry and reduces the software overhead that is associated with applying serial patterns with a parallel processor. The SCANSTA101 features a generic Parallel Processor Interface (PPI) which operates by serializing data from the parallel bus for shifting through the chain of 1149.1 compliant components (i.e., scan chain). Writes can be controlled either by wait states or the DTACK line. Handshaking is accomplished with either polling or interrupts.

#### Features

- Compatible with IEEE Std. 1149.1 (JTAG) Test Access Port and Boundary Scan Architecture

- Supported by National's SCAN Ease (Embedded Application Software Enabler) Software Rev 2.0

- Available as a Silicon Device and Intellectual Property (IP) model for embedding into VLSI devices

- Uses generic, asynchronous processor interface; compatible with a wide range of processors and PCLK frequencies

- 16-bit Data Interface (IP scalable to 32-bit)

- 2Kx32 bit dual-port memory addressing for access by the PPI or the 1149.1 master

- Load-on-the-fly (LotF) and Preload operating modes supported

- On-Board Sequencer allows multi-vector operations such as those required to load data into an FPGA

- On-Board Comparers support TDI validation against preloaded expected data

- 32-bit Linear Feedback Shift Register (LFSR) at the Test Data In (TDI) port

- State, Shift, and BIST macros allow predetermined TMS sequences to be utilized

- Operates at 3.3v supply voltages w/ 5V tolerant I/O

- Outputs support Power-Down TRI-STATE mode.

#### SCANSTA101 Architecture

\* Note: IP data bus width can be configured for 16 or 32 bit applications. Silicon data bus width is fixed at 16 bits.

10121502

FIGURE 1.

**SCANSTA101 Architecture** (Continued)

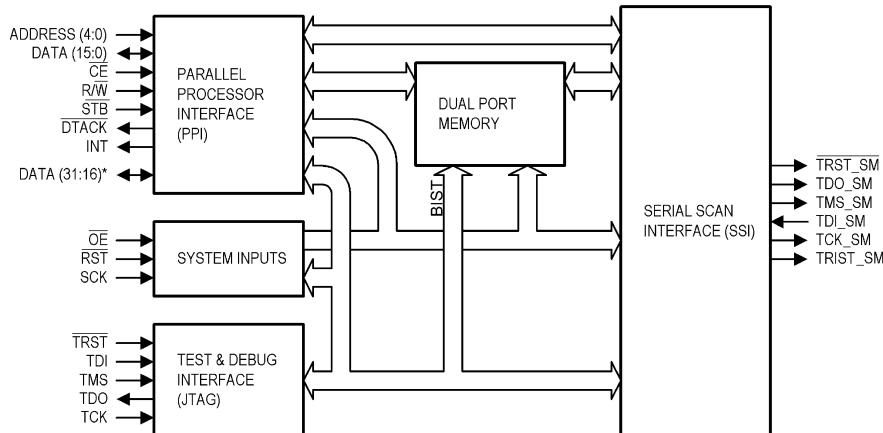

*Figure 1* shows a high level view of the SCANSTA101 Scan Master and its interface groups. *Table 1* provides a brief description of each of these interface groups. *Table 2* provides a brief description of the external interfaces. The device is composed of three interfaces around a dual-port

memory. These interfaces consist of the Parallel Processor Interface (PPI), Serial Scan Interface (SSI), and Test and Debug Interface. The System Input block is included only to designate inputs that have global use across the device. The Test and Debug interface supports BIST, boundary scan, and internal scan for this device.

**TABLE 1. Interface Descriptions**

| Interface                    | Description                                                                                                                                                         |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parallel Processor Interface | Used for configuration, ScanMaster scan chain loads and reads, programmable device file loads and reads, and status monitoring.                                     |

| Serial Scan Interface        | Performs parallel to serial conversion, sequences and formats the outgoing serial stream to conform to 1149.1 protocol.                                             |

| Test and Debug Interface     | Interfaces used for manufacturing tests, this includes a JTAG interface and a scan interface. The three scan interface pins are shared with three of the data pins. |

| System Inputs                | Interface inputs for system control, i.e. clock, reset and output tristate control.                                                                                 |

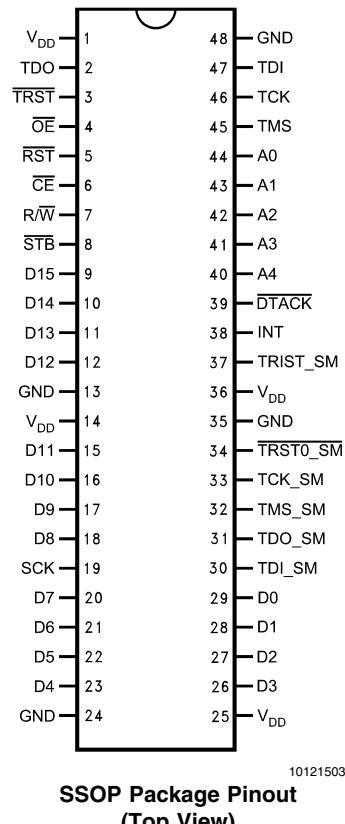

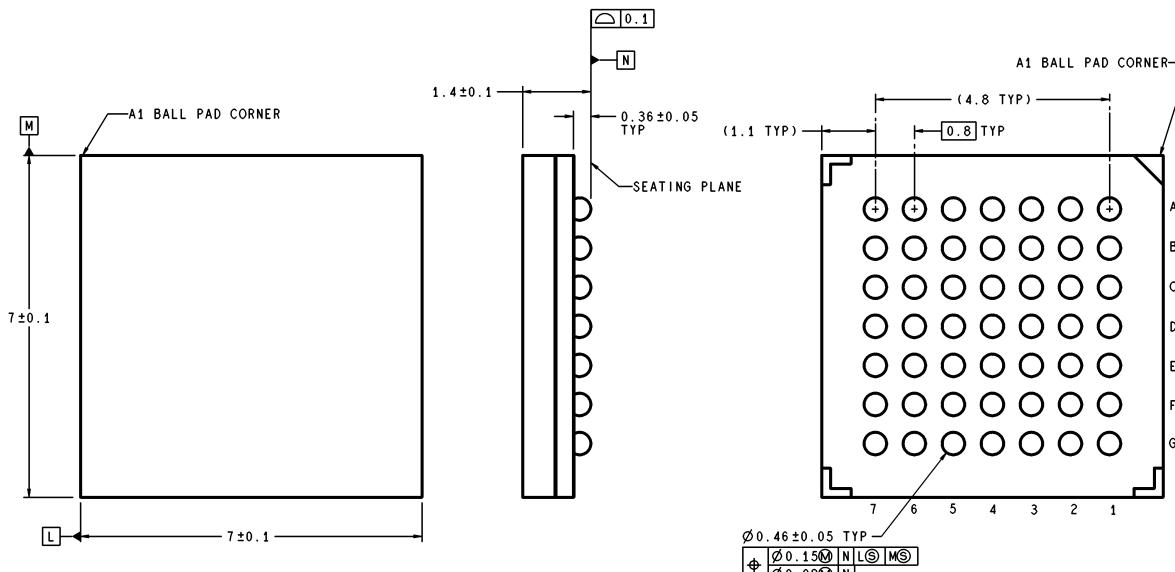

# Connection Diagrams

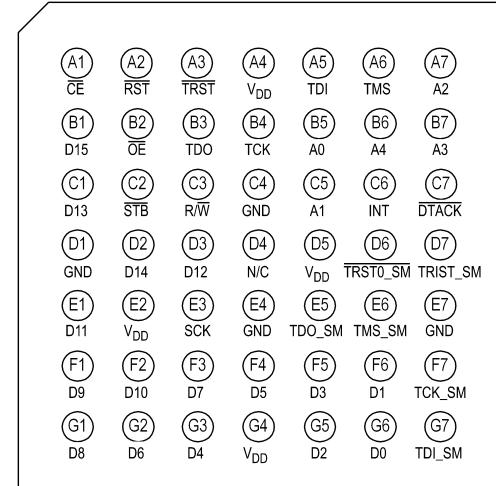

## BGA Package Pinout (Top View)

**TABLE 2. Pin Descriptions**

| Pin Name                    | No. Pins | I/O | Description                                                                                                                                                                                                                                                                                              |

|-----------------------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>VCC</b>                  | 4        | N/A | Power                                                                                                                                                                                                                                                                                                    |

| <b>GND</b>                  | 4        | N/A | Ground                                                                                                                                                                                                                                                                                                   |

| <b>D(15:0)</b>              | 16       | I/O | Bidirectional Data Bus. Signals are bonded out for the packaged device. D15 and D14 are shared pins with SCAN_IN, and SCAN_OUT respectively.                                                                                                                                                             |

| <b>D(31:16)</b><br>(Note 1) | 16       | I/O | Bidirectional Data Bus. These signals are not available in the packaged device.                                                                                                                                                                                                                          |

| <b>A(4:0)</b>               | 5        | I   | Address Bus                                                                                                                                                                                                                                                                                              |

| <b>SCK</b>                  | 1        | I   | The system clock that drives all internal timing. TCK_SM is a gated, divided and buffered version of SCK.                                                                                                                                                                                                |

| <b>INT</b>                  | 1        | O   | Interrupt Output                                                                                                                                                                                                                                                                                         |

| <b>OE</b>                   | 1        | I   | Output enable that tristates all 1149.1 "_SM" outputs when high.                                                                                                                                                                                                                                         |

| <b>DTACK</b>                | 1        | O   | <b>DTACK</b> is used to synchronize asynchronous transfers between the host and the STA101. When <b>CE</b> is high, <b>DTACK</b> is tristated. When <b>CE</b> is low, <b>DTACK</b> is enabled. <b>DTACK</b> goes low when data has been registered and then goes tri-state when the cycle has completed. |

| <b>R/W</b>                  | 1        | I   | <b>R/W</b> defines a PPI cycle. Read when high, write when low.                                                                                                                                                                                                                                          |

| <b>STB</b>                  | 1        | I   | Strobe is used for timing all PPI transfers. D(15:0), or D(31:0) in 32-bit mode, are tristated when <b>STB</b> is high. Data valid setup is with respect to the falling edge of <b>STB</b> and data valid hold is with respect to rising edge of <b>STB</b> .                                            |

| <b>CE</b>                   | 1        | I   | Chip Enable, when low, enables the PPI for data transfers. <b>CE</b> can remain low during back-to-back accesses. D(15:0), or D(31:0) in 32-bit mode, and <b>DTACK</b> are tristated when <b>CE</b> is high.                                                                                             |

| <b>RST</b>                  | 1        | I   | Asynchronous reset, when low, initializes the STA101.                                                                                                                                                                                                                                                    |

| <b>TDO</b>                  | 1        | O   | Test Data Out is the serial scan output from the STA101. TDO is enabled when <b>OE</b> is low.                                                                                                                                                                                                           |

| <b>TDI</b>                  | 1        | I   | Test Data In is the serial scan input to the STA101.                                                                                                                                                                                                                                                     |

| <b>TMS</b>                  | 1        | I   | Test Mode Select. The Test Mode Select pin is a serial input used to accept control logic to the Test & debug interface.                                                                                                                                                                                 |

| <b>TCK</b>                  | 1        | I   | Test Clock Input for 1149.1                                                                                                                                                                                                                                                                              |

| <b>TRST</b>                 | 1        | I   | Test Reset                                                                                                                                                                                                                                                                                               |

| <b>TDI_SM</b>               | 1        | I   | Scan Master Test Data Input in the Serial Scan Interface                                                                                                                                                                                                                                                 |

| <b>TDO_SM</b>               | 1        | O   | Scan Master Test Data Output in the Serial Scan Interface                                                                                                                                                                                                                                                |

| <b>TMS_SM</b>               | 1        | O   | Scan Master Test Mode Select in the Serial Scan Interface                                                                                                                                                                                                                                                |

| <b>TCK_SM</b>               | 1        | O   | Scan Master Test Clock in the Serial Scan Interface                                                                                                                                                                                                                                                      |

| <b>TRST0_SM</b>             | 1        | O   | Scan Master Test Reset output in the Serial Scan Interface                                                                                                                                                                                                                                               |

| <b>TRST1_SM</b><br>(Note 1) | 1        | O   | Redundant ScanMaster <b>TRST</b> . This signal is not available for the packaged device.                                                                                                                                                                                                                 |

| <b>TRIST_SM</b>             | 1        | O   | The TRI-STATE notification pin exerts a high signal when <b>TDO_SM</b> is TRI-STATED                                                                                                                                                                                                                     |

**Note 1:** D(31:16) in the Parallel Processor Interface and TRST1\_SM in the Serial Scan Interface are not bonded out for the packaged part. These are used in the 32-bit Macro Mode only.

**Absolute Maximum Ratings** (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

|                                              |                 |

|----------------------------------------------|-----------------|

| Supply Voltage ( $V_{CC}$ )                  | -0.5V to +4.0V  |

| DC Input Diode Current ( $I_{IK}$ )          |                 |

| $V_I = -0.5V$                                | -20 mA          |

| DC Input Voltage ( $V_I$ )                   | -0.5V to +4.0V  |

| DC Output Diode Current ( $I_{OK}$ )         |                 |

| $V_O = -0.5V$                                | -20 mA          |

| DC Output Voltage ( $V_O$ )                  | -0.5V to +4.0V  |

| DC Output Source/Sink Current ( $I_O$ )      | $\pm 50$ mA     |

| DC $V_{CC}$ or Ground Current per Output Pin | $\pm 50$ mA     |

| DC Latchup Source or Sink Current            | $\pm 300$ mA    |

| Junction Temperature                         |                 |

| Plastic                                      | +150°C          |

| Storage Temperature                          | -65°C to +150°C |

| Lead Temperature (Solder, 4sec)              |                 |

| 49L BGA                                      | 220°C           |

Max Pkg Power Capacity @ 25°C

|                                      |                       |

|--------------------------------------|-----------------------|

| 49L BGA                              | 1.47W                 |

| Thermal Resistance ( $\theta_{JA}$ ) |                       |

| 49L BGA                              | 85°C/W                |

| Package Derating                     | 11.8mW/°C above +25°C |

ESD Last Passing Voltage (Min) 2000V

**Recommended Operating Conditions**

|                                 |                |

|---------------------------------|----------------|

| Supply Voltage ( $V_{CC}$ )     | 3.0V to 3.6V   |

| Input Voltage ( $V_I$ )         | 0V to $V_{CC}$ |

| Output Voltage ( $V_O$ )        | 0V to $V_{CC}$ |

| Operating Temperature ( $T_A$ ) | -40°C to +85°C |

**Note 2:** Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. National does not recommend operation of SCAN STA products outside of recommended operation conditions.

**DC Electrical Characteristics**

Over recommended operating supply voltage and temperature ranges unless otherwise specified.

| Symbol      | Parameter                                                                                | Conditions                                                                                                            | Min             | Max       | Units   |

|-------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------|-----------|---------|

| $V_{IH}$    | Minimum High Input Voltage                                                               | $V_{OUT} = 0.1V$ or $V_{CC} - 0.1V$                                                                                   | 2.1             |           | V       |

| $V_{IL}$    | Maximum Low Input Voltage                                                                | $V_{OUT} = 0.1V$ or $V_{CC} - 0.1V$                                                                                   |                 | 0.8       | V       |

| $V_{OH}$    | Minimum High Output Voltage                                                              | $I_{OUT} = -100 \mu A$ , $V_{IN} = V_{IL}$ or $V_{IH}$                                                                | $V_{CC} - 0.2V$ | 2.2       | V       |

|             | Minimum High Output Voltage, TDO_SM, TMS_SM, TCK_SM, $\overline{TRST0\_SM}$ outputs only | $I_{OH} = -24 mA$ , $V_{IN} = V_{IL}$ or $V_{IH}$                                                                     |                 |           |         |

|             | Minimum High Output Voltage, All other outputs including 1149.1                          | $I_{OH} = -12 mA$ , $V_{IN} = V_{IL}$ or $V_{IH}$                                                                     |                 |           |         |

| $V_{OL}$    | Maximum Low Output Voltage                                                               | $I_{OUT} = +100 \mu A$ , $V_{IN} = V_{IL}$ or $V_{IH}$                                                                |                 | 0.2       | V       |

|             | Maximum Low Output Voltage, TDO_SM, TMS_SM, TCK_SM, $\overline{TRST0\_SM}$ outputs only  | $I_{OL} = 24 mA$ , $V_{IN} = V_{IL}$ or $V_{IH}$                                                                      |                 | 0.5       | V       |

|             | Maximum Low Output Voltage, all other outputs including 1149.1                           | $I_{OL} = 12mA$ , $V_{IN} = V_{IL}$ or $V_{IH}$                                                                       |                 | 0.4       | V       |

| $I_{IN}$    | Maximum Input Leakage Current, All pins except TDI, TMS, $\overline{TRST}$ , TDI_SM      | $V_{IN} = V_{CC}$ for TDI, $\overline{OE}$ , $V_{IN} = V_{CC}$ , GND for All Others                                   |                 | $\pm 5.0$ | $\mu A$ |

| $I_{ILR}$   | Maximum Input Leakage Current, TDI, TMS, $\overline{TRST}$ , TDI_SM                      | $V_{IN} = GND$                                                                                                        | -45             | -200      | $\mu A$ |

| $I_{IH}$    | Maximum Input Leakage Current, TDI, TMS, $\overline{TRST}$ , TDI_SM                      | $V_{IN} = V_{CC}$                                                                                                     |                 | 5.0       | $\mu A$ |

| $I_{OZ}$    | Maximum TRI-STATE Leakage Current                                                        | $V_{IN} = V_{CC}$ , GND, $V_{IN}$ ( $\overline{OE}$ , R/W, $\overline{CE}$ , $\overline{STB}$ ) = $V_{IL}$ , $V_{IH}$ |                 | $\pm 5.0$ | $\mu A$ |

| $I_{OFF}$   | Power Off Leakage Current All pins except TDI, TMS, $\overline{TRST}$ , and TDI_SM       | $V_{CC} = 0.0V$                                                                                                       |                 | 5.0       | $\mu A$ |

| $I_{CC}$    | Maximum Quiescent Supply Current                                                         |                                                                                                                       |                 | 250       | $\mu A$ |

| $I_{CCmax}$ | Maximum Supply Current                                                                   | All inputs low                                                                                                        |                 | 1.2       | mA      |

| $I_{CCT}$   | Maximum $I_{CC}$ /Input                                                                  | $V_{IN} = V_{CC} - 0.6V$                                                                                              |                 | 250       | $\mu A$ |

## AC Electrical Characteristics/Operating Requirements

Over recommended operating supply voltage and temperature ranges unless otherwise specified.  $C_L = 50 \text{ pF}$ ,  $R_L = 500\Omega$  unless otherwise specified.

| Symbol                                    | Parameter                                                                                                     | Conditions            | # of SCK<br>(Notes 3, 4) | Min | Max  | Units |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|-----|------|-------|

| <b>PARALLEL PROCESSOR INTERFACE (PPI)</b> |                                                                                                               |                       |                          |     |      |       |

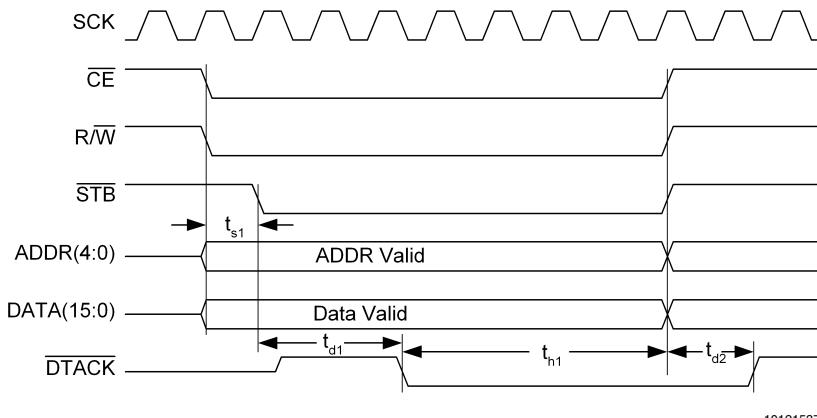

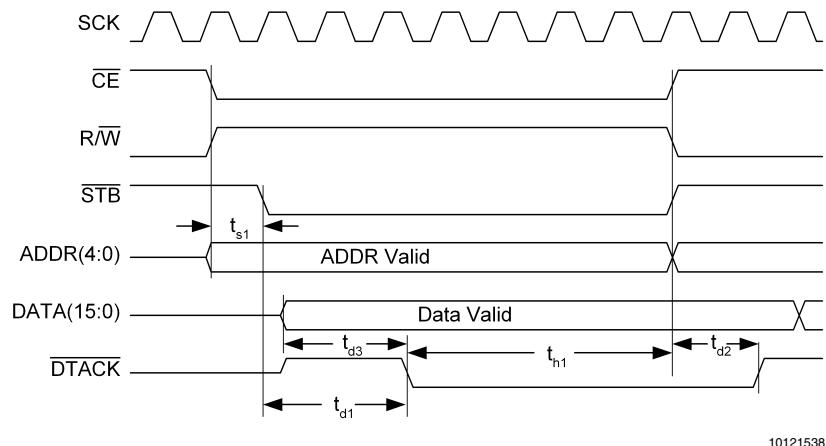

| $t_{S1}$                                  | Set Up Time<br>$\overline{CE}$ , $\overline{R/W}$ , Addr, Data to $\overline{STB}$                            | <i>Figures 11, 12</i> |                          | 0   |      | ns    |

| $t_{H1}$                                  | Hold Time<br>$\overline{CE}$ , $\overline{R/W}$ , Addr, Data to $\overline{STB}$                              | <i>Figures 11, 12</i> |                          | 0   |      | ns    |

| $t_{D1}$                                  | Propagation Delay<br>$\overline{STB}$ low to $\overline{DTACK}$ low, Register Write                           | <i>Figure 11</i>      | 2 or 3                   |     | 11.5 | ns    |

| $t_{D1}$                                  | Propagation Delay<br>$\overline{STB}$ low to $\overline{DTACK}$ low, Register Read                            | <i>Figure 12</i>      | 4 or 5                   |     | 11.5 | ns    |

| $t_{D1}$                                  | Propagation Delay<br>$\overline{STB}$ low to $\overline{DTACK}$ low, Memory Write: 16-bit first access        | <i>Figure 11</i>      | 3 or 4                   |     | 11.5 | ns    |

| $t_{D1}$                                  | Propagation Delay<br>$\overline{STB}$ low to $\overline{DTACK}$ low, Memory Write: 16-bit second access       | <i>Figure 11</i>      | 7 or 8                   |     | 11.5 | ns    |

| $t_{D1}$                                  | Propagation Delay<br>$\overline{STB}$ low to $\overline{DTACK}$ low, Memory Read: 16-bit first access         | <i>Figure 12</i>      | 9 or 10                  |     | 11.5 | ns    |

| $t_{D1}$                                  | Propagation Delay<br>$\overline{STB}$ low to $\overline{DTACK}$ low, Memory Read: 16-bit second access        | <i>Figure 12</i>      | 3 or 4                   |     | 11.5 | ns    |

| $t_{D2}$                                  | Propagation Delay<br>$\overline{STB}$ high to $\overline{DTACK}$ TRISTATE, Register Write                     | <i>Figure 11</i>      | 1 or 2                   |     | 10.0 | ns    |

| $t_{D2}$                                  | Propagation Delay<br>$\overline{STB}$ high to $\overline{DTACK}$ TRISTATE, Register Read                      | <i>Figure 12</i>      | 1 or 2                   |     | 10.0 | ns    |

| $t_{D2}$                                  | Propagation Delay<br>$\overline{STB}$ high to $\overline{DTACK}$ TRISTATE, Memory Write: 16-bit first access  | <i>Figure 11</i>      | 1 or 2                   |     | 10.0 | ns    |

| $t_{D2}$                                  | Propagation Delay<br>$\overline{STB}$ high to $\overline{DTACK}$ TRISTATE, Memory Write: 16-bit second access | <i>Figure 11</i>      | 1 or 2                   |     | 10.0 | ns    |

| $t_{D2}$                                  | Propagation Delay<br>$\overline{STB}$ high to $\overline{DTACK}$ TRISTATE, Memory Read: 16-bit first access   | <i>Figure 12</i>      | 1 or 2                   |     | 10.0 | ns    |

| $t_{D2}$                                  | Propagation Delay<br>$\overline{STB}$ high to $\overline{DTACK}$ TRISTATE, Memory Read: 16-bit second access  | <i>Figure 12</i>      | 1 or 2                   |     | 10.0 | ns    |

| $t_{D3}$                                  | Propagation Delay<br>Output data valid to $\overline{DTACK}$ low, all read cycles                             | <i>Figure 12</i>      | 1                        |     |      | ns    |

| $t_{PHL1}$                                | Propagation Delay<br>$\overline{STB}$ low to INT low, register write (clears Interrupt)                       | <i>Figure 11</i>      | 5 or 6                   |     | 10.5 | ns    |

| $t_W$                                     | Clock Pulse Width, SCK, H or L                                                                                |                       |                          | 3.0 |      | ns    |

| $f_{MAX}$                                 | Clock Frequency, SCK                                                                                          |                       |                          |     | 66   | MHz   |

| $t_{RELEASE}$                             | Release Time, $\overline{RST}$ to $\overline{STB}$                                                            |                       | 2                        |     |      | ns    |

**Note 3:** Due to uncertainty in the relationship of the  $\overline{STB}$  placement to the system clock, SCK, the  $\overline{STB}$  may be detected during the current or the next SCK cycle.

**Note 4:** An absolute maximum delay can be calculated as: (Max # SCK) x (SCK Period) +  $t_D$ .

For example, for  $t_{D1}$  ( $\overline{STB}$  low to  $\overline{DTACK}$  low, register write), the # SCK cycles is 2 or 3 and the delay,  $t_D$ , is 11.5ns. For a SCK with a 100ns period, the absolute maximum delay is  $(3 \times 100\text{ns}) + 11.5$ , or 311.5ns.

## AC Electrical Characteristics/Operating Requirements

Over recommended operating supply voltage and temperature ranges unless otherwise specified.  $C_L = 50 \text{ pF}$ ,  $R_L = 500\Omega$  unless otherwise specified. (Continued)

| Symbol                             | Parameter                                                                                     | Conditions       | Min | Max  | Units |

|------------------------------------|-----------------------------------------------------------------------------------------------|------------------|-----|------|-------|

| <b>SERIAL SCAN INTERFACE (SSI)</b> |                                                                                               |                  |     |      |       |

| $t_{D5}$                           | Propagation Delay<br>SCK to TCK_SM                                                            | <i>Figure 13</i> |     | 11.5 | ns    |

| $t_{D6}$                           | Propagation Delay<br>SCK to TDO_SM                                                            | <i>Figure 13</i> |     | 12.0 | ns    |

| $t_{D7}$                           | Propagation Delay<br>SCK to TMS_SM                                                            | <i>Figure 13</i> |     | 12.5 | ns    |

| $t_{D8}$                           | Propagation Delay - tpLH<br>SCK to TRIST_SM                                                   | <i>Figure 13</i> |     | 15.0 | ns    |

| $t_{D9}$                           | Propagation Delay - tpHL<br>SCK to TRIST_SM                                                   | <i>Figure 13</i> |     | 12.5 | ns    |

| $t_{D10}$                          | Propagation Delay<br>SCK to TDO_SM disable                                                    | <i>Figure 13</i> |     | 12.5 | ns    |

| $t_{D11}$                          | Propagation Delay<br>SCK to TDO_SM enable                                                     | <i>Figure 13</i> |     | 14.0 | ns    |

| $t_{EN1}$                          | Enable Delay<br>$\overline{OE}$ low to TCK_SM, TDO_SM, TMS_SM, or<br>$\overline{TRST0\_SM}$   | <i>Figure 13</i> |     | 12.0 | ns    |

| $t_{DIS1}$                         | Disable Delay<br>$\overline{OE}$ high to TCK_SM, TDO_SM, TMS_SM, or<br>$\overline{TRST0\_SM}$ | <i>Figure 13</i> |     | 11.0 | ns    |

| $t_{EN2}$                          | Enable Delay<br>$\overline{OE}$ low to TRIST_SM                                               |                  |     | 10.0 | ns    |

| $t_{DIS2}$                         | Disable Delay<br>$\overline{OE}$ high to TRIST_SM                                             |                  |     | 11.5 | ns    |

| $t_{DIS3}$                         | Disable Delay<br>$RST$ low to $\overline{TRST0\_SM}$                                          |                  |     | 12.5 | ns    |

| $t_{S2}$                           | Setup Time<br>SCK to TDI_SM                                                                   | <i>Figure 13</i> | 3.5 |      | ns    |

| $t_{H2}$                           | Hold Time<br>SCK to TDI_SM                                                                    | <i>Figure 13</i> | 2.0 |      | ns    |

**AC Electrical Characteristics/Operating Requirements**

Over recommended operating supply voltage and temperature ranges unless otherwise specified.  $C_L = 50 \text{ pF}$ ,  $R_L = 500\Omega$  unless otherwise specified. (Continued)

| Symbol                                                       | Parameter                                          | Conditions | Min  | Max | Units |

|--------------------------------------------------------------|----------------------------------------------------|------------|------|-----|-------|

| <b>TEST &amp; DEBUG INTERFACE TIMING REQUIREMENTS (SCAN)</b> |                                                    |            |      |     |       |

| $t_S$                                                        | Setup Time<br>TMS to TCK                           |            | 2.0  |     | ns    |

| $t_H$                                                        | Hold Time<br>TMS to TCK                            |            | 1.0  |     | ns    |

| $t_S$                                                        | Setup Time<br>TDI to TCK                           |            | 1.0  |     | ns    |

| $t_H$                                                        | Hold Time<br>TDI to TCK                            |            | 2.0  |     | ns    |

| $t_W$                                                        | Pulse Width<br>TCK (H or L)                        |            | 10.0 |     | ns    |

| $t_{WL}$                                                     | Reset Pulse Width<br>$\overline{\text{TRST}}$ (L)  |            | 2.5  |     | ns    |

| $t_{REC}$                                                    | Recovery Time<br>TCK from $\overline{\text{TRST}}$ |            | 2.0  |     | ns    |

| $f_{MAX}$                                                    | Maximum Clock Frequency, TCK                       |            |      | 25  | MHz   |

## Applications/Programmers Reference

TABLE 3. Register Summary

| Address | Type | Mnemonic | Register                      | Active Register Bits | Reset Value |

|---------|------|----------|-------------------------------|----------------------|-------------|

| 00h     | RW   | START    | Start Register                | 5                    | 0000h       |

| 01h     | RW   | STATUS   | Status Register               | 10                   | 0800h       |

| 02h     | RW   | INTCTRL  | Interrupt Control Register    | 8                    | 0000h       |

| 03h     | RW   | INTSTAT  | Interrupt Status Register     | 8                    | 0000h       |

| 04h     | RW   | SETUPR   | Setup Register                | 8                    | 0043h       |

| 05h     | RW   | CLKDIV   | Clock Divider Register        | 6                    | 0000h       |

| 07h     | RW   | EXPR     | TDI_SM LFSR Exponent Register | 3                    | 0000h       |

| 08h     | RW   | LSSEDR   | TDI_SM LSB Seed Register      | 16                   | 0000h       |

| 09h     | RW   | MSSEDR   | TDI_SM MSB Seed Register      | 16                   | 0000h       |

| 0Ah     | RW   | LSRESR   | TDI_SM LSB Result Register    | 16                   | 0000h       |

| 0Bh     | RW   | MSRESR   | TDI_SM MSB Result Register    | 16                   | 0000h       |

| 0Ch     | RW   | INDEXR   | Index Register                | 16                   | 0000h       |

| 11h     | RW   | VINDEXR  | Vector Index Register         | 16                   | 0000h       |

| 13h     | RW   | HTINDEXR | Header/Trailer Index Register | 16                   | 0000h       |

| 15h     | RW   | MINDEXR  | Macro Index Register          | 16                   | 0000h       |

| 17h     | RW   | SINDEXR  | Sequencer Index Register      | 16                   | 0000h       |

| 19h     | RW   | BSINDEXR | Bridge Support Register       | 16                   | 0000h       |

TABLE 4. Memory/Register Address Map

| A4 | A3 | A2 | A1 | A0 | Function               | Base Address | Long Word Index | Structure/Size           |

|----|----|----|----|----|------------------------|--------------|-----------------|--------------------------|

| 0  | 0  | 0  | 0  | 0  | Start                  | N/A          | N/A             | 16-bit Register          |

| 0  | 0  | 0  | 0  | 1  | Status                 | N/A          | N/A             | 16-bit Register          |

| 0  | 0  | 0  | 1  | 0  | Interrupt Control      | N/A          | N/A             | 16-bit Register          |

| 0  | 0  | 0  | 1  | 1  | Interrupt Status       | N/A          | N/A             | 16-bit Register          |

| 0  | 0  | 1  | 0  | 0  | Setup                  | N/A          | N/A             | 16-bit Register          |

| 0  | 0  | 1  | 0  | 1  | Clock Divider          | N/A          | N/A             | 16-bit Register          |

| 0  | 0  | 1  | 1  | 1  | TDI_SM LFSR Exponent   | N/A          | N/A             | 16-bit Register          |

| 0  | 1  | 0  | 0  | 0  | TDI_SM LFSR LSB Seed   | N/A          | N/A             | 16-bit Register (Note 5) |

| 0  | 1  | 0  | 0  | 1  | TDI_SM LFSR MSB Seed   | N/A          | N/A             | 16-bit Register (Note 5) |

| 0  | 1  | 0  | 1  | 0  | TDI_SM LFSR LSB Result | N/A          | N/A             | 16-bit Register (Note 5) |

| 0  | 1  | 0  | 1  | 1  | TDI_SM LFSR MSB Result | N/A          | N/A             | 16-bit Register (Note 5) |

| 0  | 1  | 1  | 0  | 0  | Index Register         | N/A          | N/A             | 16-bit Register (Note 6) |

| 0  | 1  | 1  | 0  | 1  | TDO_SM                 | 0            | 0 - 0x1BF       | (Note 7)                 |

| 0  | 1  | 1  | 1  | 0  | TDI_SM                 | 0 x 1C0      | 0 - 0x1BF       | (Note 7)                 |

| 0  | 1  | 1  | 1  | 1  | Expected               | 0 x 380      | 0 - 0x1BF       | (Note 7)                 |

| 1  | 0  | 0  | 0  | 0  | Mask                   | 0 x 540      | 0 - 0x1BF       | (Note 7)                 |

| 1  | 0  | 0  | 0  | 1  | Vector Index           | N/A          | N/A             | 16-bit Register          |

| 1  | 0  | 0  | 1  | 0  | Vector 1               | 0 x 700      | 0x0 - 0x1       | (Note 8) Table 5         |

|    |    |    |    |    | Vector 2               | 0 x 700      | 0x2 - 0x3       |                          |

|    |    |    |    |    | Vector 3               | 0 x 700      | 0x4 - 0x5       |                          |

|    |    |    |    |    | Vector 4               | 0 x 700      | 0x6 - 0x7       |                          |

| 1  | 0  | 0  | 1  | 1  | Header/Trailer Index   | N/A          | N/A             | 16-bit Register          |

| 1  | 0  | 1  | 0  | 0  | Data Header            | 0 x 708      | 0x0 - 0x1F      | Table 6                  |

|    |    |    |    |    | Data Trailer           | 0 x 728      | 0x20 - 0x3F     |                          |

|    |    |    |    |    | Instruction Header     | 0 x 748      | 0x40 - 0x5F     |                          |

|    |    |    |    |    | Instruction Trailer    | 0 x 768      | 0x60 - 0x7F     |                          |

| 1  | 0  | 1  | 0  | 1  | Macro Index            | N/A          | N/A             | 16-bit Register          |

TABLE 4. Memory/Register Address Map (Continued)

| A4 | A3 | A2 | A1 | A0 | Function                                        | Base Address                                   | Long Word Index                | Structure/Size  |

|----|----|----|----|----|-------------------------------------------------|------------------------------------------------|--------------------------------|-----------------|

| 1  | 0  | 1  | 1  | 0  | Macro 1<br>Macro 2<br>Macro 3 . . .<br>Macro 16 | 0 x 788<br>0 x 789<br>0 x 78A . . .<br>0 x 797 | 0x0<br>0x1<br>0x2 . . .<br>0xF | Tables 7, 8, 9  |

| 1  | 0  | 1  | 1  | 1  | Sequencer Index                                 | N/A                                            | N/A                            | 16-bit Register |

| 1  | 1  | 0  | 0  | 0  | Sequencer                                       | 0 x 798                                        | 0x0 - 0x1F                     | Table 10        |

| 1  | 1  | 0  | 0  | 1  | Scan Bridge Support Index                       | N/A                                            | N/A                            | 16-bit Register |

| 1  | 1  | 0  | 1  | 0  | Scan Bridge Support                             | 0 x 7B8                                        | 0x0 - 0x3F                     | Table 11        |

**Note 5:** The TDI\_SM LFSR result and seed registers require two sequential reads/writes for each register pair.

**Note 6:** The index register is used to set the individual address pointers. Writing to the index register will set each of the individual address pointers (TDO\_SM, TDI\_SM, Expected, and Mask). The individual address pointers will automatically increment with each long word read from TDI\_SM or each long word written to the TDO\_SM, Expected, or Mask memory spaces.

**Note 7:** The actual address is calculated from the base address of the memory area plus the content of its address pointer.

**Note 8:** The upper two bytes of each vector is ignored. These have been inserted to make the space align on long word boundaries.

TABLE 5. Vector Structure

| Bit(s)      | Function                                     |

|-------------|----------------------------------------------|

| 0x00 - 0x1F | Length (maximum of 4G)                       |

| 0x20 - 0x27 | Macro Number (1 of 256) Room for scalability |

| 0x28 - 0x2E | Reserved                                     |

| 0x2F        | Preloaded data / Load-on-the-fly (LotF)      |

| 0x30 - 0x3F | Reserved                                     |

TABLE 6. Header/Trailer Structure

| Bit(s)       | Function                                 |

|--------------|------------------------------------------|

| 0x00 - 0x1F  | 32-bit count (Note 9)                    |

| 0x20 - 0x3FF | 124 bytes (992 bits) header/trailer data |

**Note 9:** Count must be greater than zero if the Header/Trailer Usage bits are not equal to "000" or "111".

TABLE 7. Macro Structure

| Bit(s)      | Function                                                                                                                                                |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x1F        | Compare                                                                                                                                                 |

| 0x1E        | Use Mask / Compare full length of vector (not including header/trailer)                                                                                 |

| 0x1D - 0x1B | Post-shift TCK_SM Count                                                                                                                                 |

| 0x1A - 0x18 | Pre-shift TCK_SM Count                                                                                                                                  |

| 0x17        | Sync Bit Support Enable                                                                                                                                 |

| 0x16        | Macro Structure Bit 8 Enable (Ignored for the shift macros with or without capture)                                                                     |

| 0x15        | Macro Structure bit 7 Enable (Ignored for the shift macros with or without capture)                                                                     |

| 0x14 - 0x12 | Header/Trailer Usage                                                                                                                                    |

| 0x11        | Macro Type bit 1                                                                                                                                        |

| 0x10        | Macro Type bit 0                                                                                                                                        |

| 0xF - 0x9   | Last 7 TMS_SM bits                                                                                                                                      |

| 0x8         | Presented during the falling edge of TCK_SM at terminal count during a Shift macro. Use in the same manner as other TMS bits for State and BIST Macros. |

| 0x7         | Loop Bit if Macro type is Shift (for 1149.1 it would be a 0) or BIST                                                                                    |

| 0x6 - 0x0   | First 7 TMS_SM Bits (LSB is first bit to be shifted out of TMS_SM)                                                                                      |

TABLE 8. Header / Trailer Usage

| Bit 2 | Bit 1 | Bit 0 | Function                    |

|-------|-------|-------|-----------------------------|

| 0     | 0     | 0     | Ignore Headers and Trailers |

**TABLE 8. Header / Trailer Usage (Continued)**

| Bit 2 | Bit 1 | Bit 0 | Function                                |

|-------|-------|-------|-----------------------------------------|

| 0     | 0     | 1     | Use Instruction Header                  |

| 0     | 1     | 0     | Use Instruction Trailer                 |

| 0     | 1     | 1     | Use both Instruction Header and Trailer |

| 1     | 0     | 0     | Use Data Header                         |

| 1     | 0     | 1     | Use Data Trailer                        |

| 1     | 1     | 0     | Use both Data Header and Trailer        |

| 1     | 1     | 1     | Reserved                                |

**TABLE 9. Macro Type bits 10 and 11**

| Bit 1 | Bit 0 | Function                 | Function                                                        |

|-------|-------|--------------------------|-----------------------------------------------------------------|

| 0     | 0     | BIST Macro               | Loop on loop bit for Vector count. No Data                      |

| 0     | 1     | Shift Macro              | Loop on loop bit for vector count. Read data from TDO_SM memory |

| 1     | 0     | Shift Macro with Capture | Loop on loop bit for vector count. Read data from TDO_SM memory |

| 1     | 1     | State Macro              | Do not loop on loop bit of macro. No data to be shifted         |

**TABLE 10. Sequencer Structure**

| Bit(s)        | Function                                     |

|---------------|----------------------------------------------|

| 0x00 - 0x1F   | Sequence repeat count (up to 255)            |

| 0x20 - 0x2F   | Vector repeat count                          |

| 0x30 - 0x3F   | Vector number                                |

| ..x.. - ..x.. | Repeat vector repeat count and vector number |

| 0x3E0 - 0x3EF | Vector repeat count (up to 255)              |

| 0x3F0 - 0x3FF | Vector number (up to 63)                     |

**TABLE 11. Scan Bridge Support Structure**

| Bit(s)        | Function                                                       |

|---------------|----------------------------------------------------------------|

| 0x00 - 0x0F   | Levels of Scan Bridge support to be inserted in the scan chain |

| 0x10 - 0x17   | Hierarchical Level 0 Scan Bridge Address                       |

| 0x18 - 0x1F   | Hierarchical Level 0 Scan Bridge LSP                           |

| 0x20 - 0x27   | Hierarchical Level 1 Scan Bridge Address                       |

| 0x28 - 0x2F   | Hierarchical Level 1 Scan Bridge LSP                           |

| ..x.. - ..x.. | Hierarchical Level Scan Bridge Address and LSP                 |

| 0x7F0 - 0x7F7 | Hierarchical Level 125 Scan Bridge Address                     |

| 0x7F8 - 0x7FF | Hierarchical Level 125 Scan Bridge LSP                         |

## Module Descriptions

Figure 1 shows a high level view of the STA101 which is composed of two main modules, the Parallel Processor Interface (PPI) and the Serial Scan Interface (SSI) which interface to each other through a dual-port memory. The PPI provides a parallel interface for transferring data into and out of the dual-port memory, and for configuring, controlling and obtaining the status of the device. The SSI which resides on the other side of the dual-port memory provides the parallel-to-serial and serial-to-parallel conversion paths for providing test data and test control to support the ScanMaster and IEEE 1532 functions.

## Dual Port Memory

The dual port memory will be treated as a separate module in the design to facilitate portability of the RTL of the design to an FPGA host. The Dual Port Memory module is a 2048 x 32 bit dual-port memory which acts as the buffer between

the PPI and the SSI. There are seven regions of memory as viewed from the processor side. These regions, shown in Table 4, are TDO\_SM, TDI\_SM, Expected, Mask, Vector, Header/Trailer, Macro, Sequencer, and ScanBridge Support. Each has a pointer which resides in the PPI.

The memory is big endian oriented and is viewed as a single entity from the SSI side and the SSI maintains a pointer. The dual port memory module does not include any logic outside of its own macro function, so all the timing and support logic is included in the following PPI and SSI sections. There will be no logic included in the STA101 design to utilize the "busy" indicators to keep the user from overwriting memory locations. The only area where this could occur in memory would be the TDI\_SM memory space since both the SSI and PPI can write to this space, but the drivers shouldn't allow PPI writes to this area during normal operations.

## Parallel Processor Interface

The overall function of the PPI is to receive the parallel data from the processor interface, store the data in its appropriate register or memory location, act on the data if the data are PPI control data, provide status data back to the processor and to provide a read path for result data to the processor. To perform these functions, the PPI consists of seven main blocks of logic along with the dual-port memory. These blocks include the Edge Detector (ED), Processor Interface Controller (PIC), the Memory/ Register Decoder (MRD), the Word/Long Word Converter (WLWC), the Control Generator (CG), the Status/Interrupt Generator (SIG) and the Flag Generator (FG).

### WORD/LONG WORD CONVERTER

The Word/Long Word Converter (WLWC) has four 16-bit capture registers, and least significant/ most significant (LS/ MS) word read capture register pair and an LS/MS word write capture register pair. Each register within the write register pair has a separate enable to allow for the necessary control to accomplish word to long word conversions when in the 16-bit mode. In 32-bit mode, these enables will be driven simultaneously. A mux is provided in front of the MS word register for the write capture to select between the 32-bit and 16-bit mode external bus. Only one enable and a mux select is needed to control the read capture register pair to accomplish the long word to word conversions when in the 16-bit mode. In the 32-bit mode, the mux selection doesn't change so 32-bits are always driven. A mux is on either side of the LS word register for the read capture. The one at the register output provides for selection between the 32-bit and 16-bit mode. The one at the register input is for selection between register space and memory space. All the control for this block is provided by the PIC and MRD with the 16/32 bit mode enable coming from the Setup register.

### EDGE DETECTOR

The PPI module can support either an asynchronous or synchronous processor interface. For an asynchronous interface the circuit initially synchronizes STB and CE to the system clock, SCK, by pipelining these two signals through two flip-flop stages and then performs an edge detection on STB and CE. For a synchronous parallel processor interface this circuit just performs an edge detection. The outputs of this circuit, one clock wide pulses indicating the detection of negative and positive edges, will be used by the Processor Interface Controller (PIC) state machine to start and to end a processor access.

### PROCESSOR INTERFACE CONTROLLER

The Processor Interface Controller (PIC) monitors the incoming processor control signals and sets up the appropriate internal control signals to move the data into memory or an internal register on a write or to move the data out of memory or out of an internal register on a read. The PIC edge detects the CE and the STB to start the access. The PIC provides the control for the word to long word conversion in the WLWC by controlling the three enables and the mux select (READ\_MSW) to the capture registers. The PIC also controls when the internal read/write enable is issued to the memory to complete the read/write operation. Timing for register and memory read and write operations is described in *PPI INTERFACE TIMING*.

### MEMORY/REGISTER DECODER

The Memory/Register Decoder (MRD) contains all six index registers (Index, Vector Index, Header/Trailer Index, Macro Index, Sequencer Index and ScanBridge Support Index) and four address registers (TDI\_SM Address, TDO\_SM Address, Expected Address and Mask Address). In general, both index and address registers are used to maintain pointers to their respective memory spaces. The exception is the Index register which is used to set values in the four address registers, i.e., writing to the Index register sets each of the address registers. The value written to each address register is the sum of its base address and the value written to the Index register (the offset). All index and address registers, with the exception of the Index register, will auto-increment with each access to the corresponding memory space.

The MRD provides the address decode to generate all the control and status register enables for the CG and the SIG. The MRD also provides the mux selects for the register or memory selection for the read capture operation in the WLWC.

### CONTROL GENERATOR

The Control Generator has the seven control registers within it. The Start, Interrupt Control, Setup, Clock Divider, TDI\_SM LFSR Exponent, TDI\_SM LFSR LSB Seed, and TDI\_SM LFSR MSB Seed registers are all within this block. The CG will issue a strobe to the SSI when a write has been issued to the Start or Setup registers so the SSI can react to the new control data. The strobe will be derived from edge detecting the enables to the Start or Setup registers. The "new" data to the SSI are the Use Sequencer bit and three Use Vector bits from the Start register, and the TDO Default Value, TRST, ScanBridge Support Initiate/Release, three Sync Bit Length, and two Test Loop-back bits from the Setup register.

### STATUS/INTERRUPT GENERATOR

The Status/Interrupt Generator has the four status registers plus the logic to generate the interrupts and clear the interrupts on a read. The registers are the Status, Interrupt Status, TDI\_SM LFSR LSB Result and TDI\_SM LFSR MSB Result registers. The SIG receives the LFSR result and strobe signal SSI\_LFSR\_EN from the SSI and captures the data in the LSB and MSB registers. The SIG receives the compare result bit value from the SSI along with the compare result bit clear and the compare result bit load.

The SIG receives the 4 memory space flags from the FG along with their associated load and clear signals so these bits may be constantly updated. The half-full, half-empty, full and empty flags will be generated and updated regardless of the states of their respective interrupt enables. The SIG also receives the 4 interrupt enables for the flags. The SIG also receives the sequencer active and 3 vector active signals from the SSI. These will also be updated regardless of the enable state.

If an interrupt enable is set then an interrupt will be generated. If an interrupt occurs at the same time as the interrupt status is being read, then the interrupt will be set after the read is complete. All bits in the Interrupt Status register are cleared when the register is read.

### FLAG GENERATOR

The FG takes in the TDI\_SM or TDO\_SM pointer values from the PPI address pointers, compares them and generates the appropriate flags. If a flag condition has occurred, it is passed along with the corresponding load enable to set

## Parallel Processor Interface

(Continued)

the bit in the status register in the SIG. If the flag condition changes then the clear for the corresponding bit is passed to the SIG to clear the flag. The TDO\_SM empty and the TDI\_SM full flags are passed to the SSI also. A counter enable is passed from the SSI indicate to the FG when the SSI's pointer value has changed. If a decrement and an increment occur at the same time to either of the counters, the counter value will not change.

### PPI INTERFACE TIMING

The processor accesses to SCANSTA101 can be classified into six categories:

- register read

- register write

- 16-bit memory read

- 16-bit memory write

- 32-bit memory read

- 32-bit memory write

Register reads and register writes are performed the same whether the device is in 16-bit mode or 32-bit mode. In 32-bit mode, only the LS word is used. The MS word is ignored. All timing for the 16-bit and 32-bit modes are exactly the same.

The 16-bit mode memory write is accomplished by performing two consecutive register writes with the only difference being that the actual write occurs on the second access. The 16-bit mode register read consists of two accesses, with the first access performed similar to the 16-bit register read but requiring one more clock to complete the memory access. Since all 32-bits of the memory data are captured on the first access, the second memory read access is 2 clocks shorter than the first.

The processor initiates a write cycle by asserting  $\overline{CE}$  followed by  $\overline{STB}$ . A set time prior to asserting  $\overline{STB}$ , the  $\overline{R/W}$  is driven low and the address and data buses are driven by valid address and data, respectively. After edge detecting the  $\overline{STB}$  and registering all the inputs, the address is decoded to determine which internal address within the STA101 will be written by the processor. The  $\overline{DTACK}$  will be asserted on the same rising edge of SCK on which the  $\overline{STB}$ 's negative edge is detected, indicating to the processor that it can deassert the  $\overline{STB}$ . When the STA101 detects the positive edge of the  $\overline{STB}$ , it will deassert the  $\overline{DTACK}$  indicating to the processor that it can start a new cycle. The processor can start a new cycle by asserting the  $\overline{STB}$  and by driving the address and data buses with new address and data.

A read cycle is similar to the write cycle except that the  $\overline{DTACK}$  will not be asserted until the selected address location's contents are loaded. So, for a 16-bit register read it takes one more clock than it does for a write cycle.

Accesses to STA101 memory require two consecutive accesses in the 16-bit external bus mode. The memory writes are similar to register writes but the only difference is that processor has to perform two consecutive 16-bit writes to write to the selected memory location. One important note, during a memory read, is that  $\overline{DTACK}$  is not asserted until the contents of the memory is loaded into the capture registers. For this reason the first read from the memory requires five clocks which includes the memory access time, while the second read is done in 3 clock cycles.

## Serial Scan Interface

The Serial Scan Interface consists of the following units:

- Clock Divider and TCK\_SM Control

- TAP Tracker

- Pointer Generator

- Structure (Sequencer/Vector/Macro/ScanBridge) Decoder

- Structure (Sequencer/Vector/Macro/ScanBridge) Control Registers

- Count Generator

- Shifter (TDO\_SM/TDI\_SM/TMS\_SM)

- Comparator

- Expected and Mask Registers

- Serial Scan Interface Controller (SSIC) and ScanBridge Controller

The clock divider unit divides system clock SCK based on the programmable divisor set in the clock divider to generate TCK\_SM. The TCK\_SM control unit gates TCK\_SM if the TDO\_SM buffer is empty.

The TAP Tracker unit keeps track of the target's TAP controller state. The purpose of the TAP Tracker is to determine whether the target's TAP controller is in SIR or SDR state, so that the necessary PAD bits are inserted.

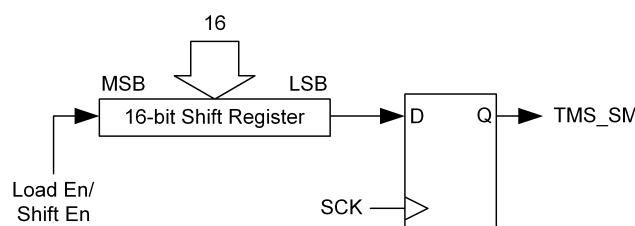

The shifter block contains two 32-bit shift registers for TDO\_SM and TDI\_SM respectively, and a 16-bit shift register for TMS\_SM.

The comparator unit compares the serial input on the TDI\_SM pin with the expected, data bit by bit, if the compare bit of the Macro Structure is set. However, if compare/mask bit is set, then the comparator unit compares only those bits that are unmasked.

Expected and Mask Registers contain the data fetched from the memory. This data will be used by the comparator to compare the TDI\_SM input with the expected data.

The SSIC provides the timing and control signals to synchronize the operation of the various blocks in the SSI. The ScanBridge Controller consists of the control logic to set up the ScanBridge's hierarchy, if the ScanBridge Support Initiate/Release bit is enabled, prior to scanning actual test vectors out of TDO\_SM.

### CLOCK DIVIDER AND TCK\_SM CONTROL

The clock divider will be a binary divider where only one bit of the clock divider register will be set to one at any given time. The implementation will ignore bits 0, and 8-15, so the supported divisors are 2, 4, 8, 16, 32, 64 and 128.

To generate a TCK\_SM of frequency SCK/4, the clock divider register should be set to 4 (00000100). This will enable the gate at the output of bit 2 of the counter to generate a clock of SCK divided by 4. If in LotF mode, then the TCK\_SM enable from the SSIC will gate TCK\_SM when the TDO\_SM buffer is empty.

### TAP TRACKER

The TAP Tracker consists of a 16-bit register to trace the IEEE Standard 1149.1 state machine. The state machine is one hot encoded and will continuously track the target's TAP Controller based on the TMS\_SM sequence. The TAP Tracker will be used by the ScanBridge support controller to determine whether the target's TAP controller is in SIR or SDR state so that it can insert an appropriate number of pre and post-PAD bits.

## Serial Scan Interface (Continued)

The TAP Tracker will enter Test-Logic Reset state upon setting the TRST bit (bit 5) in the Setup register or by issuing a sequence of five TMS\_SM high bits.

### SHIFTER

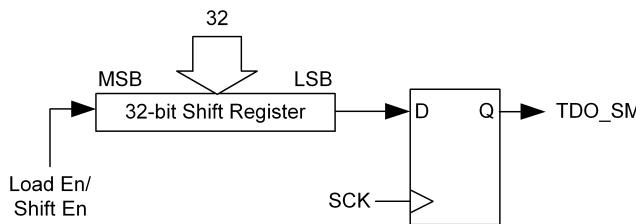

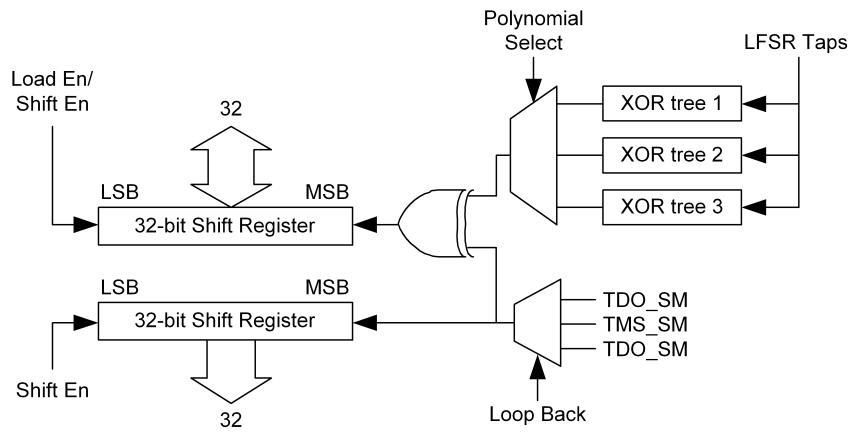

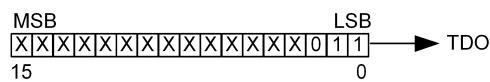

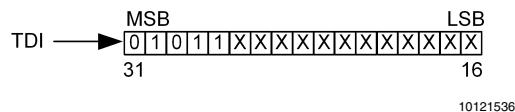

The Shifter block contains two 32-bit shift registers for TDO\_SM and TDI\_SM respectively, and one 16-bit shift register for TMS\_SM. The TMS\_SM shifter block diagram is shown in *Figure 2*, the TDO\_SM shifter block diagram is shown in *Figure 3*, and the TDI\_SM shifter block diagram is shown in *Figure 4*.

Before the start of a vector processing the TMS\_SM shifter is loaded with the least significant 16 bits of the macro structure. Based on the pre-shift TCK\_SM count, the TMS\_SM

shifter will skip (7 - pre-shift count) least significant bits. e.g., if the pre-shift count is 4, the least significant 3 bits of the TMS\_SM shifter will not be used to drive TMS\_SM during pre-shift. Similarly, if the post-shift is less than 7 then, during post shift only the number of bits equal to the post-shift count following the macro structure bit 8 will be used to drive TMS\_SM.

The STA101 memory is organized in big Endian format. Since a memory write can be accomplished by two consecutive writes to the same location when embedded software loads the TDO\_SM memory, it is assumed that the least significant 16 bits are written first and then the most significant 16 bits. Therefore, when the Sequencer or a Vector is initialized the SSIC can directly fetch and load the long word to the TDO\_SM shifter without any modification.

10121521

**FIGURE 2. TMS\_SM Shifter**

10121522

**FIGURE 3. TDO\_SM Shifter**

Similarly, reading from TDI\_SM memory can be accomplished by two consecutive reads. When reading from the

TDI\_SM memory, the first read will contain the least significant 16 bits and the second read the most significant 16 bits.

## Serial Scan Interface (Continued)

10121523

**FIGURE 4. TDI\_SM Shifter**

The TDI\_SM shifter unit consists of two 32-bit shift registers as shown in *Figure 4*. The shift register on top will be used as an LFSR register. However, before using the TDI\_SM LFSR register, the LFSR Exponent and LFSR Seed registers must be written with valid data. The LFSR Exponent register must be written with a 3-bit binary encoded value such that the corresponding polynomial out of the five available polynomials will be selected. The value written to the LFSR Seed registers will be used to initialize the TDI\_SM LFSR register to a predetermined state. Once the test vector has completely scanned in, the final contents of the LFSR register will be transferred to the LFSR Result registers. The 32-bit shift register at the bottom will be used to shift in TDI\_SM directly in normal mode or to shift in TMS\_SM or TDO\_SM in the

loop-back mode. After shifting in every thirty two bits, the contents of this register will be transferred to the corresponding TDI memory location before the next shift operation.

### SHIFTER IMPLEMENTATION

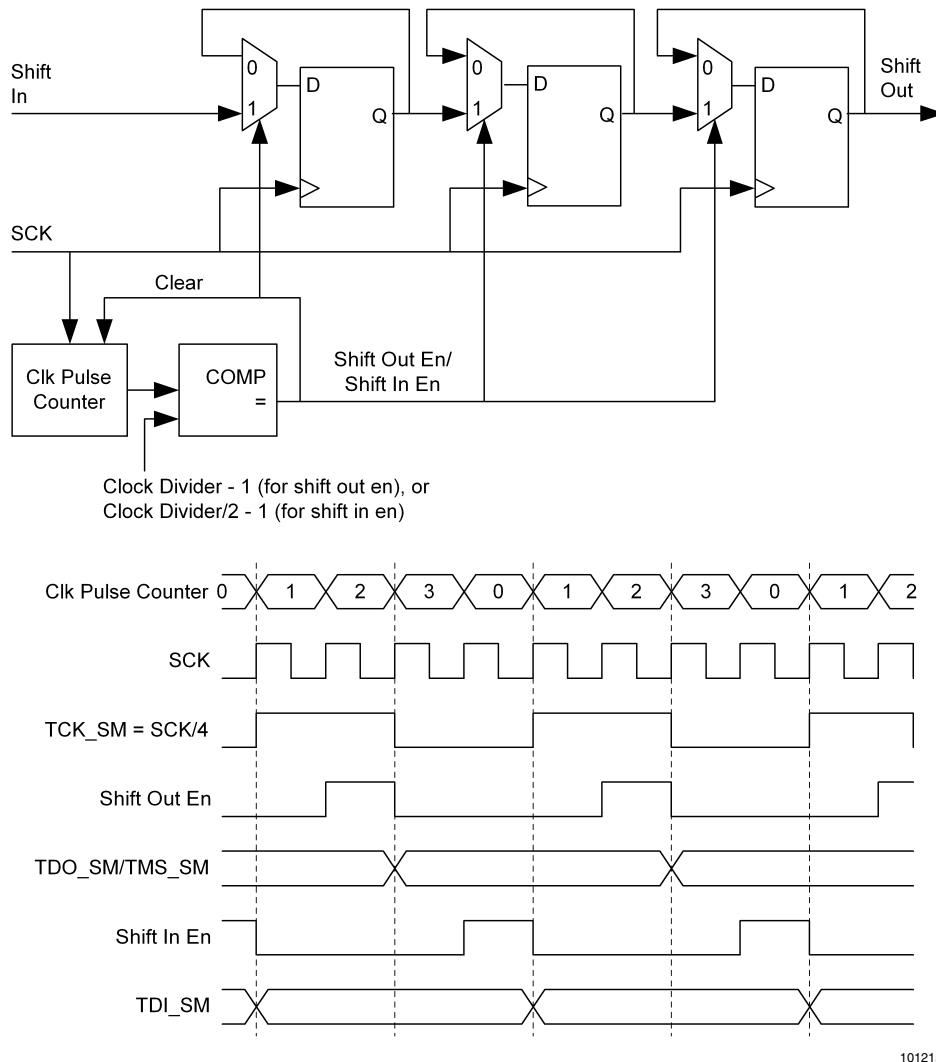

Shift register implementation is illustrated in *Figure 5*. Shift out enable for the TMS\_SM and TDO\_SM shifters is generated by comparing the clock pulse counter output to the clock divider - 1. Shift in enable for the TDI\_SM shifter is generated by comparing the clock pulse counter to programmable divisor/2 - 1. These enables are gated by the control signals from SSIC so that data are shifted out (TMS\_SM/TDO\_SM) or shifted in (TDI\_SM) only when necessary.

## Serial Scan Interface (Continued)

FIGURE 5. Shift Register Implementation and Timing

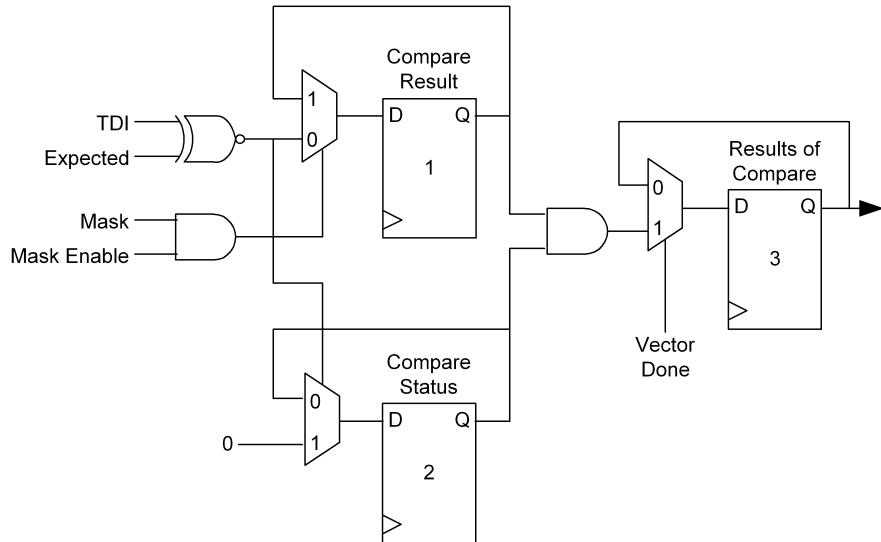

### COMPARATOR AND EXPECTED/MASK REGISTERS

The One Bit Comparator, when enabled, will compare TDI\_SM input with expected data. When the compare feature is enabled (pre-load only) the SSIC pre-fetches data into Expected and Mask registers from the address locations pertaining to the current vector being processed. The com-

parator will compare each bit on the TDI\_SM input with the corresponding bit from the expected register. If the mask feature is enabled, then the comparison is performed only on those bits that are not masked, i.e., on those bits whose mask is set to zero. Table 12 shows how Compare and Use Mask/Compare bits in the Macro Structure will be used.

TABLE 12. Compare and Use Mask/Compare Bit Descriptions

| Compare | Use Mask/Compare | Description          |

|---------|------------------|----------------------|

| 0       | 0                | Do Not Compare       |

| 0       | 1                | Compare with Mask    |

| 1       | 0                | Compare without Mask |

| 1       | 1                | Compare with Mask    |

Results of Compare bit (bit 15 of Status register) stores the comparison results in the status register. This bit defaults to fail (zero) and will be updated only after the current vector is processed. In the case of a single vector the Results of Compare bit will be set to one (pass) only if all the bits in the

scanned in vector match the expected vector. However, in the case of the sequencer only the results of final vector comparison will be taken into account.

Each vector within the sequencer is repeated until the vector repeat count is exhausted. However, the sequence is re-

## Serial Scan Interface (Continued)

peated until either the sequencer repeat count is exhausted or the compare passes and that the loop of the sequence is completed.

Figure 6 illustrates the compare logic.

10121525

**FIGURE 6. Compare Logic**

After reset and before every sequencer process, flip-flops 1 and 3 are initialized to zero while flip-flop 2 is set to 1. When the compare feature is enabled flip-flop 1 is continuously updated with the immediate comparison results (1 for pass and 0 for fail). Flip-flop 2 is reset to zero when a mismatch occurs and remains in this state for the remainder of the current vector processing. When the current vector is completely processed flip-flop 3 (Results of Compare register) will be updated with the current status.

### SERIAL SCAN INTERFACE CONTROLLER AND SCANBRIDGE CONTROLLER

The Serial Scan Interface Controller (SSIC) remains in the Idle state until new data are written to the Start register. When this event occurs the following operations are performed:

## Serial Scan Interface (Continued)

1. If the ScanBridge Support Initiate/Release bit was not set previously and is currently set in the Setup register, the SSIC initializes the ScanBridge Controller (SBC) to perform the following steps to set up all ScanBridges in the hierarchy.

- A. Determine the number of levels of ScanBridge support to be inserted (from the ScanBridge support structure)

- B. Sequence TMS\_SM so that all ScanBridges in the same level of hierarchy enter the SIR state, and then shift in the address (from the ScanBridge structure) to select a ScanBridge in the current level of hierarchy. The ScanBridge's TAP controller is then sequenced through the Update-IR state.

- C. Sequence TMS\_SM so that the selected ScanBridge's TAP controller enters the SIR state, then scan in the MODESEL instruction to put its mode register in the data path.

- D. Sequence the selected ScanBridge's TAP controller to enter the Shift-DR state and scan in the LSP contents (from the ScanBridge structure) into its mode register. The ScanBridge's TAP controller is then sequenced through the Update-DR state.

- E. Repeat Step 1c, but this time scan in the UNPARK instruction so that the LSP is inserted into the active scan chain.

- F. Sequence the ScanBridge's TAP controller to enter the RTI state (the LSP will not be unparked until its TAP controller enters RTI).

- G. Repeat Steps 1b through 1g to configure the ScanBridges in the remaining hierarchy levels. One set of pre-PAD and post-PAD bits is added to the patterns for each hierarchy level between the ScanMaster and the ScanBridge being configured. The PAD bits are used to bypass the intermediate levels of hierarchy.

- H. For the subsequent vectors, if the TAP Tracker enters the

- a. SDR state, the STA101 will add one pre-bit for the PAD register and one post-bit for the bypass register for each level of hierarchy.

- b. SIR state, the STA101 will add one pre-bit for the PAD register and eight post-bits for the ScanBridge instruction register for each level of hierarchy. The eight post-bits will be all ones because the ScanBridge will be forced into bypass mode.

- I. The PAD bits need to be stripped when loading a vector into TDI\_SM. This will be done by having a status flag to indicate whether the vector that is being scanned out has ScanBridge support or not. If the scanned-out vector has ScanBridge support, then the PAD bits will be stripped when the TAP Tracker enters the SDR or SIR states.

2. If the ScanBridge Support Initiate/Release bit was set previously and is currently reset in the Setup register, the SSIC will toggle TCK\_SM five times while TMS\_SM is held high. This will return all selected ScanBridges to the wait-for-address state and park the LSPs in the Test-Logic-Reset state. When the ScanBridge support is released the user should make sure that the Use Vector and Use Sequencer bits in the Start register are not set, such that, the SSIC will not start processing a vector or

the sequencer immediately after releasing the ScanBridge support. However, once the ScanBridge support is released the user may start processing a vector or the sequencer by writing to the Start register.

3. If the sequencer is enabled (the Use Sequencer bit in the Start register is one),

- A. Clear the Results of Compare bit and set the Using Sequencer bit in the Status register.

- B. Fetch the sequence repeat count.

- C. If the sequence repeat count is zero, the sequence is complete so reset the Using Sequencer bit and return to the Idle state, otherwise fetch the next vector number and its repeat count.

- D. If the vector number is zero, decrement the sequence repeat count and return to Step 3c. If the vector number is illegal, i.e., other than 001, 010, 011, or 100, decrement the sequence repeat count and return to Step 3c.

- E. If the vector repeat count is equal to zero, fetch the next vector number and its repeat count and go to Step 3d. If the repeat count is non-zero fetch the vector structure.

- F. If the pre-load bit in the vector structure is not set, reset the Using Sequencer bit and return to the Idle state.

4. If the sequencer is not enabled but a vector is enabled (the Use Vector bits in the Start register are non-zero), fetch the current vector structure and set the appropriate Using Vector bits in the Status register. If neither the sequencer nor a vector is enabled, return to the Idle state.

5. Fetch the Macro Structure to be used, set the vector/macro control bits and store the TMS\_SM bits in the Structure Control registers.

6. If the Pre-shift TCK\_SM Count is not zero, then enable TCK\_SM and drive TMS\_SM using the first seven bits of the macro until the Pre-shift TCK\_SM Count is zero. During pre-shift, TDO\_SM will be driven with its previous value.

7. If the macro type is State then,

- A. If the Macro Structure Bit 7 is enabled, set TMS\_SM to the bit 7 value of the macro structure and drive TDO\_SM with its previous value.

- B. If the Macro Structure Bit 8 is enabled, set TMS\_SM to the bit 8 value of the macro structure and drive TDO\_SM with its previous value and then go to Step 10.

- C. If the sequencer is being used then, decrement the vector repeat count and return to Step 3e. If a vector is being used, return to the Idle state.

8. If the macro type is BIST then,

- A. If the Macro Structure Bit 7 is enabled, set the count length, set TMS\_SM to the bit 7 value of the macro structure and drive TDO\_SM with the default value (Setup register bit 6) until the count length is zero.

- B. If the Macro Structure Bit 8 is enabled, set TMS\_SM to the bit 8 value of the macro structure and drive TDO\_SM with the default value (Setup register bit 6) and then go to Step 10.

- C. If the sequencer is being used then, decrement the vector repeat count and return to Step 3e. If a vector is being used, return to the Idle state.

## Serial Scan Interface (Continued)

9. If the macro type is Shift or Shift with Capture then,

- A. If the macro type is Shift with Capture, enable TDI capture.

- B. If the Sync Bit Support Enable bit is set, fetch sync bit count, set the count length, set TMS\_SM to the loop bit and drive the TDO\_SM high until sync bit count is zero.

- C. If the ScanBridge Support Initiate/Release bit is set, drive the TDO\_SM with pre- PAD bit (high) and while TMS\_SM remains set to the loop bit. Repeat for each level of hierarchy.

- D. If the Use Data/Instruction Header is enabled, fetch the header length and data, set the count length, and drive the TDO\_SM with header data until the header length is zero and while TMS\_SM remains set to the loop bit.

- E. If the Compare or Mask/Compare is set, enable the comparator.

- F. Set the vector count length, and drive the TDO\_SM with vector data until the count length is one and while TMS\_SM remains set to the loop bit. In the LotF mode if the count length is not zero and the TDO buffer is empty, then gate TCK\_SM until more data are available in the TDO buffer. When TCK\_SM is disabled TMS\_SM and TDO\_SM will be driven with their previous values.

- G. If the Use Data/Instruction Trailer is enabled, fetch the trailer length and data, set the count length, and drive TDO\_SM with trailer data until the trailer length is one and while TMS\_SM remains set to the loop bit.

- H. If the ScanBridge Support Initiate/Release bit is set:

- a. If the TAP tracker is in the Shift-IR state and the number of levels of hierarchy is greater than one, set the count length to eight, and drive TDO\_SM with post-PAD bits (all high) until the count length is zero for each level of hierarchy and while TMS\_SM remains set to the loop bit.

### MODE REGISTER WRITE TO VECTOR/SEQUENCER START

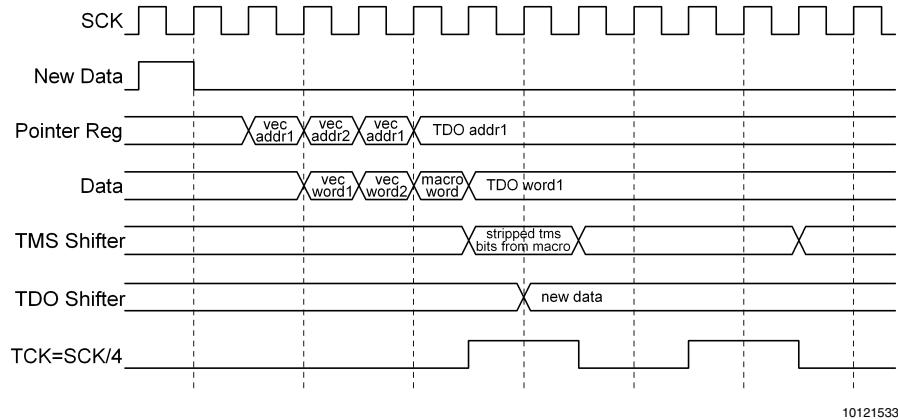

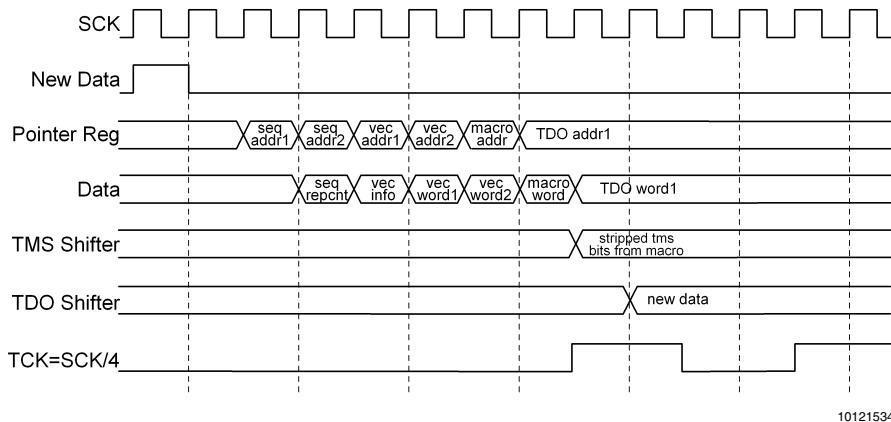

FIGURE 7. Timing from Mode Register Write to Vector Start

Figure 7 shows the timing from the processor write to the start of vector processing, whereas Figure 8 shows the

- b. If the TAP tracker is in the Shift-DR state and the number of levels of hierarchy is greater than one, drive TDO\_SM with a post-PAD bit (high) for each level of hierarchy and while TMS\_SM remains set to the loop bit.

- c. For the final level of hierarchy or if there is only one level of hierarchy, and if the TAP tracker is in the Shift-IR state, set the count length to eight, and drive TDO\_SM with post-PAD bits (all high) until the count length is one and while TMS\_SM remains set to the loop bit.

- I. If the Sync Bit Support Enable is set, fetch sync bit count, set the count length, and drive the TDO\_SM high until sync bit count is one and while TMS\_SM remains set to the loop bit.

- J. Set TMS\_SM to the bit 8 of the TMS\_SM Macro Structure sequence and drive TDO\_SM with the final vector bit or trailer bit or post-PAD bit or sync bit. After shifting out the final vector bit, disable the comparator and register the comparison results.

10. If the Post-shift TCK\_SM Count is not zero, then enable TCK\_SM and drive TMS\_SM using the last seven bits of the macro until the Post-shift TCK\_SM Count is zero.

11. If the Sequencer is being used,

- A. Decrement the sequence repeat count and return to Step 3c if the Compare or Mask/Compare is enabled and the results of compare is a fail.

- B. Decrement the vector repeat count and return to Step 3e if the if the Compare or Mask/Compare is enabled and the results of compare is a pass.

- C. Decrement the vector repeat count and return to Step 3e if the Compare or Mask/ Compare is not enabled.

12. If the Vector is being used return to the Idle state.

timing from the processor write to the start of sequencer processing. A processor write to the Start registers is indi-

## Serial Scan Interface (Continued)