## QT2225PRKD Data Sheet

# Dual Port Serial 10Gbps-to-XAUI Transceiver with Adaptive EDC May 4, 2009

#### **Features**

- 10Gbps Operation: 10GbE LAN/WAN & 10GFC

- Advanced EDC Engine with Auto Tap Weight Adjustment & Advanced Tracking

- 10G High-Speed Interface with Integrated RX AGC, Adjustable TX Amplitude with Pre-Emphasis, and I/O Polarity Swap

- XAUI Interface with Selectable Lane Ordering, Polarity Swap, Input Equalization, Output Pre-Emphasis, Amplitude Adjust

- Ethernet Clock recovery for Synchronous Ethernet applications (125MHz and 156.25MHz)

- Integrated Loopback and Line Timing Functionality

- Integrated BER Tester, and PRBS, Packet, and Programmable Pattern Generation and Checking

- Tri-State Push/Pull 25MHz MDIO Operation with Two Additional I2C Compatible Interfaces for EEPROM External Device Configuration and External Module Status/ Control including NVR

- Compliant to Applicable IEEE & INCITS Specs

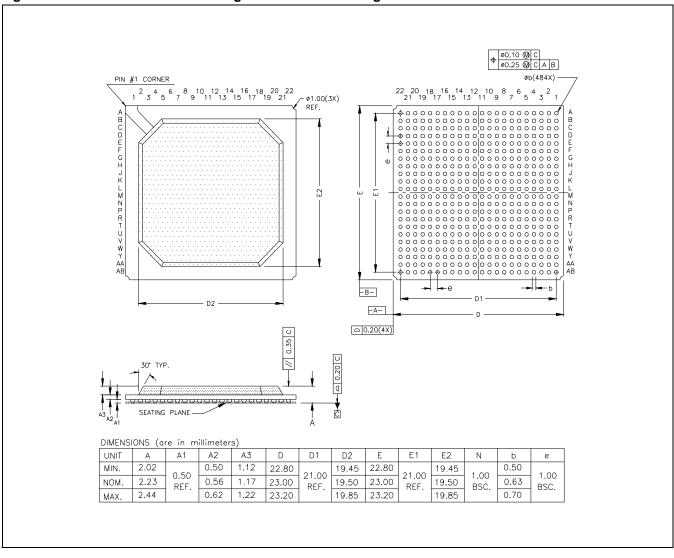

- 23mm x 23mm, 1mm Ball Pitch, BGA Package with Green/ RoHS Compliant Lead Free Option

#### **Backplane Specific Features**

- 1000BASE-KX and 10GBASE-KR Support

- Auto-Negotiation & In-Band FEC Capability

- KR Training for Channel Optimization

#### SFP+ Specific Features

- SFI-to-XAUI Operation for SFP+ Modules Supporting Limiting & Linear (-1 Only) Applications

- 1GE Operation for SFP Applications

- DFE/FFE Adaptive EQ for Pre/Post/Symmetric Stressors Compliant to IEEE 802.3aq

- Passive Direct Attach SFP+ Cable Support (Twinax)

#### XFP Module Specific Features

- Low Power XFI-to-XAUI Operation

- WIS (10GBASE-W) SONET/SDH Support with Overhead DCC Channel Available

- Automatic Line Timing Capability for Synchronous Operation in SONET Networks

## **Applications**

#### QT2225:

- Backplane 10GBASE-KR /1000BASE-KX Support

- Hostboard Termination for SFP+/SFP Limiting Modules including 10GBASE-SR, -LR & 1000BASE-X and Passive Direct Attach SFP+ Cable

- Hostboard Termination for XFP Modules including 10GBASE-R & -W Protocols

#### QT2225-1:

- Hostboard Termination for SFP+/SFP Limiting & Linear Modules: 10GBASE-LRM/SR/LR, 1000BASE-X and Passive Direct Attach SFP+ Cable

- On-board PHY inside XENPAK/X2 Modules for 10GBASE-LRM, -R, & -W Protocols

## **General Description**

The QT2225 is a fully integrated dual 9.95-10.52 Gbps transceiver with fully adaptive Electronic Dispersion Compensation (EDC) capabilities. The device provides a high performance interface between a MAC or switch device and copper media including Twinax Cable and 10GBASE-KR backplanes. The data rate is switchable to 1.25 Gbps, allowing dual 1000BASE-KX / 10GBASE-KR support on a single backplane design using Auto-negotiation for rate selection.

It can also interface to optical media including SFP+, SFP and XFP modules or reside inside a XENPAK or X2 module. When designing for SFP+ applications, customers can generate one dual-rate design that supports SFP+ modules (10GBASE-R) and SFP modules (1000BASE-X), as well as Twinax cable, providing maximum medium flexibility.

In the receive direction the device uses a sophisticated EDC engine that continuously adapts to the channel characteristics providing an optimum level of performance regardless of environmental conditions. The QT2225-1 was designed to exceed the performance specified in the 10GBASE-LRM Standard.

In the transmit direction, the 10Gbps driver utilizes signal equalization to compensate for degradation due to copper traces and connectors in the signal path.

The QT2225 includes two standard two-wire interfaces for each port (plus a single MDIO) for auto/manual initialization, firmware loading, NVR & optical module status/control.

## **Firmware**

The PHY is provided with a firmware program that runs on the built-in 8051 microprocessor. The firmware configures the PHY for different applications and works in conjunction with the silicon to provide the features and performance specified in this document.

Please consult the AMCC website for access to the production firmware.

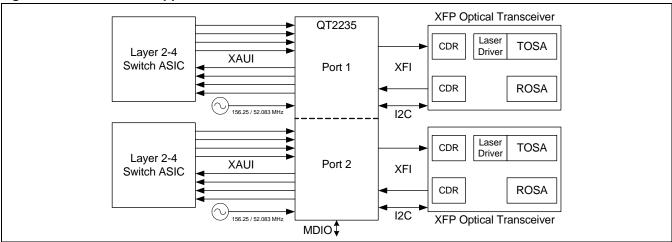

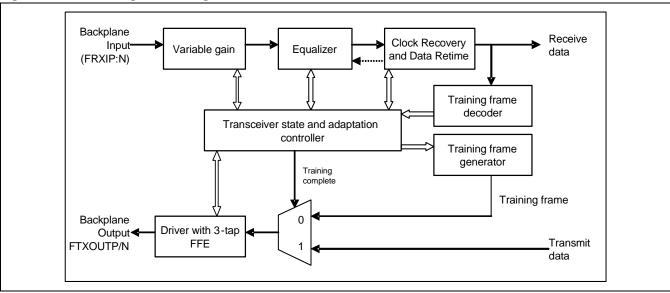

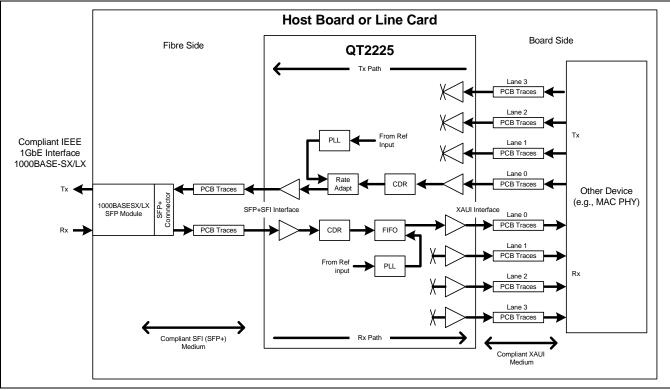

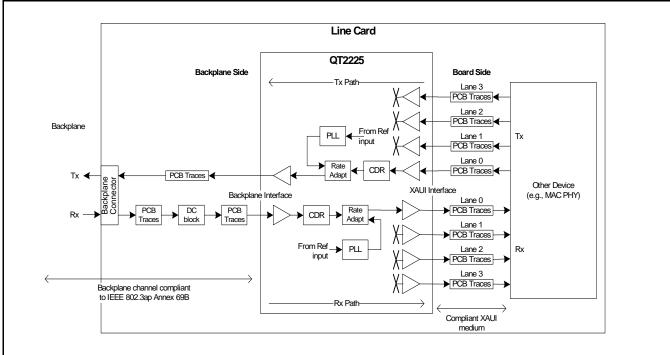

Figure 1: System Block Diagram

## **NOTICE: THIS IS A "RELEASED" SPECIFICATION**

This document is a RELEASED specification for a device under development by AMCC:

- Specifications in this document are not guaranteed to be the latest and are subject to change

- This data sheet may be superseded by a future revision. Always confirm with AMCC that you are using the latest version.

- Please consult and register for documentation updates from AMCC's external website via the AMCC's MyProduct subscription updates page: https://www.amcc.com/MyAMCC/jsp/secure/alertSubscriptions/my\_product\_list.jsp.

| Data Sheet Type | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONCEPT         | Concept Specifications are made available for products ideas that are being marketed to obtain customer feedback.                                                                                                                                                                                                                                                                                                                                                 |

| ADVANCE         | Advance Specifications are made available for products that are in the engineering development cycle. General samples are not yet available for these products and the specifications, including pin lists and functional descriptions, may change at any time WITHOUT NOTICE.                                                                                                                                                                                    |

| PRELIMINARY     | Preliminary Specifications are made available for products that have been released for general sampling by AMCC (known as Sample Release (SR)). The SR milestone indicates that device samples and evaluation kits may made available upon request. Preliminary device characterization and evaluation has also been completed by AMCC. Known device errata's will be published and dispositioned upon SR. Device specifications may still change WITHOUT NOTICE. |

| RELEASED        | Released Specifications are made available for products that have passed AMCC's Production and Qualification Testing. Although Released Specifications are expected to never change, occasional clean-up changes may be made throughout the remaining product life cycle. All future specification changes that negatively impact a customer are processed through AMCC's Product Change Notification system.                                                     |

## **Table of Contents**

| FEATURES                            |    |

|-------------------------------------|----|

| APPLICATIONS                        |    |

| GENERAL DESCRIPTION                 |    |

| FIRMWARE                            |    |

| DATA SHEET TYPE                     |    |

| TABLE OF CONTENTS                   | 3  |

| LIST OF FIGURES                     | 6  |

| LIST OF TABLES                      | g  |

| QT2225 OVERVIEW                     | 11 |

| FUNCTIONAL BLOCK DIAGRAM            |    |

| FUNCTIONAL DESCRIPTION              |    |

| Transmit Data Path: XAUI Interface  |    |

| Transmit XGXS                       |    |

| Transmit PCS                        |    |

| Transmit 10G Driver                 |    |

| Receive Data Path: 10G Interface    | 17 |

| Receive PCS                         | 18 |

| Receive XGXS                        | 18 |

| HIGH SPEED INTERFACES               | 19 |

| XAUI Interface                      | 19 |

| 10Gbps Interface                    | 23 |

| EDC ENGINE                          | 26 |

| Overview                            | 26 |

| Linear Equalizer                    | 27 |

| Automatic Gain Control              | 27 |

| Adaptive Equalizer                  | 27 |

| KR INTERFACE                        | 28 |

| 10GBASE-KR Receiver                 | 28 |

| KR Transmitter                      | 28 |

| Auto-Negotiation                    | 28 |

| MDIO Access                         | 28 |

| Link Codeword Format                | 30 |

| Clause 72 Link Training             | 33 |

| 10GBASE-KR Link Control Algorithms  | 36 |

| KR Frame Lock State Machine         | 37 |

| KR Training State Machine           |    |

| KR Coefficient Update State Diagram | 39 |

| FEC ENCODING/DECODING               | 40 |

| Overview                            |    |

| Properties                          |    |

| FEC Transmit Encoder                | 40 |

| FEC Receive                                     | 44 |

|-------------------------------------------------|----|

| FEC MDIO Register Mapping                       | 46 |

| 10GBASE-KR Considerations                       | 46 |

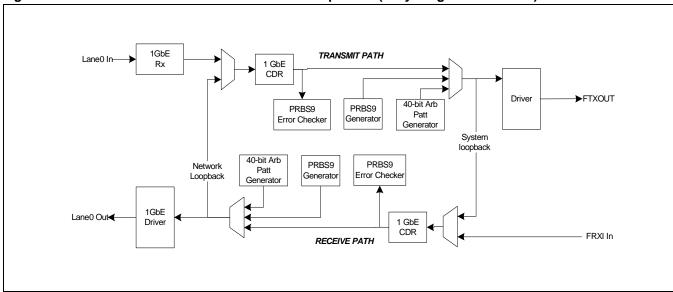

| 1GE MODE                                        | 47 |

| Overview                                        | 47 |

| Features                                        | 50 |

| 1GE Test Patterns and Loopbacks                 | 50 |

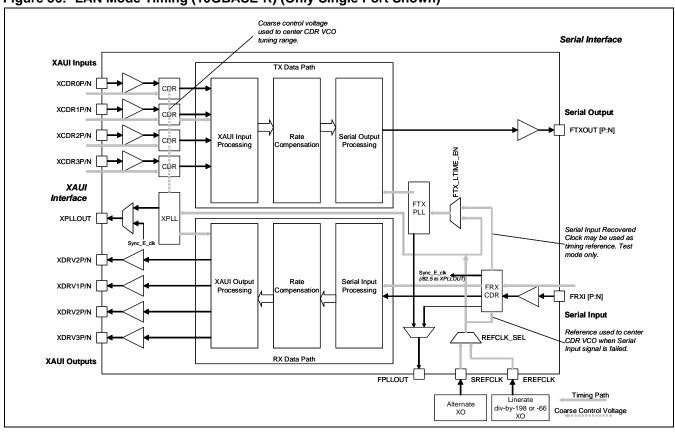

| 10G MODE DATAPATH CLOCKING                      | 54 |

| Datapath clocking MDIO Registers                | 54 |

| LAN Application Timing Modes                    |    |

| WAN Application Timing Modes (10GBASE-W Mode)   |    |

| WIS MODE                                        | 66 |

| Extended WIS Features                           | 66 |

| CONTROL AND STATUS PINS DESCRIPTION             | 68 |

| I/O Polarity and Monitoring                     |    |

| Low-Speed Output Pins                           |    |

| LINK ALARM STATUS INTERRUPT PIN (LASI)          |    |

| RX ALARM                                        |    |

| TX ALARM                                        |    |

| WIS Alarms                                      |    |

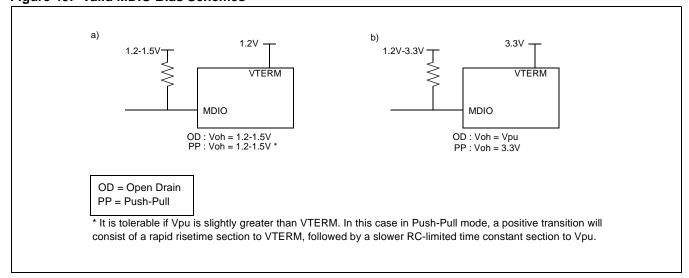

| EMBEDDED MICRO-CONTROLLER                       |    |

| Micro-controller Architecture                   |    |

| Memories                                        |    |

| Microcontroller I/O                             |    |

| Program Execution                               |    |

| Program Memory Location                         |    |

| MANAGEMENT DATA I/O (MDIO) INTERFACE            |    |

| MDIO Bus Speed                                  |    |

| Clock Signal (MDC)                              |    |

| Data Signal (MDIO)                              |    |

| MDIO Management Frame Format                    |    |

| Preamble Field (PRE)                            | 88 |

| Start Field (ST)                                |    |

| Operation Code Field (OP)                       | 88 |

| Port Address Field (PRTAD)                      | 88 |

| Device Address Field (DEV_ADDR)                 | 88 |

| Turnaround Field (TA)                           | 88 |

| Register Data/Address Field (REG_DATA/REG_ADDR) | 88 |

| Idle Field (IDLE)                               | 88 |

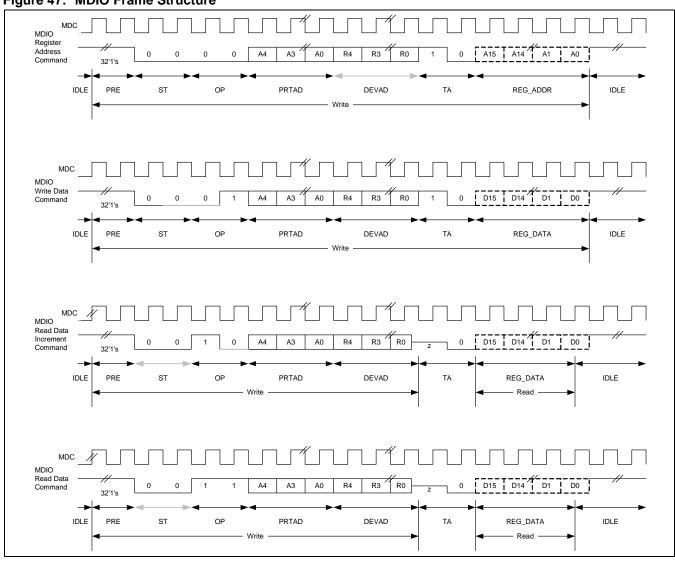

| MDIO Timing Relationship to MDC                 | 88 |

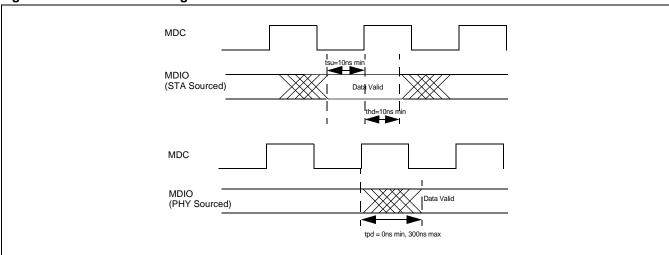

| Open Drain Operation                            | 88 |

| Push-Pull Operation                             |    |

| Voh Voltage on VTERM                            |    |

| MDIO Configuration                              | 90 |

| XFP/SFP+ Module Access through MDIO                           | 90  |

|---------------------------------------------------------------|-----|

| TWO WIRE INTERFACES                                           | 91  |

| Two Wire Data Transfer Protocol                               | 91  |

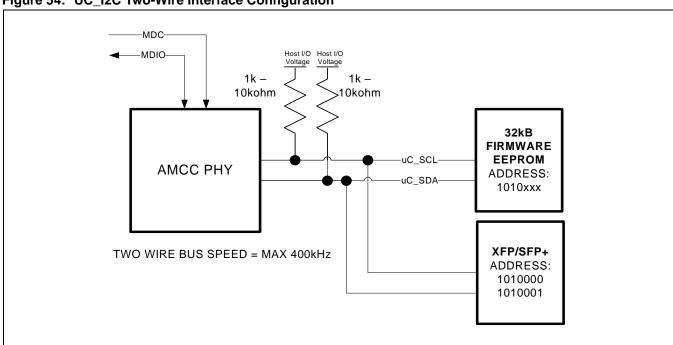

| UC_I2C Microcontroller Two Wire Interface                     | 93  |

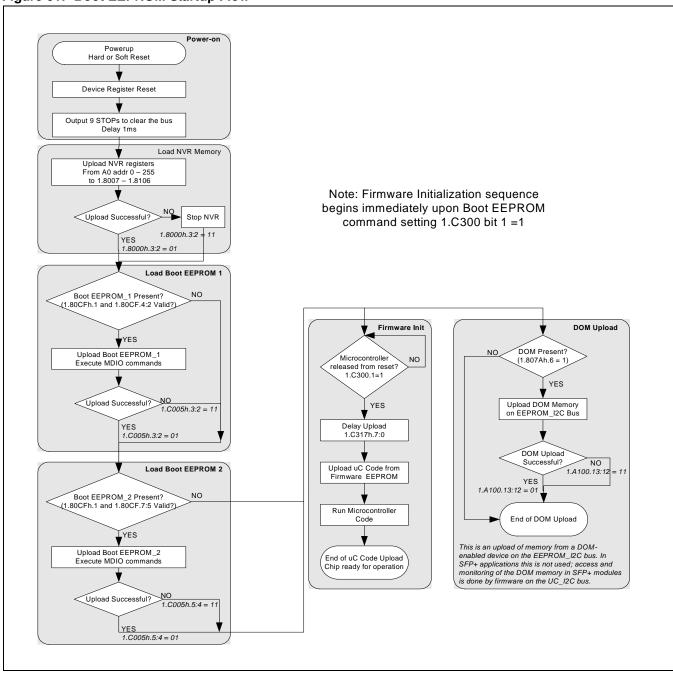

| Firmware EEPROM                                               | 94  |

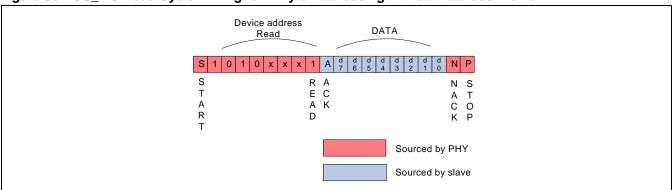

| XFP/SFP/SFP+ Module Two-Wire Access                           | 94  |

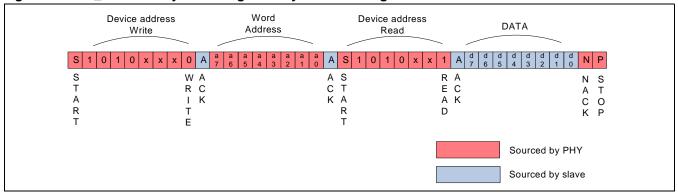

| UC_I2C Bus One-Byte Addressing                                | 95  |

| UC_I2C Bus Two-byte Addressing                                | 97  |

| EEPROM_I2C Two Wire Interface                                 |     |

| Boot EEPROM: MDIO Register Configuration from External EEPROM | 99  |

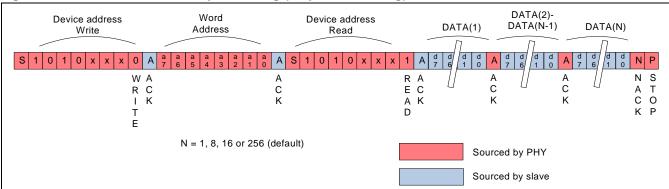

| EEPROM_I2C One-Byte Addressing                                | 102 |

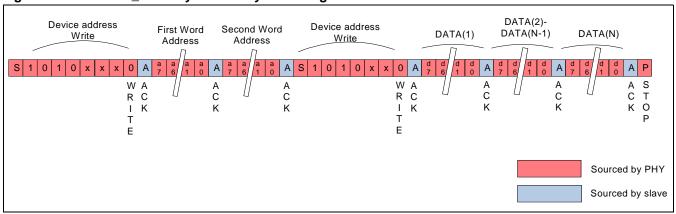

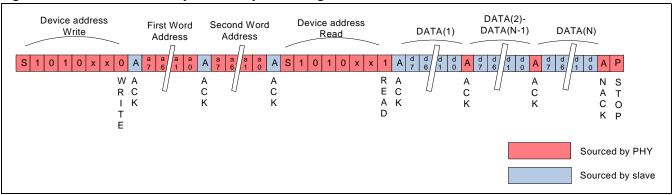

| EEPROM_I2C Two-byte Addressing                                |     |

| EEPROM_I2C Slave Mode for Register Configuration              |     |

| Addressing Mode                                               |     |

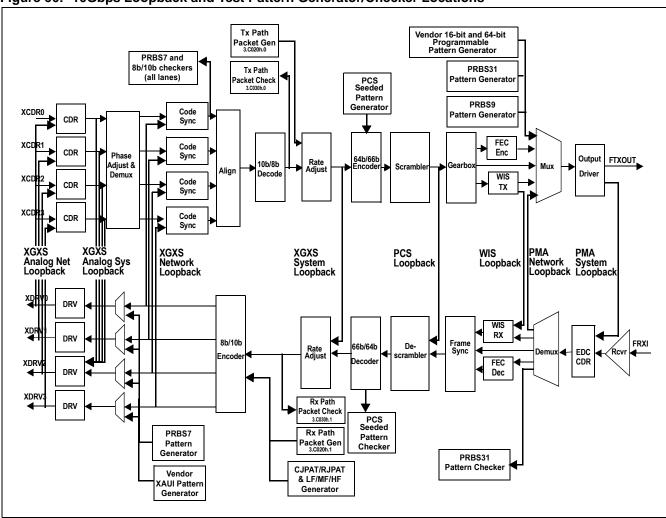

| 10GBPS DIAGNOSTIC AND TEST FEATURES                           | 107 |

| Loopback Modes                                                | 107 |

| XAUI Interface Test Features                                  | 110 |

| PCS/PMA Data Path Test Features                               | 111 |

| WIS Test Features                                             |     |

| Ethernet Packet Generator/Checker                             |     |

| Disabling the Idle Decode Process                             |     |

| Test Access Port and Boundary Scan                            | 117 |

| BALL ASSIGNMENT AND DESCRIPTION                               | 120 |

| Ball Arrangement                                              | 120 |

| BALL MAP ARRANGEMENT                                          | 127 |

| MECHANICAL SPECIFICATIONS                                     | 128 |

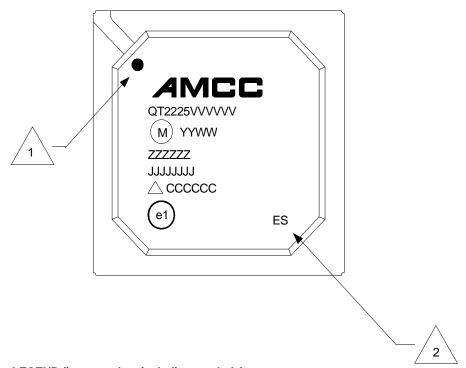

| PACKAGE MARKING DRAWING                                       | 129 |

| PERFORMANCE SPECIFICATIONS                                    | 130 |

| ELECTRICAL SPECIFICATIONS                                     | 158 |

| SFP+ LAYOUT RECOMMENDATIONS                                   |     |

| POWER SUPPLY SEQUENCING                                       |     |

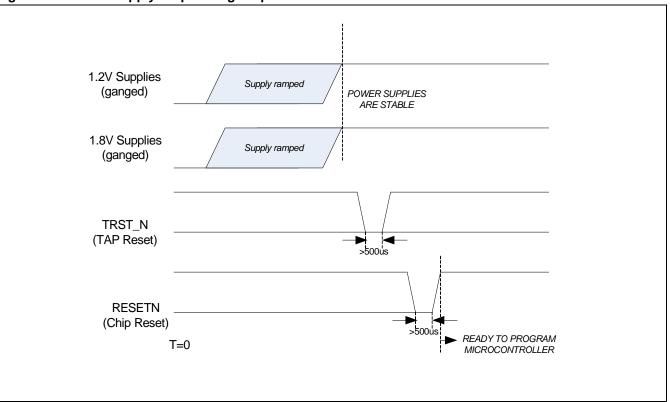

| Chip Reset Timing                                             | 171 |

| Managing Multi-Port Designs                                   |     |

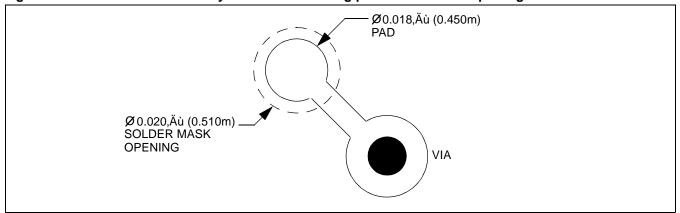

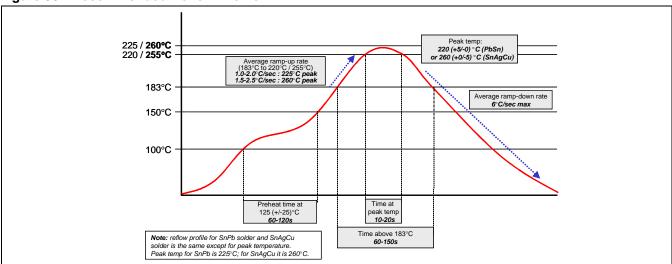

| RECOMMENDED LANDING PATTERN AND REFLOW                        |     |

| PCB Layout Recommendations                                    |     |

| Baking Instructions                                           |     |

| Thermal Reflow Profile                                        |     |

| REVISION HISTORY                                              |     |

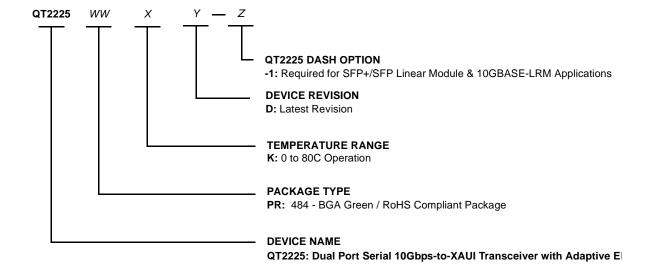

| ORDERING INFORMATION                                          | 175 |

## **List of Figures**

| Figure 1: System Block Diagram                                                                   | 1  |

|--------------------------------------------------------------------------------------------------|----|

| Figure 2: QT2225-1 SFP+ Application                                                              | 12 |

| Figure 3: QT2225-1 1GbE SFP Application                                                          | 12 |

| Figure 4: QT2225 XFP Application                                                                 | 13 |

| Figure 5: QT2225 10GBASE-KR Backplane Application                                                | 13 |

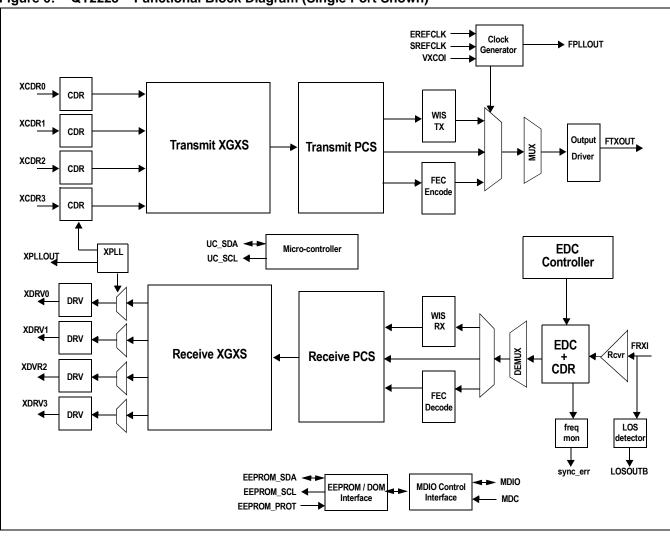

| Figure 6: QT2225 – Functional Block Diagram (Single Port Shown)                                  | 14 |

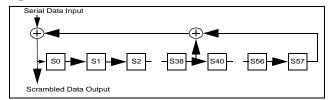

| Figure 7: Transmit Scrambler                                                                     | 16 |

| Figure 8: Receiver Input                                                                         | 17 |

| Figure 9: Receive Descrambler                                                                    |    |

| Figure 10: XAUI XDRV Pre-Emphasis                                                                | 20 |

| Figure 11: 10G Transmit Driver Modes, Block Diagrams, and Example Differential Waveforms         | 25 |

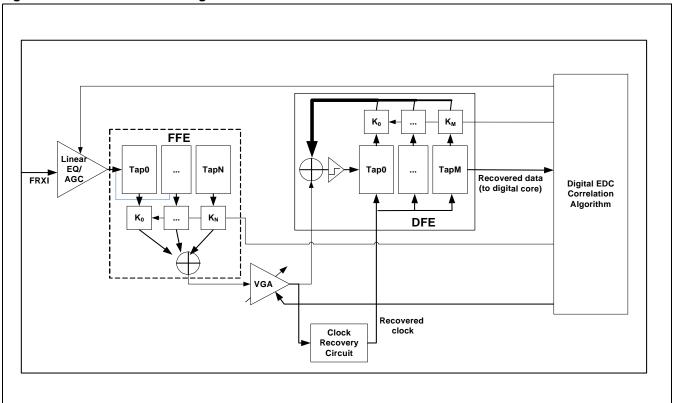

| Figure 12: Data Path Block Diagram                                                               | 26 |

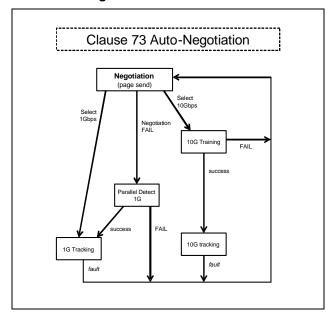

| Figure 13: Simplified Auto-Negotiation State Diagram                                             | 28 |

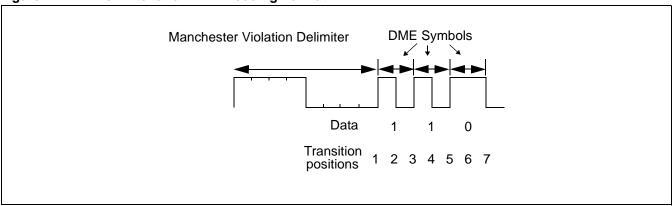

| Figure 14: MV Delimiter and DME Encoding Format                                                  | 29 |

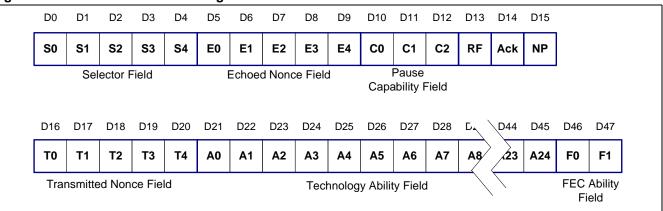

| Figure 15: Link Codeword Base Page Format                                                        | 30 |

| Figure 16: Selector Field Encoding                                                               | 30 |

| Figure 17: Technology Ability Field Encoding                                                     | 31 |

| Figure 18: FEC Capability Field Encoding                                                         | 31 |

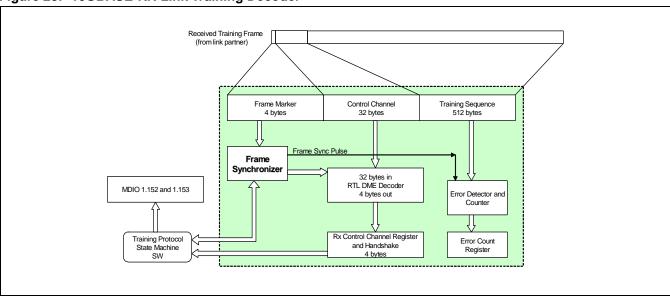

| Figure 19: KR Training Block Diagram                                                             | 33 |

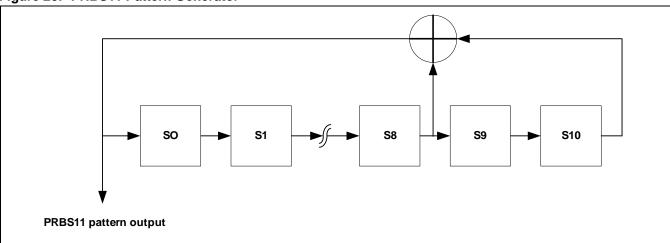

| Figure 20: PRBS11 Pattern Generator                                                              | 34 |

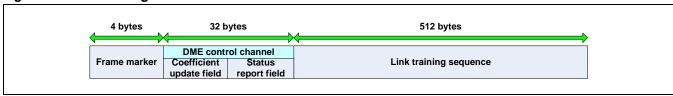

| Figure 21: KR Training Frame                                                                     | 34 |

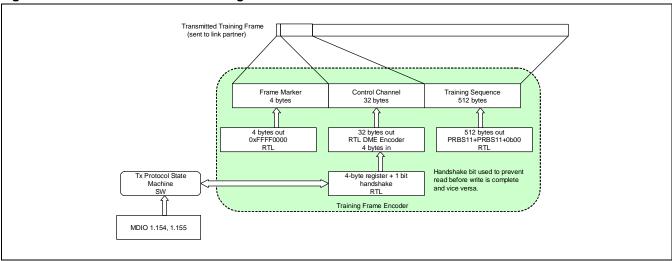

| Figure 22: 10GBASE-KR Link Training Encoder                                                      | 36 |

| Figure 23: 10GBASE-KR Link Training Decoder                                                      | 36 |

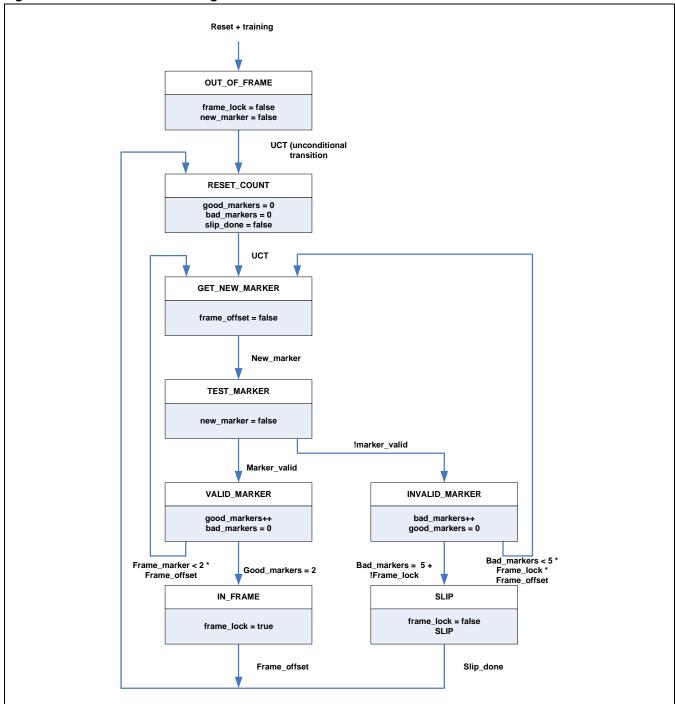

| Figure 24: Frame Lock State Diagram                                                              | 37 |

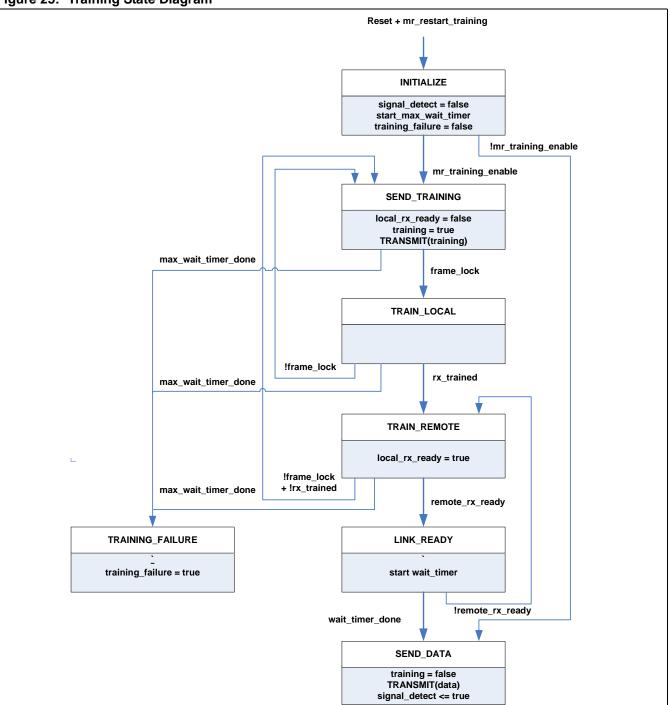

| Figure 25: Training State Diagram                                                                | 38 |

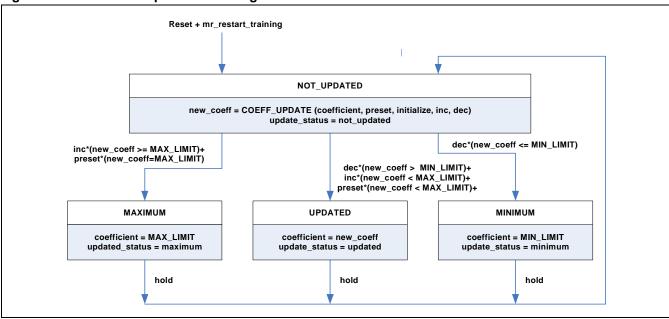

| Figure 26: Coefficient Update State Diagram                                                      | 39 |

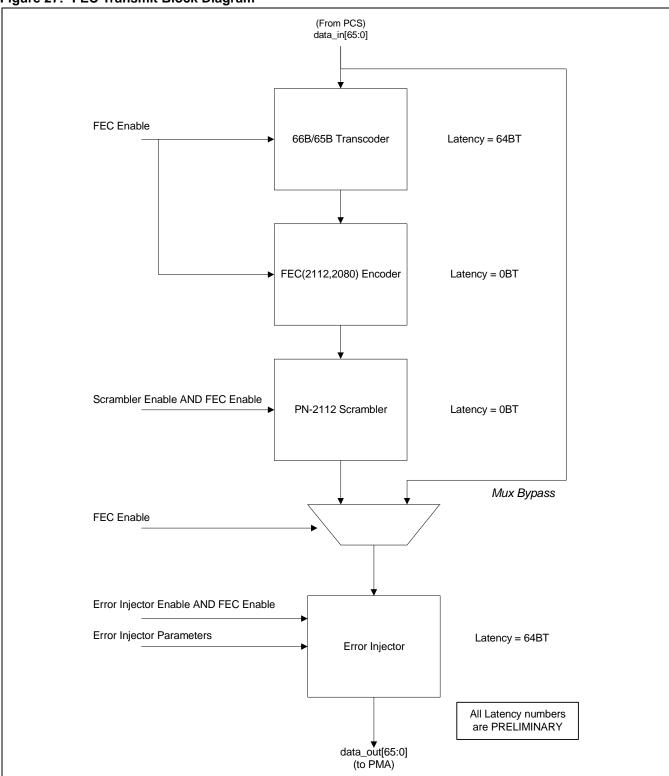

| Figure 27: FEC Transmit Block Diagram                                                            | 41 |

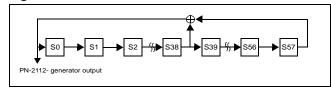

| Figure 28: PN-2112 Scrambler                                                                     |    |

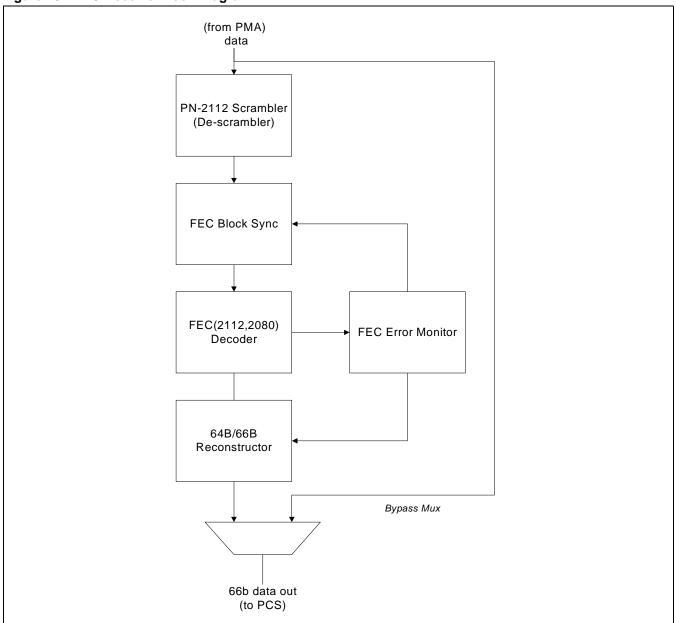

| Figure 29: FEC Receive Block Diagram                                                             | 44 |

| Figure 30: SFP+ Board with 1GbE SFP Module Application: Rate Adaptation Mode (Single Port Shown) | 48 |

| Figure 31: Backplane 1GE Application with Rate Adaptation on RX Path (Only Single Port Shown)    | 49 |

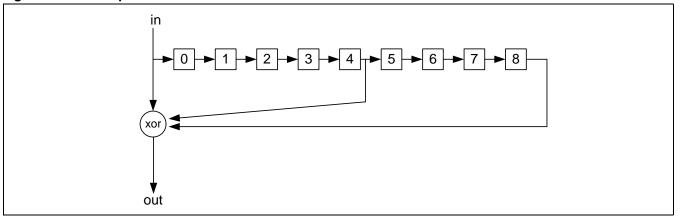

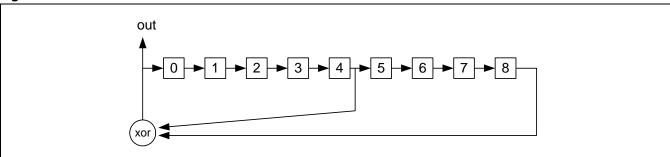

| Figure 32: 1.25Gbps PRBS9 Pattern Checker                                                        | 51 |

| Figure 33: 1.25Gbps Transmit Path 40-bit Pattern Output Order                                    | 51 |

| Figure 34: 1.25Gbps Receive Path 40-bit Pattern Output Order                                     | 52 |

| Figure 35: Location of 1.25G Test Patterns and Loopbacks (Only Single Port Shown)                | 53 |

| Figure 36: LAN Mode Timing (10GBASE-R) (Only Single Port Shown)                                  | 55 |

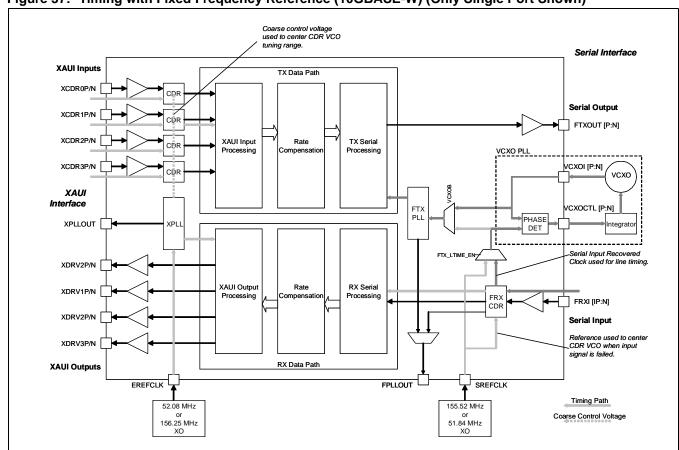

| Figure 37: Timing with Fixed Frequency Reference (10GBASE-W) (Only Single Port Shown)            | 57 |

| Figure 38: Timing without Fixed Frequency Reference (10GBASE-W) (Only Single Port Shown)         | 58 |

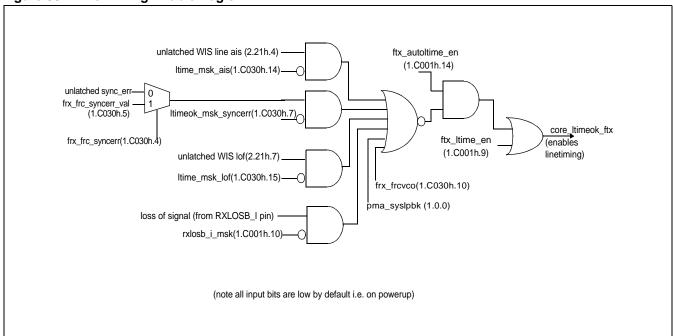

| Figure 39: Line Timing Enable Logic                                                              | 60 |

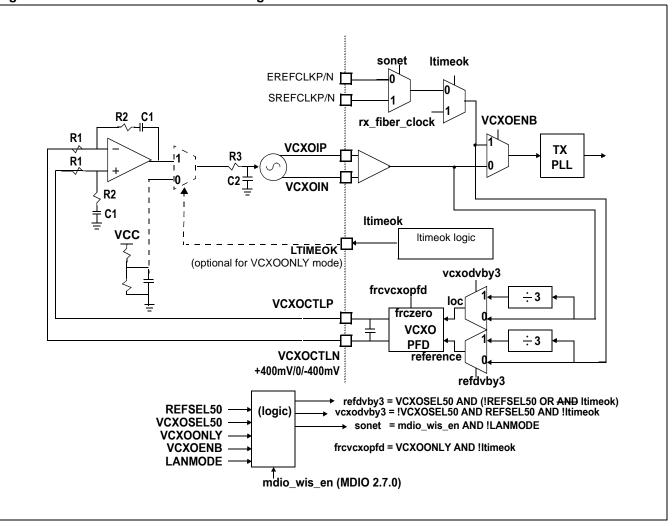

| Figure 40: VCXO PLL Interface block diagram                                                      | 62 |

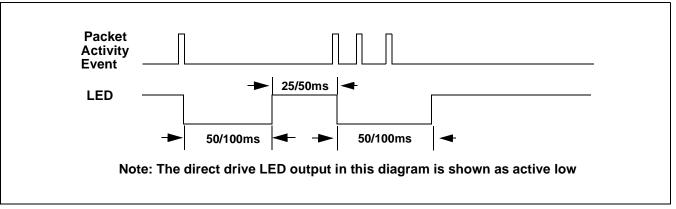

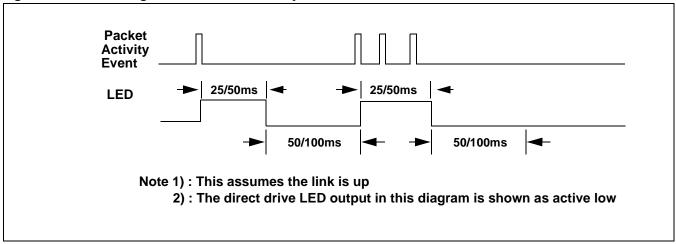

| Figure 41: LED Timing for 'Activity Only' Mode                                                | . 72 |

|-----------------------------------------------------------------------------------------------|------|

| Figure 42: LED Timing for 'Link Status/Activity' Mode                                         | . 72 |

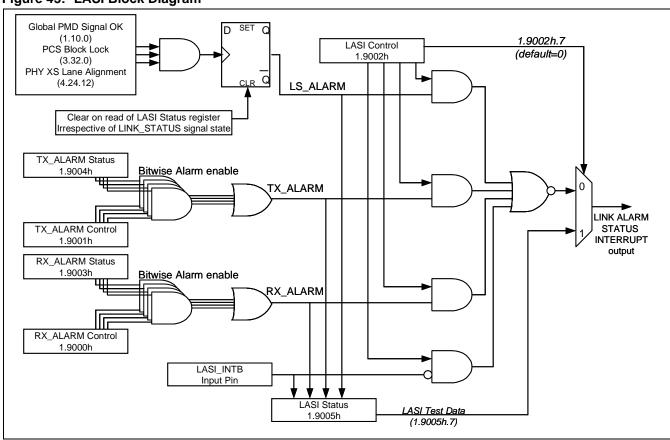

| Figure 43: LASI Block Diagram                                                                 | . 73 |

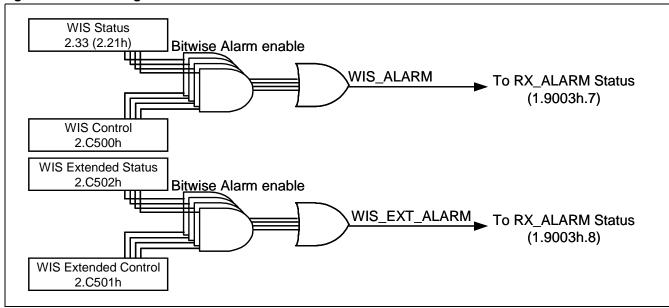

| Figure 44: Block diagram of WIS Alarms                                                        | . 79 |

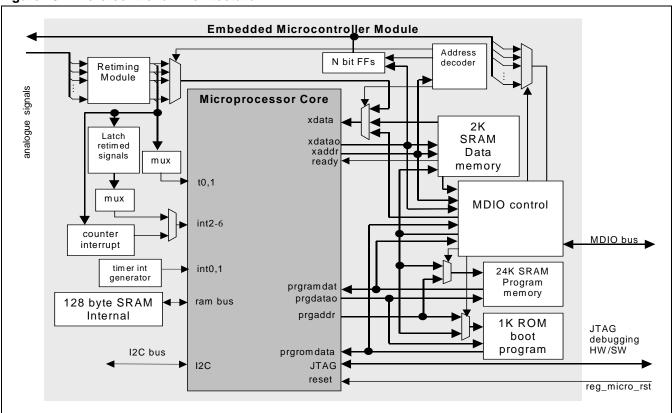

| Figure 45: Micro-controller Architecture                                                      | . 82 |

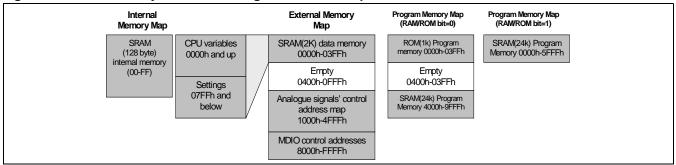

| Figure 46: 8051 Memory and Control Signal Address Map                                         | . 83 |

| Figure 47: MDIO Frame Structure                                                               | . 87 |

| Figure 48: MDIO/MDC Timing                                                                    | . 89 |

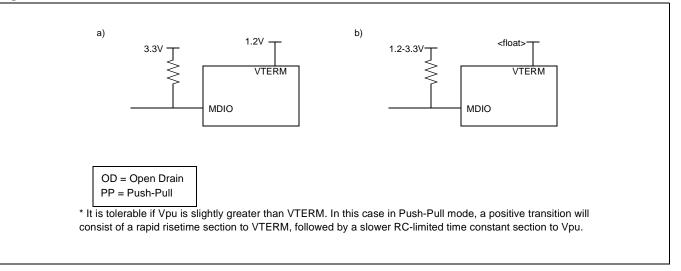

| Figure 49: Valid MDIO Bias Schemes                                                            | . 89 |

| Figure 50: Invalid MDIO Bias Schemes                                                          | . 90 |

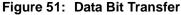

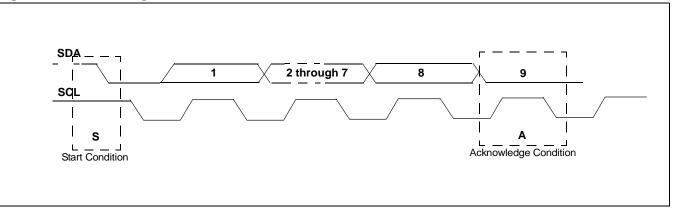

| Figure 51: Data Bit Transfer                                                                  | . 91 |

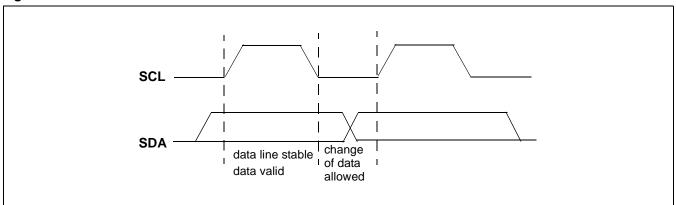

| Figure 52: Start and Stop Conditions                                                          | . 91 |

| Figure 53: Acknowledge Condition                                                              | . 92 |

| Figure 54: UC_I2C Two-Wire Interface Configuration                                            | . 93 |

| Figure 55: UC_I2C Read Cycle Timing for 1-Byte Addressing with Address Frame                  | . 95 |

| Figure 56: UC_I2C Read Cycle Timing for 1-Byte Addressing without Address Frame               | . 95 |

| Figure 57: UC_I2C Write Cycle Timing for 1-Byte Addressing                                    | . 96 |

| Figure 58: UC_I2C Write Cycle Timing for 2-Byte Addressing                                    | . 97 |

| Figure 59: UC_I2C Read Cycle Timing for 2-Byte Addressing                                     | . 97 |

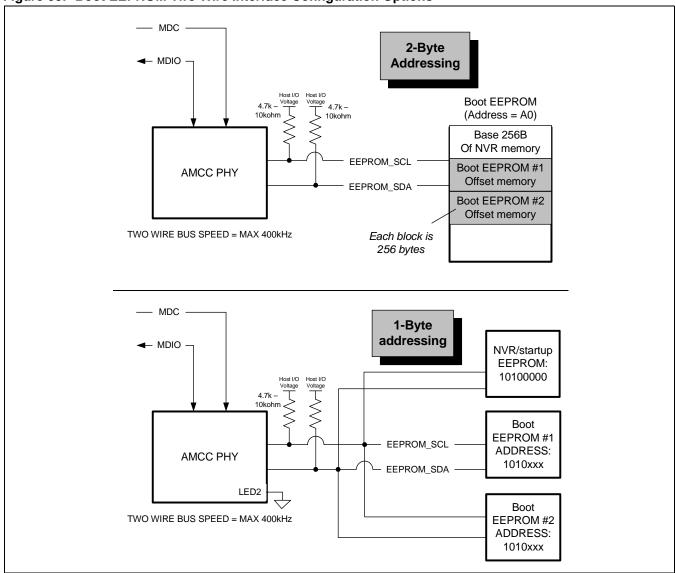

| Figure 60: Boot EEPROM Two Wire Interface Configuration Options                               | . 98 |

| Figure 61: Boot EEPROM Startup Flow                                                           |      |

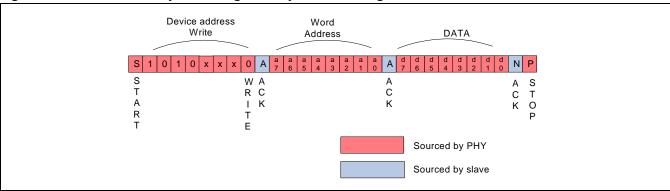

| Figure 62: EEPROM_I2C Read Cycle Timing (1-byte addressing)                                   | 102  |

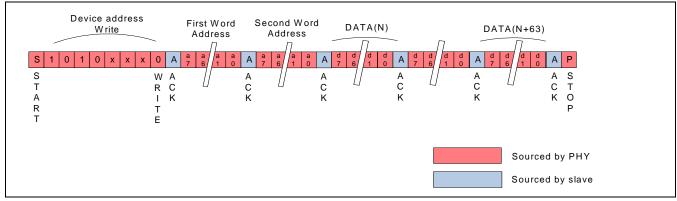

| Figure 63: EEPROM_I2C 2-Byte Write Cycle Timing                                               | 104  |

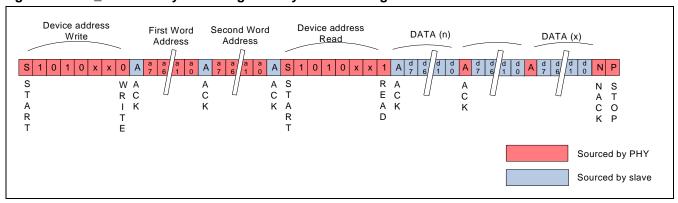

| Figure 64: EEPROM_I2C 2-Byte Read Cycle Timing                                                | 104  |

| Figure 65: MDIO Register Indirect Access Memory Mapping for Two-Wire Access                   | 106  |

| Figure 66: 10Gbps Loopback and Test Pattern Generator/Checker Locations                       |      |

| Figure 67: PRBS9 Pattern Generator                                                            |      |

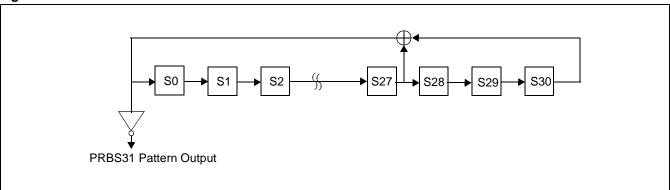

| Figure 68: PRBS31 Pattern Generator                                                           | .112 |

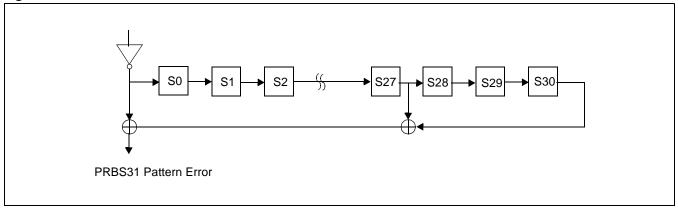

| Figure 69: PRBS31 Pattern Checker                                                             | .113 |

| Figure 70: QT2225 Ball Arrangement (TOP VIEW, THROUGH THE PACKAGE)                            | 127  |

| Figure 71: QT2225 – 484 BGA Package Mechanical Drawing                                        |      |

| Figure 72: QT2225 – 484 BGA Package Marking Drawing                                           | 129  |

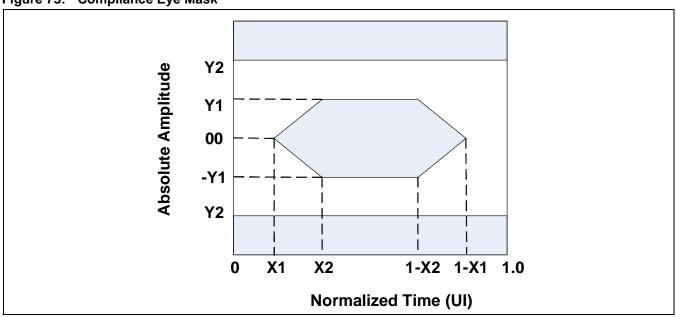

| Figure 73: Compliance Eye Mask                                                                | 136  |

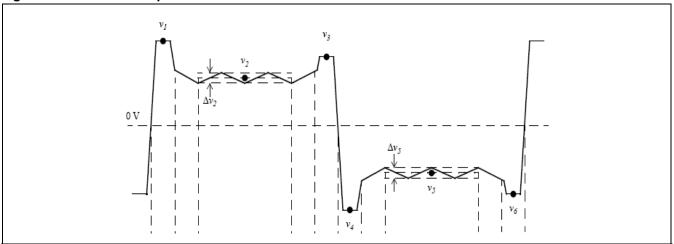

| Figure 74: 10G KR Backplane Waveform Definition                                               | 137  |

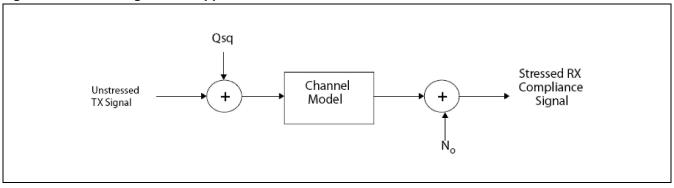

| Figure 75: Block Diagram of Copper Stressor Noise Model                                       | 141  |

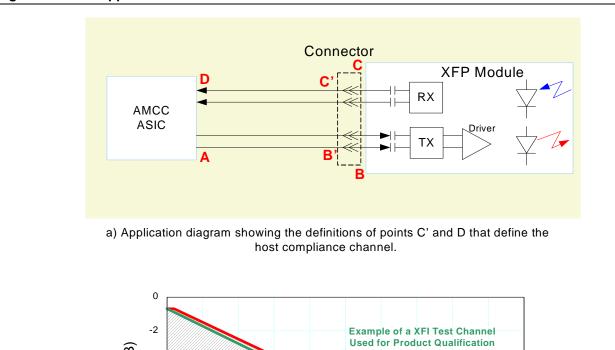

| Figure 76: XFP Application Reference Model                                                    | 143  |

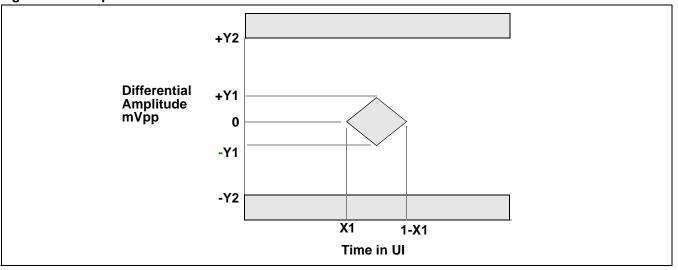

| Figure 77: Compliance Mask                                                                    | 148  |

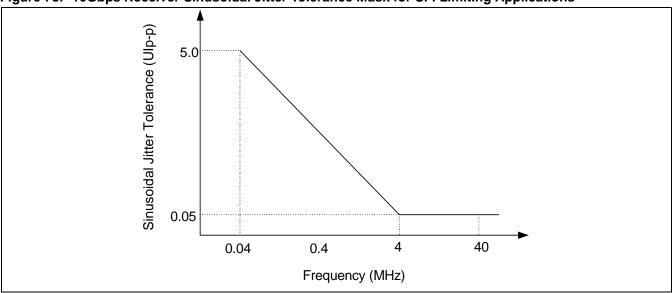

| Figure 78: 10Gbps Receiver Sinusoidal Jitter Tolerance Mask for SFI Limiting Applications     | 148  |

| Figure 79: 10Gbps Receiver Sinusoidal Jitter Tolerance Mask for XFI Applications              | 149  |

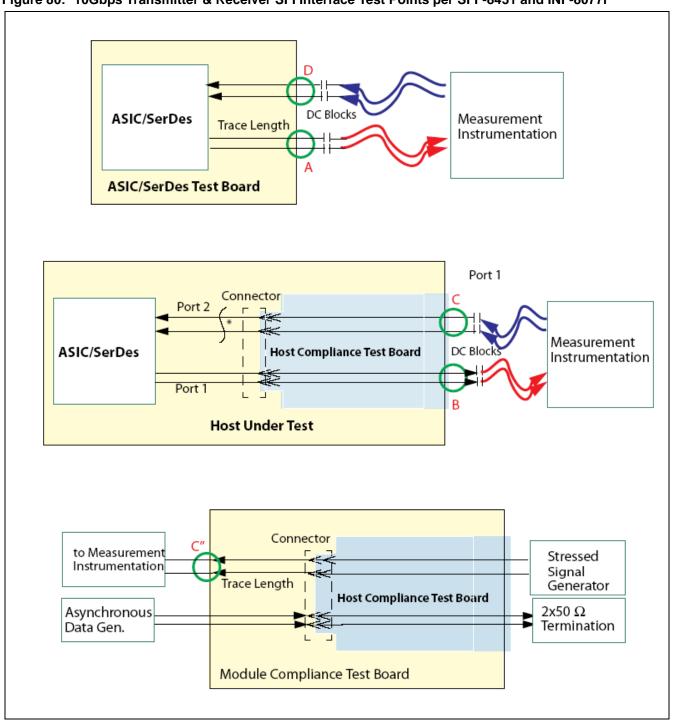

| Figure 80: 10Gbps Transmitter & Receiver SFI Interface Test Points per SFF-8431 and INF-8077i | 150  |

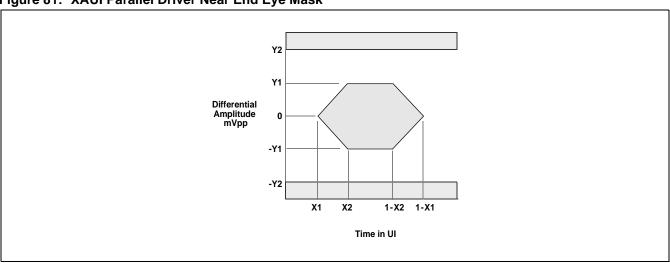

| Figure 81: XAUI Parallel Driver Near End Eye Mask                                             |      |

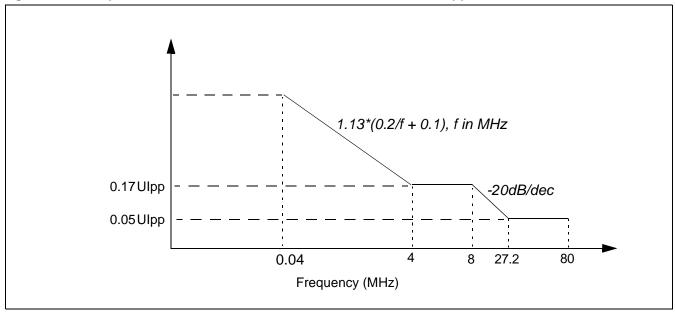

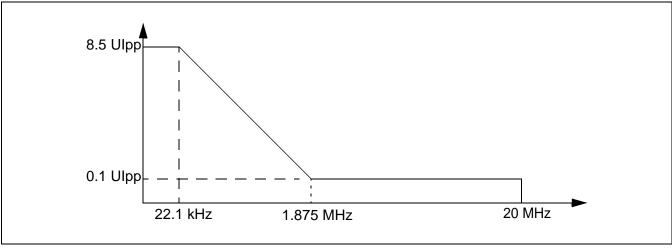

| Figure 82: XAUI Receiver Sinusoidal Jitter Tolerance Mask                                     | 153  |

|                                                                                               |      |

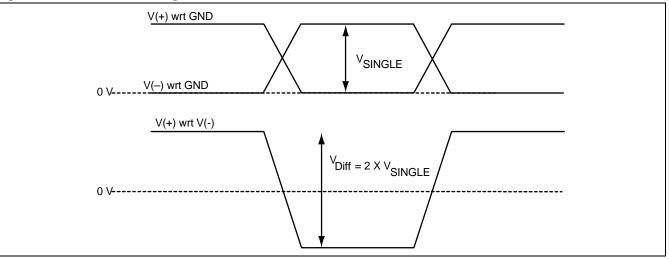

| Figure 83: Differential Voltage Measurement                                 | 168 |

|-----------------------------------------------------------------------------|-----|

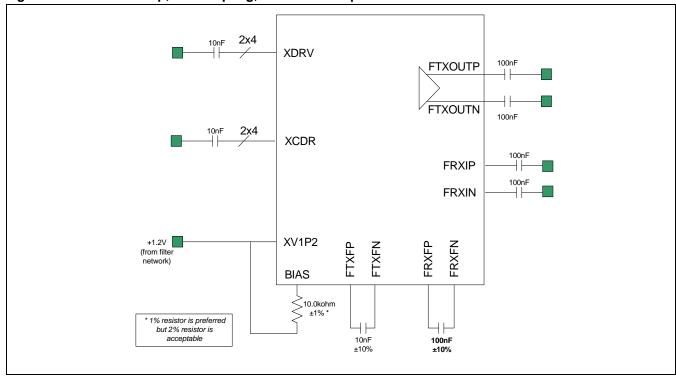

| Figure 84: External Loop, AC Coupling, and Bias Component Values            | 169 |

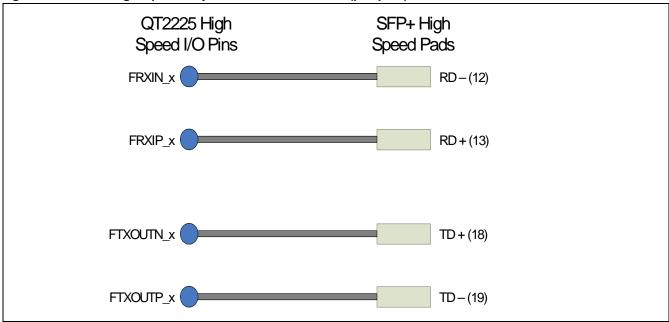

| Figure 85: SFP+ High Speed Layout Recommendation (per port)                 | 170 |

| Figure 86: Power Supply Sequencing Requirements                             | 172 |

| Figure 87: Recommended PCB layout for BGA landing pad for 23x23 mm2 package | 173 |

| Figure 88: Recommended Reflow Profile                                       | 173 |

## **List of Tables**

| Table 1: Standard Compliance List                                       |     |

|-------------------------------------------------------------------------|-----|

| Table 2: XAUI Driver Parameters                                         | 21  |

| Table 3: XAUI Driver Control Registers                                  | 22  |

| Table 4: 10Gbps Driver Configuration                                    | 24  |

| Table 5: Priority for Supported Technology                              | 32  |

| Table 6: Coefficient Update Field                                       | 35  |

| Table 7: Status Report Field                                            | 35  |

| Table 8: Transcoder Data Re-mapping                                     | 42  |

| Table 9: T to SYNC[1:0] Reconstruction for FEC Block of i=1 to 32 words | 45  |

| Table 10: MDIO/FEC Variable Mapping                                     | 46  |

| Table 11: 1.25Gbps Loopback Control Registers                           | 53  |

| Table 12: MDIO Registers for Datapath Clocking                          | 54  |

| Table 13: Line Timing Control Modes                                     | 59  |

| Table 14: VCXO PLL Control Pin Settings                                 | 64  |

| Table 15: XPLLOUT Configuration Settings                                | 64  |

| Table 16: FPLLOUT Configuration Settings                                | 65  |

| Table 17: TXENABLE Logic                                                | 70  |

| Table 18: LASI Control Registers                                        |     |

| Table 19: Receive Alarm Registers (RX_ALARM)                            | 75  |

| Table 20: rx_flag Alarm Registers                                       |     |

| Table 21: Transmit Alarm Registers (TX_ALARM)                           | 76  |

| Table 22: tx_flag Alarm Registers                                       |     |

| Table 23: WIS Status 3 Register (WIS_ALARM)                             | 80  |

| Table 24: WIS Extended Alarms Status Register (WIS_EXT_ALARM)           |     |

| Table 25: MDIO Management Frame Format                                  | 86  |

| Table 26: MDIO OP Code Definitions                                      |     |

| Table 27: Two-Wire Bus Rate Control Settings                            | 92  |

| Table 28: MDIO Register Config Data Structure                           |     |

| Table 29: Boot EEPROM Config Register 0xC8 Definition                   | 100 |

| Table 30: Checksum Calculations for EEPROM_I2C Reads                    | 102 |

| Table 31: System Loopback Modes and MDIO Control Registers              | 107 |

| Table 32: 10GE Network Loopback Modes and MDIO Control Registers        | 108 |

| Table 33: XAUI Jitter Test Pattern Generator Enable                     |     |

| Table 34: Test Pattern Priority                                         |     |

| Table 35: 10Gbps PRBS Generator and Checker Control                     |     |

| Table 36: BER Test Procedure                                            |     |

| Table 37: Supported BSCAN Instructions                                  |     |

| Table 38: Unsupported BSCAN Instructions                                |     |

| Table 39: Device ID Register                                            |     |

| Table 40: BSCAN Chain Implementation                                    |     |

| Table 41: QT2225 Ball Assignment & Signal Description                             | . 120 |

|-----------------------------------------------------------------------------------|-------|

| Table 42: Supply Pad and Ball Assignment and Description                          | . 125 |

| Table 43: Thermal Management                                                      | . 128 |

| Table 44: Common Serial Transmitter Specifications (FTXOUTP_x, FTXOUTN_x)         | . 130 |

| Table 45: SFI 10Gbps Serial Transmitter Specifications                            | . 131 |

| Table 46: XFI 10Gbps Serial Transmitter Specifications                            | . 132 |

| Table 47: Backplane (KR) 10Gbps Serial Transmitter Specifications                 | . 133 |

| Table 48: SFI 1.25Gbps Serial Transmitter Specifications                          | . 134 |

| Table 49: Backplane (KX) 1.25Gbps Serial Transmitter Specifications               | . 135 |

| Table 50: XAUI 1.25Gbps Serial Transmitter Specifications                         | . 136 |

| Table 51: Common Receiver Specifications (FRXIP_1/ FRXIN_1, FRXIP_2/FRXIN_2)      | . 138 |

| Table 52: SFI 10Gbps Receiver Specifications Supporting Limiting Modules          | . 139 |

| Table 53: SFI 10Gbps Receiver Specifications Supporting Linear Modules            | . 140 |

| Table 54: SFI 10Gbps Receiver Specifications Supporting SFP+ Direct Attach Cables | . 141 |

| Table 55: XFI 10Gbps Receiver Specification                                       | . 142 |

| Table 56: Backplane (KR) 10Gbps Receiver Specifications                           | . 144 |

| Table 57: Backplane (KX) 1.25Gbps Serial Receiver Specifications                  | . 145 |

| Table 58: SFI 1.25Gbps Serial Receiver Specifications                             | . 146 |

| Table 59: XAUI 1.25Gbps Serial Receiver Specifications                            | . 147 |

| Table 60: XAUI 3.125Gbps Driver Parallel Interface Specifications                 | . 151 |

| Table 61: XAUI 3.125Gbps Input Parallel Interface Specifications                  | . 152 |

| Table 62: VCXO Performance Specifications                                         | . 153 |

| Table 63: Latency Performance Specifications                                      | . 154 |

| Table 64: CML Clock Input Performance Specifications                              | . 155 |

| Table 65: CML Clock Output Performance Specifications                             | . 156 |

| Table 66: Reference Clock Jitter Specifications                                   | . 157 |

| Table 67: Absolute Maximum Ratings                                                | . 158 |

| Table 68: Recommended Operating Conditions                                        | . 159 |

| Table 69: LVCMOS Input/Output Characteristics                                     | . 162 |

| Table 70: MDIO Input/Output Characteristics                                       | . 163 |

| Table 71: MDIO Interface Timing                                                   | . 164 |

| Table 72: DCC Interface Timing                                                    | . 164 |

| Table 73: I2C Input/Output Characteristics                                        | . 166 |

| Table 74: I2C Interface Timing                                                    | . 166 |

| Table 76: Auto-Negotiation DME Page Specifications                                | . 167 |

| Table 75: JTAG Interface Timing                                                   | . 167 |

#### QT2225 Overview

The QT2225 implements a dual high speed interface for 10GbE LAN/WAN, 10GFC, 1GbE equipment and optical modules. The QT2225 devices may be used in diverse applications including:

#### QT2225:

- 10GBASE-KR,1000BASE-KX Backplane

- SFP+/SFP Limiting Module Applications

- XFP Module Applications

#### QT2225-1:

- SFP+/SFP Linear and Limiting Module & Passive Direct Attach Cable Applications

- XENPAK/X2 10GBASE-LRM Applications

The basic flow of operations is contained in lists below and the detailed descriptions of all of the features are contained in the applicable sections. An important feature of the device, the on-chip EDC engine, provides equalization for Multimode Fiber (to meet the IEEE 10GBASE-LRM spec in the QT2225-1), FR4 and connector effects. The EDC engine is fully adaptable to compensate for cable variations and the system is field programmable in order to support standards changes or emerging standards such as 10GBASE-VSRM (850 linear w/EDC). The 10G transmitter includes waveform reshaping capability, allowing the signal jitter content to be minimized. This enables low bit error rate and transmission over longer trace lengths.

#### Serial 10G (RX Channel) to XAUI Operations

- 1. FRXI Serial Data Input

- 2. AGC w/DC Offset Control

- 3. EDC & CDR; DeMultiplexer and Clock Divider

- 4. Receive WIS (Optional), Frame Sync, Descrambler

- 5. 66B/64B Decoder, Rate Adjust, 8B/10B Encoder

- 6. XDRV XAUI Data Output

#### XAUI (TX Channel) to Serial 10G Operations

- 1. XCDR XAUI Data Input

- 2. Phase Adjust & Demultiplexer

- 3. XAUI Code Synchronization & Lane Alignment

- 4. 8B/10B Decoding, Rate Adjust, 64/66B Encoding

- 5. Scrambler and Gear Box

- 6. Transmit WIS (Optional), Mux, & Clock Generation

- 7. 10G FTXI Serial Data Output

Table 1: Standard Compliance List

| Standard                                                                                                         | Revision      | Date                  |

|------------------------------------------------------------------------------------------------------------------|---------------|-----------------------|

| Backplane Ethernet Standard<br>10GBASE-KR, 1000BASE-X: IEEE 802.3ap-<br>2007                                     | Released 2007 | March 22, 2007        |

| SFP+ Standard:<br>SFF-8431 Specification for Enhanced 10<br>Gigabit Small Form Factor Pluggable Module<br>"SFP+" | Revision 3.3  | April 8, 2009         |

| XFP Standard:<br>INF-8077i 10 Gigabit Small Form Factor Plug-<br>gable Module                                    | Revision 4.5  | August 31,<br>2005    |

| SFP Standard:<br>INF-8074i Specification for SFP (Small Form<br>Factor Pluggable) Transceiver                    | Revision 1.0  | May 12, 2001          |

| IEEE Ethernet:<br>Std. 802.3-2005                                                                                | Released 2005 | December 12,<br>2005  |

| IEEE LRM:<br>802.3aq/D4.0                                                                                        | D4.0          | May 2007              |

| IEEE JTAG:<br>IEEE Std. 1149.1-2001                                                                              | Released 2001 |                       |

| IEEE Std. 1149.6-2003                                                                                            | Released 2003 |                       |

| 10G Fibre Channel:<br>INCITS T11/Project 1413-D                                                                  | Revision 3.1  | June 7, 2002          |

| JEDEC Power Supply and Voltage Interface Standard: JEDEC JESD8-11                                                |               | October, 2000         |

| JEDEC ESD:<br>JEDEC JESD22-A114-B                                                                                |               | June, 2000            |

| JEDEC/IPC Handling, Packaging, Shipping<br>and Reflow of Sensitive SMD's:<br>IPC/JEDEC J-STD-033A                | Revision 1.0  | July 2002             |

| SONET:<br>GR-253-CORE                                                                                            | Issue 3       | September,<br>2000    |

| XENPAK MSA                                                                                                       | Issue 3.0     | September 18,<br>2002 |

| RoHS Directive                                                                                                   |               | February 13,<br>2003  |

Note: Standards compliance only relates to applicable sections pertaining to this product type.

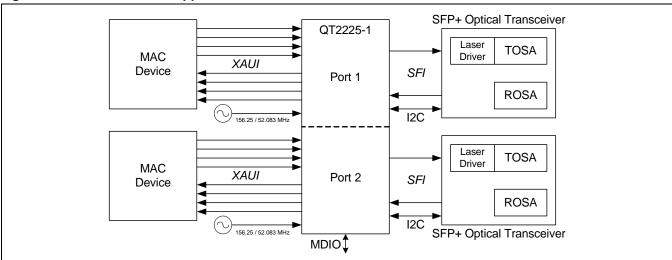

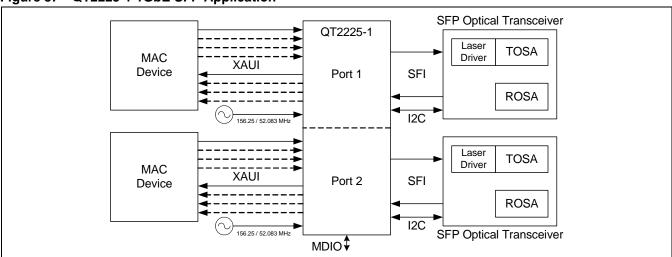

## QT2225-1 Application: 10GbE SFP+ Line Card

The QT2225-1 device supports the high-speed 10G serial SFI performance specifications. It is fully compatible with industry standard SFP+ modules and supports two reference clock rates as shown in Figure 2. Direct Attach SFP+ cable applications are also supported.

## QT2225-1 Application: 1GbE SFP on a 10GbE Line Card

The QT225-1 device supports the related 1GbE protocol and is fully compatible with industry standard 1GbE SFP modules. In this mode, the PHY supports a 1GbE signal on XAUI Lane 0 and interfaces to the SFP module on the same pins used for 10GbE.

All hardware configurations for the QT2225-1 are the same between the 1GbE and 10GbE applications. The host system must configure the device to operate with the installed module.

Figure 2: QT2225-1 SFP+ Application

Figure 3: QT2225-1 1GbE SFP Application

#### QT2225 Application: 10GbE XFP Line Cards

The QT2225 device supports the high-speed 10G serial XFI performance specifications. Figure 4, below, shows the QT2225 in a 10GE LAN/PHY with optional WIS support. XFI Rx equalization and/or XFI Tx preemphasis can be activated to allow the designer to use longer FR-4 traces on the XFI interface or to compensate for marginal PCB performance.

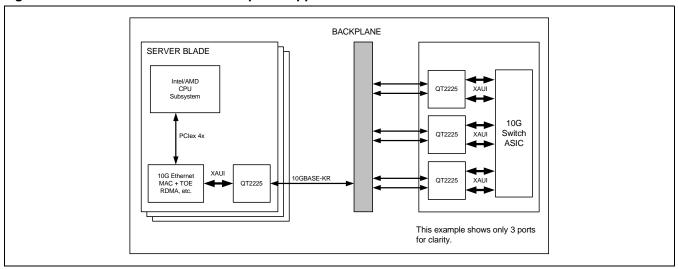

#### QT2225 Application: 10GbE over Backplane

The QT2225 supports 10GBASE-KR applications and the device, when enabled in KR Mode, provides

transmit pulse shaping that gets optimized for each backplane channel using link training specified in IEEE 802.3ap.

Figure 5 shows a typical blade server application. In this case, the QT2225 converts the XAUI signal from a 10G Ethernet MAC engine to 10GBASE-KR on a single differential signal pair. On the server blades themselves, there are typically two ports (for failover and/or increased bandwidth). Each server port must be matched by a port on the switch blade. ATCA backplane applications look very similar to the blade server application.

Figure 5: QT2225 10GBASE-KR Backplane Application

## **Functional Block Diagram**

Figure 6: QT2225 - Functional Block Diagram (Single Port Shown)

## **Functional Description**

This section describes the functional blocks of the QT2225 illustrated below. Each block will be described in the following sections.

#### Transmit Data Path: XAUI Interface

The XAUI input accepts 4 differential 3.125Gbps data lanes on inputs XCDR0 - XCDR3. The data must be encoded as specified by IEEE 802.3 Clause 47. The XAUI signal is recovered, synchronized and deskewed. The data is then passed through a rate compensation block. Finally, the data is 10b/8b decoded and passed to the next block for 64b/66b encoding.

#### XAUI I/O & CDR

At the XAUI inputs, clock and data are recovered for each of the four 3.125Gbps input lanes. The differential receivers used at this interface have  $100\Omega$  differential input impedance and are intended to be AC coupled. The XAUI interface includes a passive equalization circuit to improve tolerance for sub-optimal XAUI interface design.

#### Transmit XGXS

#### Phase Adjust/Demux

The signal from each lane is phase adjusted to a single clock and then demultiplexed.

#### XAUI Code Synchronization

The Code Synchronization block delineates the 10 bit code word boundaries by identifying the comma character in the K28.5 Idle code. This is performed independently on each lane. The code synchronization status is displayed in Register bits 4.0018h[3:0].

If any single lane loses signal (no transitions detected), the code sync block will not attempt to achieve sync on the XAUI input lanes. The QT2225 will report 'loss of sync' on all 4 lanes. However, when transitions are received on all 4 lanes, the code sync block is fully active. If no K28.5 codes are detected on a given lane, the QT2225 will report 'loss of sync' independently for each lane.

#### XAUI Lane Alignment

The incoming XAUI data must be aligned due to varying off-chip transmission delays between the four lanes. The alignment operation is done by aligning /A/ codes on all four lanes. The /A/ codes appear randomly in the idle data stream and are transmitted simultaneously at the source on all four channels as a single column of data, ||A||.

The QT2225 can tolerate a skew of up to 40 bits between any two lanes at the XCDR input pins.

## 8B/10B Decoding

Each 10 bit code word is decoded into 8 data bits and 1 control bit. The 8 data bits and 1 control bit are then passed on to the rate adjust function.

8B/10B coding errors are counted on a per lane basis. For each lane, errors are reported in an 8 bit, non-rollover counter that is read cleared. The four counters for Lane 0 to Lane 3 are located in the lower byte of MDIO registers 4.C030h - 4.C033h.

#### Transmit Rate Adjust

Data is written into a rate compensation FIFO. The outgoing data is read out using a clock derived from the local reference clock. Idle codes or sequence ordered\_sets from the data stream are added or dropped to compensate for the clock rate difference. The minimum inter-frame gap (IFG) of five characters and sequence ordered sets are always maintained.

Proper rate compensation will always be performed when the clock rates are within 200ppm. In LAN mode, the QT2225 can tolerate a continuous input and output stream of back-to-back 9600 byte jumbo frames with minimum IFG. In WAN mode, this is limited to 2 jumbo frames with minimum IFG. If the clock rate difference exceeds 200ppm or multiple back-to-back jumbo frames are transmitted, one or more packets may be corrupted.

Transmit rate adjust operation is monitored in MDIO register 4.C002h. This register flags idle code removal and insertion in bits [15:14] (normal operation), as well as overflow/underflow in bits [9:8] (fault condition).

#### **Transmit PCS**

#### 64B/66B Encoding

The encoder takes 64 bits of input data and the associated 8-bit control word from the XAUI block and creates a new 66 bit data bus. The 66 bits are composed of 2 sync bits followed by 64 bits of data. The sync bits are used to synchronize the data stream on a frame boundary. The sync bits [1:0] are 10 if 64 bit data bus is composed solely of data words. If the bus contains 1 or more control words, the sync bits [1:0] are set to 01 and are followed by a 8 bit type data. The type word indicates the content of the following 56 bits of data. The sync bit values of 00 or 11 are invalid.

Incoming control words are converted from 8 bits to 7 bits. Data words are not altered. When combinations of data and control words are used in a bus, extra bits are inserted if needed at the boundary between the data and control words to make the total number of bits 64. Ordered set control codes are encoded using a combination of the block's type field and a 4 bit O code for each ordered set.

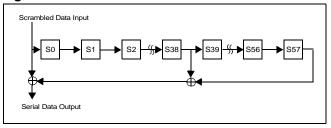

#### Scrambler

The 66-encoded data is scrambled before transmission. The scrambler polynomial is  $1+x^{39}+x^{58}$ . Only the 64 data bits pass through the scrambler. The sync bits are not scrambled. The scrambler can be bypassed by setting the MDIO register bit 3.C000h[2]. The scrambler is depicted in Figure 7.

Figure 7: Transmit Scrambler

#### Gearbox

The gearbox converts the data from a 66 bit wide data bus at 156.25 Mb/s to a 64 bit wide bus at 161.1328 Mb/s. This step is required to prepare the data for serialization in the next functional block.

#### Transmit 10G Driver

#### Transmit WAN Interface Sublayer (WIS)

When enabled, via 2.0007h[0], the optional TX WIS block accepts data from the Gearbox and maps it into the payload of the transmitted STS-192C WIS frame stream. Fixed stuff octets are added, together with a set of Path Overhead octets, to create a Synchronous Payload Envelope (SPE). Line and Section Overhead octets are combined with the SPE and then scrambled using the frame-synchronous scrambler to produce the final transmitted WIS frame. The WIS continuously generates one WIS frame every 125µs.

The WIS function is not supported in 10GBASE-KR applications.

#### Transmit FEC

The QT2225 implements an optional FEC (Forward Error Correction) sublayer for 10GBASE-R applications to improve link performance. The chip uses an in-band FEC encoding that does not consume additional bandwidth, and so is compatible with currently supported PMD devices. It is optimized to handle short bursts of errors in the signal. The implementation is compliant to IEEE 802.3ap Clause 74 and is specifically intended for 10GBASE-KR applications.

The FEC sublayer acts on the scrambled 66b encoded data blocks from the PCS layer. The algorithm encodes FEC information across a group of 32 data blocks, forming a FEC frame that is 66 x 32 = 2112 bits long. The FEC Transmitter engine consists of a Transcoder, Encoder and Scrambler. An Error Injector is also available. The Transcoder shortens each block from 66 bits to 65 bits by reducing the sync header field from 2 bits to 1. The Encoder calculates a 32-bit parity-check field across the FEC frame that is appended to the frame end. The Scrambler is then applied to the frame before it is transmitted.

The FEC block is described in detail in "FEC Encoding/ Decoding" on page 40.

### Transmit Multiplexer and Clock Generation

A clock divider generates the clock frequencies required to multiplex the 64 bit wide bus coming from the previous block into a single 10Gbps output, from the locally generated 10GHz clock.

#### **Output Data Driver**

The output driver is a differential pair, FTXOUTN and FTXOUTP, which are both terminated on chip with  $50\Omega$  to 1.8V. The output level can be adjusted and output polarity inverted with a vendor specific MDIO register. The output driver has the ability to emphasize the output to overcome frequency dependent loss of FR4.

#### Receive Data Path: 10G Interface

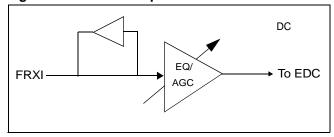

## Linear Equalizer/AGC

The QT2225 is configured with a front end Linear Equalizer/AGC with a DC Offset circuit which provides an equalized, fixed amplitude signal to the EDC engine input (Figure 8). The input must be externally ACcoupled.

#### **EDC Engine**

In 10GBASE-LRM applications (QT2225-1 Only), an adaptive Electronic Dispersion Compensation Engine is used to equalize signal impairments caused by the transmission channel response. The equalizer employs a linear AGC amplifier and both a Feed Forward Equalizer (FFE) and a Decision Feedback Equalizer (DFE). The values of the tap weights in the FFE and DFE are adapted automatically.

In backplane applications only the DFE is used to save power.

#### **Adaptive Data Recovery**

The clock and data recovery adapt both the phase and decision threshold of the sampling point for optimum BER.

## Clock Recovery

The signal from EDC block is passed to a clock and data recovery (CDR) circuit. The clock recovery circuit recovers the clock from the received signal. The recovered clock is used to time the EDC engine and provides the frequency reference from the receiver. When the PLL is frequency locked to the incoming data

the internal signal, frxlock, is asserted. When frxlock is low the receive data outputs XDRV<3:0> will transmit idle frames and error codes. The state of frxlock is reflected in the 'PMA receive link status' bit, 1.0001h.2 and 1.0008h.10, a latched low and latch high register bit respectively whose value is determined by the equation {frxlock AND RXLOSB\_I}. The state of the RXLOSB\_I input is available in Register bit 1.D002h.2.

#### Recovered Clock Frequency Monitoring

When the receive recovered clock is more than 500 ppm from the transmit reference clock, a synchronization error is declared and the internal signal *sync\_err* goes high. *sync\_err* can be viewed at MDIO register 1.C001h.1. This is a latched high register bit that is cleared on read. On powerup or reset, the register must be read to clear it.

## Demultiplexer and Clock Divider

All clocks needed for the demultiplexer and the reset of the receive path are generated in this block by dividing down the 10 GHz recovered clock. The demux converts the 10 Gbps serial incoming data into 64 parallel bits.

## Receive WAN Interface Sublayer (WIS)

The RX WIS block receives data from a SONET link and extracts the Ethernet payload from the STS-192c SPE. It also monitors the integrity of data at the Section, Line and Path levels and monitors both near and far end faults. The WIS receive and transmit blocks are bypassed in 10GBASE-R applications.

The WIS function is not supported in 10GBASE-KR Backplane applications.

Figure 8: Receiver Input

#### Receive FEC

The QT2225 implements an optional FEC (Forward Error Correction) sublayer for 10GBASE-R applications to improve link performance. The chip uses an in-band FEC encoding that does not consume additional

bandwidth, and so is compatible with currently supported PMD devices. It is optimized to handle short bursts of errors in the signal. The implementation is compliant to the IEEE 802.3ap Standard and specifically intended for 10GBASE-KR applications.

The FEC sublayer acts on the scrambled 66b encoded data blocks from the PCS layer. The algorithm encodes FEC information across a group of 32 data blocks, forming a FEC frame that is  $66 \times 32 = 2112$  bits long. The FEC Receiver Engine consists of a De-Scrambler, Block Synchronizer, Decoder and Reconstructor, along with an Error Monitor.

#### **Receive PCS**

#### Frame Synchronization

The frame synchronizer takes the 64 bit wide data bus output from the demultiplexer and converts it to a 66 bit wide data bus. The 66 bits are composed of 2 sync bits followed by 64 bits of data. The sync bits are used to synchronize the data stream on a frame boundary. The bus rate at each stage will depend on the selected protocol.

The chip also monitors invalid sync header bits. Valid sync bits include 01b and 10b. The combinations 11b and 00b are invalid. When an invalid sync header is detected, a 6-bit counter is incremented. This counter is located in MDIO register field 3.0021h[13:8]. This is a read only, non-rollover counter that is cleared when read. The counter will count a maximum of 16 sync header errors in a 125  $\mu$ s window.

When there are 16 or more sync header errors in a 125µs window, the 'hi\_ber' flag is set to 1b in MDIO register bit 3.0020h[1]. This is a read only register bit. The algorithm for counting sync header errors and detecting 'hi\_ber' follows the 'BER monitor state machine' described in IEEE 802.3-2005 Figure 49-13.

#### Descrambler

The descrambler processes the payload to reverse the effect of the scrambler on the payload. The descrambler is self-synchronizing. It calculates the inverse of the scrambler function using the polynomial  $1+x^{39}+x^{58}$ . The descrambler is depicted in Figure 9. Only the 64 data bits are passed through the descrambler. The descrambler is bypassed when the scrambler bypass mode is enabled through MDIO register 3.C000h[1].

Figure 9: Receive Descrambler

#### 66b/64b Decoder

The decoder performs the inverse function of the encoder. This block converts the 64 bit payload back into the original eight 8-bit codes. Valid code word formats are described in IEEE 802.3-2005 Figure 49-7.

#### Receive XGXS

## Receive Rate Adjust

Data from the 66b/64b decoder is written into a rate compensation FIFO using the fiber recovered clock. The outgoing data is read out using the XAUI reference clock. Due to the fact that these clocks are derived from different sources, a rate adjust operation needs to be performed. The rate compensation block accomplishes this by either adding or dropping Idle ordered\_sets, as required, from the data stream. The minimum inter packet gap of five characters and sequence ordered set messages are maintained.

Receive rate adjust operation is monitored in MDIO register 4.C002h. This register flags Idle code removal and insertion in bits [13:12] (normal operation), as well as overflow/underflow in bits [7:6] (fault condition).

#### 8b/10b Encoder

The data bus is divided into four 8-bit wide data channels. Each of the four channels has independent 8b/10b encoders which will convert the 8 bit data lanes into 10 bit code words. Either a positive or negative disparity 10 bit code word will be selected, depending on the running disparity.

#### **Receive XAUI Driver**

### Multiplexer and XAUI DRV

After 8b/10b encoding has been added, the receive multiplexer serializes data words to form four 3.125Gbps output data lanes. The XAUI output drivers provide high-swing differential outputs with  $100\Omega$  differential output impedance and are intended to be AC coupled. The 3.125GHz timing is derived from the reference clock, EREFCLK.

The receive XAUI driver interface includes programmable pre-emphasis to compensate for sub-optimal host-side PCB design.

## **High Speed Interfaces**

This section describes the high-speed XAUI and 10Gbps interfaces, with focus on configurable capabilities.

#### **XAUI** Interface

### XAUI XCDR Input Equalization

The XAUI input includes an equalization circuit to compensate for FR4 channel loss. There are two equalization settings:

- Standard equalization (4.C05Eh[0] = 0b, default)

- Enhanced equalization (4.C05Eh[0] = 1b)

For FR4 channels that are compliant to 802.3-2005, the standard equalization setting should be used. The enhanced equalization setting can be used to compensate for exceptionally poor channels, however it will over-compensate a high quality signal and result in degraded performance, so should not be used unnecessarily.

#### XAUI XDRV Driver

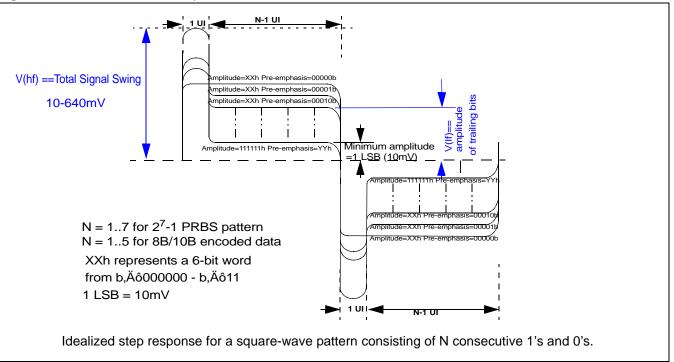

The XAUI driver uses a 2-tap FIR architecture with a 1UI spacing. The main amplitude and post-cursor taps are independently adjustable to compensate for host board transmission media effects. The settings are controlled via MDIO registers and can be set via EEPROM. Each lane is independently controlled.

The post-cursor driver increases the amplitude of the first bit following any transition in the data pattern, the leading edge of the bit being defined by the transition. The driver also decreases the amplitude of subsequent bits having the same binary value as the bit following the transition, until the next data transition occurs.

The post-cursor driver can be disabled via register bits 4.C05Ah[7:4]. The individual XAUI drivers may also be disabled from register bits 4.C05Ah[3:0].

Figure 10: XAUI XDRV Pre-Emphasis

### Programming the XAUI Driver

To program the XAUI driver to a desired setting, use the following procedure. Note that the voltages are measured differentially and refer to the peak voltage from GND for an AC-coupled signal.

Determine the target peak voltage. This is the "high frequency" amplitude, V(hf), from Figure 10. Calculate the digital weight of the amplitude, hf\_amp, following the formula in Table 2.

- Determine the target voltage for the trailing bits.

This is the "low frequency" amplitude, V(If), from Figure 10. Calculate the digital weight of the amplitude, If\_amp, following the formula in Table 2.

- 3. Calculate the main driver amplitude, main\_xdrv\_amp, and post-cursor amplitude, post\_xdrv\_amp.

- 4. Calculate XDRV\_AMP\_x, XDRV\_DEEMP\_x and HF\_AMP\_x. Program into MDIO register fields for each lane (x = lane number).

**Table 2: XAUI Driver Parameters**

| Parameter     | Description                                                                  | Comment                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V(hf)         | 10-640mV                                                                     | High frequency voltage. Represents the peak voltage of the signal, measured on the first bit on a string of consecutive identical digits.                                                                                                                                                                                                                                     |

| hf_amp        | hf_amp = int ( V(hf) / dV) - 1                                               | Digital weight of the High Frequency voltage.  Valid range is 0 - 63.  While the maximum allowable weight is 63, a practical limit of 57 should be observed to avoid driver saturation.  (This field is equivalent to the sum of the driver weights, such that hf_amp = main_xdrv_amp + post_xdrv_amp)                                                                        |

| V(If)         | 10-640mV                                                                     | Low frequency voltage.  Represents the voltage of the signal measured on the trailing bits in a string of consecutive identical digits.                                                                                                                                                                                                                                       |

| lf_amp        | If_amp = int ( V(If) / dV) - 1                                               | Digital weight of the Low Frequency voltage. Valid range is 0 - 63.                                                                                                                                                                                                                                                                                                           |

| main_xdrv_amp | main_xdrv_amp = (hf_amp + lf_amp)/2                                          | Digital weight of the Main Driver in the 2-tap FIR driver. Valid range is 0 - 63.                                                                                                                                                                                                                                                                                             |

| post_xdrv_amp | post_xdrv_amp = (hf_amp - lf_amp)/2                                          | Digital weight of the Post-cursor Driver Valid range is 0 - 31.                                                                                                                                                                                                                                                                                                               |

| XDRV_AMP_x    | XDRV_AMP_x = 63 - main_xdrv_amp                                              | MDIO Register field to program the main driver amplitude.  There is one register field for each lane, denoted by x, where x = 03.  Valid range 0 - 63.  The register field is a 6-bit binary weighted number where the maximum value is encoded by '000000' and the minimum by '111111'.                                                                                      |

| XDRV_DEEMP_x  | XDRV_DEEMP_x = 31 - post_xdrv_amp                                            | MDIO Register field to program the post-cursor driver amplitude. There is one register field for each lane, denoted by x, where x = 03. Valid range 0 - 31. The register field is a 5-bit binary weighted number where the maximum value is encoded by '00000' and the minimum by '11111'.                                                                                    |

| XDRV_HF_AMP_x | XDRV_HF_AMP_x equals hf_amp when hf_amp >=30, and equals 0 when hf_amp < 30. | MDIO Register field to program the High Frequency voltage digital weight. There is one register field for each lane, denoted by x, where $x = 03$ . Valid range $0 - 63$ . This field must be programmed only for high amplitude signals and ensures that the step size, dV, remains linear. The register field is a 6-bit binary weighted number. The value is not inverted. |

| dV            | 10mV                                                                         | This is the voltage step size for a +1 LSB change in the driver weight. The main and post-cursor driver step size is the same.  Measured as a peak voltage on the differential signal.                                                                                                                                                                                        |

#### Main XDRV Amplitude

The main output driver is set by a 6-bit binary-weighted word. One LSB corresponds to +10mV peak differential voltage swing (or +20mV peak-to-peak). With a flat-channel response (post-cursor driver is off), the digital word will set the amplitude of the output.

The amplitude corresponding to the binary-weighted word is inverted, as described in Table 2.

The drive amplitude can theoretically be set in the range 20-1280mVpp differential. The binary-weighted amplitude should be kept below 57 to avoid saturating the driver (binary word of 6b'000110).

#### Post-Cursor XDRV Amplitude

The post-cursor output driver is set by a 5-bit binary-weighted word. One LSB corresponds to +10mV peak differential voltage swing (or +20mV peak-to-peak).

The amplitude corresponding to the binary-weighted word is inverted, as described in Table 2.

### XDRV HF Amplitude Field

The HF\_AMP\_x register fields must be programmed to maintain amplitude linearity of the driver for large

voltage swings. This field is equivalent to the sum of the main and post-cursor driver weights. When the driver weight sum is below 30, this field should be set to 0.

The register addresses to program the XAUI drivers are listed in Table 3.

#### Considerations

Two factors must be considered when setting the main and post-cursor amplitudes so as not to violate the chip limits and exceed the capabilities of the driver.

- 1) The total voltage swing should not exceed the absolute maximum of 640mVpp (single-ended). This means that the sum of the digital amplitude and post-cursor words should be less than 63 (Table 2 recommends a maximum practical limit of 57).

- 2) The post-cursor amplitude should always be smaller than the main amplitude setting to avoid voltage values of the opposite polarity on subsequent identical digits when looking at the differential waveform.

The calculation rules outlined in Table 2 enforce these restrictions.

Table 3: XAUI Driver Control Registers

| Parameter           | Register Field      | Register Address | Description                                 |

|---------------------|---------------------|------------------|---------------------------------------------|

|                     | XDRV_AMP_0          | 4.C057.5:0       | Lane 0 Main Driver Amplitude                |

|                     | XDRV_AMP_1          | 4.C057.10:6      | Lane 1 Main Driver Amplitude                |

| Main Drivers        | XDRV_AMP_2          | 4.C056.5:0       | Lane 2 Main Driver Amplitude                |

|                     | XDRV_AMP_3          | 4.C056.10:6      | Lane 3 Main Driver Amplitude                |

|                     | XDRV_DIS_x          | 4.C05A.3:0       | Lane 3:0 Main Driver Disable Controls       |

|                     | XDRV_DEEMP_0        | 4.C059.4:0       | Lane 0 Post-cursor Driver Amplitude         |

| Post-Cursor Drivers | XDRV_DEEMP_1        | 4.C059.9:5       | Lane 1 Post-cursor Driver Amplitude         |

|                     | XDRV_DEEMP_2        | 4.C058.4:0       | Lane 2 Post-cursor Driver Amplitude         |

|                     | XDRV_DEEMP_3        | 4.C058.9:5       | Lane 3 Post-cursor Driver Amplitude         |

|                     | XDRV_PRE_EMP_PWDN_x | 4.C05A.7:4       | Lane 3:0 Post-cursor Driver Disable Control |

|                     | XDRV_HF_AMP_0       | 4.C070.5:0       | Lane 0 HF Amplitude                         |

| HF Amplitude Fields | XDRV_HF_AMP_1       | 4.C070.10:6      | Lane 1 HF Amplitude                         |

|                     | XDRV_HF_AMP_2       | 4.C071.5:0       | Lane 2 HF Amplitude                         |

|                     | XDRV_HF_AMP_3       | 4.C071.10:6      | Lane 3 HF Amplitude                         |

## 10Gbps Interface

#### **Transmit Control**

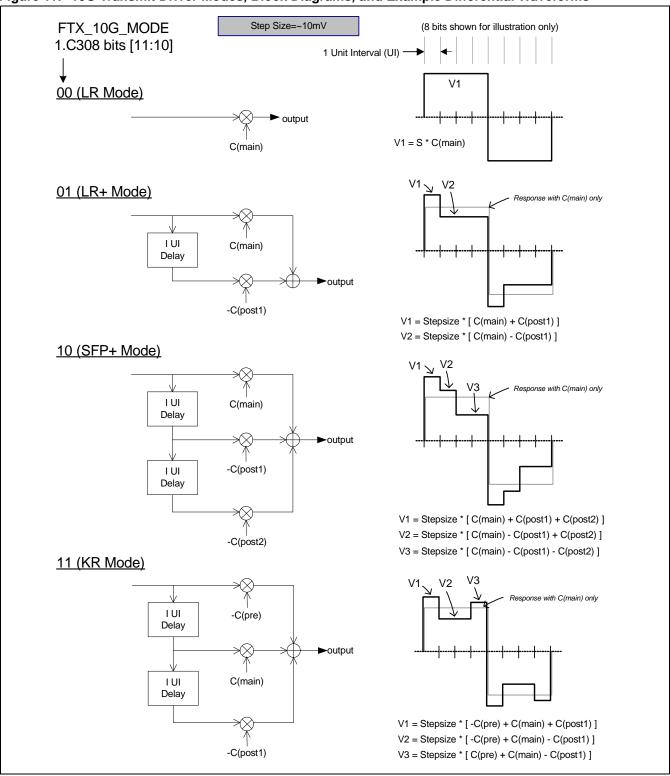

The QT2225 10Gbps serial transmitter has programmable amplitude control and optional post-cursor and pre-cursor emphasis using a finite impulse response (FIR) structure with a maximum of 3 taps. By adjusting FIR architecture and tap weights, different channel responses can be generated for improving signal integrity performance.

The FIR structure is configured using MDIO register FTX\_10G\_MODE (1.C308h[11:10]), as illustrated in Figure 11 for LR, LR+, SFP+, and KR modes. Example waveforms (differential) are provided in Figure 11 to illustrate pre-cursor and post-cursor effects for each mode, using a bit pattern of 11110000. The FIR structure uses a combination of delay and tap weighting functions to emphasize high frequency content in the waveform. A fixed Stepsize converts the tap weights to a voltage swing, where Stepsize is approximately 10mV/step.

The different 10G mode settings enable users to optimize device performance based on end-application channel characteristics. The KR mode is a requirement of the 802.3ap-2007 Standard and provides the best signal performance for backplanes. The SFP+ mode minimizes the deterministic jitter at the SFP+ module input. The LR+ mode provides a lower-power alternative to the SFP+ mode. The LR mode is a low power setting when no emphasis is desired. The modes are summarized in Table 4.

The main driver channel amplitude is controlled by the 6-bit MDIO word FTX\_DATA\_LVL (1.C308h[5:0]). The output signal amplitude is equal to Stepsize \* C(main) in Figure 11 where C(main) is a binary weighted value set by FTX DATA LVL.

#### **Post1-Cursor Emphasis**

Post-cursor emphasis is used to adjust the relative amplitude of the *first* bit in a string of consecutive identical digits. This amplitude is controlled by a 5-bit word in MDIO register FTX\_PST\_LVL (1.C309h[4:0]). The output signal amplitude is equal to Stepsize \*

C(post1) in Figure 11 where C(post1) is a binary weighted value that is set by FTX\_PST\_LVL.

For XFP applications, the resulting waveform must still conform to the XFI eye mask with pre-emphasis invoked, which limits the peak amplitude to fall below 385mVpp.

Note that C(post1) in Figure 11 corresponds to -C(+1) in the 802.3ap-2007 Standard (Section 72.7.1.10).

#### **Pre-Cursor Emphasis**

Pre-cursor emphasis is used to adjust the relative amplitude of the *last* bit in a string of consecutive identical digits. The amplitude for pre-cursor emphasis is controlled by a 4-bit word in MDIO register FTX\_PRE\_LVL (1.C309h[8:5]). The output signal amplitude is equal to Stepsize \* C(pre) where C(pre) is a binary weighted value that is set by FTX\_PRE\_LVL.

Pre-cursor emphasis is used for KR mode in Figure 11.

Note that C(pre) in Figure 11 corresponds to -C(-1) in the 802.3ap-2007 Standard (Section 72.7.1.10).

#### **Post2-Cursor Emphasis**

Post2-cursor emphasis is used to adjust the relative amplitude of the *second* bit in a string of consecutive identical digits. The amplitude for post2-cursor emphasis is controlled by a 4-bit word in MDIO register FTX\_PRE\_LVL (1.C309h[8:5]). The output signal amplitude is equal to Stepsize \* C(post2) where C(post2) is a binary weighted value that is set by FTX\_PRE\_LVL.

Post2-cursor emphasis is used in SFP+ mode in Figure 11.

#### **Considerations**

The total weight of all combined tap settings must sum to a value of 63 or less for proper operation. The main tap amplitude must be programmed to a positive voltage greater than 0V.

Post2-cursor and pre-cursor emphasis cannot be used simultaneously e.g. post2-cursor is available in SFP+ mode only, while the pre-cursor is available only in KR mode.

Table 4: 10Gbps Driver Configuration

| Transmitter Mode<br>Name | FTX_10G_MODE<br>1.C308h[11:10] | Pre-cursor | Main | Post1-cursor | Post2-cursor |

|--------------------------|--------------------------------|------------|------|--------------|--------------|

| LR                       | 00                             |            | Y    |              |              |

| LR+                      | 01                             |            | Y    | Y            |              |

| KR                       | 11                             | Y          | Y    | Y            |              |

| SFP+                     | 10                             |            | Υ    | Y            | Y            |

Figure 11: 10G Transmit Driver Modes, Block Diagrams, and Example Differential Waveforms

## **EDC Engine**

The QT2225 includes a sophisticated Electronic Dispersion Compensation (EDC) engine to meet IEEE 802.3ap 10GBASE-KR requirements, IEEE 802.3aq 10GBASE-LRM requirements and SFP+ requirements. The EDC engine is automatic and will adapt in real-time to compensate for dispersion in the transport medium. No external control is required but manual modes are available. The EDC Engine is not used in 1.25Gbps mode.

Unique features of the EDC engine include:

Compensation in excess of the 10GBASE-LRM Standard, allowing reliable transmission over MMF fibers >220 meters in length with PIE-D exceeding 4.5dBm.

- High-performance, dynamic-tracking operation that offers instantaneous correction for dynamic response changes due to environmental factors (fiber vibration, thermal shifts, and other effects).

- Micro-controller software-based EDC algorithm allows for field upgrades and/or user added-value functionality.

#### Overview

The EDC equalizer employs a multi-tap Feed-Forward Equalizer (FFE) and Decision-Feedback Equalizer (DFE) architecture. The basic EDC block diagram is illustrated in Figure 12 below. The following sections cover the blocks in more detail.

Figure 12: Data Path Block Diagram

## **Linear Equalizer**

The input stage contains a linear equalizer. The linear equalizer provides an adaptable frequency gain profile to compensate for frequency-dependent loss. It provides a programmable amount of gain at a high frequency relative to a low frequency.

#### **Automatic Gain Control**

The input stage includes a variable gain stage (AGC) that allows the chip to accept a range of input amplitudes. The AGC controls the overall gain of the input stage such that the amplitude into the EDC block is set to a fixed amplitude that is optimized for EDC operation.

## **Adaptive Equalizer**

The adaptive equalizer employs a multi-tap Feed Forward Equalizer (FFE) and a multi-tap Decision Feedback Equalizer (DFE) to correct signal impairments caused by the transmission channel response.

## Feed-Forward Equalizer (FFE)<sup>1</sup>

The FFE block sends the data signal to multiple taps. Each tap adds a fixed amount of propagation delay relative to the previous tap, resulting in N equally spaced tap signals. Each tap output is adjusted by a tap weighting factor. The outputs are then summed to generate a combined signal.

#### **VGA**

The Variable Gain Amplifier (VGA) adjusts the FFE signal amplitude to provide an optimal signal level to the DFE.

#### Decision Feedback Equalizer (DFE)

The DFE block consists of a summing node, a data slicer, and multiple feedback tap paths. The summing node sums the input data with weighted values of previous data decisions. The slicer makes a digital decision on the resultant signal from the summer. The multiple taps are progressively delayed by a fixed amount.

#### **EDC Correlation Algorithm**

The FFE and DFE tap weights are controlled by an EDC Correlation Algorithm. This optimizes the tap weights by minimizing the correlation between data bits in the signal that cause ISI.

### **Equalization Control and Monitoring**

The QT2225 provides a number of features for inservice or test-and-evaluation control and monitoring of the equalization functions.

All receiver optimization features can be monitored and controlled via the standard I2C and MDIO register interfaces. Upon device power up, default settings for the EDC algorithms are configured by the device firmware supplied by AMCC and generally will not need to be modified. Automatic update of these settings can be disabled and frozen and manual settings can be applied as desired. Refer to the register map for details.

<sup>1.</sup> The use of the FFE and DFE taps is controlled by firmware to optimize power and performance.

## **KR Interface**

The QT2225 has fully 802.3ap compliant 10GBASE-KR receive and transmit interfaces. Clause 73 Autonegotiation is supported on the backplane interface, allowing datarate negotiation between 10Gbps and 1.25Gbps with the link partner. 1000BASE-KX protocol is supported (but 10GBASE-KX4 is not supported). The product also supports Link Training and in-band FEC for 10Gbps channels.

#### 10GBASE-KR Receiver

The 10BGASE-KR receiver uses the EDC engine described on page 26. The VGA has sufficient gain and range to accommodate the supported signalling levels at the FRXIN/P inputs for backplane applications.

#### **KR Transmitter**

The KR transmitter contains a 3-tap FIR driver. The driver is fully described in "10Gbps Interface" on page 23. The driver is capable of variable pre-cursor and post-cursor emphasis based on the tap coefficients provided to it by the KR training algorithm. The driver is capable of driving both +ve and -ve FIR tap coefficients. The dynamic range of V1 (pre-cursor level), V2 (steady state level) and V3 (post-cursor level) exceed that required by IEEE 802.3ap Subclause 72.7.1.10.

The transmitter tap settings are automatically optimized for the backplane channel by the IEEE 802.3 Clause 72 Link Training protocol, described on page 33. The tap coefficients can be manually overridden if desired through the MDIO interface.

## **Auto-Negotiation**

Auto-Negotiation (AN) is defined in Clause 73 of IEEE 802.3ap. This function allows this device to advertise modes of operation to another device at the remote end of an ethernet link across a backplane and to detect corresponding operational modes the other device may be advertising.

The device will select a mode of operation based on the operating mode agreed upon with the link partner during Arbitration. This will always be the highest protocol level advertised by both link partners. Any additional features or modes supported by both link partners will also be enabled. A simplified Auto-negotiation flow chart is shown in Figure 13 on page 28. The operating mode is determined in the Negotiation phase. If the negotiation is successful at finding a common supported operating mode, the chip will send traffic at 1Gbps or attempt link training at 10Gbps (based on the negotiation outcome). If the negotiation is unsuccessful the chip will attempt parallel detection at 1Gbps on the serial input.

Once a successful link is established, the chip will stay in the tracking state (either 1G or 10G). The chip will reenter the Negotiation phase when a major fault is detected e.g. lose link partner.

Figure 13: Simplified Auto-Negotiation State Diagram

#### **MDIO Access**

All Auto-negotiation functions are accessed through MDIO registers in logical device 7.

#### **Auto-Negotiation Pages**

The Auto-Negotiation messaging is transmitted within a differential Manchester encoded (DME) page. The differential Manchester encoding ensures a high transition density.

A DME page consists of a page delimiter field, a 48-bit Link Codeword field and a single bit from a pseudorandom sequence.

#### Manchester Violation Delimiter

The page delimiter field is called a Manchester violation (MV) delimiter and marks the start of each DME page. The MV delimiter is 8 bit positions long with a transition in position 1 and 5 only.

#### Link Codeword

The 48-bit Link Codeword field is used to communicate with the link partner and negotiate the supported protocol. Each bit is DME encoded.

#### DME Page Bit 49 Randomizer

The 49th bit to be transmitted is DME encoded and is generated by a pseudo-random number generator defined by the polynomial  $g(x) = x^7 + x^3 + 1$  implemented using a linear feedback shift register