## FAST TRANSIENT 3.5A STEP-DOWN CONVERTER

## Description

The PAM2325 is a 3.5A step-down synchronous converter. The 1.2MHz switching frequency enables the use of small external components. The ultra-small 2mm x 2mm footprint and high efficiency make the PAM2325 an ideal choice for portable applications.

The PAM2325 delivers 3.5A maximum output current while consuming only 55 $\mu$ A no load quiescent current. Low R integrated MOSFETs and 100% duty cycle operation make the PAM2325 the ideal choice for high output voltage, high current applications which require a low dropout threshold.

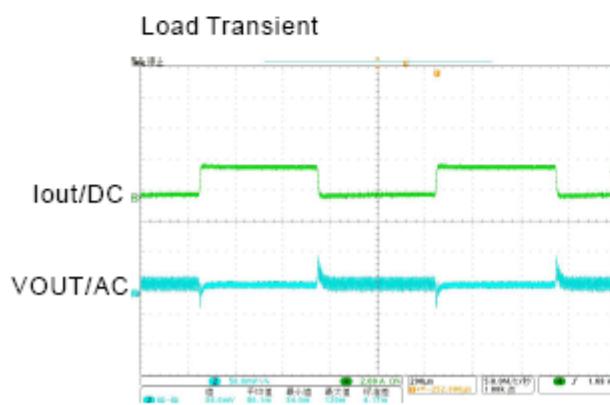

The PAM2325 provides excellent transient response and output accuracy across the operating range.

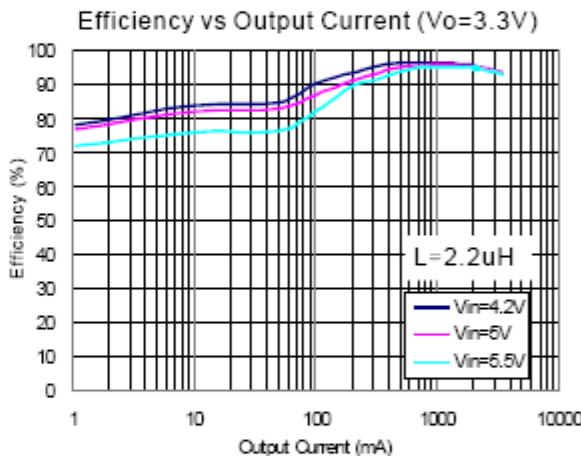

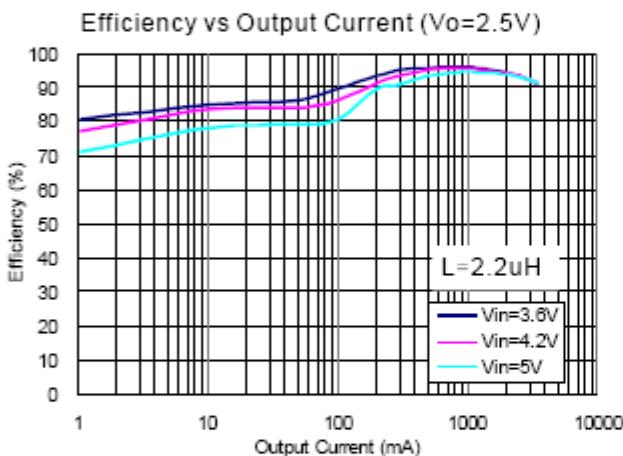

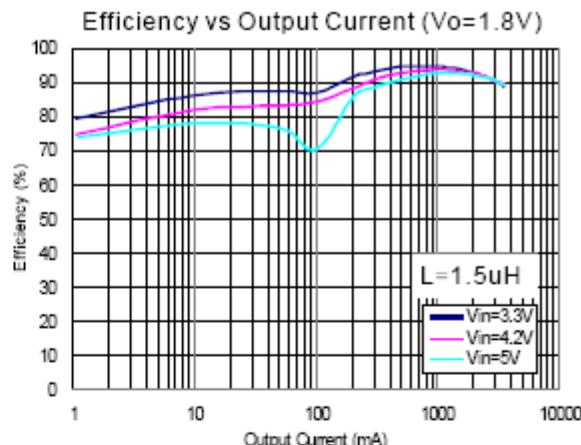

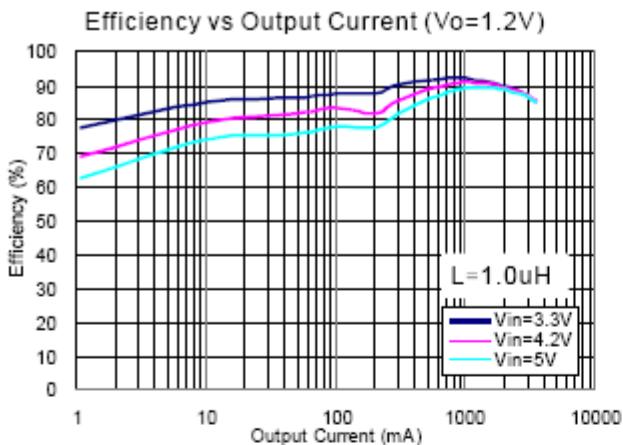

The PAM2325 maintains high efficiency throughout the load range.

The PAM2325 automatically optimizes efficiency during light load mode (PSM) and maintains constant frequency and low output ripple during PWM mode.

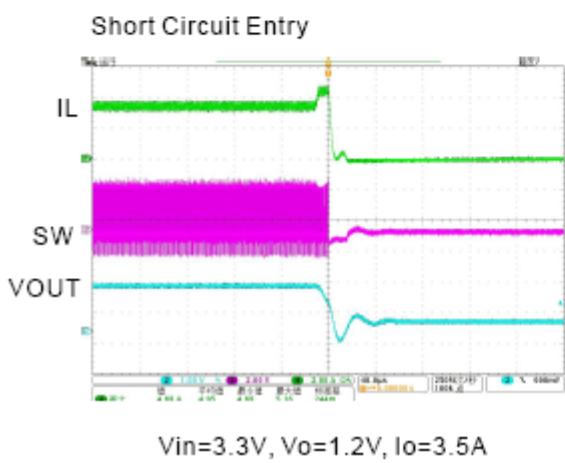

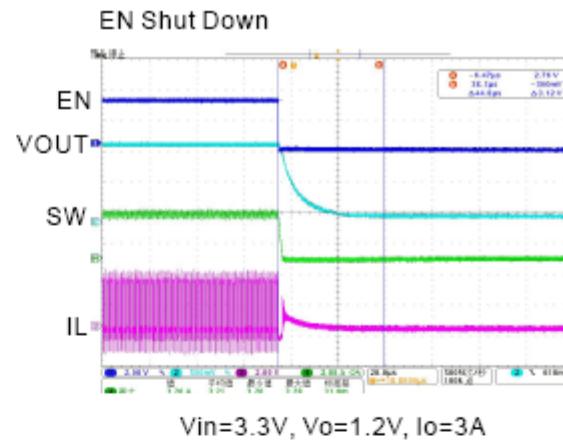

Over-temperature and short circuit protection safeguard the PAM2325 and system components from damage.

The PAM2325 is available in an ultra-small QFN2x2-12 package. The product is rated over a temperature range of -40°C to +85°C.

## Applications

- Cellular Phone

- Digital Cameras

- Hard Disk Drives

- MP3 Players

- PDAs and Handheld Computers

- Portable Media Players

- USB Devices

- Wireless Network Cards

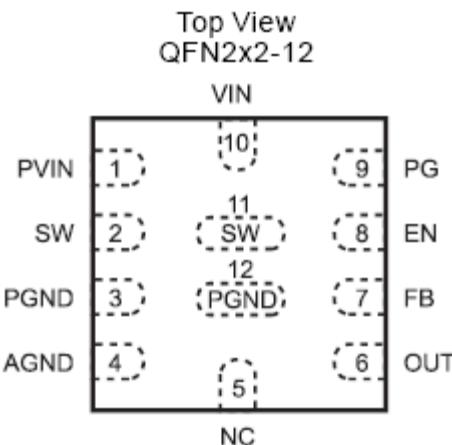

## Pin Assignments

## Features

- 3.5A Maximum Output Current

- Tiny 1.0 $\mu$ H Chip Inductor

- Excellent Transient Response

- Input Voltage: 2.5V to 5.5V

- Adjustable Output Voltage: 1.0V to 4.0V

- High Efficiency with 1.2MHz Switching Frequency

- 55 $\mu$ A No Load Quiescent Current

- 100% Duty Cycle Low-Dropout Operation

- Internal Soft Start

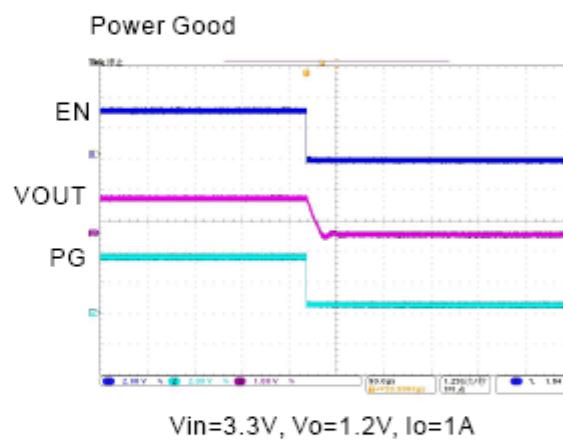

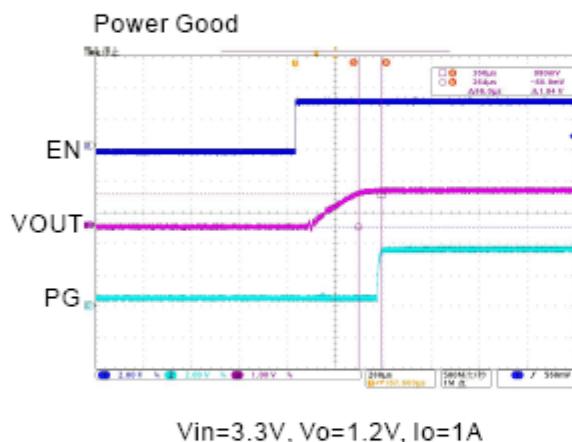

- Power Good Indicator

- Over-Temperature and Current Limit Protection

- Hiccup mode for output short protection

- 1 $\mu$ A Shutdown Current

- -40°C to +85°C Temperature Range

- Available in QFN2x2-12 Package

- RoHS/REACH Compliant

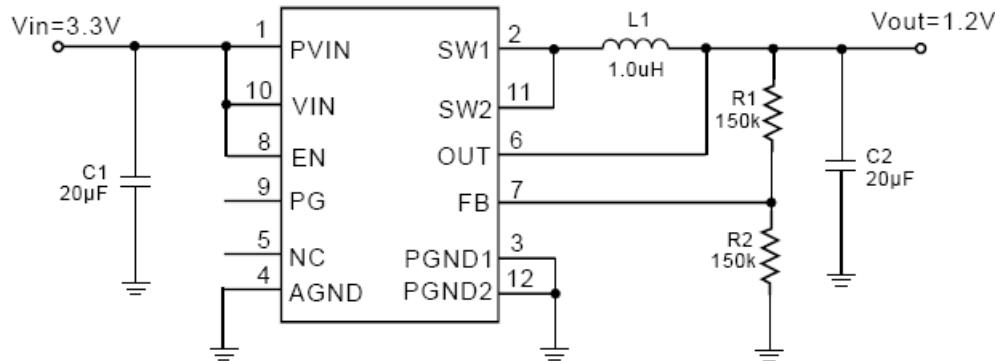

## Typical Applications Circuit

## Pin Descriptions

| Pin Number | Pin Name | Function                                                                                                                                                                                                    |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | PVIN     | Supply Voltage to power FETs. PVIN is connected to VIN internally.                                                                                                                                          |

| 2, 11      | SW       | Switch Output. Pin 2 and 11 can be connected together.                                                                                                                                                      |

| 3, 12      | PGND     | Power Ground. Pin 3 and 12 can be connected together.                                                                                                                                                       |

| 4          | AGND     | Quiet ground for controller circuits                                                                                                                                                                        |

| 5          | NC       | Leave this pin open. Do not connect it to ground.                                                                                                                                                           |

| 6          | OUT      | Input sense pin for output voltage                                                                                                                                                                          |

| 7          | FB       | Feedback. An external resistor divider from the output to GND, tapped to the FB pin, sets the output voltage.                                                                                               |

| 8          | EN       | On/Off Control.                                                                                                                                                                                             |

| 9          | PG       | Power Good Indicator. The output of this pin is an open drain with internal pull up resistor to VIN. PG is pulled up to VIN when the FB voltage is within 10% of the regulation level, otherwise it is LOW. |

| 10         | VIN      | Supply Voltage to internal control circuitry. VIN is connected to PVIN internally.                                                                                                                          |

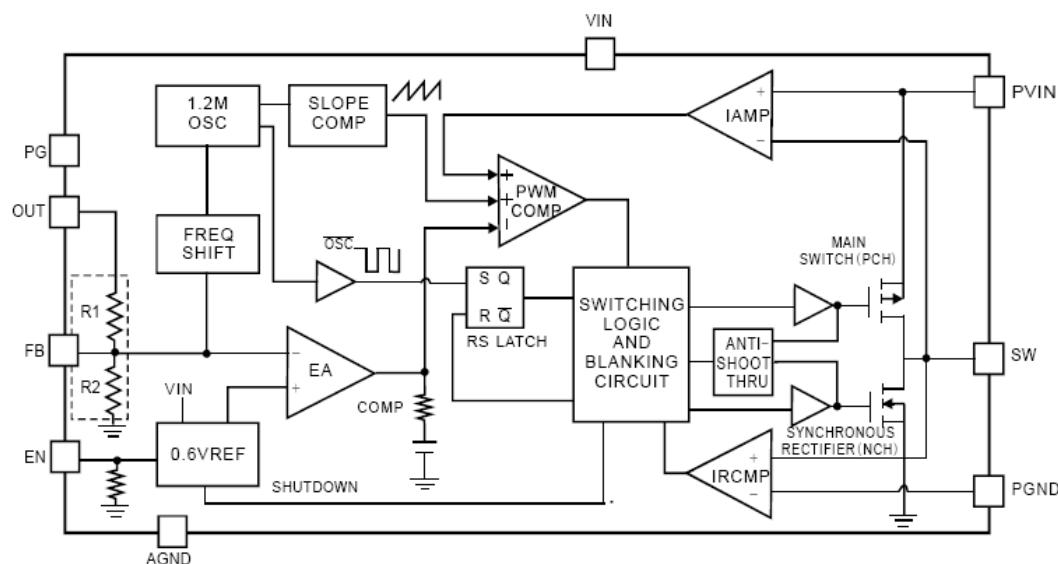

## Functional Block Diagram

---

**Absolute Maximum Ratings** (@ $T_A = +25^\circ\text{C}$ , unless otherwise specified.)

---

These are stress ratings only and functional operation is not implied. Exposure to absolute maximum ratings for prolonged time periods may affect device reliability. All voltages are with respect to ground.

| Parameter                 | Rating                     | Unit             |

|---------------------------|----------------------------|------------------|

| Input Voltage             | -0.3 to +6.5               | V                |

| EN, FB Pin Voltage        | -0.3 to $V_{IN}$           | V                |

| SW Pin Voltage            | -0.3 to ( $V_{IN} + 0.3$ ) | V                |

| Junction Temperature      | 150                        | $^\circ\text{C}$ |

| Storage Temperature Range | -65 to +150                | $^\circ\text{C}$ |

| Soldering Temperature     | 300, 5sec                  | $^\circ\text{C}$ |

---

**Recommended Operating Conditions** (@ $T_A = +25^\circ\text{C}$ , unless otherwise specified.)

---

| Parameter                   | Rating      | Unit             |

|-----------------------------|-------------|------------------|

| Supply Voltage              | 2.5 to 5.5  | V                |

| Operation Temperature Range | -40 to +85  | $^\circ\text{C}$ |

| Junction Temperature Range  | -40 to +125 | $^\circ\text{C}$ |

---

**Thermal Information**

---

| Parameter                                | Symbol        | Package   | Max | Unit               |

|------------------------------------------|---------------|-----------|-----|--------------------|

| Thermal Resistance (Junction to Case)    | $\theta_{JC}$ | QFN2x2-12 | 16  |                    |

| Thermal Resistance (Junction to Ambient) | $\theta_{JA}$ | QFN2x2-12 | 80  | $^\circ\text{C/W}$ |

## Electrical Characteristics

(@ $T_A = +25^\circ\text{C}$ ,  $V_{IN} = 3.3\text{V}$ ,  $V_{OUT} = 1.2\text{V}$ ,  $C_{IN} = 20\mu\text{F}$ ,  $C_O = 20\mu\text{F}$ ,  $L = 1\mu\text{H}$ , unless otherwise specified.)

| Parameter                                        | Symbol       | Test Conditions                              |          | Min   | Typ      | Max   | Units            |

|--------------------------------------------------|--------------|----------------------------------------------|----------|-------|----------|-------|------------------|

| Input Voltage Range                              | $V_{IN}$     |                                              |          | 2.5   | 3.3      | 5.5   | V                |

| UVLO Threshold                                   | $V_{UVLO}$   | $V_{IN}$ Rising                              |          | 2.35  | 2.5      | 2.65  | V                |

|                                                  |              | Hysteresis                                   |          |       | 400      | 550   | mV               |

| Output Voltage Accuracy                          | $V_{OUT}$    |                                              |          | -4.0  |          | +4.0  | %                |

| Regulated Feedback Voltage                       | $V_{FB}$     | No Load                                      |          | 0.591 | 0.60     | 0.609 | V                |

| PMOS Current Limit                               | $I_{LIM}$    |                                              |          |       | 4.8      |       | A                |

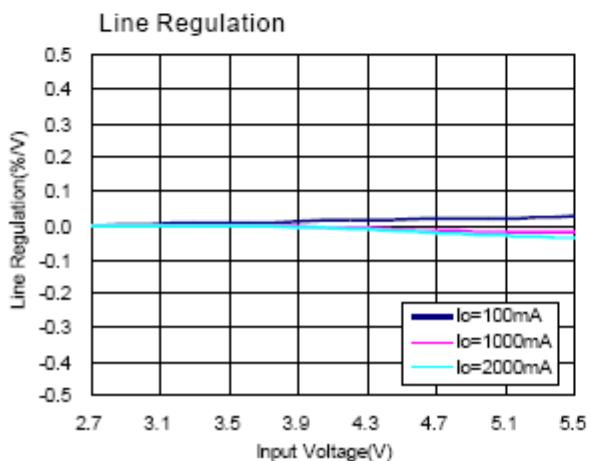

| Output Voltage Line Regulation                   | $LNR$        | $V_{IN} = 3.3\text{V}$ to $5.5\text{V}$      |          |       | 0.5      | 1     | %/V              |

| Output Voltage Load Regulation                   | $LDR$        | $I_O = 1\text{mA}$ to $2\text{A}$            |          |       |          | 2     | %                |

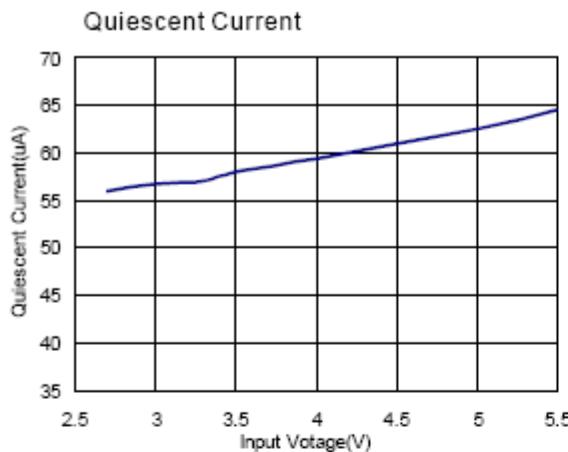

| Quiescent Current                                | $I_Q$        | No Load                                      |          |       | 55       | 100   | $\mu\text{A}$    |

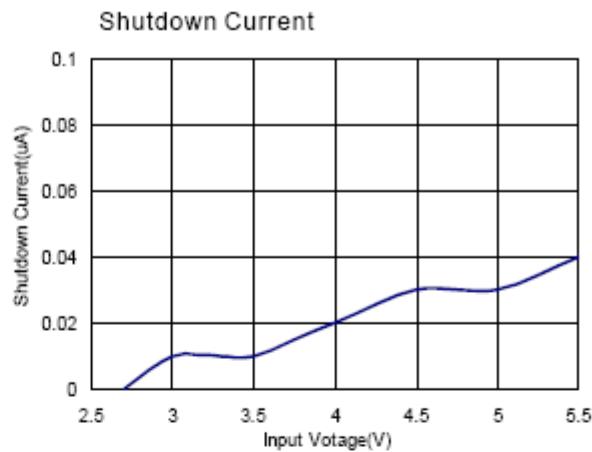

| Shutdown Current                                 | $I_{SD}$     | $V_{EN} = 0\text{V}$                         |          |       |          | 1     | $\mu\text{A}$    |

| Oscillator Frequency                             | $f_{osc}$    |                                              |          | 1.0   | 1.2      | 1.6   | MHz              |

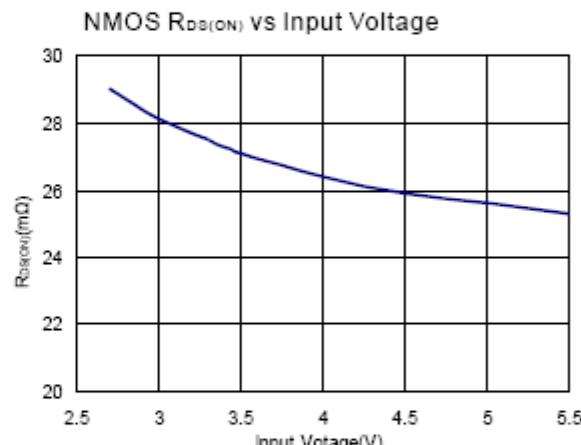

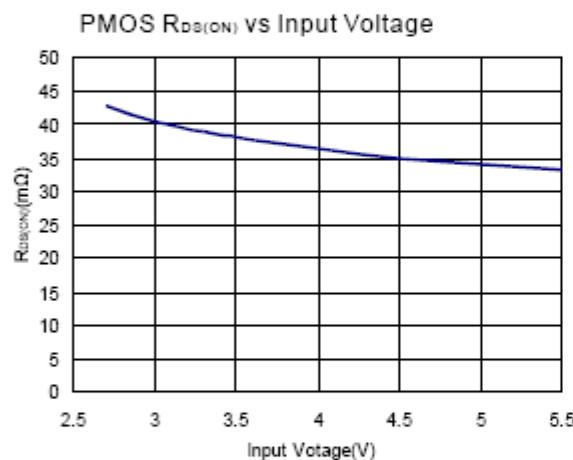

| Drain-Source On-State Resistance                 | $R_{DS(ON)}$ | $I_{DS} = 100\text{mA}$                      | P MOSFET |       | 40       | 70    | $\text{m}\Omega$ |

|                                                  |              |                                              | N MOSFET |       | 30       | 50    | $\text{m}\Omega$ |

| SW Leakage Current                               | $I_{LSW}$    |                                              |          |       |          | 1     | $\mu\text{A}$    |

| Start-Up Time                                    | $t_s$        |                                              |          |       | 250      | 1000  | $\mu\text{s}$    |

| PSM Threshold                                    | $I_{TH}$     | $V_{IN} = 3.3\text{V}$ , $V_O = 1.2\text{V}$ |          |       |          | 250   | mA               |

| EN Threshold High                                | $V_{EH}$     |                                              |          | 1.2   |          |       | V                |

| EN Threshold Low                                 | $V_{EL}$     |                                              |          |       |          | 0.4   | V                |

| EN Input Current                                 | $I_{EN}$     | $V_{EN} = 2\text{V}$                         |          |       | 1.2      | 4     | $\mu\text{A}$    |

| Over Temperature Protection                      | OTP          |                                              |          |       | 150      |       | $^\circ\text{C}$ |

| OTP Hysteresis                                   | OTH          |                                              |          |       | 30       |       | $^\circ\text{C}$ |

| Effciency                                        | $\eta$       | $I_O = 10\text{mA}$                          |          | 75    | 81       |       |                  |

|                                                  |              | $I_O = 500\text{mA}$ to $1\text{A}$          |          | 85    | 90       |       | %                |

|                                                  |              | $I_O = 1.5\text{A}$                          |          | 85    | 90       |       |                  |

|                                                  |              | $I_O = 2\text{A}$                            |          | 80    | 89       |       |                  |

| Output Ripple                                    | Ripple       | $I_O = 10\text{mA}$                          |          | -5    |          | +5    | %                |

|                                                  |              | $I_O \geq 300\text{mA}$                      |          | -2    |          | +2    |                  |

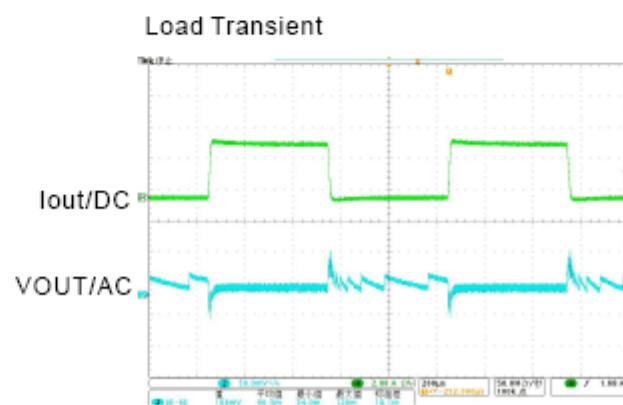

| Output Transient Ripple                          | $V_{PK-PK}$  | $I_O = 20\text{mA}$ to $1\text{A}$           |          | -10   |          | +10   | %                |

|                                                  |              | $I_O = 20\text{mA}$ to $2\text{A}$           |          | -12   |          | +12   |                  |

| PG Pin Trigger Delay                             |              |                                              |          |       | 90       |       | $\mu\text{s}$    |

| PG Pin Threshold (relative to $V_{OUT}$ )        |              |                                              |          |       | $\pm 10$ |       | %                |

| PG Open Drain Impedance<br>( $PG = PV_{IN}$ )    |              |                                              |          | 250K  | 500K     |       | $\Omega$         |

| PG Open Drain Impedance<br>( $PG = \text{Low}$ ) |              |                                              |          |       |          | 100   | $\Omega$         |

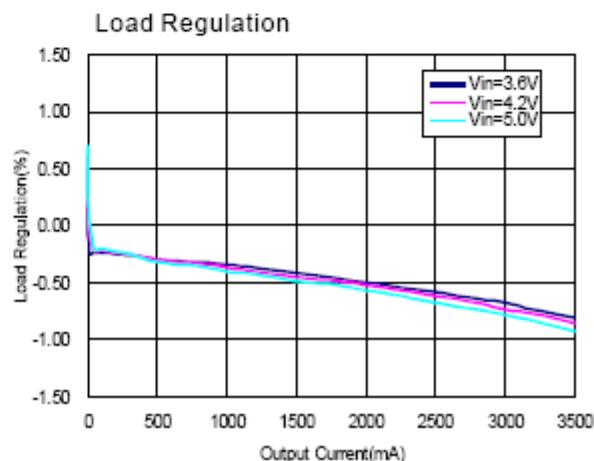

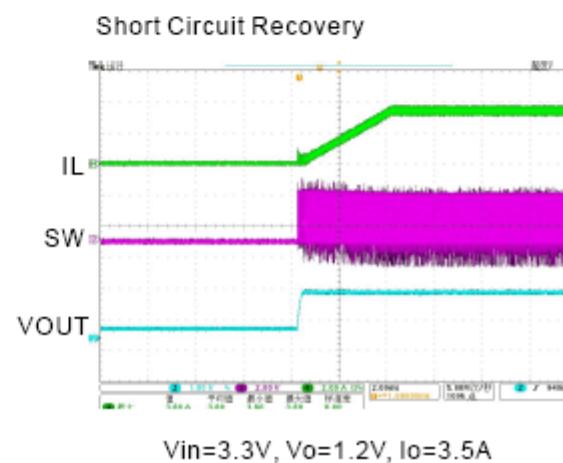

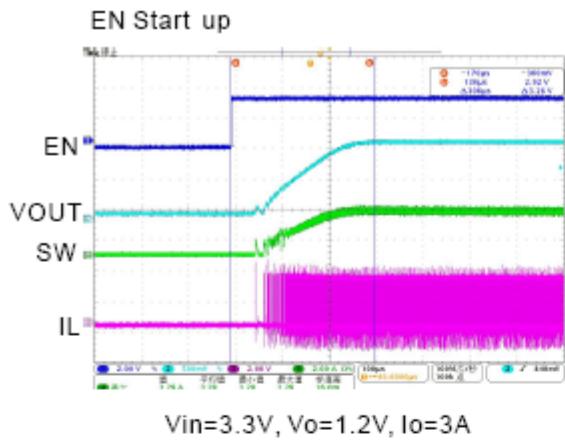

**Typical Performance Characteristics** (@ $T_A = +25^\circ\text{C}$ ,  $C_{IN} = 20\mu\text{F}$ ,  $C_O = 20\mu\text{F}$ ,  $V_O = 1.2\text{V}$ , unless otherwise specified.)

**Typical Performance Characteristics** (cont.) (@ $T_A = +25^\circ\text{C}$ ,  $C_{IN} = 10\mu\text{F}$ ,  $C_O = 10\mu\text{F}$ ,  $V_O = 1.2\text{V}$ , unless otherwise specified.)

$V_{IN} = 3.3\text{V}$ ,  $V_O = 1.2\text{V}$ ,  $I_O = 0.2\text{A} \sim 2\text{A}$ ,  $f = 1\text{kHz}$

$V_{IN} = 3.3\text{V}$ ,  $V_O = 1.2\text{V}$ ,  $I_O = 0\text{A} \sim 3.5\text{A}$ ,  $f = 1\text{kHz}$

**Typical Performance Characteristics (cont.) (@ $T_A = +25^\circ\text{C}$ ,  $C_{IN} = 10\mu\text{F}$ ,  $C_O = 10\mu\text{F}$ ,  $V_O = 1.2\text{V}$ , unless otherwise specified.)**

## Application Information

The basic PAM2325 application circuit is shown on Page 1. External component selection is determined by the load requirement, selecting L first and then  $C_{IN}$  and  $C_{OUT}$ .

### Inductor Selection

For most applications, the value of the inductor will fall in the range of  $1\mu H$  to  $3.3\mu H$ . Its value is chosen based on the desired ripple current. Large value inductors lower ripple current and small value inductors result in higher ripple currents. Higher  $V_{IN}$  or  $V_{OUT}$  also increases the ripple current as shown in equation 3.5A reasonable starting point for setting ripple current is  $\Delta I_L = 1.4A$  (40% of 3.5A).

$$\Delta I_L = \frac{1}{(f)(L)} V_{OUT} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right) \quad (1)$$

The DC current rating of the inductor should be at least equal to the maximum load current plus half the ripple current to prevent core saturation. Thus, a 4.2A rated inductor should be enough for most applications ( $3.5A + 0.7A$ ). For better efficiency, choose a low DC-resistance inductor.

### $C_{IN}$ and $C_{OUT}$ Selection

In continuous mode, the source current of the top MOSFET is a square wave of duty cycle  $V_{OUT}/V_{IN}$ . To prevent large voltage transients, a low ESR input capacitor sized for the maximum RMS current must be used. The maximum RMS capacitor current is given by:

$$C_{IN \text{ required}} I_{RMS} \approx I_{OMAX} \frac{[V_{OUT}(V_{IN} - V_{OUT})]^{1/2}}{V_{IN}}$$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT}/2$ . This simple worst -case condition is commonly used for design because even significant deviations do not offer much relief. Note that the capacitor manufacturer's ripple current ratings are often based on 2000 hours of life. This makes it advisable to further derate the capacitor, or choose a capacitor rated at a higher temperature than required. Consult the manufacturer if there is any question.

The selection of  $C_{OUT}$  is driven by the required effective series resistance (ESR).

Typically, once the ESR requirement for  $C_{OUT}$  has been met, the RMS current rating generally far exceeds the  $I_{RIPPLE}$  (P-P) requirement. The output ripple  $\Delta V_{OUT}$  is determined by:

$$\Delta V_{OUT} \approx \Delta I_L (ESR + 1/8fC_{OUT})$$

Where  $f$  = operating frequency,  $C_{OUT}$  = output capacitance and  $\Delta I_L$  = ripple current in the inductor. For a fixed output voltage, the output ripple is highest at maximum input voltage since  $\Delta I_L$  increases with input voltage.

### Using Ceramic Input and Output Capacitors

Higher values, lower cost ceramic capacitors are now becoming available in smaller case sizes. Their high ripple current, high voltage rating and low ESR make them ideal for switching regulator applications. Using ceramic capacitors can achieve very low output ripple and small circuit size.

When choosing the input and output ceramic capacitors, choose the X5R or X7R dielectric formulations. These dielectrics have the best temperature and voltage characteristics of all the ceramics for a given value and size.

### Thermal Consideration

Thermal protection limits power dissipation in the PAM2325. When the junction temperature exceeds  $+150^{\circ}C$ , the OTP (Over Temperature Protection) starts the thermal shutdown and turns the pass transistor off. The pass transistor resumes operation after the junction temperature drops below  $120^{\circ}C$ .

For continuous operation, the junction temperature should be maintained below  $125^{\circ}C$ . The power dissipation is defined as:

$$P_D = I_{O}^2 \frac{V_O R_{DS(ON)H} + (V_{IN} - V_O) R_{DS(ON)L}}{V_{IN}} + (t_{SW} F_s I_{O} + I_Q) V_{IN}$$

$I_Q$  is the step-down converter quiescent current. The term  $t_{SW}$  is used to estimate the full load step-down converter switching losses.

For the condition where the step-down converter is in dropout at 100% duty cycle, the total device dissipation reduces to:

$$P_D = I_{O}^2 R_{DS(ON)H} + I_Q V_{IN}$$

## Application Information (cont.)

### Thermal Consideration (cont.)

Since  $R_{DS(ON)}$ , quiescent current, and switching losses all vary with input voltage, the total losses should be investigated over the complete input voltage range. The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surrounding airflow and temperature difference between junction and ambient. The maximum power dissipation can be calculated by the following formula:

$$P_D = \frac{T_{J(MAX)} - T_A}{\theta_{JA}}$$

Where  $T_{J(MAX)}$  is the maximum allowable junction temperature 125°C.  $T$  is the ambient temperature and  $\theta_{JA}$  is the thermal resistance from the junction to the ambient. Based on the standard JEDEC for a two layer thermal test board, the thermal resistance  $\theta_{JA}$  of QFN2X2-12 80°C/W respectively. The maximum power dissipation at  $T_A = +25^\circ\text{C}$  can be calculated by following formula:

$$P_D = (125^\circ\text{C} - 25^\circ\text{C}) / 80^\circ\text{C/W} = 1.25\text{W}$$

### Setting the Output Voltage

The internal reference is 0.6V (Typical). The output voltage is calculated as below:

The output voltage is given by Table 1.

$$V_O = 0.6 \times \left(1 + \frac{R1}{R2}\right)$$

**Table 1:** Resistor selection for output voltage setting.

| <b>V<sub>O</sub></b> | <b>R1</b> | <b>R2</b> |

|----------------------|-----------|-----------|

| 1.2V                 | 150k      | 150k      |

| 1.5V                 | 150k      | 100k      |

| 1.8V                 | 300k      | 150k      |

| 2.5V                 | 380k      | 120k      |

| 3.3V                 | 680k      | 150k      |

### Pulse Skipping Mode (PSM) Description

When load current decreases, the peak switch current in Power-PMOS will be lower than skip current threshold and the device will enter into Pulse Skipping Mode.

In this mode, the device has two states, working state and idle state. First, the device enters into working state control led by internal error amplifier. When the feedback voltage gets higher than internal reference voltage, the device will enter into low I<sub>DS</sub> idle state with most of internal blocks disabled. The output voltage will be reduced by loading or leakage current. When the feedback voltage gets lower than the internal reference voltage, the convertor will start a working state again.

### 100% Duty Cycle Operation

As the input voltage approaches the output voltage, the converter turns the P-Channel transistor continuously on. In this mode the output voltage is equal to the input voltage minus the voltage drop across the P-Channel transistor:

$$V_{OUT} = V_{IN} - I_{LOAD} (R_{DS(ON)} + R_L)$$

where  $R_{DS(ON)}$  = P-Channel switch ON resistance,  $I_{LOAD}$  = Output current,  $R_L$  = Inductor DC resistance.

### UVLO and Soft-Start

The reference and the circuit remain reset until the  $V_{IN}$  crosses its UVLO threshold. The PAM2325 has an internal soft-start circuit that limits the in-rush current during start-up.

This prevents possible voltage drops of the input voltage and eliminates the output voltage overshoot.

### Hiccup Mode Short Circuit Control

When the converter output is shorted or the device is overloaded, each high-side MOSFET current-limit event turns off the high-side MOSFET and turns on the low-side MOSFET. An internal counter is used to count the each current-limit event. The counter is reset after consecutive high-side MOSFETs turn on without reaching current limit. If the current-limit condition persists, the counter fills up. The control logic then stops both high-side and lowside MOSFETs and waits for a hiccup period, before attempting a new soft-start sequence. The counter bit is decided by  $V_{FB}$  voltage. If  $V_{FB} \leq 0.2$ , the counter is 3-bit counter; if  $V_{FB} > 0.2$  the counter is 6-bit counter. The typical hiccup mode duty cycle is 1.7%. The hiccup mode is disable during soft-start time.

---

**Application Information (cont.)**

---

**Thermal Shutdown**

When the die temperature exceeds +150°C, a reset occurs and the reset remains until the temperature decrease to +120°C, at which time the circuit can be restarted.

---

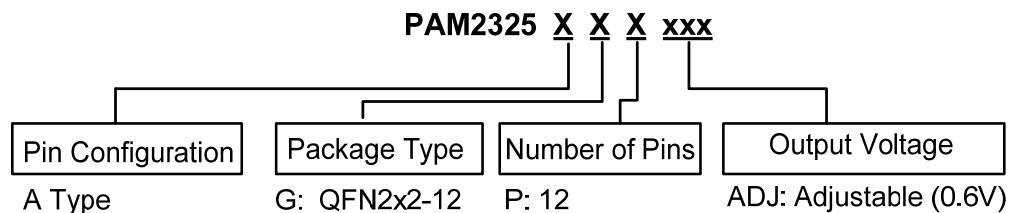

**Ordering Information**

---

| Part Number   | Output Voltage | Part Type | Standard Package       |

|---------------|----------------|-----------|------------------------|

| PAM2325AGPADJ | CLVXYW         | QFN2x2-12 | 3000 Units/Tape & Reel |

---

**Marking Information**

---

CL: Product Code

of PAM2325

V: Output Voltage

X: Internal Code

Y: Year

W: Week

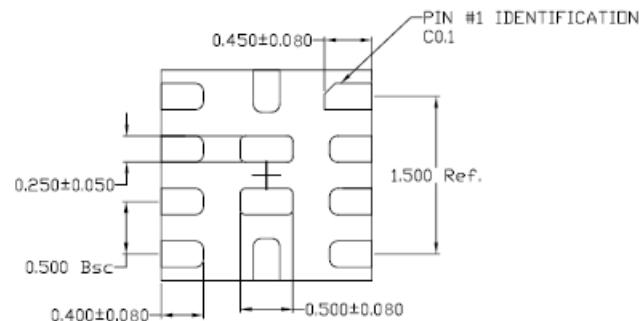

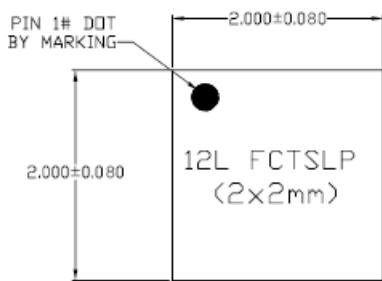

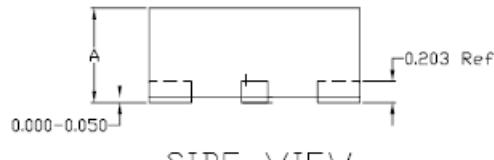

**Package Outline Dimensions** (All dimensions in mm.)

QFN2x2-12

TOP VIEW

BOTTOM VIEW

NOTE:

1). 'A' DIMENSION AS BELOW TABLE

| A | TSLP |       |

|---|------|-------|

|   | MAX. | 0.800 |

|   | NOM. | 0.750 |

|   | MIN. | 0.700 |

SIDE VIEW

**IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

**LIFE SUPPORT**

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2013, Diodes Incorporated

[www.diodes.com](http://www.diodes.com)