## 700 mA dual DC-DC converter for powering AMOLED displays

Datasheet — production data

#### **Features**

- Step-down and inverter converters

- Operating input voltage range from 6 V to 13 V

- Synchronous rectification for both converters

- 700 mA output current

- Fixed positive voltage 4.6 V

- Programmable negative voltage by S<sub>WIRE</sub> from 2.4 V to 6.0 V

- Typical efficiency 85%

- PWM mode controller @ 1.6 MHz switching frequency

- Enable pin for shutdown mode

- Low quiescent current in shutdown mode

- Soft-start with inrush current protection

- Short-circuit protection on positive output

- Overtemperature protection

- Temperature range 40 °C to 85 °C

- True shutdown mode

- Fast output discharge after shutdown

- Package DFN 4x4 mm 12 leads 0.75 mm height, 0.5 mm pitch

### **Applications**

- Digital photo frames

- Ultra mobile PCs

- Mobile Internet devices

- Digital still cameras / camcorders

- Portable media players / DVD players

### **Description**

The STOD14 is a dual channel DC-DC converter driver for medium-sized AMOLED display panels. It integrates a step-down and an inverting converter in a compact IC design. The excellent efficiency makes it particularly suitable for battery operated products. The high frequency operation allows the value and size of external components to be reduced.

The positive output voltage is fixed at 4.6 V with very high current capability and is generated using a buck converter. The negative output is programmable by an external MCU through a dedicated pin which implements single-wire protocol, with values from - 2.4 to - 6.0 V.

Soft-start with controlled inrush current limit, load disconnect and thermal shutdown are integrated functions of the device.

Table 1. Device summary

| Order code | Positive voltage | Negative voltage   | Package           | Packaging           |

|------------|------------------|--------------------|-------------------|---------------------|

| STOD14PUR  | 4.6 V            | - 2.4 V to - 6.0 V | DFN12L (4 x 4 mm) | 3000 parts per reel |

Contents STOD14

# **Contents**

| 1 | Sche  | matic 3                                |

|---|-------|----------------------------------------|

| 2 | Pin c | onfiguration                           |

| 3 | Maxi  | mum ratings                            |

| 4 | Elect | rical characteristics7                 |

| 5 | Туріс | cal performance characteristics9       |

| 6 | Appl  | ication Information11                  |

|   | 6.1   | Inductor selection                     |

|   | 6.2   | Input and output capacitor selection   |

|   | 6.3   | Recommended PCB layout                 |

| 7 | Deta  | iled description                       |

|   | 7.1   | Mode of operation                      |

|   | 7.2   | Enable pin                             |

|   | 7.3   | Soft-start and inrush current limiting |

|   | 7.4   | Startup sequence                       |

|   | 7.5   | Fast discharge 14                      |

|   | 7.6   | Undervoltage lockout                   |

|   | 7.7   | Overtemperature protection             |

|   | 7.8   | Short-circuit startup detection (SSD)  |

|   | 7.9   | Overload protection (OLP)              |

|   | 7.10  | Short-circuit protection (SCP)         |

|   | 7.11  | S-WIRE protocol description            |

|   | 7.12  | Enable and S-WIRE operation            |

|   | 7.13  | Programming negative output voltage    |

| 8 | Pack  | age mechanical data                    |

| 9 | Revi  | sion history                           |

STOD14 Schematic

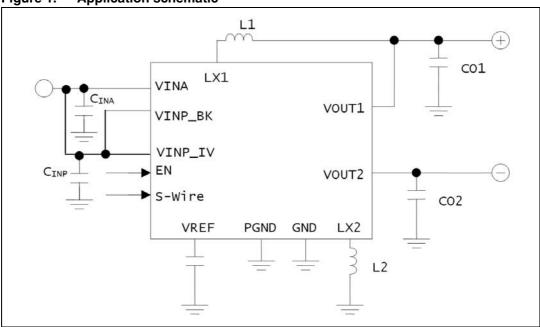

## 1 Schematic

Figure 1. Application schematic

Table 2. Typical external components

|                  | Typical external compensition |                       |                         |             |                              |  |  |  |

|------------------|-------------------------------|-----------------------|-------------------------|-------------|------------------------------|--|--|--|

| Description      | Manufacturer                  | Part number           | Value                   | Size        | Ratings                      |  |  |  |

| L <sub>1</sub>   | Coilcraft                     | LPS4012-472MLB        | 4.7 µH                  | 4 x 4 x 1.2 | 1.6 A / 1.8 A <sup>(1)</sup> |  |  |  |

| L <sub>2</sub>   | Coilcraft                     | LPS4012-472MLB        | 4.7 μH                  | 4 x 4 x 1.2 | 1.6 A / 1.8 A <sup>(1)</sup> |  |  |  |

| C <sub>INA</sub> | Murata                        | GRM21BR61C106KE15L    | 10 μF                   | 0805        | X5R, 16 V                    |  |  |  |

| C <sub>INP</sub> | Murata                        | 2x GRM21BR61C106KE15L | 2x 10 μF <sup>(2)</sup> | 0805        | X5R, 16 V                    |  |  |  |

| C <sub>O1</sub>  | Murata                        | 2x GRM21BR61C106KE15L | 2x 10 μF                | 0805        | X5R, 16 V                    |  |  |  |

| C <sub>O2</sub>  | Murata                        | 2x GRM21BR61C106KE15L | 2x 10 μF                | 0805        | X5R, 16 V                    |  |  |  |

| C <sub>REF</sub> | Murata                        | GRM185R60J105KE26D    | 1.0 μF                  | 0603        | X5R, 6.3 V                   |  |  |  |

<sup>1.</sup>  $I_{SAT}$  10% drop / 30% drop.

Note: All the above components refer to the typical application performance characteristics. Operation of the device is not limited to the choice of these external components.

<sup>2.</sup> Doubled  $C_{\mbox{\scriptsize INP}}$  useful at low temperatures.

Schematic STOD14

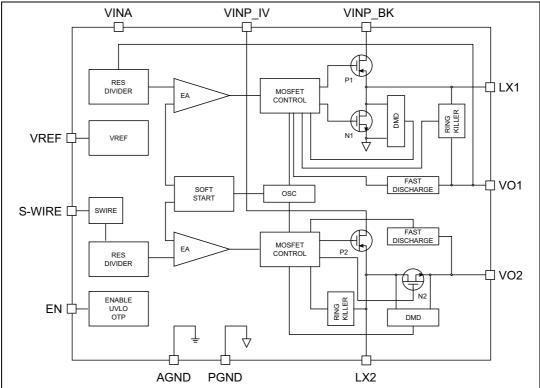

Figure 2. Block schematic

STOD14 Pin configuration

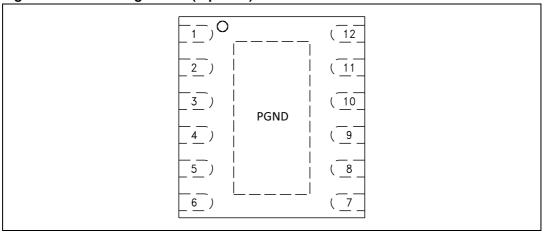

# 2 Pin configuration

Figure 3. Pin configuration (top view)

Table 3. Pin description

| Symbol            | Pin    | Description                                                                                                            |  |

|-------------------|--------|------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>O2</sub>   | 1      | Inverting converter output voltage (negative)                                                                          |  |

| LX2               | 2      | Switching node of the inverting converter                                                                              |  |

| V <sub>inIV</sub> | 3      | Power input supply voltage for inverting converter                                                                     |  |

| V <sub>inBK</sub> | 4      | Power input supply voltage for step-down converter                                                                     |  |

| LX1               | 5      | Switching node of the step-down converter                                                                              |  |

| PGND              | 6      | Power ground pin                                                                                                       |  |

| V <sub>O1</sub>   | 7      | Step-down converter output voltage (positive)                                                                          |  |

| AGND              | 8      | Signal ground pin. This pin must be connected to power ground pin                                                      |  |

| S <sub>WIRE</sub> | 9      | S- <sub>WIRE</sub> pin                                                                                                 |  |

| V <sub>inA</sub>  | 10     | Analog input supply voltage                                                                                            |  |

| EN                | 11     | Enable control pin. ON = HIGH. When pulled low, puts the device into shutdown mode                                     |  |

| V <sub>REF</sub>  | 12     | Voltage reference output. Connect 1 μF bypass capacitor between this pin and AGND                                      |  |

| EXPOSE            | ED PAD | Exposed pad must be connected to AGND and PGND in the PCB layout in order to guarantee proper operation of the device. |  |

Maximum ratings STOD14

# 3 Maximum ratings

Table 4. Absolute maximum ratings

| Symbol                | Parameter                             | Value              | Unit |

|-----------------------|---------------------------------------|--------------------|------|

| VinA, VinIV,<br>VinBK | DC supply voltage                     | - 0.3 to 13.5      | V    |

| EN, S <sub>WIRE</sub> | Enable pin, S- <sub>WIRE</sub> pin    | - 0.3 to 4.6       | V    |

| ILx2                  | Inverting converter switching current | Internally limited | Α    |

| Lx2                   | Inverting converter switching node    | - 6.5 to VINP +0.3 | V    |

| VO2                   | Inverting converter output voltage    | - 6.0 to GND +0.3  | V    |

| VO1                   | Step-down converter output voltage    | - 0.3 to 6         | V    |

| Lx1                   | Step-down converter switching node    | - 0.3 to VINP +0.3 | V    |

| ILx1                  | Step-down converter switching current | Internally limited | Α    |

| VREF                  | Reference voltage                     | - 0.3 to 3         | V    |

| PD                    | Power dissipation                     | Internally limited | mW   |

| T <sub>STG</sub>      | Storage temperature range             | - 65 to 150        | °C   |

| TJ                    | Maximum junction temperature          | 150                | °C   |

| ESD                   | Human body model ESD protection       | 2                  | kV   |

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

Table 5. Thermal data

| Symbol            | Parameter                                   | Value | Unit |

|-------------------|---------------------------------------------|-------|------|

| R <sub>thJA</sub> | Thermal resistance junction-ambient (1)     | 33    | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction-case (FR-4 PCB) | 1.64  | °C/W |

<sup>1.</sup> The package is mounted on a 4-layer (2S2P) JEDEC board as per JESD51-7 and JESD51-5.

# 4 Electrical characteristics

$T_A$  = 25 °C,  $V_{INA}$  =  $V_{INP}$  = 9.0 V,  $I_{O1,2}$  = 150 mA,  $C_{IN}$  = 10  $\mu\text{F},\,C_{O1,2}$  = 22  $\mu\text{F},\,C_{REF}$  = 1  $\mu\text{F},\,L1$  = 4.7  $\mu\text{H},\,L2$  = 4.7  $\mu\text{H},\,V_{EN}$  = High,  $V_{O1}$  = 4.6 V,  $V_{O2}$  = -4.9 V, unless otherwise specified.

Table 6. Electrical characteristics

| Symbol              | Parameter                                             | Test conditions                                                                                                        | Min.       | Тур.  | Max.  | Unit |  |

|---------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------|-------|-------|------|--|

| V <sub>IN</sub>     | Operating input voltage range                         | T <sub>A</sub> = - 40 to 85 °C                                                                                         | 6          |       | 13    | V    |  |

| UVLO_H              | Undervoltage lockout<br>HIGH                          | V <sub>INA</sub> rising, T <sub>A</sub> = -40 to 85 °C                                                                 |            | 5     | 5.2   | ٧    |  |

| UVLO_L              | Undervoltage lockout<br>LOW                           | $V_{INA}$ falling, $T_A = -40$ to 85 °C                                                                                | 4.6        | 4.8   |       | V    |  |

| I_V <sub>I</sub>    | Input current                                         | No load condition $(I_V_I = I_{INA} + I_{INP})$                                                                        |            | 30    |       | mA   |  |

| I <sub>Q_SH</sub>   | Shutdown current                                      | $V_{EN} = GND, (I_{Q\_SH} = I_{INA} + I_{INP})$                                                                        |            |       | 5     | μΑ   |  |

| V <sub>EN</sub> H   | Enable HIGH threshold                                 | $V_{INA} = 6 \text{ V to } 13 \text{ V}, T_A = -40 \text{ to } 85 \text{ °C}$ 1.2                                      |            |       |       | V    |  |

| V <sub>EN</sub> L   | Enable LOW threshold                                  | V <sub>INA</sub> = 6 V to 13 V, T <sub>A</sub> = -40 to 85 °C                                                          |            |       | 0.4   | V    |  |

| I <sub>EN</sub>     | Enable input current                                  | $V_{EN} = V_{IN}$                                                                                                      |            |       | 1     | μΑ   |  |

| F <sub>SW</sub>     | Frequency                                             | PWM mode, T <sub>A</sub> = -40 to 85 °C                                                                                | 1.44       | 1.6   | 1.76  | MHz  |  |

| D1 <sub>MAX</sub>   | 1 <sub>MAX</sub> Step-down maximum duty cycle No load |                                                                                                                        |            | 90    |       | %    |  |

| D2 <sub>MAX</sub>   | 2 <sub>MAX</sub> Inverting maximum duty cycle No load |                                                                                                                        | 90         |       | %     |      |  |

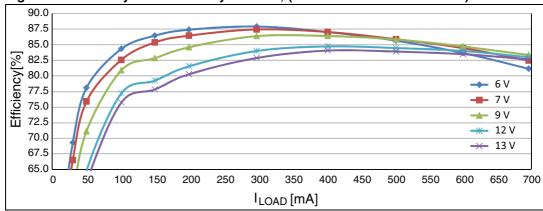

| n                   | Total system officionay                               | I <sub>O1,2</sub> = 10 to 150 mA<br>V <sub>O1</sub> =4.6 V, V <sub>O2</sub> =-4.9 V                                    | see figure |       | %     |      |  |

| η                   | Total system efficiency                               | I <sub>O1,2</sub> =150 to 700 mA<br>V <sub>O1</sub> =4.6 V, V <sub>O2</sub> =-4.9 V                                    |            | 85    |       | %    |  |

| V <sub>REF</sub>    | Voltage reference                                     | I <sub>REF</sub> = 10 μA                                                                                               | 1.198      | 1.211 | 1.222 | V    |  |

| I <sub>REF</sub>    | Voltage reference current capability                  | At V <sub>REF</sub> = V <sub>REF</sub> - 1.5%                                                                          | 100        |       |       | μΑ   |  |

| Step-down o         | converter section                                     |                                                                                                                        |            |       |       |      |  |

| V <sub>O1</sub>     | Output voltage                                        | V <sub>INA</sub> =6 V to 13 V, I <sub>O1</sub> =5 mA to 700 mA, T <sub>A</sub> =-40 °C to 85 °C                        | 4.55       | 4.6   | 4.65  | ٧    |  |

| A) /                | Otatia lina na natatian (1)                           | $\rm V_{INA}{=}6~V~to~13~V,~I_{O1}{=}5~mA~I_{O2}~no$ load; $\rm T_{A}{=}{-}40~^{\circ}C~to~85~^{\circ}C$               |            | 0.5   |       | 0/   |  |

| ΔV <sub>O1 SL</sub> | Static line regulation <sup>(1)</sup>                 | $\rm V_{INA}{=}6~V~to~13~V,~I_{O1}{=}700~mA~I_{O2}~no~load,~T_{A}{=}{-}40~^{\circ}C~to~85~^{\circ}C$                   |            | 0.5   |       | %    |  |

| 417                 | Chatia land a contain (2)                             | $\rm I_{O1}{=}5$ to 700 mA, $\rm I_{O2}$ no load, $\rm V_{INA}{=}6$ V; $\rm T_{A}{=}{-}40~^{\circ}C$ to 85 $^{\circ}C$ |            | 1     |       | 0/   |  |

| $\Delta V_{O1}$     | Static load regulation (2)                            | I <sub>O1</sub> =5 to 700 mA, I <sub>O2</sub> no load,<br>V <sub>INA</sub> =13 V; T <sub>A</sub> =-40 °C to 85 °C      |            | 1     |       | %    |  |

| I <sub>O1</sub>     | Maximum step-down output current                      | V <sub>I</sub> =6 V to 13 V                                                                                            | 700        |       |       | mA   |  |

Electrical characteristics STOD14

Table 6. Electrical characteristics (continued)

| Symbol               | Parameter                             | Test conditions                                                                                                   | Min. | Тур. | Max. | Unit |

|----------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| I-L <sub>1MAX</sub>  | Inductor peak current                 | V <sub>O1</sub> below 10% of nominal value                                                                        | 1.2  |      |      | Α    |

| R <sub>DSON</sub> P1 |                                       | T <sub>A</sub> = -40 to 85 °C                                                                                     |      | 0.2  | 0.5  | Ω    |

| R <sub>DSON</sub> N1 |                                       | T <sub>A</sub> = -40 to 85 °C                                                                                     |      | 0.18 | 0.5  | Ω    |

| Inverting co         | nverter section                       |                                                                                                                   |      |      |      |      |

|                      | Output negative voltage range         | 41 discrete values with 100 mV steps set by S <sub>WIRE</sub> pin                                                 | -6.0 |      | -2.4 | V    |

| $V_{O2}$             | Default value                         | Default output voltage                                                                                            |      | -4.9 |      | V    |

|                      | Accuracy                              | Output voltage variation on the nominal value                                                                     | -1.4 |      | +1.4 | %    |

| 41/                  | Static line regulation (3)            | $V_{\rm INA}$ =6 V to 13 V, $I_{\rm O2}$ =5 mA $I_{\rm O1}$ no load; $T_{\rm A}$ =-40 °C to 85 °C                 |      | 1    |      | %    |

| ∆V <sub>O2 SL</sub>  | Static line regulation (*)            | $\rm V_{INA}$ =6 V to 13 V, $\rm I_{O2}$ =700 mA $\rm I_{O1}$ no load, $\rm T_A$ =-40 °C to 85 °C                 |      | 1    |      | 70   |

|                      | Static load regulation (4)            | $I_{O2}$ =5 to 700 mA, $I_{O1}$ no load, $V_{INA}$ =6 V; $T_A$ =-40 °C to 85 °C                                   |      | 1    |      | 9/   |

| $\Delta V_{O2}$      | Static load regulation V              | I <sub>O2</sub> =5 to 700 mA, I <sub>O1</sub> no load,<br>V <sub>INA</sub> =13 V; T <sub>A</sub> =-40 °C to 85 °C |      | 1    |      | %    |

| I <sub>O2</sub>      | Maximum inverting output current      | V <sub>INA</sub> =6 V to 13 V                                                                                     | -700 |      |      | mA   |

| I-L <sub>2MAX</sub>  | Inductor peak current                 | V <sub>O2</sub> below 10% of nominal value                                                                        |      |      | -2.0 | Α    |

| R <sub>DSON</sub> P2 |                                       | T <sub>A</sub> = -40 to 85 °C                                                                                     |      | 0.17 | 0.5  | Ω    |

| R <sub>DSON</sub> N2 |                                       | $T_A = -40 \text{ to } 85 ^{\circ}\text{C}$                                                                       |      | 0.16 | 0.5  | Ω    |

| Thermal shu          | utdown                                |                                                                                                                   |      |      |      |      |

| OTP                  | Overtemperature protection            |                                                                                                                   |      | 150  |      | °C   |

| OTP <sub>HYST</sub>  | Overtemperature protection hysteresis |                                                                                                                   |      | 15   |      | °C   |

| Discharge re         | esistor                               |                                                                                                                   |      |      |      |      |

| R <sub>DIS</sub>     | Discharge resistor value              |                                                                                                                   |      | 300  |      | Ω    |

| T <sub>DIS</sub>     | Discharge time                        | No load, from 90% to 10%                                                                                          |      | 15   |      | ms   |

|                      | •                                     |                                                                                                                   |      |      |      |      |

<sup>1.</sup> [(VO1MAX - VO1MIN) / (VO1 @ 25 °C and VINA,P = 6 V)] x 100.

<sup>2.</sup> [(VO1MAX - VO1MIN) / (VO1 @ 25 °C and IO1 = 5 mA)] x 100.

<sup>3.</sup> [(VO2MAX - VO2MIN) / (VO2 @ 25 °C and VINA,P = 6 V)] x 100.

<sup>4.</sup> [(VO2MAX - VO2MIN) / (VO2 @ 25 °C and IO2 = 5 mA)] x 100.

# 5 Typical performance characteristics

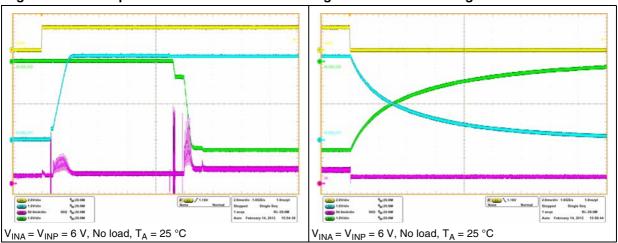

Figure 5. Startup and inrush current

Figure 6. Fast discharge

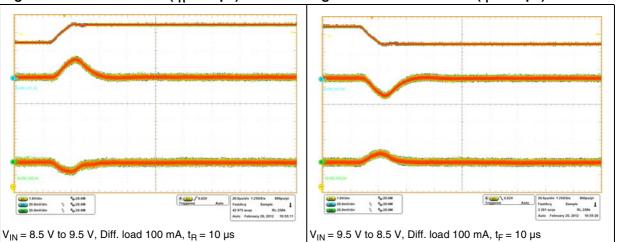

Figure 7. Line transient ( $t_R = 10 \mu s$ )

Figure 8. Line transient ( $t_F = 10 \mu s$ )

577

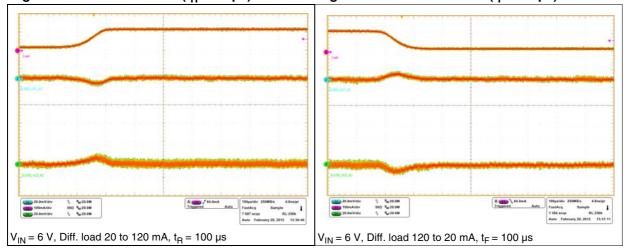

Figure 9. Load transient ( $t_R = 10 \mu s$ )

Figure 10. Load transient ( $t_F = 10 \mu s$ )

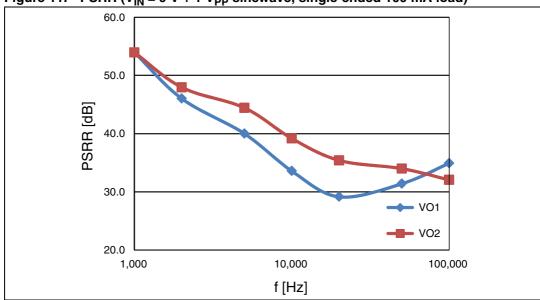

Figure 11. PSRR ( $V_{IN}$  = 9 V + 1  $V_{PP}$  sinewave, single-ended 100 mA load)

Table 7. PSRR

| f [Hz]  | PSRR_VO1 [dB] | PSRR_VO2 [dB] |

|---------|---------------|---------------|

| 10      | > 60          | > 60          |

| 100     | > 60          | > 60          |

| 1 000   | 54            | 54            |

| 2 000   | 46            | 48            |

| 5 000   | 40            | 44            |

| 10 000  | 34            | 39            |

| 20 000  | 29            | 35            |

| 50 000  | 31            | 34            |

| 100 000 | 35            | 32            |

### 6 Application Information

#### 6.1 Inductor selection

The inductor is the key passive component for switching converters.

For the step-down converter an inductance between 3.3  $\mu$ H and 6.8  $\mu$ H is recommended. For the inverting stage the suggested inductance ranges from 3.3  $\mu$ H to 4.7  $\mu$ H.

It is very important to select a proper inductor according to the maximum current the inductor can handle in order to avoid saturation. The peak current for the step-down and the inverting can be calculated with the following formulas:

#### **Equation 1**

$$I_{PEAK\_BUCK} = \frac{V_{O1} \cdot (1 - V_{O1} / V_{IN})}{2 \cdot f_s \cdot L_1} + I_{O}$$

#### **Equation 2**

$$I_{PEAK\_INV} = \frac{V_{IN} \cdot V_{O2}}{2 \cdot f_s \cdot L_2(V_{O2} - V_{IN})} + \frac{I_O\left(V_{IN} - V_{O2}\right)}{\eta_2 \cdot V_{IN}}$$

where

V<sub>O1</sub> is step-down output voltage

V<sub>O2</sub> is inverting output voltage including sign

IO is output current for both DC-DC converters

V<sub>IN</sub> is input voltage; use minimum of operating voltage

f<sub>s</sub> is switching frequency; use the minimum value of 1.44 MHz for worst case

η is inverter efficiency; typ. 85%

L1 is buck inductor value; including tolerance

L2 is inverter inductor value; including tolerance.

### 6.2 Input and output capacitor selection

It is recommended to use ceramic capacitors with low ESR as input and output capacitors in order to filter any disturbance present in the input line and to get stable operation for the switching converters.

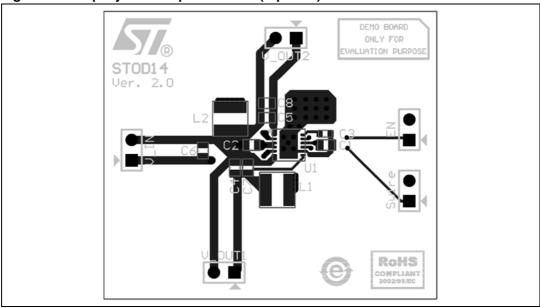

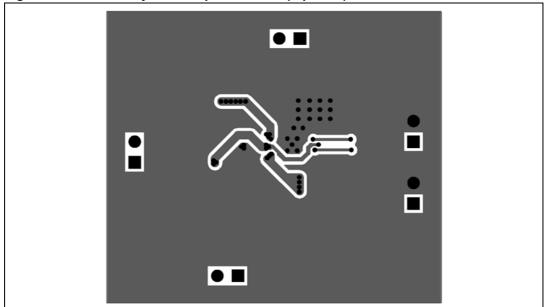

### 6.3 Recommended PCB layout

The STOD14 is a high frequency power switching device so it requires a proper PCB layout in order to obtain the necessary stability and optimize line/load regulation and output voltage ripple. Analog input ( $V_{INA}$ ) and power input ( $V_{INP}$ ) must be kept separated and connected together at the  $C_{IN}$  pad only. The input capacitor must be as close as possible to the IC. To minimize the ground noise, a common ground node for power ground and a different one for analog ground must be used. The exposed pad is connected to AGND through vias.

Figure 12. Top layer and top silkscreen (top view)

Figure 13. Bottom layer and top silkscreen (top view)

STOD14 Detailed description

### 7 Detailed description

The STOD14 is a high efficiency dual DC-DC converter which integrates a step-down and inverting power stage suitable for supplying AMOLED panels.

Thanks to the high level of integration it needs only 6 external components to operate and it achieves very high efficiency using a synchronous rectification technique for both the DC-DC converters.

The controller uses an average current mode technique in order to obtain good stability and precise voltage regulation in all possible conditions of input voltage, output voltage and output current. In addition, the peak inductor current is monitored in order to avoid inductor saturation.

The STOD14 avoids battery leakage thanks to the true-shutdown feature and it is self protected from overtemperature. Undervoltage lockout and soft-start guarantee proper operation during startup.

### 7.1 Mode of operation

To guarantee the minimal output voltage ripple, the device works just in continuous conduction mode (CCM). In this mode, reverse current pulses flowing back to the power supply can appear, especially at low load.

### 7.2 Enable pin

The device operates when the Enable pin is set high. If the Enable pin is set low, the device stops switching, and all the internal blocks are turned off. In addition, the internal switches are in an OFF state so the load is electrically disconnected from the input. This avoids unwanted current leakage from the input to the load.

When the EN is pulled high, the P1 switch is turned on for 100  $\mu$ s. In normal operation, during this time, apart of a small drop due to parasitic resistance,  $V_{O1}$  reaches  $V_{IN}$ . After 100  $\mu$ s, if  $V_{O1}$  stays below  $V_{IN}$ , the P1 is turned off and stays off until a new pulse is applied to EN. This mechanism avoids the device starting if a short-circuit is present on  $V_{O1}$ .

## 7.3 Soft-start and inrush current limiting

As a first step, the  $C_{O1}$  capacitor is charged, the P1 switch implements a current limiting technique in order to keep the charge current below 400 mA. This avoids battery overloading during startup.

After VO1 reaches VINP voltage level, the P1 switch is fully turned on and the soft-start procedure for the step-down is started.

After around 2 ms the soft-start for the inverting is started. The positive and negative voltage is under regulation around 6 ms after the Enable pin is asserted high.

## 7.4 Startup sequence

After the Enable pin is pulled high, or after a suitable voltage is applied to  $V_{INP}$ ,  $V_{INA}$  and the Enable pin, the device begins the startup phase. The positive and negative voltages are

Detailed description STOD14

under regulation about 10 ms after the Enable pin is asserted high. The short-circuit protection is designed to prevent overload, performing a dynamic current limitation on both output pins. At light load condition (up to 150 mA), the load can be connected during the startup phase. At medium/high load condition (above 150 mA), the proper sequence needs the startup phase to be entirely completed before connecting a load.

### 7.5 Fast discharge

When the device goes into shutdown mode and LX1 and LX2 stop switching, the discharge switch between  $V_{O1}$  and  $V_{IN}$  and the switch between  $V_{O2}$  and GND turn on and discharge the positive and the negative output voltages. After output voltages are discharged to zero, the switches turn off and the outputs stay in high impedance state.

### 7.6 Undervoltage lockout

The undervoltage lockout function avoids improper operation of the device when the input voltage is not high enough. When the input voltage is below the UVLO threshold, the device is in shutdown mode. The hysteresis avoids unstable operation at input voltage levels close to the UVLO threshold.

### 7.7 Overtemperature protection

An internal temperature sensor continuously monitors the IC junction temperature. If the temperature exceeds the specified value (see *Table 5*) the device stops operating. As soon as the temperature falls below the threshold (including hysteresis), normal operation is restored.

## 7.8 Short-circuit startup detection (SSD)

During device soft-start on positive output, an internal comparator checks load condition to detect eventual panel damage. In such case soft-start is stopped and the device is parked in power-off. To reset the normal functionality (assuming that the anomalous load condition was removed), it is necessary to restart the converter by an enable transient.

If no damage is detected during soft-start on the positive output, the startup procedure follows with negative output soft-start to reach, at the end, normal outputs functionality and voltages.

## 7.9 Overload protection (OLP)

Output current is internally limited. An overload condition, as a short-circuit between the two outputs or between each output and GND, produces the device power-off. To reset normal functionality (assuming that the short condition was removed), it is necessary to restart the converter by an enable transient.

## 7.10 Short-circuit protection (SCP)

When short-circuit occurs, the device is able to detect the voltage difference between  $V_{IN}$  and  $V_{OUT}$ . Overshoots are limited, decreasing the inductor current. After that, the output

STOD14 Detailed description

stages of the device are turned off. This status is maintained avoiding current flowing to the load. A new enable transition is needed to restart the device. The short-circuit protection is active during startup.

### 7.11 S-WIRE protocol description

Protocol to digitally communicate over a single cable with single-wire components.

#### Features and benefits

- Fully digital signal

- No handshake needed

- Protection against glitches and spikes though an internal low-pass filter acting on both rising and falling edges

- Uses a single-wire (plus analog ground) to accomplish both communication and power control transmission

- Simple design with an interface protocol that supplies control and signaling over a single-wire connection to set the output voltages.

#### S-WIRE protocol

- Single-wire protocol uses conventional CMOS/TTL logic levels (maximum 0.6 V for logic "zero" and a minimum 1.2 V for the logic "one") with operation specified over a supply voltage range of 2.5 V to 4.5 V

- Both master (MCU) and slave (this device) are configured to permit bit sequential data to flow only in one direction at a time; master initiates and controls the device

- Data is bit-sequential with a START bit and a STOP bit

- Signal is transferred in real time

- System clock is not required; each single-wire pulse is self-clocked by the oscillator integrated in the master and asserted valid within a frequency range of 250 kHz (maximum).

#### S-WIRF basic operations

The negative output voltage levels are selectable within a wide range (steps of 100 mV). The device can be enabled / disabled via S-WIRF in combination with the Enable pin.

## 7.12 Enable and S-WIRE operation

Both S-<sub>WIRE</sub> and Enable pins can be used to switch on and off the device. *Table 8* describes functionality for all combinations.

Table 8. EN and S-WIRE operation table

| EN   | S <sub>WIRE</sub> | Action                                |

|------|-------------------|---------------------------------------|

| Low  | Low               | Device off                            |

| Low  | High              | Negative output voltage set by S-WIRE |

| High | Low               | Default negative output voltage       |

| High | High              | Default negative output voltage       |

Detailed description STOD14

Note: Enable pin must be set to AGND while using the S-WIRE function.

# 7.13 Programming negative output voltage

Negative output voltage is set through the S-<sub>WIRE</sub> interface by providing a number of pulses according to the following table.

Table 9. Negative output voltage programming levels

| Bit clock | V <sub>O2</sub> (V) |

|-----------|---------------------|-----------|---------------------|-----------|---------------------|-----------|---------------------|-----------|---------------------|

| 1         | N/A                 | 11        | -5.4                | 21        | -4.4                | 31        | -3.4                | 41        | -2.4                |

| 2         | N/A                 | 12        | -5.3                | 22        | -4.3                | 32        | -3.3                |           |                     |

| 3         | N/A                 | 13        | -5.2                | 23        | -4.2                | 33        | -3.2                |           |                     |

| 4         | N/A                 | 14        | -5.1                | 24        | -4.1                | 34        | -3.1                |           |                     |

| 5         | -6.0                | 15        | -5.0                | 25        | -4.0                | 35        | -3.0                |           |                     |

| 6         | -5.9                | 16        | -4.9                | 26        | -3.9                | 36        | -2.9                |           |                     |

| 7         | -5.8                | 17        | -4.8                | 27        | -3.8                | 37        | -2.8                |           |                     |

| 8         | -5.7                | 18        | -4.7                | 28        | -3.7                | 38        | -2.7                |           |                     |

| 9         | -5.6                | 19        | -4.6                | 29        | -3.6                | 39        | -2.6                |           |                     |

| 10        | -5.5                | 20        | -4.5                | 30        | -3.5                | 40        | -2.5                |           |                     |

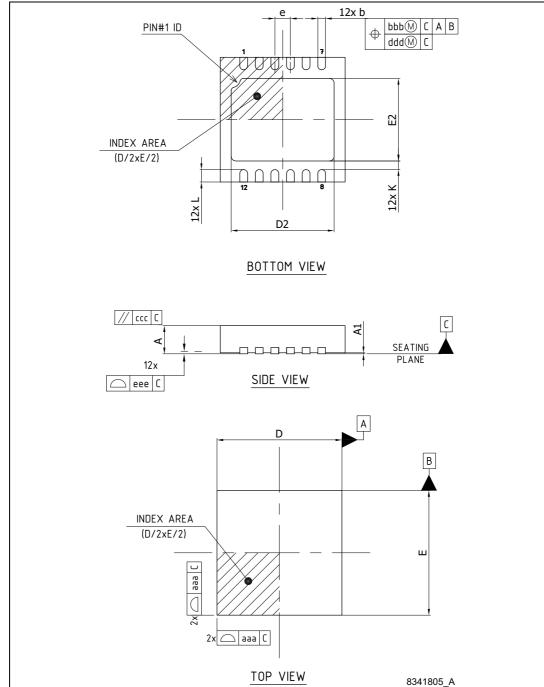

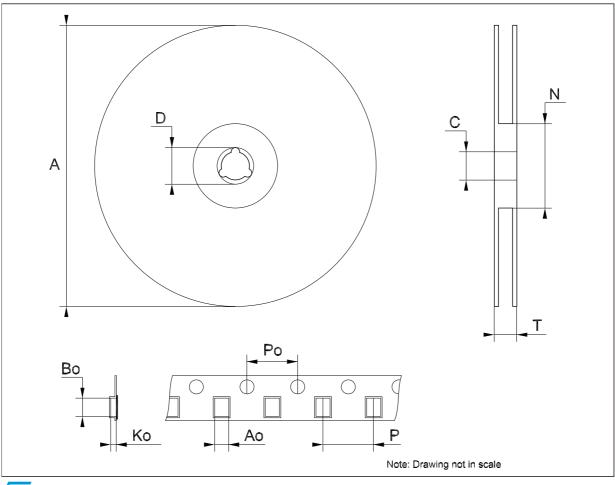

# 8 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

Table 10. DFN12L (4 x 4) mechanical data

| Dim.   | mm   |      |      |  |  |

|--------|------|------|------|--|--|

| Dilli. | Min. | Тур. | Max. |  |  |

| Α      | 0.70 | 0.75 | 0.80 |  |  |

| A1     | 0    | 0.02 | 0.05 |  |  |

| b      | 0.18 | 0.25 | 0.30 |  |  |

| D      |      | 4.0  |      |  |  |

| D2     | 3.15 | 3.30 | 3.40 |  |  |

| E      |      | 4.0  |      |  |  |

| E2     | 2.50 | 2.65 | 2.75 |  |  |

| е      |      | 0.5  |      |  |  |

| L      | 0.30 | 0.40 | 0.50 |  |  |

Figure 14. DFN12L (3 x 3) drawing

Tape & reel QFNxx/DFNxx (4x4) mechanical data

| Dim.   | mm.  |      |      | inch. |       |        |

|--------|------|------|------|-------|-------|--------|

| Dilli. | Min. | Тур. | Max. | Min.  | Тур.  | Max.   |

| А      |      |      | 330  |       |       | 12.992 |

| С      | 12.8 |      | 13.2 | 0.504 |       | 0.519  |

| D      | 20.2 |      |      | 0.795 |       |        |

| N      | 99   |      | 101  | 3.898 |       | 3.976  |

| Т      |      |      | 14.4 |       |       | 0.567  |

| Ao     |      | 4.35 |      |       | 0.171 |        |

| Во     |      | 4.35 |      |       | 0.171 |        |

| Ko     |      | 1.1  |      |       | 0.043 |        |

| Ро     |      | 4    |      |       | 0.157 |        |

| Р      |      | 8    |      |       | 0.315 |        |

3.40

Figure 15. DFN12L footprint recommended data (dimensions in millimeters)

STOD14 Revision history

# 9 Revision history

Table 11. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 16-Aug-2012 | 1        | Initial release. |

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2012 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

**577**

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics: STOD14PUR