www.ti.com

## MuxIt™ PLL FREQUENCY MULTIPLIER

#### **FEATURES**

- A Member of the MuxIt<sup>™</sup> Serializer-Deserializer Building-Block Chip Family

- Pin Selectable Frequency Multiplier Ratios Between 4 and 40

- Input Clock Frequencies From 5 to 50 MHz

- Multiplied Clock Frequencies up to 400 MHz

- Internal Loop Filters and Low PLL-Jitter of 20 ps RMS Typical at 200 MHz

- LVDS Compatible Differential Inputs and Outputs Meet or Exceed the Requirements of ANSI EIA/TIA-644-A

- LVTTL Compatible Inputs Are 5 V Tolerant

- LVDS Inputs and Outputs ESD Protection Exceeds 12 kV HBM

- Operates From a Single 3.3 V Supply

- Packaged in 28-Pin Thin Shrink Small-Outline Package With 26 mil Terminal Pitch

#### **SN65LVDS150 PW PACKAGE** (Marked as 65LVDS150) V<sub>CC</sub> 1 28 NC 27 NC CRI+ [ 2 26 NC CRI- [ 3 V<sub>T</sub> **∏** 4 25 V<sub>CC</sub> GND 5 24 GND 23 NC M1 **∏** 6 22 | GND M2 **∏** 7 M3 **∏** 8 21 NC М4 🛮 9 20 MCO+

19 MCO-

18 T GND

17 TEN

LCRO- 13 16 LCRO\_EN

LCRO+ 14 15 LVO

NC - No internal connection

M5 **□** 10

BSEL I 11

GND **1** 12

#### **DESCRIPTION**

The MuxIt is a family of general-purpose, multiple-chip building blocks for implementing parallel data serializers and deserializers. The system allows for wide parallel data to be transmitted through a reduced number of differential transmission lines over distances greater than can be achieved with a single-ended (e.g., LVTTL or LVCMOS) data interface. The number of bits multiplexed per transmission line is user selectable, allowing for higher transmission efficiencies than with other existing fixed ratio solutions. MuxIt utilizes the LVDS (TIA/EIA-644) low voltage differential signaling technology for communications between the data source and data destination.

The MuxIt family initially includes three devices supporting simplex communications; *The SN65LVDS150 Phase Locked Loop-Frequency Multiplier, The SN65LVDS151 Serializer-Transmitter,* and *The SN65LVDS152 Receiver-Deserializer.*

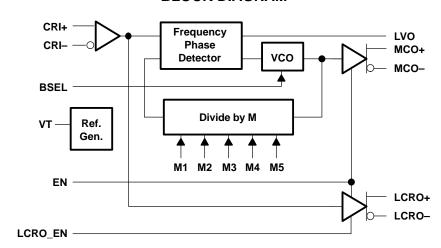

The SN65LVDS150 is a PLL based frequency multiplier designed for use with the other members of the MuxIt family of serializers and deserializers. The frequency multiplication ratio is pin selectable over a wide range of values from 4 through 40 to accommodate a broad spectrum of user needs. No external filter components are needed. A PLL lock indicator output is available which may be used to enable link data transfers.

The design of the SN65LVDS150 allows it to be used at either the transmit end or the receive end of the MuxIt serial link. The differential clock reference input (CRI) is driven by the system's parallel data clock when at the source end of the link, or by the link clock when at the destination end of the link. The differential clock reference input may be driven by either an LVDS differential signal, or by a single ended clock of either polarity. For single-ended use the nonclocked input is biased to the logic threshold voltage. A  $V_{\rm CC}/2$  threshold reference, VT, is provided on a pin adjacent the differential CRI pins for convenience when the input is used in a single-ended mode.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

MuxIt is a trademark of Texas Instruments.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DESCRIPTION (CONTINUED)**

The multiplied clock output (MCO) is an LVDS differential signal used to drive the high-speed shift registers in either the SN65LVDS151 serializer-transmitter or the SN65LVDS152 receiver-deserializer. The link clock reference output (LCRO) is an LVDS differential signal provided to the SN65LVDS151 serializer-transmitter for transmission over the link.

An internal power on reset and an enable input (EN) control the operation of the SN65LVDS150. When  $V_{CC}$  is below 1.5 V, or when EN is low, the device is in a low power disabled state and the MCO and LCRO differential outputs are in a high-impedance state. When  $V_{CC}$  is above 3 V and EN is high, the device and the two differential outputs are enabled and operating to specifications. The link clock reference output enable input (LCRO\_EN) is used to turn off the LCRO output when it is not being used. A band select input (BSEL) is used to optimize the VCO performance as a function of M-clock frequencies and M multiplier that is being used: The  $f_{max}$  parameter in the switching characteristic table includes details on the MCO frequency and choices of BSEL and M.

#### **BLOCK DIAGRAM**

# Frequency Multiplier Value Table (1)

| MULTIPLIER | M1 | M2 | M3 | M4 | M5 | RECOMMI<br>(MI          |                         |

|------------|----|----|----|----|----|-------------------------|-------------------------|

| (m)        |    |    |    |    | -  | BSEL = 0                | BSEL = 1                |

| 4          | L  | L  | L  | L  | L  | f <sub>IN</sub> < 12.50 | 12.50 ≤ f <sub>IN</sub> |

| Reserved   | L  | L  | L  | L  | Н  | NA                      | NA                      |

| 6          | L  | L  | L  | Н  | L  | f <sub>IN</sub> < 8.33  | $8.33 \le f_{IN}$       |

| Reserved   | L  | L  | L  | Н  | Н  | NA                      | NA                      |

| 8          | L  | L  | Н  | L  | L  | f <sub>IN</sub> < 12.50 | 12.50 ≤ f <sub>IN</sub> |

| 9          | L  | L  | Н  | L  | Н  | f <sub>IN</sub> < 11.11 | 11.11 ≤ f <sub>IN</sub> |

| 10         | L  | L  | Н  | Н  | L  | f <sub>IN</sub> < 10.00 | 10.00 ≤ f <sub>IN</sub> |

| Reserved   | L  | L  | Н  | Н  | Н  | NA                      | NA                      |

| 12         | L  | Н  | L  | L  | L  | f <sub>IN</sub> < 8.3   | 8.3 ≤ f <sub>IN</sub>   |

| 13         | L  | Н  | L  | L  | Н  | f <sub>IN</sub> < 7.7   | 7.7 ≤ f <sub>IN</sub>   |

| 14         | L  | Н  | L  | Н  | L  | f <sub>IN</sub> < 7.14  | 7.14 ≤ f <sub>IN</sub>  |

| 15         | L  | Н  | L  | Н  | Н  | f <sub>IN</sub> < 6.67  | 6.67 ≤ f <sub>IN</sub>  |

| 16         | L  | Н  | Н  | L  | L  | f <sub>IN</sub> < 6.25  | 6.25 ≤ f <sub>IN</sub>  |

| 17         | L  | Н  | Н  | L  | Н  | f <sub>IN</sub> < 5.88  | 5.88 ≤ f <sub>IN</sub>  |

| 18         | L  | Н  | Н  | Н  | L  | f <sub>IN</sub> < 5.56  | 5.56 ≤ f <sub>IN</sub>  |

| 19         | L  | Н  | Н  | Н  | Н  | f <sub>IN</sub> < 5.26  | 5.26 ≤ f <sub>IN</sub>  |

| 20         | Н  | L  | L  | L  | L  | f <sub>IN</sub> = 5.00  | 5.00 ≤ f <sub>IN</sub>  |

| 22         | Н  | L  | L  | L  | Н  | NA                      | 5.00 ≤ f <sub>IN</sub>  |

| 24         | Н  | L  | L  | Н  | L  | NA                      | 5.00 ≤ f <sub>IN</sub>  |

| 26         | Н  | L  | L  | Н  | Н  | NA                      | 5.00 ≤ f <sub>IN</sub>  |

| 28         | Н  | L  | Н  | L  | L  | NA                      | 5.00 ≤ f <sub>IN</sub>  |

| 30         | Н  | L  | Н  | L  | Н  | NA                      | 5.00 ≤ f <sub>IN</sub>  |

| 32         | Н  | L  | Н  | Н  | L  | NA                      | 5.00 ≤ f <sub>IN</sub>  |

| 34         | Н  | L  | Н  | Н  | Н  | NA                      | 5.00 ≤ f <sub>IN</sub>  |

| 36         | Н  | Н  | L  | L  | L  | NA                      | 5.00 ≤ f <sub>IN</sub>  |

| 38         | Н  | Н  | L  | L  | Н  | NA                      | 5.00 ≤ f <sub>IN</sub>  |

| 40         | Н  | Н  | L  | Н  | L  | NA                      | 5.00 ≤ f <sub>IN</sub>  |

| Reserved   | Н  | Н  | L  | Н  | Н  | NA                      | NA                      |

| Reserved   | Н  | Н  | Н  | L  | L  | NA                      | NA                      |

| Reserved   | Н  | Н  | Н  | L  | Н  | NA                      | NA                      |

| Reserved   | Н  | Н  | Н  | Н  | L  | NA                      | NA                      |

| Reserved   | Н  | Н  | Н  | Н  | Н  | NA                      | NA                      |

<sup>(1)</sup> H = high level, L= low level

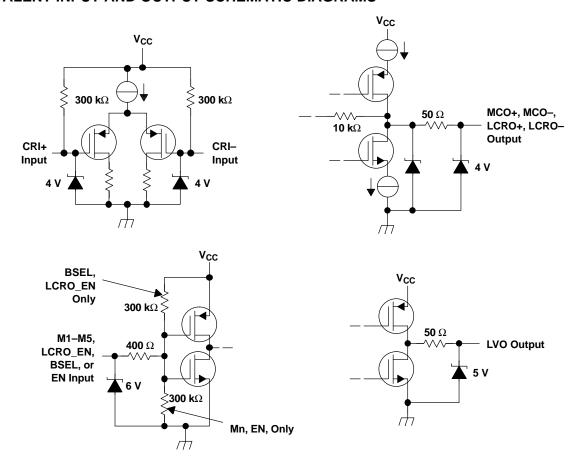

## **EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS**

#### **Terminal Functions**

| TERMIN          | NAL                  | 1/0 | TYPE  | DECEDIPTION                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|----------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO.                  | I/O | ITPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                         |

| BSEL            | 11                   | I   | LVTTL | Band select. Used to optimize VCO performance for minimum M-clock jitter: See recommended f <sub>max</sub> in the frequency multiplier value table.                                                                                                                                                                                                                                                                 |

| CRI+, CRI-      | 2, 3                 | I   | LVDS  | Clock reference input. This is the reference clock signal for the PLL frequency multiplier.                                                                                                                                                                                                                                                                                                                         |

| EN              | 17                   | I   | LVTTL | Enable input. Used to disable the device to a low power state. A high level input enables the device, a low level input disables the device.                                                                                                                                                                                                                                                                        |

| GND             | 5, 12, 18,<br>22, 24 | I   | NA    | Circuit ground                                                                                                                                                                                                                                                                                                                                                                                                      |

| LCRO-,<br>LCRO+ | 13, 14               | 0   | LVDS  | Link clock reference output. This is the data block synchronization clock signal from the PLL frequency multiplier.                                                                                                                                                                                                                                                                                                 |

| LCRO_EN         | 16                   | I   | LVTTL | LCRO enable. Used to turn off the LCRO outputs when they are not used. A high level input enables the LCRO output; a low level input disables the LCRO output.                                                                                                                                                                                                                                                      |

| LVO             | 15                   | 0   | LVTTL | Lock/valid output. This is signal required for proper Muxlt system operation. It is to be directly connected to the LVI inputs of SN65LVDS151 or SN65LVDS152 devices. It is used to inhibit the operation of those devices until after the PLL has stabilized. It remains at a low level following a reset until the PLL has become phase locked. A low to high-level transition indicates phase lock has occurred. |

| M1-M5           | 6–10                 | I   | LVTTL | Multiplier value selection inputs. These inputs determine the frequency multiplication ratio M.                                                                                                                                                                                                                                                                                                                     |

| MCO-, MCO+      | 19, 20               | 0   | LVDS  | M-clock output. This is the high frequency multiplied clock output from the PLL frequency multiplier. It is used by the companion serializer or deserializer devices to synchronizes the transmission or reception of data                                                                                                                                                                                          |

| NC              | 21, 23,<br>26–28     |     | NA    | These pins are not connected and may be left open.                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>CC</sub> | 1, 25                |     | NA    | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>T</sub>  | 4                    |     | NA    | Voltage reference. A $V_{\rm CC}/2$ reference supplied for the unused CRI input when operated in a single-ended mode.                                                                                                                                                                                                                                                                                               |

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                     |                                                | UNIT                         |

|------------------|-------------------------------------|------------------------------------------------|------------------------------|

| $V_{CC}$         | Supply voltage range <sup>(2)</sup> |                                                | −0.5 V to 4 V                |

|                  |                                     | EN, BSEL, LCRO_EN, or M1-M5 inputs             | –0.5 V to 6 V                |

|                  | Voltage range                       | CRI input                                      | –0.5 V to 4 V                |

|                  |                                     | LCRO±, MCO± outputs                            | –0.5 V to 4 V                |

|                  |                                     | Human body model (CRI±, LCRO±, MCO±,and GND(3) | ±12 kV                       |

|                  | Electrostatic discharge             | All pins                                       | ±2 kV                        |

|                  |                                     | Charged-device model (all pins) <sup>(4)</sup> | ±500 V                       |

|                  | Continuous total power d            | lissipation                                    | See Dissipation Rating Table |

| T <sub>stg</sub> | Storage temperature ran             | -65°C to 150°C                                 |                              |

|                  | Lead temperature 1,6 mr             | 260°C                                          |                              |

<sup>(1)</sup> Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> All voltages, except differential I/O bus voltages, are with respect to the network ground terminal.

<sup>(3)</sup> Tested in accordance with JEDEC Standard 22, Test method A114-B.

<sup>(4)</sup> Tested in accordance with JEDEC Standard 22, Test method C101.

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR <sup>(1)</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|---------------------------------------|---------------------------------------------------------------|---------------------------------------|

| PW      | 1207 mW                               | 9.6 mW/°C                                                     | 628 mW                                |

<sup>(1)</sup> This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

## **RECOMMENDED OPERATING CONDITIONS**

|                 |                                         |                                 | MIN                         | NOM | MAX                        | UNIT |

|-----------------|-----------------------------------------|---------------------------------|-----------------------------|-----|----------------------------|------|

| $V_{CC}$        | Supply voltage                          |                                 | 3                           | 3.3 | 3.6                        | V    |

| $V_{IH}$        | High-level input voltage                | EN, BSEL, LCRO_EN, M1-M5        | 2                           |     |                            | V    |

| $V_{IL}$        | Low-level input voltage                 | EIN, BSEL, LCRO_EIN, IVI I-IVIS |                             |     | 0.8                        | V    |

| V <sub>ID</sub> | Magnitude of differential input voltage | CRI                             | 0.1                         |     | 0.6                        | V    |

| V <sub>IC</sub> | Common-mode input voltage               | CRI                             | $\frac{ V_{\text{ID}} }{2}$ |     | $2.4 - \frac{ V_{ID} }{2}$ | ٧    |

| T <sub>A</sub>  | Operating free-air temperature          |                                 | 40                          |     | V <sub>CC</sub> - 0.8      | °C   |

## **TIMING REQUIREMENTS**

|                      |                                             | MIN                   | TYP MAX               | UNIT |

|----------------------|---------------------------------------------|-----------------------|-----------------------|------|

| t <sub>c(1)</sub>    | Input clock cycle time                      | 20                    | 200                   | ns   |

| t <sub>w(1)</sub>    | High-level input clock pulse width duration | 0.4 t <sub>c(1)</sub> | 0.6 t <sub>c(1)</sub> |      |

| f <sub>(clock)</sub> | Input clock frequency, CRI                  | 5                     | 50                    | MHz  |

## **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                                                         |                                | TEST CONDITIONS                                             | MIN                       | TYP(1) | MAX                       | UNIT |

|-----------------------|-------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------|---------------------------|--------|---------------------------|------|

| V <sub>IT+</sub>      | Positive-going differential inpu                                  | ut threshold voltage           | 0 5 4 17 11 4                                               |                           |        | 100                       | mV   |

| V <sub>IT</sub>       | Negative-going differential inp                                   | out threshold voltage          | See Figure 1 and Table 1                                    | -100                      |        |                           | mV   |

| V <sub>OD(SS) </sub>  | Steady-state differential output                                  | ıt voltage magnitude           | $R_L = 100 \Omega$ , See Figure 3                           | 247                       | 340    | 454                       | mV   |

| $\Delta  V_{OD(SS)} $ | Change in steady-state different magnitude between logic stat     |                                | V <sub>ID</sub> = ±100 mV,<br>See Figure 2 and Figure 3     | -50                       |        | 50                        | mV   |

| V <sub>OC(SS)</sub>   | Steady-state common-mode                                          | output voltage                 |                                                             | 1.125                     |        | 1.375                     | V    |

| $\Delta V_{OC(SS)}$   | Change in steady-state communication voltage between logic states | non-mode output                | See Figure 4                                                | -50                       |        | 50                        | mV   |

| V <sub>OC(PP)</sub>   | Peak-to-peak change commo                                         | n-mode output voltage          |                                                             |                           | 50     | 150                       | mV   |

| V <sub>OH</sub>       | High-level output voltage (LV                                     | O)                             | $I_{OH} = -8 \text{ mA}$                                    | 2.4                       |        |                           | V    |

| V <sub>OL</sub>       | Low-level output voltage (LVC                                     | D)                             | I <sub>OL</sub> = 8 mA                                      |                           |        | 0.4                       | ٧    |

| V <sub>(T)</sub>      | Threshold reference bias voltage                                  |                                | –100 μA ≤ I <sub>O</sub> ≤ 100 μA                           | $\frac{V_{CC}}{2} - 0.15$ |        | $\frac{V_{CC}}{2} + 0.15$ | V    |

|                       | Supply current                                                    |                                | Enabled, $R_L = 100 \Omega$ , CRI ± open                    |                           | 25     | 70                        | mA   |

| I <sub>CC</sub>       |                                                                   |                                | Disabled                                                    |                           | 2.5    | 6                         |      |

|                       | Innut ourrent (CDI innute)                                        |                                | V <sub>I</sub> = 0                                          | -20                       |        | -2                        |      |

| l <sub>1</sub>        | Input current (CRI inputs)                                        |                                | V <sub>I</sub> = 2.4 V                                      | -1.2                      |        |                           | μA   |

| I <sub>(ID)</sub>     | Differential input current (I <sub>IA</sub> -                     | I <sub>IB</sub> ) (CRI inputs) | V <sub>IC</sub> = 0.05 V or 2.35 V,V <sub>ID</sub> = ±0.1 V | -2                        |        | 2                         | μΑ   |

| I <sub>I(OFF)</sub>   | Power-off input current (CRI i                                    | nputs)                         | V <sub>CC</sub> = 0 V, V <sub>I</sub> = 3.6 V               |                           |        | 20                        | μΑ   |

|                       | High lavelinest somest                                            | M1-M5, EN                      |                                                             |                           |        | 20                        |      |

| I <sub>IH</sub>       | High-level input current                                          | BSEL, LCRO_EN                  | V <sub>IH</sub> = 2 V                                       | -10                       |        |                           | μA   |

|                       | Laurent Samuel aussauer                                           | M1-M5, EN                      | V 00V                                                       |                           |        | 10                        |      |

| I <sub>IL</sub>       | Low-level input current                                           | BSEL, LCRO_EN                  | V <sub>IL</sub> = 0.8 V                                     | -20                       |        |                           | μΑ   |

|                       | Ob and almostic automate accomment                                | MOO LODO                       | V <sub>O+</sub> or = V <sub>O-</sub> = 0 V                  | -10                       |        | 10                        | A    |

| los                   | Short-circuit output current                                      | MCO, LCRO                      | V <sub>OD</sub> = 0 V                                       | -10                       |        | 10                        | mA   |

| l <sub>OZ</sub>       | High-impedance output current MCO, LCRO                           |                                | V <sub>O</sub> = 0 V or V <sub>CC</sub>                     | -5                        |        | 5                         | μΑ   |

| I <sub>O(OFF)</sub>   | Power-off output current                                          |                                | V <sub>CC</sub> = 1.5 V , V <sub>O</sub> = 3.6 V            | -5                        |        | 5                         | μΑ   |

| Cı                    | Input capacitance (CRI inputs                                     | )                              | $V_{ID} = [(0.4\sin(4E6\pi t) = 0.5] \text{ V}$             |                           | 3      |                           | pF   |

<sup>(1)</sup> All typical values are at  $T_A$  = 25°C and with  $V_{CC}$  = 3.3 V.

#### **SWITCHING CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                        |                                 | TEST CONDITIONS                                      | MIN                  | TYP <sup>(1)</sup> | MAX                  | UNIT |

|---------------------|--------------------------------------------------|---------------------------------|------------------------------------------------------|----------------------|--------------------|----------------------|------|

|                     | MCO output clock period jitter <sup>(2)</sup>    | р-р                             | EN = 1, BSEL = 1,                                    |                      | 200                |                      | 20   |

|                     | MCO output clock period jitter -                 | rms                             | LCRO_EN = 1, M = 40,                                 |                      | 20                 |                      | ps   |

| t <sub>(lock)</sub> | Lock (stabilization time)(3)                     |                                 | f <sub>I</sub> = 5 MHz                               |                      | 0.2                | 1                    | ms   |

| t <sub>w(2)</sub>   | Multiplied clock output pulse wid                | th                              |                                                      | 0.4t <sub>c(2)</sub> |                    | 0.6t <sub>c(2)</sub> |      |

| t <sub>r</sub>      | Differential output signal rise time             | e (MCO, LCRO)                   | $R_L = 100 \Omega$ , $C_L = 10 pF$ ,<br>See Figure 5 | 0.3                  | 0.6                | 1.5                  |      |

| t <sub>f</sub>      | Differential output signal fall time             | (MCO, LCRO)                     | Geo rigulo o                                         | 0.3                  | 0.6                | 1.5                  | ns   |

|                     |                                                  | f <sub>I</sub> = 5 MHz, M = 4   | $R_L = 100 \Omega$ , $C_L = 10 pF$ ,<br>See Figure 6 | -2.5                 | 0                  | 2.5                  | ns   |

| t <sub>(OS)</sub>   | CRI <sup>↑</sup> to MCO <sup>↑</sup> offset time | f <sub>I</sub> = 10 MHz, M = 10 |                                                      | -1.5                 | 0                  | 1.5                  |      |

|                     |                                                  | f <sub>I</sub> = 5 MHz, M = 40  |                                                      | -1.65                | 0                  | 1.65                 |      |

|                     |                                                  | f <sub>I</sub> = 5 MHz, M = 4   | $R_L = 100 \Omega$ , $C_L = 10 pF$ ,<br>See Figure 6 | 0.5                  | 2.5                | 6                    |      |

| t <sub>d</sub>      | MCO↑ before LCRO↑ , time delay                   | f <sub>I</sub> = 10 MHz, M = 10 |                                                      | 0.5                  | 2.5                | 6                    | ns   |

|                     | dolay                                            | f <sub>I</sub> = 5 MHz, M = 40  |                                                      | 0.5                  | 2.5                | 4.5                  |      |

|                     | Maximum MCO output frequency                     |                                 | BSEL =1, M = 4, 6                                    | 200                  |                    |                      | MHz  |

| 4                   |                                                  |                                 | BSEL =1, M ≠ 4, 6                                    | 400                  |                    |                      |      |

| f <sub>max</sub>    |                                                  |                                 | BSEL =0, M = 4, 6                                    | 50                   |                    |                      |      |

|                     |                                                  |                                 | BSEL =0, M ≠ 4, 6                                    | 100                  |                    |                      |      |

All typical values are at T<sub>A</sub> = 25°C and with V<sub>CC</sub> = 3.3 V.

Output clock jitter is the change in the output clock period from one cycle to the next cycle observed over 10,000 cycles with a source having less than 10 psec jitter rms.

Lock time is measured from the application of the clock reference input signal to the assertion of a high-level lock/valid output.

#### PARAMETER MEASUREMENT INFORMATION

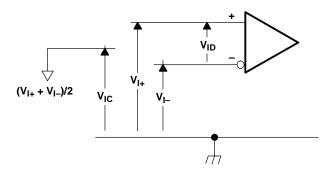

Figure 1. Receiver Input Voltage Definitions

Table 1. Receiver Minimum and Maximum Input Threshold Test Voltages

| APPLIED VOLTAGES  |                   | RESULTING DIFFERENTIAL INPUT VOLTAGE | RESULTING COMMON-<br>MODE INPUT VOLTAGE |

|-------------------|-------------------|--------------------------------------|-----------------------------------------|

| V <sub>(IA)</sub> | V <sub>(IB)</sub> | V <sub>ID</sub>                      | V <sub>IC</sub>                         |

| 1.25 V            | 1.15 V            | 100 mV                               | 1.2 V                                   |

| 1.15 V            | 1.25 V            | –100 mV                              | 1.2 V                                   |

| 2.4 V             | 2.3 V             | 100 mV                               | 2.35 V                                  |

| 2.3 V             | 2.4 V             | –100 mV                              | 2.35 V                                  |

| 0.1 V             | 0 V               | 100 mV                               | 0.05 V                                  |

| 0 V               | 0.1 V             | –100 mV                              | 0.05 V                                  |

| 1.5 V             | 0.9 V             | 600 mV                               | 1.2 V                                   |

| 0.9 V             | 1.5 V             | –600 mV                              | 1.2 V                                   |

| 2.4 V             | 1.8 V             | 600 mV                               | 2.1 V                                   |

| 1.8 V             | 2.4 V             | –600 mV                              | 2.1 V                                   |

| 0.6 V             | 0 V               | 600 mV                               | 0.3 V                                   |

| 0 V               | 0.6 V             | –600 mV                              | 0.3 V                                   |

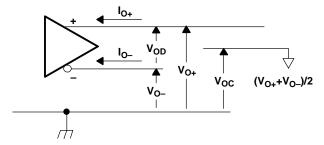

Figure 2. Driver Output Voltage and Current Definitions

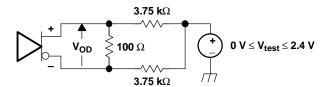

Figure 3. V<sub>OD</sub> Test Circuit

A. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_r \le 1$  ns, pulse repetition rate (PRR) = 0.5 Mpps, Pulse width = 500  $\pm$  10 ns .  $C_L$  includes instrumentation and fixture capacitance within 0,06 m of the D.U.T. The measurement of  $V_{OC(PP)}$  is made on test equipment with a -3 dB bandwidth of at least 5 GHz.

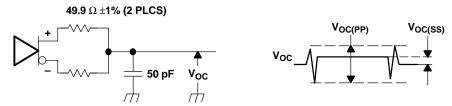

Figure 4. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

A. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 50 Mpps, Pulse width = 10  $\pm$  0.2 ns .  $C_L$  includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

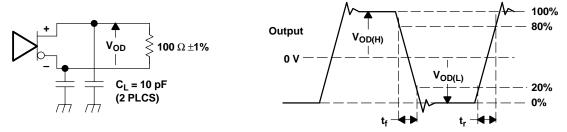

Figure 5. Test Circuit, Timing, and Voltage Definitions for the Differential Output Signal

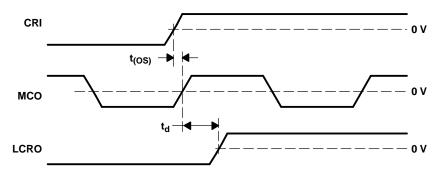

**Figure 6. Output Timing Waveform Definitions**

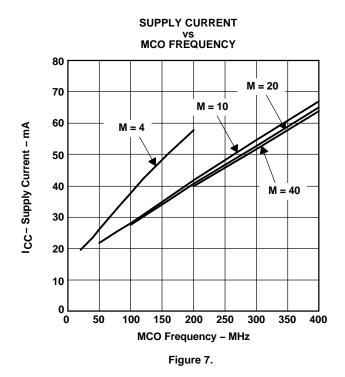

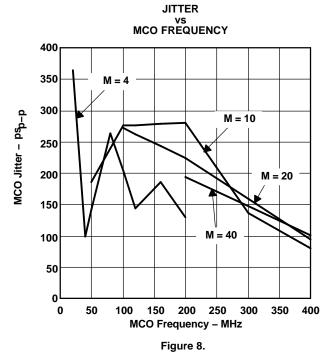

#### **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS (continued)**

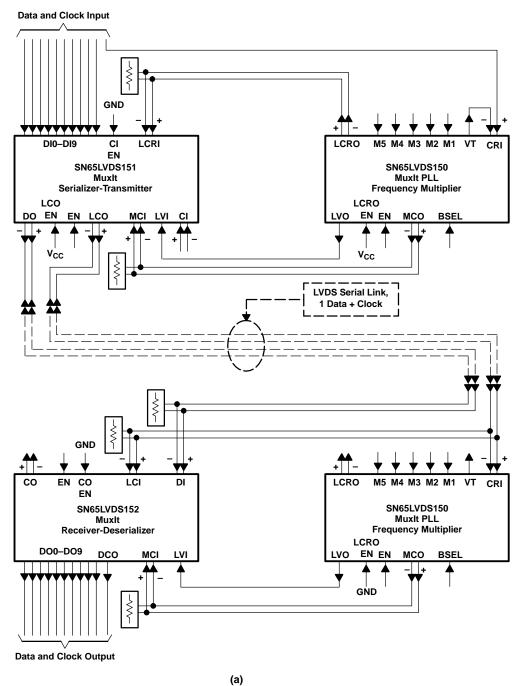

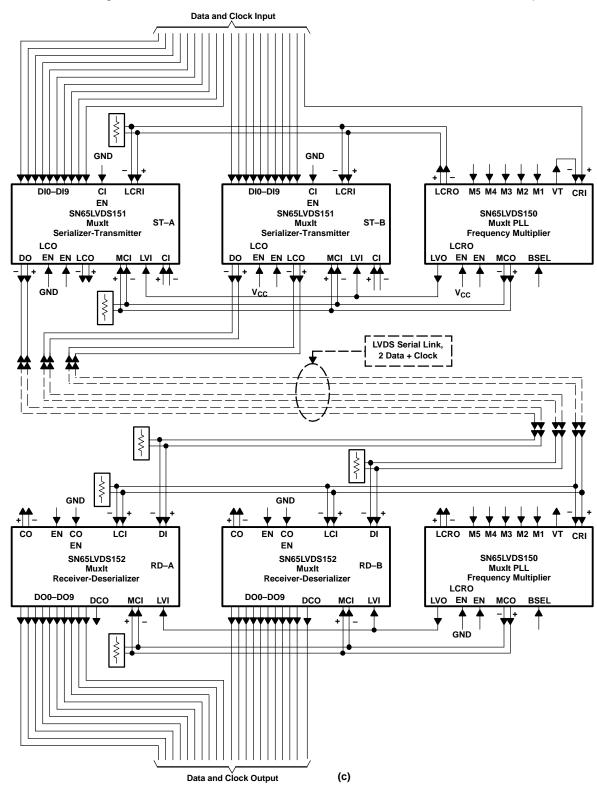

## **BASIC APPLICATIONS EXAMPLES**

Parallel data path width between 4 and 10 bits, only one LVDS data link required.

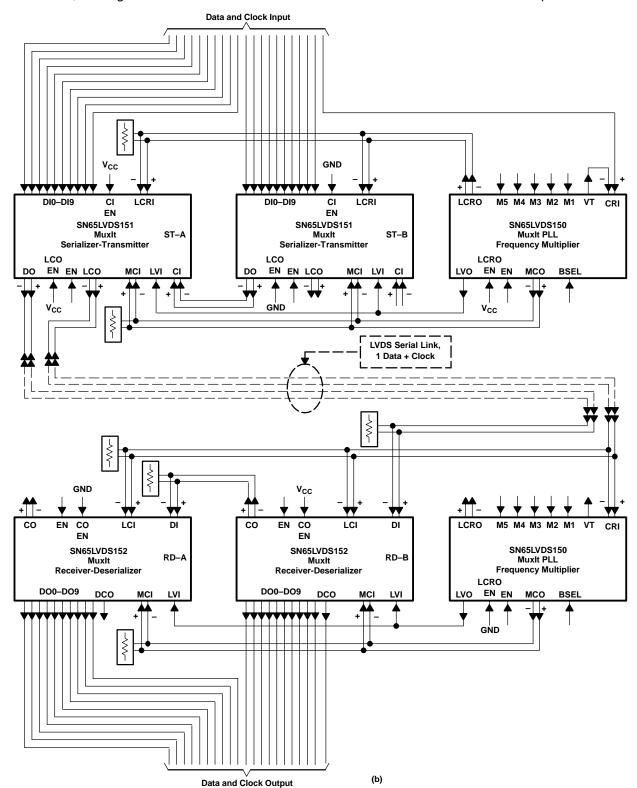

## **TYPICAL CHARACTERISTICS (continued)**

Parallel data path width between 11 and 20 bits, aggregate data rate low enough to allow transmission over one LVDS data link, sharing of PLL-FM between serializer-transmitter and receiver-deserializer chips at each end.

## **TYPICAL CHARACTERISTICS (continued)**

Parallel data path width between 11 and 20 bits, aggregate data rate requires transmission over two separate LVDS data links, sharing of PLL-FM between serializer-transceiver and receiver-deserializer chips at each end.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2006, Texas Instruments Incorporated