## Product Brief

# Multi-Output PMIC with Integrated Sequencer

IRPS5401

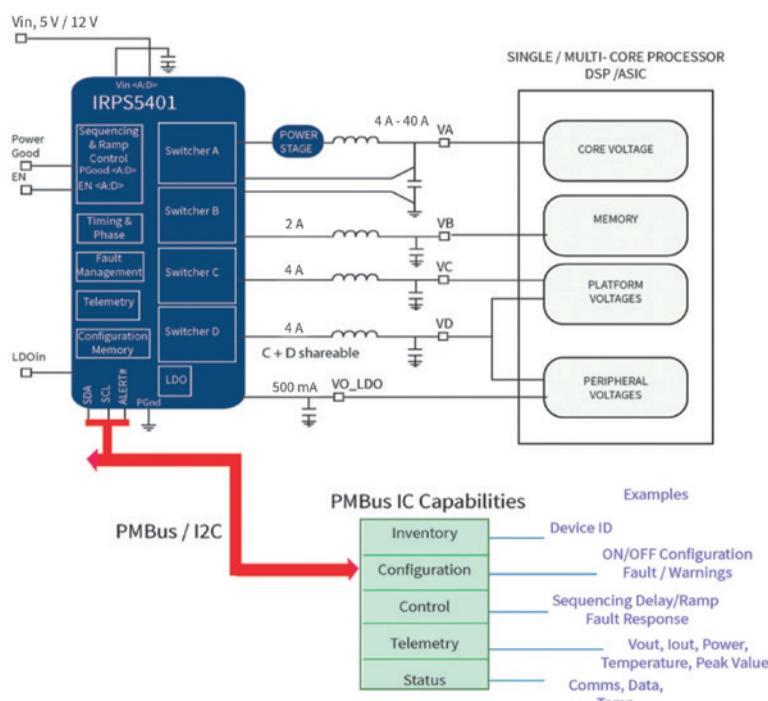

The IRPS5401 is an integrated power management IC ideal for tight board space requirements; for example, FPGAs, System On Chip ASICs and multi-core processors containing several voltages that require precision accuracy and voltage sequencing.

## Typical Application

## Industry reference Designs

IRPS5401 is designed to support several industry ASICs, FPGA's and SOCs.

[www.infineon.com/xilinx](http://www.infineon.com/xilinx)

[www.infineon.com/altera](http://www.infineon.com/altera)

## Key features

- › Multi-output DC/DC with integrated FETs and Sequencer

- › 4 switchers and 1 LDO in one package

- Output A: 2 A (without), 50 A (with power stage)

- Output B: 2 A

- Outputs C,D: 4 A

- Linear regulator: +/-0.5 A

- › Full PMBus: Margining, Fault Management, Telemetry

## Key benefits

- › Simplified BOM: Replace many regulators with one PMIC

- › Design re-use: One design is scalable to cover wide range of FPGAs and ASICs

- › Lower total solution cost: Eliminates external sequencer

- › 35% board area reduction: High level integration and component reduction

## Target Applications

- › High density ASIC, FPGA & CPU multi-rail systems

- › Xilinx Zynq ZU02 to ZU19 Embedded Computing systems

- › Communications and Storage systems

- › Telecom

- › Video Processing

- › IoT

- › Instrumentation

# Multi-Output PMIC with Integrated Sequencer

## IRPS5401

### Scalable Power Options for Power Design Flexibility

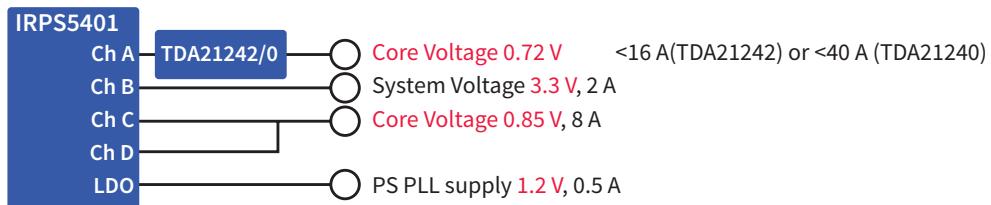

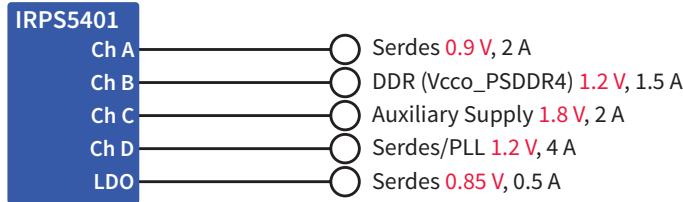

IRPS5401's flexibility easily addresses different types of ASICs and FPGAs. With the addition of an external power stage shown in example 1, it can easily address high current requirements.

Example PMIC Configuration 1

Example PMIC Configuration 2

### Compact Power Solutions Includes Sequencer

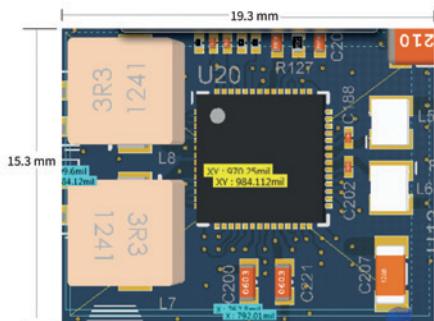

Complete ASIC/FPGA power solution including sequencer in 295mm<sup>2</sup> represents a 35% reduction over traditional solutions.

| Part Number      | Application                                             | Status             |

|------------------|---------------------------------------------------------|--------------------|

| IRPS5401MTRPBF   | Blank, unprogrammed part for general use                | Active & Preferred |

| IRPS5401MXI03TRP | Pre-programmed for Xilinx Zynq UltraScale+ ZU02 to ZU09 | Coming Soon        |

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2017 Infineon Technologies AG.

All Rights Reserved.

#### Please note!

THIS DOCUMENT IS FOR INFORMATION PURPOSES ONLY AND ANY INFORMATION GIVEN HEREIN SHALL IN NO EVENT BE REGARDED AS A WARRANTY, GUARANTEE OR DESCRIPTION OF ANY FUNCTIONALITY, CONDITIONS AND/OR QUALITY OF OUR PRODUCTS OR ANY SUITABILITY FOR A PARTICULAR PURPOSE. WITH REGARD TO THE TECHNICAL SPECIFICATIONS OF OUR PRODUCTS, WE KINDLY ASK YOU TO REFER TO THE RELEVANT PRODUCT DATA SHEETS PROVIDED BY US. OUR CUSTOMERS AND THEIR TECHNICAL DEPARTMENTS ARE REQUIRED TO EVALUATE THE SUITABILITY OF OUR PRODUCTS FOR THE INTENDED APPLICATION.

WE RESERVE THE RIGHT TO CHANGE THIS DOCUMENT AND/OR THE INFORMATION GIVEN HEREIN AT ANY TIME.

#### Additional information

For further information on technologies, our products, the application of our products, delivery terms and conditions and/or prices, please contact your nearest Infineon Technologies office ([www.infineon.com](http://www.infineon.com)).

#### Warnings

Due to technical requirements, our products may contain dangerous substances. For information on the types in question, please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by us in a written document signed by authorized representatives of Infineon Technologies, our products may not be used in any life-endangering applications, including but not limited to medical, nuclear, military, life-critical or any other applications where a failure of the product or any consequences of the use thereof can result in personal injury.