# 256K x 36/512K x 18 Pipelined SRAM with NoBL™ Architecture

### **Features**

- Zero Bus Latency™, no dead cycles between Write and Read cycles

- Fast clock speed: 200, 166, 133, 100 MHz

- Fast access time: 3.2, 3.6, 4.2, 5.0 ns

- Internally synchronized registered outputs eliminate the need to control OE

- Single 3.3V –5% and +5% power supply V<sub>CC</sub>

- Separate V<sub>CCQ</sub> for 3.3V or 2.5V I/O

- · Single WEN (Read/Write) control pin

- Positive clock-edge triggered, address, data, and control signal registers for fully pipelined applications

- Interleaved or linear four-word burst capability

- Individual byte Write (BWa–BWd) control (may be tied LOW)

- CEN pin to enable clock and suspend operations

- · Three chip enables for simple depth expansion

- Automatic power-down feature available using ZZ mode or CE select

- JTAG boundary scan

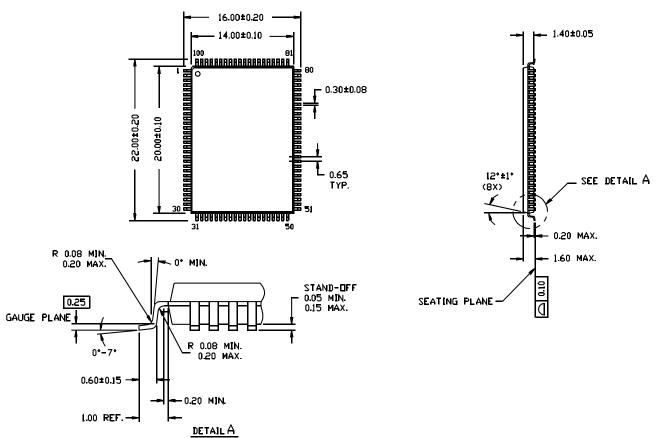

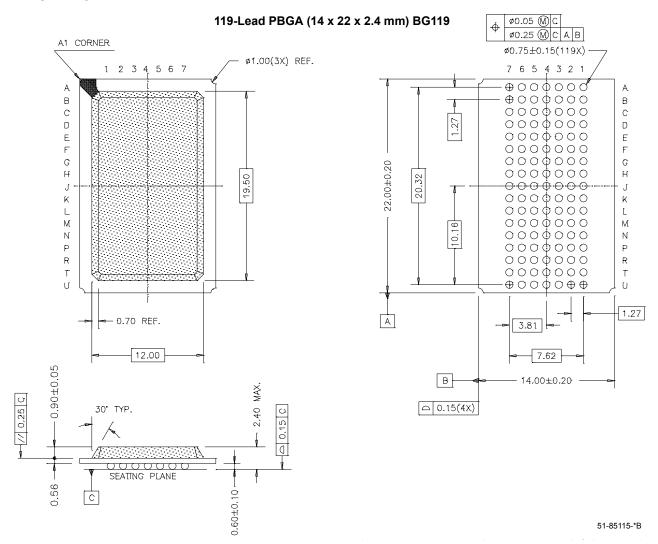

- Low-profile 119-bump, 14-mm × 22-mm BGA (Ball Grid Array), and 100-pin TQFP packages

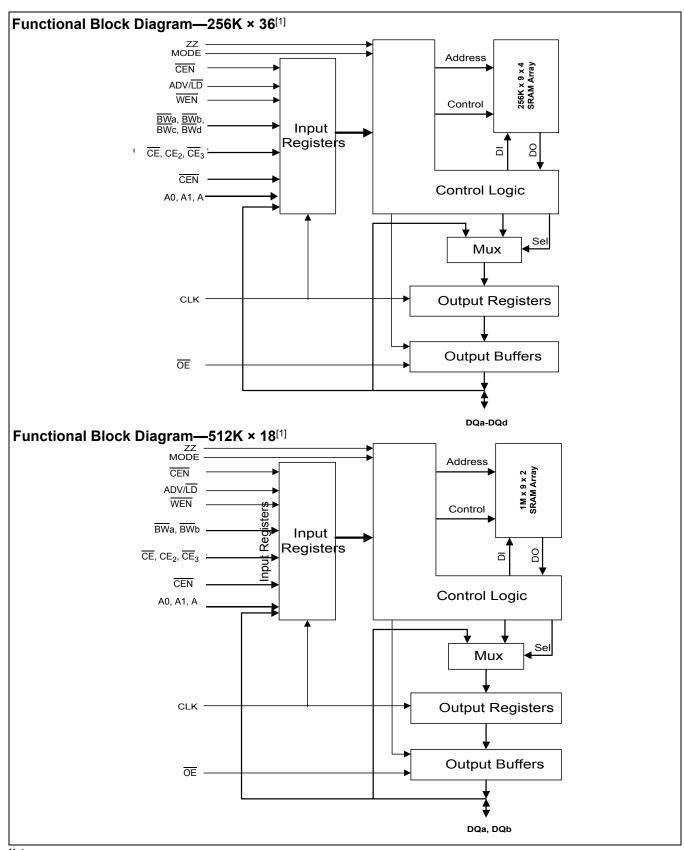

### **Functional Description**

The CY7C1354A and CY7C1356A SRAMs are designed to eliminate dead cycles when transitioning from Read to Write or vice versa. These SRAMs are optimized for 100% bus utilization and achieve Zero Bus Latency™ (ZBL™)/No Bus Latency™ (NoBL™). They integrate 262,144 × 36 and 524,288 × 18 SRAM cells, respectively, with advanced synchronous peripheral circuitry and a two-bit counter for internal burst operation. These employ high-speed, low-power CMOS designs using advanced triple-layer polysilicon, double-layer metal technology. Each memory cell consists of four transistors and two high-valued resistors.

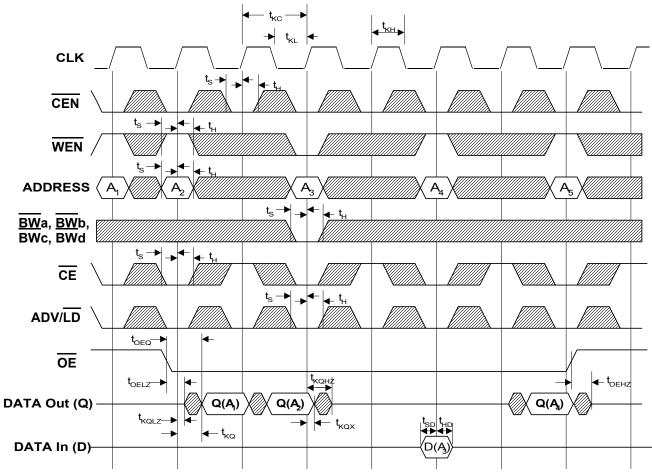

All synchronous inputs are gated by registers controlled by a positive-edge-triggered clock input (CLK). The synchronous inputs include <u>all</u> addresses, <u>all</u> data inputs, depth-expansion Chip Enables (<u>CE</u>, <u>CE</u><sub>2</sub>, and <u>CE</u><sub>3</sub>), Cycle Start Input (<u>ADV/LD</u>), Clock <u>Enable</u> (CEN), Byte Write Enables (<u>BWa</u>, <u>BWb</u>, <u>BWc</u>, and <u>BWd</u>), and Read-Write Control (<u>WEN</u>). Bwc and <u>BWd</u> apply to CY7C1354A only.

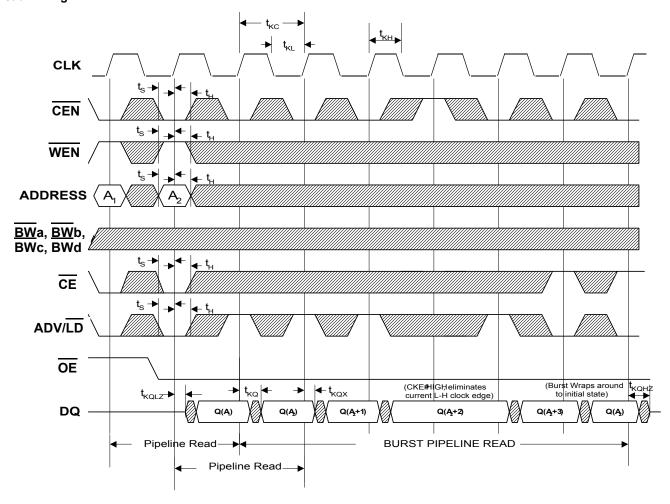

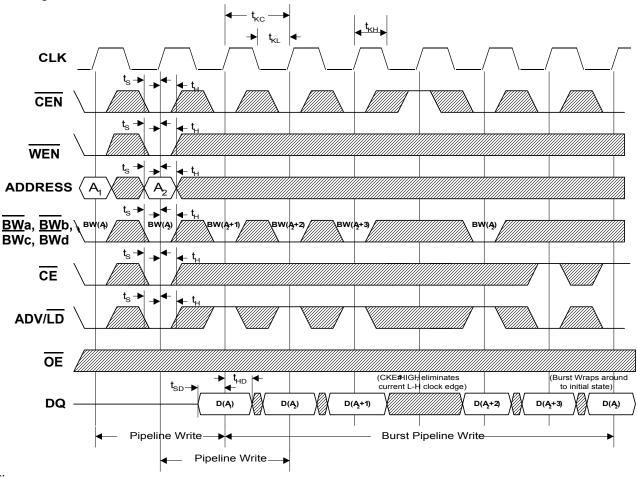

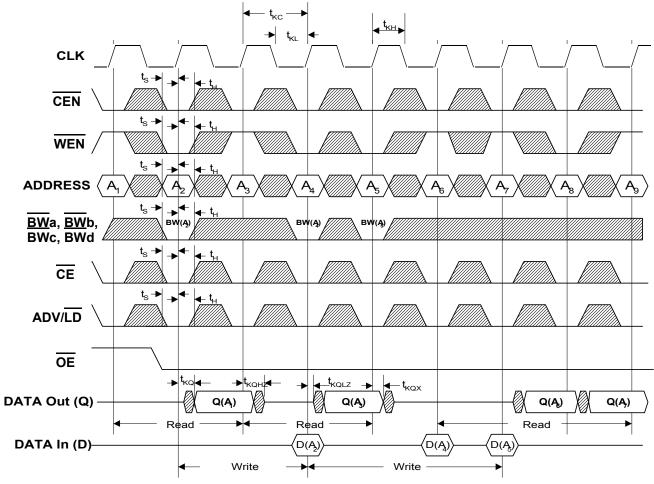

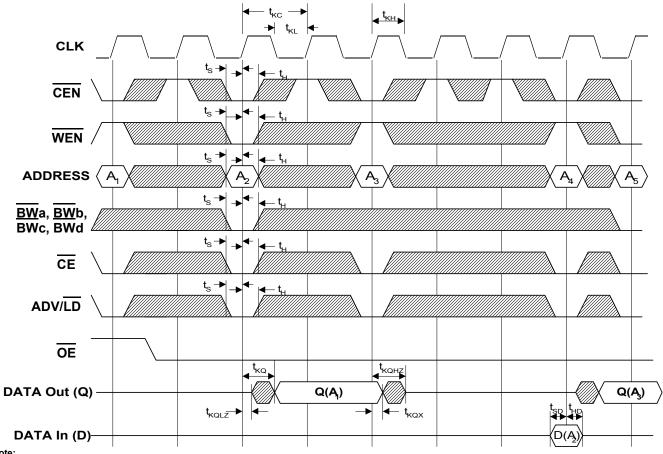

Address and control signals are applied to the SRAM during one clock cycle, and two cycles later, its associated data occurs, either Read or Write.

A clock enable (CEN) pin allows operation of the CY7C1354A/CY7C1356A to be suspended as long as necessary. All synchronous inputs are ignored when (CEN) is HIGH and the internal device registers will hold their previous values.

There are three chip enable pins  $(\overline{CE}, CE_2, \overline{CE}_3)$  that allow the user to deselect the device when desired. If any one of these three are not active when ADV/ $\overline{LD}$  is LOW, no new memory operation can be initiated and any burst cycle in progress is stopped. However, any pending data transfers (Read or Write) will be completed. The data bus will be in high-impedance state two cycles after chip is deselected or a Write cycle is initiated.

The CY7C1354A and CY7C1356A have an on-chip two-bit burst counter. In the burst mode, the CY7C1354A and CY7C1356A provide four cycles of data for a single address presented to the SRAM. The order of the burst sequence is defined by the MODE input pin. The MODE pin selects between linear and interleaved burst sequence. The ADV/LD signal is used to load a new external address (ADV/LD = LOW) or increment the internal burst counter (ADV/LD = HIGH)

Output Enable  $(\overline{OE})$ , Sleep Enable (ZZ) and <u>bur</u>st sequence select (MODE) are the asynchronous signals.  $\overline{OE}$  can be used to disable the outputs at any given time. ZZ may be tied to LOW if it is not used.

Four pins are used to implement JTAG test capabilities. The JTAG circuitry is used to serially shift data to and from the device. JTAG inputs use LVTTL/LVCMOS levels to shift data during this testing mode of operation.

### Selection Guide

|                              |            | 7C1354A-200 | 7C1354A-166<br>7C1356A-166 | 7C1354A-133<br>7C1356A-133 | 7C1356A-100 | Unit |

|------------------------------|------------|-------------|----------------------------|----------------------------|-------------|------|

| Maximum Access Time          |            | 3.2         | 3.6                        | 4.2                        | 5.0         | ns   |

| Maximum Operating Current    | Commercial | 560         | 480                        | 410                        | 350         | mA   |

| Maximum CMOS Standby Current | Commercial | 30          | 30                         | 30                         | 30          | mA   |

<sup>1.</sup> The Functional Block Diagram illustrates simplified device operation. See Truth Table, pin descriptions, and timing diagrams for detailed information.

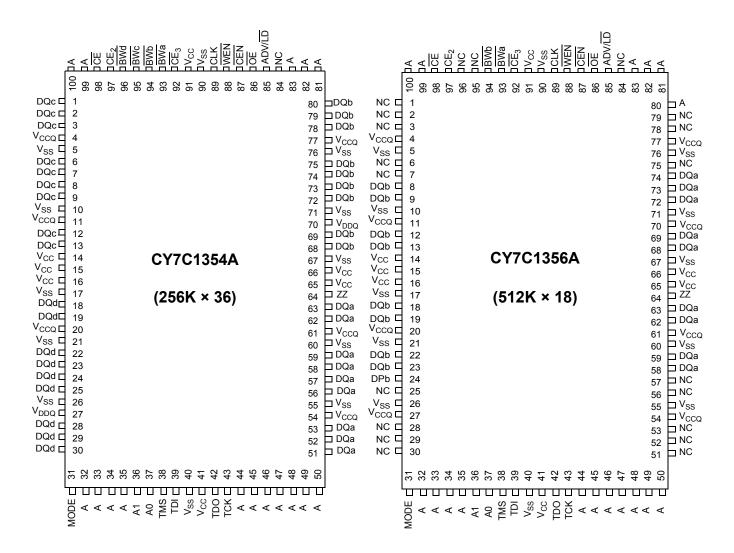

### **Pin Configurations**

### 100-lead TQFP Packages

### Pin Configurations (continued)

### 119-ball Bump BGA CY7C1354A (256K × 36)-7 × 17 BGA

Table 1.

|   | 1                | 2               | 3               | 4               | 5               | 6               | 7                |

|---|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| Α | V <sub>CCQ</sub> | Α               | Α               | NC              | Α               | Α               | V <sub>CCQ</sub> |

| В | NC               | CE <sub>2</sub> | Α               | ADV/LD          | Α               | CE <sub>3</sub> | NC               |

| С | NC               | Α               | Α               | V <sub>CC</sub> | Α               | Α               | NC               |

| D | DQc              | DQc             | V <sub>SS</sub> | NC              | V <sub>SS</sub> | DQb             | DQb              |

| E | DQc              | DQc             | $V_{SS}$        | CE              | $V_{SS}$        | DQb             | DQb              |

| F | V <sub>CCQ</sub> | DQc             | V <sub>SS</sub> | OE              | V <sub>SS</sub> | DQb             | V <sub>CCQ</sub> |

| G | DQc              | DQc             | BWc             | Α               | BWb             | DQb             | DQb              |

| Н | DQc              | DQc             | $V_{SS}$        | WEN             | $V_{SS}$        | DQb             | DQb              |

| J | V <sub>CCQ</sub> | V <sub>CC</sub> | NC              | V <sub>CC</sub> | NC              | V <sub>CC</sub> | V <sub>CCQ</sub> |

| K | DQd              | DQd             | V <sub>SS</sub> | CLK             | V <sub>SS</sub> | DQa             | DQa              |

| L | DQd              | DQd             | BWd             | NC              | BWa             | DQa             | DQa              |

| М | V <sub>CCQ</sub> | DQd             | V <sub>SS</sub> | CEN             | V <sub>SS</sub> | DQa             | V <sub>CCQ</sub> |

| N | DQd              | DQd             | V <sub>SS</sub> | A1              | V <sub>SS</sub> | DQa             | DQa              |

| Р | DQd              | DQd             | V <sub>SS</sub> | A0              | V <sub>SS</sub> | DQa             | DQa              |

| R | NC               | Α               | MODE            | V <sub>CC</sub> | V <sub>SS</sub> | Α               | NC               |

| T | NC               | NC              | Α               | Α               | Α               | NC              | ZZ               |

| U | V <sub>CCQ</sub> | TMS             | TDI             | TCK             | TDO             | NC              | $V_{CCQ}$        |

### CY7C1356A (512K × 18)-7 × 17 BGA

Table 1.

|   | 1                | 2               | 3               | 4               | 5               | 6               | 7                |

|---|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| Α | V <sub>CCQ</sub> | Α               | Α               | NC              | Α               | Α               | V <sub>CCQ</sub> |

| В | NC               | CE <sub>2</sub> | Α               | ADV/LD          | Α               | CE <sub>3</sub> | NC               |

| С | NC               | Α               | Α               | V <sub>CC</sub> | Α               | Α               | NC               |

| D | DQb              | NC              | $V_{SS}$        | NC              | V <sub>SS</sub> | DQa             | NC               |

| Е | NC               | DQb             | V <sub>SS</sub> | CE              | V <sub>SS</sub> | NC              | DQa              |

| F | V <sub>CCQ</sub> | NC              | V <sub>SS</sub> | OE              | V <sub>SS</sub> | DQa             | V <sub>CCQ</sub> |

| G | NC               | DQb             | BWb             | Α               | V <sub>SS</sub> | NC              | DQa              |

| Н | DQb              | NC              | V <sub>SS</sub> | WEN             | V <sub>SS</sub> | DQa             | NC               |

| J | V <sub>CCQ</sub> | V <sub>CC</sub> | NC              | V <sub>CC</sub> | NC              | V <sub>CC</sub> | V <sub>CCQ</sub> |

| K | NC               | DQb             | V <sub>SS</sub> | CLK             | V <sub>SS</sub> | NC              | DQa              |

| L | DQb              | NC              | V <sub>SS</sub> | NC              | BWa             | DQa             | NC               |

| М | V <sub>CCQ</sub> | DQb             | V <sub>SS</sub> | CEN             | V <sub>SS</sub> | NC              | V <sub>CCQ</sub> |

| N | DQb              | NC              | V <sub>SS</sub> | A1              | V <sub>SS</sub> | DQa             | NC               |

| Р | NC               | DQb             | V <sub>SS</sub> | A0              | V <sub>SS</sub> | NC              | DQa              |

| R | NC               | Α               | MODE            | V <sub>CC</sub> | V <sub>CC</sub> | Α               | NC               |

| T | NC               | Α               | Α               | NC              | Α               | Α               | ZZ               |

| U | V <sub>CCQ</sub> | TMS             | TDI             | TCK             | TDO             | NC              | V <sub>CCQ</sub> |

## Pin Descriptions—256K × 36

| 256K × 36                                                                              | 256K × 36                                                                           |                             |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TQFP Pins                                                                              | PBGA Pins                                                                           | Name                        | Туре                   | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 37,<br>36,<br>32, 33, 34, 35,<br>44, 45, 46, 47,<br>48, 49, 50, 81,<br>82, 83, 99, 100 | 4P<br>4N<br>2A, 3A, 5A, 6A,<br>3B, 5B, 2C, 3C,<br>5C, 6C, 4G, 2R,<br>6R, 3T, 4T, 5T | A0,<br>A1,<br>A             | Input-<br>Synchronous  | Synchronous Address Inputs: The address register is triggered by a combination of the rising edge of CLK, ADV/LD LOW, CEN LOW and true chip enables. A0 and A1 are the two least significant bits (LSBs) of the address field and set the internal burst counter if burst cycle is initiated.                                                                                                                                                                                                                                                                                                         |  |

| 93,<br>94,<br>95,<br>96                                                                | 5L<br>5G<br>3G<br>3L                                                                | BWa,<br>BWb,<br>BWc,<br>BWd | Input-<br>Synchronous  | Synchronous Byte Write Enables: Each nine-bit byte has its own active LOW byte Write enable. On load Write cycles (when WEN and ADV/LD are sampled LOW), the appropriate byte Write signal (BWx) must be valid. The byte Write signal must also be valid on each cycle of a burst Write. Byte Write signals are ignored when WEN is sampled HIGH. The appropriate byte(s) of data are written into the device two cycles later. BWa controls DQa pins; BWb controls DQb pins; BWc controls DQc pins; BWd controls DQd pins. BWx can all be tied LOW if always doing Writes to the entire 36-bit word. |  |

| 87                                                                                     | 4M                                                                                  | CEN                         | Input-<br>Synchronous  | Synchronous Clock Enable Input: When CEN is sampled HIGH, all other synchronous inputs, including clock are ignored and outputs remain unchanged. The effect of CEN sampled HIGH on the device outputs is as if the LOW-to-HIGH clock transition did not occur. For normal operation, CEN must be sampled LOW at rising edge of clock.                                                                                                                                                                                                                                                                |  |

| 88                                                                                     | 4H                                                                                  | WEN                         | Input-<br>Synchronous  | Read Write: WEN signal is a synchronous input that identifies whether the current loaded cycle and the subsequent burst cycles initiated by ADV/LD is a Read or Write operation. The data bus activity for the current cycle takes place two clock cycles later.                                                                                                                                                                                                                                                                                                                                      |  |

| 89                                                                                     | 4K                                                                                  | CLK                         | Input-<br>Synchronous  | Clock: This is the clock input to CY7C1354A. Except for $\overline{OE}$ , ZZ and MODE, all timing references for the device are made with respect to the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 98, 92                                                                                 | 4E, 6B                                                                              | CE,<br>CE <sub>3</sub>      | Input-<br>Synchronous  | Synchronous Active LOW Chip Enable: CE and CE <sub>3</sub> are used with CE <sub>2</sub> to enable the CY7C1354A. CE or CE <sub>3</sub> sampled HIGH or CE <sub>2</sub> sampled LOW, along with ADV/LD LOW at the rising edge of clock, initiates a deselect cycle. The data bus will be High-Z two clock cycles after chip deselect is initiated.                                                                                                                                                                                                                                                    |  |

| 97                                                                                     | 2B                                                                                  | CE <sub>2</sub>             | Input-<br>Synchronous  | <b>Synchronous Active High Chip Enable</b> : $CE_2$ is used with $\overline{CE}$ and $\overline{CE}_3$ to enable the chip. $CE_2$ has inverted polarity but otherwise is identical to $\overline{CE}$ and $\overline{CE}_3$ .                                                                                                                                                                                                                                                                                                                                                                         |  |

| 86                                                                                     | 4F                                                                                  | OE                          | Input                  | Asynchronous Output Enable: OE must be LOW to Read data. When OE is HIGH, the I/O pins are in high-impedance state. OE does not need to be actively controlled for Read and Write cycles. In normal operation, OE can be tied LOW.                                                                                                                                                                                                                                                                                                                                                                    |  |

| 85                                                                                     | 4B                                                                                  | ADV/<br>LD                  | Input-<br>Synchronous  | Advance/Load: ADV/LD is a synchronous input that is used to load the internal registers with new address and control signals when it is sampled LOW at the rising edge of clock with the chip is selected. When ADV/LD is sampled HIGH, then the internal burst counter is advanced for any burst that was in progress. The external addresses and WEN are ignored when ADV/LD is sampled HIGH.                                                                                                                                                                                                       |  |

| 31                                                                                     | 3R                                                                                  | MOD<br>E                    | Input-<br>Static       | <b>Burst Mode</b> : When MODE is HIGH or NC, the interleaved burst sequence is selected. When MODE is LOW, the linear burst sequence is selected. MODE is a static DC input.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 64                                                                                     | 7T                                                                                  | ZZ                          | Input-<br>Asynchronous | <b>Sleep Enable</b> : This active HIGH input puts the device in low power consumption standby mode. For normal operation, this input has to be either LOW or NC.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

## Pin Descriptions—256K × 36 (continued)

| 256K × 36<br>TQFP Pins                                                                                                  | 256K × 36<br>PBGA Pins                                                                         | Pin<br>Name              | Туре             | Pin Description                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51, 52, 53,<br>56-59, 62, 63<br>68, 69, 72-75,<br>78, 79, 80<br>1, 2, 3, 6-9, 12,<br>13<br>18, 19, 22-25,<br>28, 29, 30 | (a) 6P, 7P, 7N,<br>6N, 6M, 6L, 7L,<br>6K, 7K,<br>(b) 7H, 6H, 7G,<br>6G, 6F, 6E, 7E,<br>7D, 6D, | DQa<br>DQb<br>DQc<br>DQd | Input/<br>Output | Data Inputs/Outputs: Both the data input path and data output path are registered and triggered by the rising edge of CLK. Byte "a" is DQa pins; Byte "b" is DQb pins; Byte "c" is DQc pins; Byte "d" is DQd pins. |

| 38<br>39<br>43                                                                                                          | 2U<br>3U<br>4U                                                                                 | TMS<br>TDI<br>TCK        | Input            | <b>IEEE 1149.1 Test Inputs</b> : LVTTL-level inputs. If Serial Boundary Scan (JTAG) is not used, these pins can be floating (i.e., No Connect) or be connected to $V_{CC}$ .                                       |

| 42                                                                                                                      | 5U                                                                                             | TDO                      | Output           | IEEE 1149.1 Test Output: LVTTL-level output. If Serial Boundary Scan (JTAG) is not used, these pins can be floating (i.e., No Connect).                                                                            |

| 14, 15, 16, 41,<br>65, 66, 91                                                                                           | 4C, 2J, 4J, 6J,<br>4R, 5R                                                                      | V <sub>CC</sub>          | Supply           | <b>Power Supply</b> : +3.3V –5% and +5%.                                                                                                                                                                           |

| 5, 10, 17, 21,<br>26, 40, 55, 60,<br>67, 71, 76, 90                                                                     | 3D, 5D, 3E, 5E,<br>3F, 5F, 3H, 5H,<br>3K, 5K, 3M,<br>5M, 3N, 5N, 3P,<br>5P                     | V <sub>SS</sub>          | Ground           | Ground: GND.                                                                                                                                                                                                       |

| 4, 11, 20, 27,<br>54, 61, 70, 77                                                                                        | 1A, 7A, 1F, 7F,<br>1J, 7J, 1M, 7M,<br>1U, 7U                                                   | V <sub>CCQ</sub>         | I/O Supply       | Output Buffer Supply: +3.3V –0.165V and +0.165V for 3.3V I/O. +2.5V –0.125V and +0.4V for 2.5V I/O.                                                                                                                |

| 84                                                                                                                      | 4A, 1B, 7B, 1C,<br>7C, 4D, 3J, 5J,<br>4L, 1R, 7R, 1T,<br>2T, 6T, 6U                            | NC                       | -                | <b>No Connect</b> : These signals are not internally connected. It can be left floating or be connected to $V_{CC}$ or to GND.                                                                                     |

### Pin Descriptions—512K × 18

| 512K × 18<br>TQFP Pins | 512K × 18<br>PBGA Pins                                                                         | Pin<br>Name     | Туре | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|------------------------------------------------------------------------------------------------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44, 45, 46, 47,        | 4P<br>4N<br>2A, 3A, 5A, 6A,<br>3B, 5B, 6B, 2C,<br>3C, 5C, 6C, 4G,<br>2R, 6R, 2T, 3T,<br>5T, 6T | A0,<br>A1,<br>A |      | Synchronous Address Inputs: The address register is triggered by a combination of the rising edge of CLK, ADV/LD LOW, CEN LOW, and true chip enables. A0 and A1 are the two least significant bits of the address field and set the internal burst counter if burst cycle is initiated.                                                                                                                                                                                                                                                                |

| 93,<br>94,             | 5L<br>3G                                                                                       | BWa,<br>BWb     |      | Synchronous Byte Write Enables: Each nine-bit byte has its own active LOW byte Write enable. On load Write cycles (when WEN and ADV/LD are sampled LOW), the appropriate byte Write signal (BWx) must be valid. The byte Write signal must also be valid on each cycle of a burst Write. Byte Write signals are ignored when WEN is sampled HIGH. The appropriate byte(s) of data are written into the device two cycles later. BWa controls DQa pins; BWb controls DQb pins. BWx can all be tied LOW if always doing Write to the entire 18-bit word. |

| 87                     | 4M                                                                                             | CEN             |      | Synchronous Clock Enable Input: When CEN is sampled HIGH, all other synchronous inputs, including clock are ignored and outputs remain unchanged. The effect of CEN sampled HIGH on the device outputs is as if the LOW-to-HIGH clock transition did not occur. For normal operation, CEN must be sampled LOW at rising edge of clock.                                                                                                                                                                                                                 |

## Pin Descriptions—512K × 18 (continued)

| 512K × 18<br>TQFP Pins                                                          | 512K × 18<br>PBGA Pins                                                                       | Pin<br>Name            | Туре                       | Pin Description                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 88                                                                              | 4H                                                                                           | WEN                    | Input-<br>Synchronous      | Read Write: WEN signal is a synchronous input that identifies whether the current loaded cycle and the subsequent burst cycles initiated by ADV/LD is a Read or Write operation. The data bus activity for the current cycle takes place two clock cycles later.                                                                                                                                |

| 89                                                                              | 4K                                                                                           | CLK                    | Input-<br>Synchronous      | Clock: This is the clock input to CY7C1356A. Except for $\overline{OE}$ , ZZ, and MODE, all timing references for the device are made with respect to the rising edge of CLK.                                                                                                                                                                                                                   |

| 98,<br>92                                                                       | 4E, 6B                                                                                       | CE,<br>CE <sub>3</sub> | Input-<br>Synchronous      | Synchronous Active LOW Chip Enable: CE and CE <sub>3</sub> are used with CE <sub>2</sub> to enable the CY7C1356A. CE or CE <sub>3</sub> sampled HIGH or CE <sub>2</sub> sampled LOW, along with ADV/LD LOW at the rising edge of clock, initiates a deselect cycle. The data bus will be High-Z two clock cycles after chip deselect is initiated.                                              |

| 97                                                                              | 2B                                                                                           | CE <sub>2</sub>        | Input-<br>Synchronous      | Synchronous Active HIGH Chip Enable: $CE_2$ is used with $\overline{CE}$ and $\overline{CE}_3$ to enable the chip. $CE_2$ has inverted polarity but otherwise is identical to $\overline{CE}$ and $\overline{CE}_3$ .                                                                                                                                                                           |

| 86                                                                              | 4F                                                                                           | OE                     | Input                      | Asynchronous Output Enable: OE must be LOW to Read data. When OE is HIGH, the I/O pins are in high-impedance state. OE does not need to be actively controlled for Read and write cycles. In normal operation, OE can be tied LOW.                                                                                                                                                              |

| 85                                                                              | 4B                                                                                           | ADV<br>/LD             | Input-<br>Synchronous      | Advance/Load: ADV/LD is a synchronous input that is used to load the internal registers with new address and control signals when it is sampled LOW at the rising edge of clock with the chip is selected. When ADV/LD is sampled HIGH, then the internal burst counter is advanced for any burst that was in progress. The external addresses and WEN are ignored when ADV/LD is sampled HIGH. |

| 31                                                                              | 3R                                                                                           | MOD<br>E               | Input-<br>Static           | <b>Burst Mode</b> : When MODE is HIGH or NC, the interleaved burst sequence is selected. When MODE is LOW, the linear burst sequence is selected. MODE is a static DC input.                                                                                                                                                                                                                    |

| 64                                                                              | 7T                                                                                           | ZZ                     | Input-<br>Asynchronou<br>s | <b>Sleep Enable</b> : This active HIGH input puts the device in low power consumption standby mode. For normal operation, this input has to be either LOW or NC.                                                                                                                                                                                                                                |

| 58, 59, 62, 63,<br>68, 69, 72, 73,<br>74<br>8, 9, 12, 13, 18,<br>19, 22, 23, 24 | (a) 6D, 7E, 6F,<br>7G, 6H, 7K, 6L,<br>6N, 7P<br>(b) 1D, 2E, 2G,<br>1H, 2K, 1L, 2M,<br>1N, 2P | DQa<br>DQb             | Input/<br>Output           | <b>Data Inputs/Outputs</b> : Both the data input path and data output path are registered and triggered by the rising edge of CLK. Byte "a" is DQa pins; Byte "b" is DQb pins.                                                                                                                                                                                                                  |

| 38<br>39<br>43                                                                  | 2U<br>3U<br>4U                                                                               | TMS<br>TDI<br>TCK      | Input                      | <b>IEEE 1149.1 Test Inputs</b> : LVTTL-level inputs. If Serial Boundary Scan (JTAG) is not used, these pins can be floating (i.e., No Connect) or be connected to $V_{CC}$ .                                                                                                                                                                                                                    |

| 42                                                                              | 5U                                                                                           | TDO                    | Output                     | <b>IEEE 1149.1 Test Inputs</b> : LVTTL-level output. If Serial Boundary Scan (JTAG) is not used, these pins can be floating (i.e., No Connect).                                                                                                                                                                                                                                                 |

| 14, 15, 16, 41,<br>65, 66, 91                                                   | 4C, 2J, 4J, 6J,<br>4R, 5R                                                                    | V <sub>CC</sub>        | Supply                     | <b>Power Supply</b> : +3.3V –5% and +5%.                                                                                                                                                                                                                                                                                                                                                        |

| 5, 10, 17, 21,<br>26, 40, 55, 60,<br>67, 71, 76, 90                             | 3D, 5D, 3E, 5E,<br>3F, 5F, 5G, 3H,<br>5H, 3K, 5K, 3L,<br>3M, 5M, 3N,<br>5N, 3P, 5P           | V <sub>SS</sub>        | Ground                     | Ground: GND.                                                                                                                                                                                                                                                                                                                                                                                    |

| 4, 11, 20, 27,<br>54, 61, 70, 77                                                | 1A, 7A, 1F, 7F,<br>1J, 7J, 1M, 7M,<br>1U, 7U                                                 | V <sub>CCQ</sub>       | I/O Supply                 | Output Buffer Supply: +3.3V –0.165V and +0.165V for 3.3V I/O. +2.5V –0.125V and +0.4V for 2.5V I/O.                                                                                                                                                                                                                                                                                             |

### Pin Descriptions—512K × 18 (continued)

| 512K × 18<br>TQFP Pins   | 512K × 18<br>PBGA Pins                                                                                                                              | Pin<br>Name | Type | Pin Description                                                                                                                |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------|

| 28-30,<br>51-53, 56, 57, | 4A, 1B, 7B, 1C,<br>7C, 2D, 4D, 7D,<br>1E, 6E, 2F, 1G,<br>6G, 2H, 7H, 3J,<br>5J, 1K, 6K, 2L,<br>4L, 7L, 6M, 2N,<br>7N, 1P, 6P, 1R,<br>7R, 1T, 4T, 6U | NC          | ÷.   | <b>No Connect</b> : These signals are not internally connected. It can be left floating or be connected to $V_{CC}$ or to GND. |

### Partial Truth Table for Read/Write<sup>[2]</sup>

| Function                          | WEN | BWa | BWb | <b>BWc</b> <sup>[4]</sup> | BWd <sup>[4]</sup> |

|-----------------------------------|-----|-----|-----|---------------------------|--------------------|

| Read                              | Н   | Х   | Х   | Х                         | Х                  |

| No Write                          | L   | Н   | Н   | Н                         | Н                  |

| Write Byte a (DQa) <sup>[3]</sup> | L   | L   | Н   | Н                         | Н                  |

| Write Byte b (DQb) <sup>[3]</sup> | L   | Н   | L   | Н                         | Н                  |

| Write Byte c (DQc) <sup>[3]</sup> | L   | Н   | Н   | L                         | Н                  |

| Write Byte d (DQd) <sup>[3]</sup> | L   | Н   | Н   | Н                         | L                  |

| Write all bytes                   | L   | L   | L   | L                         | L                  |

### **Interleaved Burst Address Table** $(MODE = V_{CC} \text{ or NC})$

| First<br>Address<br>(external) | Second<br>Address<br>(internal) | Third<br>Address<br>(internal) | Fourth<br>Address<br>(internal) <sup>[5]</sup> |

|--------------------------------|---------------------------------|--------------------------------|------------------------------------------------|

| AA <sub>00</sub>               | AA <sub>01</sub>                | AA <sub>10</sub>               | AA <sub>11</sub>                               |

| AA <sub>01</sub>               | AA <sub>00</sub>                | AA <sub>11</sub>               | AA <sub>10</sub>                               |

| AA <sub>10</sub>               | AA <sub>11</sub>                | AA <sub>00</sub>               | AA <sub>01</sub>                               |

| AA <sub>11</sub>               | AA <sub>10</sub>                | AA <sub>01</sub>               | AA <sub>00</sub>                               |

### **Linear Burst Address Table** $(MODE = V_{SS})$

| First<br>Address<br>(external) | Second<br>Address<br>(internal) | Third<br>Address<br>(internal) | Fourth<br>Address<br>(internal) <sup>[5]</sup> |

|--------------------------------|---------------------------------|--------------------------------|------------------------------------------------|

| AA <sub>00</sub>               | AA <sub>01</sub>                | AA <sub>10</sub>               | AA <sub>11</sub>                               |

| AA <sub>01</sub>               | AA <sub>10</sub>                | AA <sub>11</sub>               | AA <sub>00</sub>                               |

| AA <sub>10</sub>               | AA <sub>11</sub>                | AA <sub>00</sub>               | AA <sub>01</sub>                               |

| AA <sub>11</sub>               | AA <sub>00</sub>                | AA <sub>01</sub>               | AA <sub>10</sub>                               |

- L means logic LOW. H means logic HIGH. X means Don't Care.

Multiple bytes may be selected during the same cycle.

BWc and BWd apply to 256K × 36 device only.

- 5. Upon completion of the Burst sequence, the counter wraps around to its initial state and continues counting.

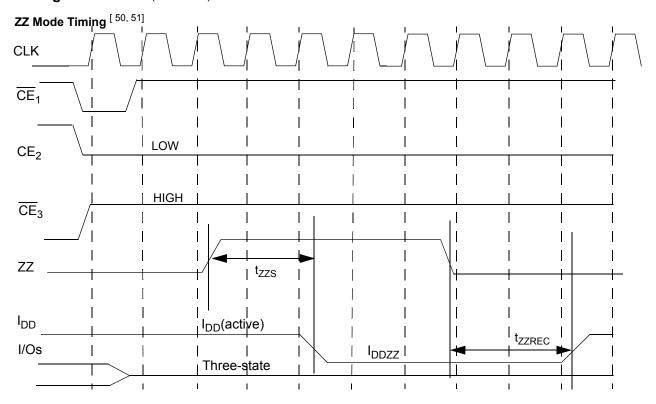

#### Sleep Mode

The ZZ input pin is an asynchronous input. Asserting ZZ places the SRAM in a power conservation "sleep" mode. Two clock cycles are required to enter into or exit from this "sleep" mode. While in this mode, data integrity is guaranteed. Accesses pending when entering the "sleep" mode are not considered valid nor is the completion of the operation guaranteed. The device must be deselected prior to entering the "sleep" mode. CEs must remain inactive for the duration of t<sub>ZZREC</sub> after the ZZ input returns LOW. CEN needs to active before going into the ZZ mode and before you want to come back out of the ZZ mode.

### **ZZ Mode Electrical Characteristics**

| Parameter         | Description                | Test Conditions        | Min.              | Max.              | Unit |

|-------------------|----------------------------|------------------------|-------------------|-------------------|------|

| I <sub>DDZZ</sub> | Sleep mode standby current | $ZZ \ge V_{DD} - 0.2V$ |                   | 10                | mA   |

| t <sub>ZZS</sub>  | Device operation to ZZ     | $ZZ \ge V_{DD} - 0.2V$ |                   | 2t <sub>CYC</sub> | ns   |

| tzzrec            | ZZ recovery time           | ZZ ≤ 0.2V              | 2t <sub>CYC</sub> |                   | ns   |

### Truth Table<sup>[9, 10, 11, 12, 13, 14, 15, 16, 17]</sup>

| Operation                                 | Previous<br>Cycle | Address<br>Used | WEN | ADV/LD | CE | CEN | BWx | OE | DQ<br>(2 cycles later) |

|-------------------------------------------|-------------------|-----------------|-----|--------|----|-----|-----|----|------------------------|

| Deselect Cycle                            | Х                 | Х               | Х   | L      | Н  | L   | Х   | Х  | High-Z                 |

| Continue Deselect/NOP <sup>[18]</sup>     | Deselect          | Х               | Х   | Н      | Х  | L   | Х   | Х  | High-Z                 |

| Read Cycle (Begin Burst)                  | Х                 | External        | Н   | L      | L  | L   | Х   | Х  | Q                      |

| Read Cycle (Continue Burst)[18]           | Read              | Next            | Х   | Н      | Х  | L   | Х   | Х  | Q                      |

| Dummy Read (Begin Burst) <sup>[19]</sup>  | Х                 | External        | Н   | L      | L  | L   | Х   | Н  | High-Z                 |

| Dummy Read (Continue Burst)[18, 19]       | Read              | Next            | Х   | Н      | Х  | L   | Х   | Н  | High-Z                 |

| Write Cycle (Begin Burst)                 | Х                 | External        | L   | L      | L  | L   | L   | Х  | D                      |

| Write Cycle (Continue Burst)[18]          | Write             | Next            | Х   | Н      | Х  | L   | L   | Х  | D                      |

| Abort Write (Begin Burst) <sup>[19]</sup> | Х                 | External        | L   | L      | L  | L   | Н   | Х  | High-Z                 |

| Abort Write (Continue Burst)[18, 19]      | Write             | Next            | Х   | Н      | Х  | L   | Н   | Х  | High-Z                 |

| Ignore Clock Edge/NOP <sup>[20]</sup>     | Х                 | Х               | Х   | Н      | Х  | Н   | Х   | Х  | _                      |

- 6. This assumes that  $\overline{\text{CEN}}$ ,  $\overline{\text{CE}}$ ,  $\overline{\text{CE}}_2$  and  $\overline{\text{CE}}_3$  are all True.

- 7. All addresses, control and data-in are only required to meet set-up and hold time with respect to the rising edge of clock. Data out is valid after a clock-to-data delay from the rising edge of clock.

- 8. DQc and DQd apply to 256K × 36 device only.

- 9. Lmeans logic LOW. H means logic HIGH. X means Don't Care. High-Z means High Impedance. BWx = L means [BWa\*BWb\*BWc\*BWd] = LOW. BWx = H means [BWa\*BWb\*BWc\*BWd] = HIGH. BWc and BWd apply to 256K × 36 device only.

- 10. <u>CE</u> = H means <u>CE</u> and <u>CE</u><sub>3</sub> are LOW along <u>with CE</u><sub>2</sub> HIGH. <u>CE</u> = L means <u>CE</u> or <u>CE</u><sub>3</sub> are <u>HIGH</u> or <u>CE</u><sub>2</sub> is LOW. <u>CE</u> = X means <u>CE</u><sub>3</sub>, and <u>CE</u><sub>2</sub> are Don't Care. 11. BWa enables Write to byte "a" (DQa pins). BWb enables Write to byte "b" (DQb pins). BWc enables Write to byte "c" (DQc pins). BWd enables Write to byte "d" (DQd pins). DQc, DQd, BWc, and BWd apply to 256K × 36 device only.

12. The device is not in Sleep Mode, i.e., the ZZ pin is LOW.

- 13. During Sleep Mode, the ZZ pin is HIGH and all the address pins and control pins are "Don't Care." The SNOOZE MODE can only be entered two cycles after the Write cycle, otherwise the Write cycle may not be completed.

- 14. All inputs, except  $\overline{\text{OE}}$ , ZZ, and MODE pins, must meet set-up time and hold time specification against the clock (CLK) LOW-to-HIGH transition edge.

- 15. OE may be tied to LOW for all the operation. This device automatically turns off the output driver during Write cycle.

- 16. Device outputs are ensured to be in High-Z during device power-up.

- 17. This device contains a two-bit burst counter. The address counter is incremented for all Continue Burst cycles. Address wraps to the initial address every fourth burst cycle.

- 18. Continue Burst cycles, whether Read or Write, use the same control signals. The type of cycle performed, Read or Write, depends upon the WEN control signal at the Begin Burst cycle. A Continue Deselect cycle can only be entered if a DESELECT cycle is executed first.

- 19. Dummy Read and Abort Write cycles can be entered to set up subsequent Read or Write cycles or to increment the burst counter.

- 20. When an Ignore Clock Edge cycle enters, the output data (Q) will remain the same if the previous cycle is Read cycle or remain High-Z if the previous cycle is Write or DESELECT cycle.

### IEEE 1149.1 Serial Boundary Scan (JTAG)

#### Overview

This device incorporates a serial boundary scan access port (TAP). This port is designed to operate in a manner consistent with IEEE Standard 1149.1–1990 (commonly referred to as JTAG), but does not implement all of the functions required for IEEE 1149.1 compliance. Certain functions have been modified or eliminated because their implementation places extra delays in the critical speed path of the device. Nevertheless, the device supports the standard TAP controller architecture (the TAP controller is the state machine that controls the TAPs operation) and can be expected to function in a manner that does not conflict with the operation of devices with IEEE Standard 1149.1-compliant TAPs. The TAP operates using LVTTL/LVCMOS logic level signaling.

#### **Disabling the JTAG Feature**

It is possible to use this device without using the JTAG feature. To disable the TAP controller without interfering with normal operation of the device, TCK should be tied LOW ( $V_{SS}$ ) to prevent clocking the device. TDI and TMS are internally pulled up and may be unconnected. They may alternately be pulled up to  $V_{CC}$  through a resistor. TDO should be left unconnected. Upon power-up the device will come up in a reset state which will not interfere with the operation of the device.

#### **Test Access Port**

#### TCK-Test Clock (INPUT)

Clocks all TAP events. All inputs are captured on the rising edge of TCK and all outputs propagate from the falling edge of TCK.

#### TMS-Test Mode Select (INPUT)

The TMS input is sampled on the rising edge of TCK. This is the command input for the TAP controller state machine. It is allowable to leave this pin unconnected if the TAP is not used. The pin is pulled up internally, resulting in a logic HIGH level.

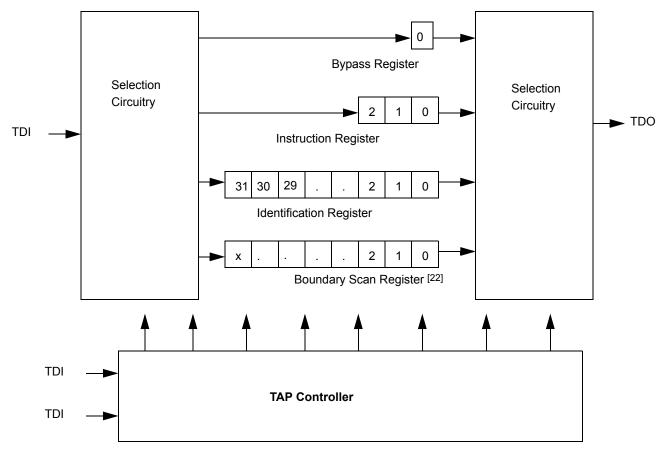

#### TDI-Test Data In (INPUT)

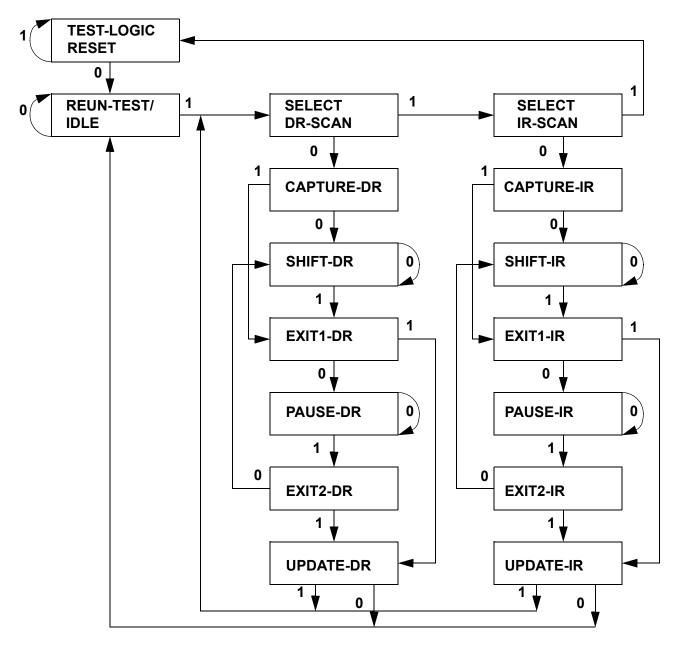

The TDI input is sampled on the rising edge of TCK. This is the input side of the serial registers placed between TDI and TDO. The register placed between TDI and TDO is determined by the state of the TAP controller state machine and the instruction that is currently loaded in the TAP instruction register (refer to *Figure 1*, TAP Controller State Diagram). It is allowable to leave this pin unconnected if it is not used in an application. The pin is pulled up internally, resulting in a logic HIGH level. TDI is connected to the most significant bit (MSB) of any register (see *Figure 2*).

### TDO-Test Data Out (OUTPUT)

The TDO output pin is used to serially clock data-out from the registers. The output that is active depending on the state of the TAP state machine (refer to *Figure 1*, TAP Controller State Diagram). Output changes in response to the falling edge of TCK. This is the output side of the serial registers placed between TDI and TDO. TDO is connected to the LSB of any register (see *Figure 2*).

#### Performing a TAP Reset

The TAP circuitry does not have a reset pin ( $\overline{TRST}$ , which is optional in the IEEE 1149.1 specification). A RESET can be performed for the TAP controller by forcing TMS HIGH ( $V_{CC}$ ) for five rising edges of TCK and pre-loads the instruction register with the IDCODE command. This type of reset does not affect the operation of the system logic. The reset affects test logic only.

At power-up, the TAP is reset internally to ensure that TDO is in a High-Z state.

### **TAP Registers**

#### Overview

The various TAP registers are selected (one at a time) via the sequences of ones and zeros input to the TMS pin as the TCK is strobed. Each of the TAP registers is a serial shift register that captures serial input data on the rising edge of TCK and pushes serial data out on subsequent falling edge of TCK. When a register is selected, it is connected between the TDI and TDO pins.

#### **Instruction Register**

The instruction register holds the instructions that are executed by the TAP controller when it is moved into the run test/idle or the various data register states. The instructions are three bits long. The register can be loaded when it is placed between the TDI and TDO pins. The parallel outputs of the instruction register are automatically preloaded with the IDCODE instruction upon power-up or whenever the controller is placed in the test-logic reset state. When the TAP controller is in the Capture-IR state, the two least significant bits of the serial instruction register are loaded with a binary "01" pattern to allow for fault isolation of the board-level serial test data path.

#### **Bypass Register**

The bypass register is a single-bit register that can be placed between TDI and TDO. It allows serial test data to be passed through the device TAP to another device in the scan chain with minimum delay. The bypass register is set LOW ( $V_{SS}$ ) when the BYPASS instruction is executed.

#### **Boundary Scan Register**

The Boundary Scan register is connected to all the input and bidirectional I/O pins (not counting the TAP pins) on the device. This also includes a number of NC pins that are reserved for future needs. There are a total of 70 bits for x36 device and 51 bits for x18 device. The boundary scan register, under the control of the TAP controller, is loaded with the contents of the device I/O ring when the controller is in Capture-DR state and then is placed between the TDI and TDO pins when the controller is moved to Shift-DR state. The EXTEST, SAMPLE/PRELOAD and SAMPLE-Z instructions can be used to capture the contents of the I/O ring.

The Boundary Scan Order table describes the order in which the bits are connected. The first column defines the bit's position in the boundary scan register. The MSB of the register is connected to TDI, and LSB is connected to TDO. The second column is the signal name and the third column is the bump number. The third column is the TQFP pin number and the fourth column is the BGA bump number.

#### Identification (ID) Register

The ID Register is a 32-bit register that is loaded with a device and vendor specific 32-bit code when the controller is put in Capture-DR state with the IDCODE command loaded in the instruction register. The register is then placed between the TDI and TDO pins when the controller is moved into Shift-DR state. Bit 0 in the register is the LSB and the first to reach TDO when shifting begins. The code is loaded from a 32-bit on-chip ROM. It describes various attributes of the device as described in the Identification Register Definitions table.

#### **TAP Controller Instruction Set**

#### Overview

There are two classes of instructions defined in the IEEE Standard 1149.1-1990; the standard (public) instructions and device specific (private) instructions. Some public instructions are mandatory for IEEE 1149.1 compliance. Optional public instructions must be implemented in prescribed ways.

Although the TAP controller in this device follows the IEEE 1149.1 conventions, it is not IEEE 1149.1-compliant because some of the mandatory instructions are not fully implemented. The TAP on this device may be used to monitor all input and I/O pads, but can not be used to load address, data, or control signals into the device or to preload the I/O buffers. In other words, the device will not perform IEEE 1149.1 EXTEST, INTEST, or the preload portion of the SAMPLE/PRELOAD command.

When the TAP controller is placed in Capture-IR state, the two least significant bits of the instruction register are loaded with 01. When the controller is moved to the Shift-IR state the instruction is serially loaded through the TDI input (while the previous contents are shifted out at TDO). For all instructions, the TAP executes newly loaded instructions only when the controller is moved to Update-IR state. The TAP instruction sets for this device are listed in the following tables.

#### **EXTEST**

EXTEST is an IEEE 1149.1 mandatory public instruction. It is to be executed whenever the instruction register is loaded with all 0s. EXTEST is not implemented in this device.

The TAP controller does recognize an all-0 instruction. When an EXTEST instruction is loaded into the instruction register, the device responds as if a SAMPLE/PRELOAD instruction has been loaded. There is one difference between two instructions. Unlike SAMPLE/PRELOAD instruction, EXTEST places the device outputs in a High-Z state.

#### **IDCODE**

The IDCODE instruction causes a vendor-specific, 32-bit code to be loaded into the ID register when the controller is in Capture-DR mode and places the ID register between the TDI and TDO pins in Shift-DR mode. The IDCODE instruction is the default instruction loaded in the instruction upon power-up and at any time the TAP controller is placed in the test-logic reset state.

#### SAMPLE-Z

If the High-Z instruction is loaded in the instruction register, all output pins are forced to a High-Z state and the boundary scan register is connected between TDI and TDO pins when the TAP controller is in a Shift-DR state.

#### SAMPLE/PRELOAD

SAMPLE/PRELOAD is an IEEE 1149.1-mandatory instruction. The PRELOAD portion of the command is not implemented in this device, so the device TAP controller is not fully IEEE 1149.1-compliant.

When the SAMPLE/PRELOAD instruction is loaded in the instruction register and the TAP controller is in the Capture-DR state, a snap shot of the data in the device's input and I/O buffers is loaded into the boundary scan register. Because the device system clock(s) are independent from the TAP clock (TCK), it is possible for the TAP to attempt to capture the input and I/O ring contents while the buffers are in transition (i.e., in a metastable state). Although allowing the TAP to sample metastable inputs will not harm the device, repeatable results can not be expected. To guarantee that the boundary scan register will capture the correct value of a signal, the device input signals must be stabilized long enough to meet the TAP controller's capture set-up plus hold time ( $t_{CS}$  plus  $t_{CH}$ ). The device clock input(s) need not be paused for any other TAP operation except capturing the input and I/O ring contents into the boundary scan register.

Moving the controller to Shift-DR state then places the boundary scan register between the TDI and TDO pins. Because the PRELOAD portion of the command is not implemented in this device, moving the controller to the Update-DR state with the SAMPLE/PRELOAD instruction loaded in the instruction register has the same effect as the Pause-DR command.

#### **BYPASS**

When the BYPASS instruction is loaded in the instruction register and the TAP controller is in the Shift-DR state, the bypass register is placed between TDI and TDO. This allows the board level scan path to be shortened to facilitate testing of other devices in the scan path.

#### Reserved

Do not use these instructions. They are reserved for future use.

Figure 1. TAP Controller State Diagram<sup>[21]</sup>

#### Note

21. The "0"/"1" next to each state represents the value at TMS at the rising edge of TCK.

Figure 2. TAP Controller Block Diagram

### **TAP Electrical Characteristics** (20°C $\leq$ T<sub>i</sub> $\leq$ 110°C; V<sub>CC</sub> = 3.3V -0.2V and +0.3V unless otherwise noted)

| Parameter        | Description                                      | Test Conditions                                             | Min.                  | Max.                  | Unit |

|------------------|--------------------------------------------------|-------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>IH</sub>  | Input High (Logic 1) Voltage <sup>[23, 24]</sup> |                                                             | 2.0                   | V <sub>CC</sub> + 0.3 | V    |

| V <sub>II</sub>  | Input Low (Logic 0) Voltage <sup>[23, 24]</sup>  |                                                             | -0.3                  | 0.8                   | V    |

| I <u>L</u>       | Input Leakage Current                            | $0V \le V_{IN} \le V_{CC}$                                  | -5.0                  | 5.0                   | μА   |

| IL <sub>I</sub>  | TMS and TDI Input Leakage Current                | $0V \le V_{IN} \le V_{CC}$                                  | -30                   | 30                    | μА   |

| ILO              | Output Leakage Current                           | Output disabled,<br>0V ≤ V <sub>IN</sub> ≤ V <sub>CCQ</sub> | -5.0                  | 5.0                   | μА   |

| V <sub>OLC</sub> | LVCMOS Output Low Voltage <sup>[23, 25]</sup>    | I <sub>OLC</sub> = 100 μA                                   |                       | 0.2                   | V    |

| V <sub>OHC</sub> | LVCMOS Output High Voltage <sup>[23, 25]</sup>   | I <sub>OHC</sub> = 100 μA                                   | V <sub>CC</sub> – 0.2 |                       | V    |

| V <sub>OLT</sub> | LVTTL Output Low Voltage <sup>[23]</sup>         | I <sub>OLT</sub> = 8.0 mA                                   |                       | 0.4                   | V    |

| V <sub>OHT</sub> | LVTTL Output High Voltage <sup>[23]</sup>        | I <sub>OHT</sub> = 8.0 mA                                   | 2.4                   |                       | V    |

Notes:

22. X = 69 for the x36 configuration;

X = 50 for the x18 configuration.

23. All voltage referenced to V<sub>SS</sub> (GND).

24. Overshoot: V<sub>IH</sub>(AC) ≤ V<sub>CC</sub> + 1.5V for t ≤ t<sub>KHKH</sub>/2; undershoot: V<sub>IL</sub>(AC) ≤ -0.5V for t ≤ t<sub>KHKH</sub>/2: power-up: V<sub>IH</sub> ≤ 3.6V and V<sub>CC</sub> ≤ 3.135V and V<sub>CCQ</sub> ≤ 1.4V for t ≤ 200 ms. During normal operation, V<sub>CCQ</sub> must not exceed V<sub>CC</sub>. Control input signals (such as WEN and ADV/LD) may not have pulse widths less than t<sub>KHKL</sub> (min.).

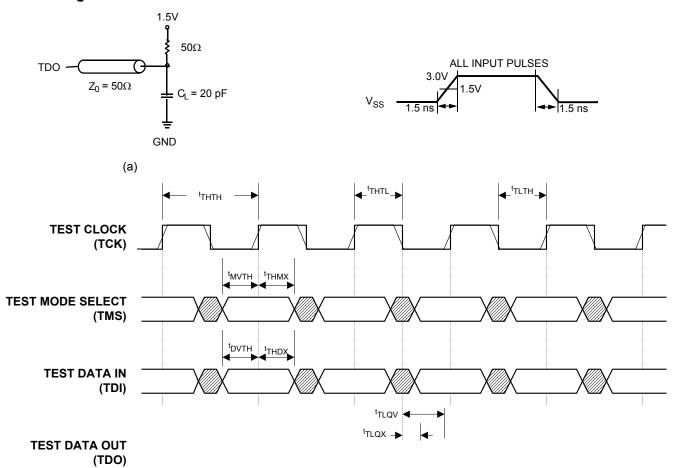

### TAP AC Switching Characteristics Over the Operating Range<sup>[26, 27]</sup>

| Parameter           | Description             | Min.     | Max. | Unit |

|---------------------|-------------------------|----------|------|------|

| Clock               |                         | <u>.</u> |      | •    |

| t <sub>THTH</sub>   | Clock Cycle Time        | 20       |      | ns   |

| f <sub>TF</sub>     | Clock Frequency         |          | 50   | MHz  |

| t <sub>THTL</sub>   | Clock HIGH Time         | 8        |      | ns   |

| t <sub>TLTH</sub>   | Clock LOW Time          | 8        |      | ns   |

| <b>Output Times</b> | 3                       |          | •    | •    |

| t <sub>TLQX</sub>   | TCK LOW to TDO Unknown  | 0        |      | ns   |

| t <sub>TLQV</sub>   | TCK LOW to TDO Valid    |          | 10   | ns   |

| t <sub>DVTH</sub>   | TDI Valid to TCK HIGH   | 5        |      | ns   |

| t <sub>THDX</sub>   | TCK HIGH to TDI Invalid | 5        |      | ns   |

| Set-up Times        | •                       |          | •    | •    |

| t <sub>MVTH</sub>   | TMS Set-up              | 5        |      | ns   |

| t <sub>TDIS</sub>   | TDI Set-up              | 5        |      | ns   |

| t <sub>CS</sub>     | Capture Set-up          | 5        |      | ns   |

| Hold Times          | •                       |          | •    | •    |

| t <sub>THMX</sub>   | TMS Hold                | 5        |      | ns   |

| t <sub>TDIH</sub>   | TDI Hold                | 5        |      | ns   |

| t <sub>CH</sub>     | Capture Hold            | 5        |      | ns   |

<sup>26.</sup>  $t_{CS}$  and  $t_{CH}$  refer to the set-up and hold time requirements of latching data from the boundary scan register. 27. Test conditions are specified using the load in TAP AC test conditions.

### **TAP Timing and Test Conditions**

### **Identification Register Definitions**

| Instruction Field                  | 256K x 36   | 512K x 18   | Description                                    |

|------------------------------------|-------------|-------------|------------------------------------------------|

| Revision Number(31:28)             | XXXX        | XXXX        | Reserved for revision number.                  |

| Device Depth (27:23)               | 00110       | 00111       | Defines depth of 256K or 512K words.           |

| Device Width (22:18)               | 00100       | 00011       | Defines width of x36 or x18 bits.              |

| Reserved (17:12)                   | XXXXXX      | XXXXXX      | Reserved for future use.                       |

| Cypress Jedec ID Code (11:1)       | 00011100100 | 00011100100 | Allows unique identification of DEVICE vendor. |

| ID Register Presence Indicator (0) | 1           | 1           | Indicates the presence of an ID register.      |

### **Scan Register Sizes**

| Register Name | Bit Size (x36) | Bit Size (x18) |

|---------------|----------------|----------------|

| Instruction   | 3              | 3              |

| Bypass        | 1              | 1              |

| ID            | 32             | 32             |

| Boundary Scan | 70             | 51             |

### **Instruction Codes**

| Instruction    | Code | Description                                                                                                                                                                                                                                    |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST         | 000  | <b>Captures I/O ring contents</b> . Places the boundary scan register between TDI and TDO. Forces all device outputs to High-Z state. This instruction is not IEEE 1149.1-compliant.                                                           |

| IDCODE         | 001  | Preloads ID register with vendor ID code and places it between TDI and TDO. This instruction does not affect device operations.                                                                                                                |

| SAMPLE-Z       | 010  | <b>Captures I/O ring contents</b> . Places the boundary scan register between TDI and TDO. Forces all device outputs to High-Z state.                                                                                                          |

| RESERVED       | 011  | Do not use these instructions; they are reserved for future use.                                                                                                                                                                               |

| SAMPLE/PRELOAD | 100  | Captures I/O ring contents. Places the boundary scan register between TDI and TDO. This instruction does not affect device operations. This instruction does not implement IEEE 1149.1 PRELOAD function and is therefore not 1149.1-compliant. |

| RESERVED       | 101  | Do not use these instructions; they are reserved for future use.                                                                                                                                                                               |

| RESERVED       | 110  | Do not use these instructions; they are reserved for future use.                                                                                                                                                                               |

| BYPASS         | 111  | Places the bypass register between TDI and TDO. This instruction does not affect device operations.                                                                                                                                            |

### **Boundary Scan Order (256K × 36)**

| Bit# | Signal Name | TQFP | Bump ID |

|------|-------------|------|---------|

| 1    | A           | 44   | 2R      |

| 2    | Α           | 45   | 3T      |

| 3    | Α           | 46   | 4T      |

| 4    | А           | 47   | 5T      |

| 5    | A           | 48   | 6R      |

| 6    | A           | 49   | 3B      |

| 7    | A           | 50   | 5B      |

| 8    | DQa         | 51   | 6P      |

| 9    | DQa         | 52   | 7N      |

| 10   | DQa         | 53   | 6M      |

| 11   | DQa         | 56   | 7L      |

| 12   | DQa         | 57   | 6K      |

| 13   | DQa         | 58   | 7P      |

| 14   | DQa         | 59   | 6N      |

| 15   | DQa         | 62   | 6L      |

| 16   | DQa         | 63   | 7K      |

| 17   | ZZ          | 64   | 7T      |

| 18   | DQb         | 68   | 6H      |

| 19   | DQb         | 69   | 7G      |

| 20   | DQb         | 72   | 6F      |

| 21   | DQb         | 73   | 7E      |

| 22   | DQb         | 74   | 6D      |

| 23   | DQb         | 75   | 7H      |

| 24   | DQb         | 78   | 6G      |

| 25   | DQb         | 79   | 6E      |

| 26   | DQb         | 80   | 7D      |

| 27   | Α           | 81   | 6A      |

| 28   | A           | 82   | 5A      |

### Boundary Scan Order (256K × 36) (continued)

| Bit# | Signal Name     | TQFP | Bump ID |

|------|-----------------|------|---------|

| 29   | А               | 83   | 4G      |

| 30   | NC              | 84   | 4A      |

| 31   | ADV/LD          | 85   | 4B      |

| 32   | ŌĒ              | 86   | 4F      |

| 33   | CEN             | 87   | 4M      |

| 34   | WEN             | 88   | 4H      |

| 35   | CLK             | 89   | 4K      |

| 36   | CE <sub>3</sub> | 92   | 6B      |

| 37   | BWa             | 93   | 5L      |

| 38   | BWb             | 94   | 5G      |

| 39   | BWc             | 95   | 3G      |

| 40   | BWd             | 96   | 3L      |

| 41   | CE <sub>2</sub> | 97   | 2B      |

| 42   | CE              | 98   | 4E      |

| 43   | Α               | 99   | 3A      |

| 44   | Α               | 100  | 2A      |

| 45   | DQc             | 1    | 2D      |

| 46   | DQc             | 2    | 1E      |

| 47   | DQc             | 3    | 2F      |

| 48   | DQc             | 6    | 1G      |

| 49   | DQc             | 7    | 2H      |

| 50   | DQc             | 8    | 1D      |

| 51   | DQc             | 9    | 2E      |

| 52   | DQc             | 12   | 2G      |

| 53   | DQc             | 13   | 1H      |

| 54   | NC              | 14   | 5R      |

| 55   | DQd             | 18   | 2K      |

| 56   | DQd             | 19   | 1L      |

|      |                 |      |         |

## Boundary Scan Order (256K × 36) (continued)

| Bit# | Signal Name | TQFP | Bump ID |

|------|-------------|------|---------|

| 57   | DQd         | 22   | 2M      |

| 58   | DQd         | 23   | 1N      |

| 59   | DQd         | 24   | 2P      |

| 60   | DQd         | 25   | 1K      |

| 61   | DQd         | 28   | 2L      |

| 62   | DQd         | 29   | 2N      |

| 63   | DQd         | 30   | 1P      |

| 64   | MODE        | 31   | 3R      |

| 65   | Α           | 32   | 2C      |

| 66   | Α           | 33   | 3C      |

| 67   | Α           | 34   | 5C      |

| 68   | Α           | 35   | 6C      |

| 69   | A1          | 36   | 4N      |

| 70   | A0          | 37   | 4P      |

### **Boundary Scan Order (512K × 18)**

| Bit# | Signal Name | TQFP | Bump ID |

|------|-------------|------|---------|

| 1    | Α           | 44   | 2R      |

| 2    | А           | 45   | 2T      |

| 3    | Α           | 46   | 3T      |

| 4    | А           | 47   | 5T      |

| 5    | A           | 48   | 6R      |

| 6    | A           | 49   | 3B      |

| 7    | A           | 50   | 5B      |

| 8    | DQa         | 58   | 7P      |

| 9    | DQa         | 59   | 6N      |

| 10   | DQa         | 62   | 6L      |

| 11   | DQa         | 63   | 7K      |

| 12   | ZZ          | 64   | 7T      |

| 13   | DQa         | 68   | 6H      |

| 14   | DQa         | 69   | 7G      |

| 15   | DQa         | 72   | 6F      |

| 16   | DQa         | 73   | 7E      |

| 17   | DQa         | 74   | 6D      |

| 18   | A           | 80   | 6T      |

| 19   | A           | 81   | 6A      |

| 20   | A           | 82   | 5A      |

| 21   | A           | 83   | 4G      |

| 22   | NC          | 84   | 4A      |

| 23   | ADV/LD      | 85   | 4B      |

| 24   | ŌĒ          | 86   | 4F      |

| 25   | CEN         | 87   | 4M      |

| 26   | WEN         | 88   | 4H      |

| 27   | CLK         | 89   | 4K      |

## **Boundary Scan Order (512K × 18)** (continued)

| Bit# | Signal Name     | TQFP | Bump ID |

|------|-----------------|------|---------|

| 28   | CE <sub>3</sub> | 92   | 6B      |

| 29   | BWa             | 93   | 5L      |

| 30   | BWb             | 94   | 3G      |

| 31   | CE <sub>2</sub> | 97   | 2B      |

| 32   | CE              | 98   | 4E      |

| 33   | Α               | 99   | 3A      |

| 34   | A               | 100  | 2A      |

| 35   | DQb             | 8    | 1D      |

| 36   | DQb             | 9    | 2E      |

| 37   | DQb             | 12   | 2G      |

| 38   | DQb             | 13   | 1H      |

| 39   | NC              | 14   | 5R      |

| 40   | DQb             | 18   | 2K      |

| 41   | DQb             | 19   | 1L      |

| 42   | DQb             | 22   | 2M      |

| 43   | DQb             | 23   | 1N      |

| 44   | DQb             | 24   | 2P      |

| 45   | MODE            | 31   | 3R      |

| 46   | Α               | 32   | 2C      |

| 47   | Α               | 33   | 3C      |

| 48   | Α               | 34   | 5C      |

| 49   | Α               | 35   | 6C      |

| 50   | A1              | 36   | 4N      |

| 51   | A0              | 37   | 4P      |

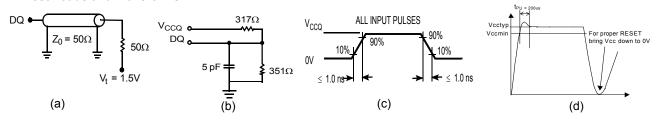

### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.) Voltage on V<sub>CC</sub> Supply Relative to V<sub>SS</sub> ...... –0.5V to +4.6V  $V_{\text{IN}}$  .....-0.5V to  $V_{\text{CC}}\text{+0.5V}$ Storage Temperature (plastic) ...... –55°C to +125° Junction Temperature .....+125° Power Dissipation ......2.0W

| Short Circuit Output Current                           | 50 mA     |

|--------------------------------------------------------|-----------|

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | . > 2001V |

| Latch-up Current                                       | > 200 mA  |

### **Operating Range**

| Range      | Ambient<br>Temperature <sup>[28]</sup> | <b>V</b> <sub>CC</sub> <sup>[29,30]</sup> | <b>V</b> <sub>CCQ</sub> <sup>[29,30]</sup> |

|------------|----------------------------------------|-------------------------------------------|--------------------------------------------|

| Commercial | 0°C to +70°C                           | $3.3V \pm 5\%$                            |                                            |

| Industrial | –40°C to +85°C                         |                                           | 3.3V+10%                                   |

### **Electrical Characteristics** Over the Operating Range

| Parameter        | Description                                       | Test Conditions                                  | Min.  | Max.                  | Unit |

|------------------|---------------------------------------------------|--------------------------------------------------|-------|-----------------------|------|

| $V_{IHD}$        | Input High (Logic 1) Voltage <sup>[23, 31]</sup>  | All other Inputs                                 | 2.0   | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IH</sub>  |                                                   | 3.3V I/O                                         | 2.0   |                       | V    |

|                  |                                                   | 2.5V I/O                                         | 1.7   |                       | V    |

| V <sub>IL</sub>  | Input Low (Logic 0) Voltage <sup>[23, 31]</sup>   | 3.3V I/O                                         | -0.3  | 0.8                   | V    |

|                  |                                                   | 2.5V I/O                                         | -0.3  | 0.7                   | V    |