### CDC7005 3.3-V HIGH PERFORMANCE CLOCK SYNTHESIZER AND JITTER CLEANER

SCAS685H - DECEMBER 2002 - REVISED FEBRUARY 2006

- High Performance 1:5 PLL Clock Synchronizer

- Two Clock Inputs: VCXO\_IN Clock Is Synchronized To REF\_IN Clock

- Synchronizes Frequencies Up To 800 MHz (VCXO\_IN)

- Supports Five Differential LVPECL Outputs

- Each Output Frequency Is Selectable By x1, /2, /4, /8, /16

- All Outputs Are Synchronized

- Integrated Low-Noise OPA For External Low-Pass Filter

- Efficient Jitter Screening From Low PLL Loop Bandwidth

- Low-Phase Noise Characteristic

- Programmable Delay For Phase Adjustments

- Predivider Loop BW Adjustment

- SPI Controllable Division Setting

- Power-Up Control Forces LVPECL Outputs to 3-State at VCC < 1.5 V</li>

- 3.3-V Power Supply

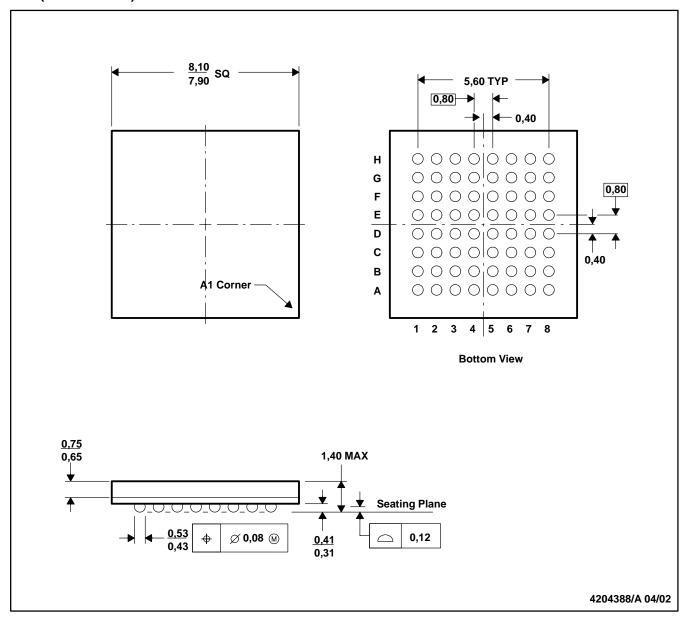

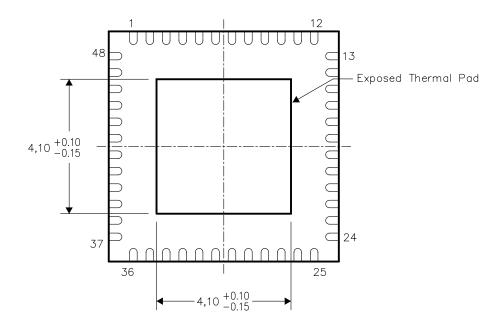

- Packaged In 64-Pin BGA (0,8 mm Pitch ZVA) or 48-Pin QFN (RGZ)

- Industrial Temperature Range –40°C To 85°C

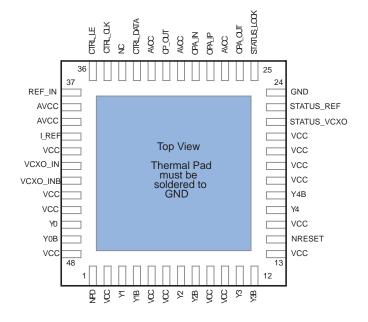

### description

The CDC7005 is a high-performance, low-phase noise, and low-skew clock synthesizer and jitter cleaner that synchronizes the voltage controlled crystal oscillator (VCXO) frequency to the reference clock. The programmable predividers M and N give a high flexibility to the frequency ratio of the reference clock to VCXO: VCXO\_IN/REF\_IN = (NxP)/M. The VCXO\_IN clock operates up to 800 MHz. Through the selection of external

VCXO and loop filter components, the PLL loop bandwidth and damping factor can be adjusted to meet different system requirements. Each of the five differential LVPECL outputs are programmable by the serial peripheral interface (SPI). The SPI allows individual control of frequency and enable/disable state of each output. The device operates in 3.3-V environment. The built-in latches ensure that all outputs are synchronized.

The CDC7005 is characterized for operation from -40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

### functional block diagram

# 3.3-V HIGH PERFORMANCE CLOCK SYNTHESIZER AND JITTER CLEANER SCAS685H - DECEMBER 2002 - REVISED FEBRUARY 2006

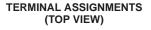

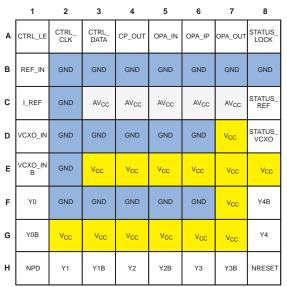

### **Terminal Functions**

| TERMINAL    |                                                                                     |                                                              |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | BGA                                                                                 | QFN                                                          | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| AVCC        | C3, C4, C5, C6, C7                                                                  | 27, 30, 32, 38, 39                                           | Power  | 3.3-V analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| CP_OUT      | A4                                                                                  | 31                                                           | 0      | Charge pump output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| CTRL_LE     | A1                                                                                  | 36                                                           | _      | LVCMOS input, control load enable for serial programmable interface (SPI) with hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| CTRL_CLK    | A2                                                                                  | 35                                                           | I      | LVCMOS input, serial control clock input for SPI, with hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| CTRL_DATA   | A3                                                                                  | 33                                                           | 1      | LVCMOS input, serial control data input for SPI, with hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| GND         | B2, B3, B4, B5, B6,<br>B7, B8, C2, D2, D3,<br>D4, D5, D6, E2, F2,<br>F3, F4, F5, F6 | Thermal pad and pin 24                                       | Ground | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| I_REF       | C1                                                                                  | 40                                                           | 0      | Current path for external reference resistor (12 k $\Omega$ ±1%) to support an accurate charge pump current, optional. Do not use any capacitor across this resistor to prevent noise coupling via this node. If internal 12 k $\Omega$ is selected (default setting), this pin can be left open.                                                                                                                                                                                                                                                                                                                    |  |  |

| NC          | -                                                                                   | 34                                                           | -      | Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| NPD         | H1                                                                                  | 1                                                            | I      | LVCMOS input, asynchronous power down (PD) signal active on low. Switches all current sources off, resets all dividers to default values, and 3-states all outputs. Has an internal 150-k $\Omega$ pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| NRESET      | H8                                                                                  | 14                                                           | _      | LVCMOS input, asynchronous reset signal active on low. Resets the counter of all dividers to zero keeping its divider values the same. It has an internal $150\text{-k}\Omega$ pullup resistor. Yx outputs are switched low during reset.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| OPA_IN      | A5                                                                                  | 29                                                           | _      | Inverting input of the op amp, see Note 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| OPA_OUT     | A7                                                                                  | 26                                                           | 0      | Output of the op amp, see Note 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| OPA_IP      | A6                                                                                  | 28                                                           | _      | Noninverting input of the op amp, see Note 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| REF_IN      | B1                                                                                  | 37                                                           | I      | LVCMOS reference clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

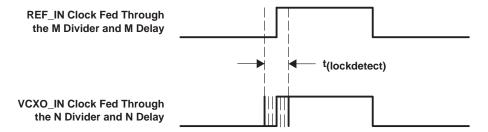

| STATUS_LOCK | A8                                                                                  | 25                                                           | 0      | This pin is high if the PLL lock definition is valid. PLL lock definition means the rising edge of REF_IN clock and VCXO_IN clock for PFD are inside the lock detect window for at least five successive input clock cycles. If the rising edge of REF_IN clock and VCXO_IN clock are out of the selected lock detect window, this pin will be low, but it does not refer to the real lock condition of the PLL. This means, that i.e. due to a strong jitter at REF_IN or VCXO_IN STATUS_LOCK can be low, even if the PLL is in Lock. The PLL is in lock for sure, if STATUS_LOCK is high.See Table 8 and Figure 4. |  |  |

| STATUS_REF  | C8                                                                                  | 23                                                           | 0      | LVCMOS output provides the status of the reference input (frequencies above 3.5 MHz are interpreted as valid clock, active high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| STATUS_VCXO | D8                                                                                  | 22                                                           | 0      | LVCMOS outputs provides the status of the VCXO input (frequencies above 10 MHz are interpreted as valid clock, active high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| VCC         | D7, E3, E4, E5, E6,<br>E7, E8, F7, G2, G3,<br>G4, G5, G6, G7                        | 2, 5, 6, 9, 10, 13,<br>15, 18, 19, 20,<br>21, 41, 44, 45, 48 | Power  | 3.3-V supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| VCXO_IN     | D1                                                                                  | 42                                                           | I      | VCXO LVPECL input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| VCXO_INB    | E1                                                                                  | 43                                                           | I      | Complementary VCXO LVPECL input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Y[0:4]      | F1, H2, H4, H6, G8                                                                  | 46, 3, 7, 11, 16                                             | 0      | LVPECL output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Y[0:4]B     | G1, H3, H5, H7, F8                                                                  | 47, 4, 8, 12, 17                                             | 0      | Complementary LVPECL output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

NOTE 1: If the internal operational amplifier is not used, these pins can be left open.

### SPI control interface

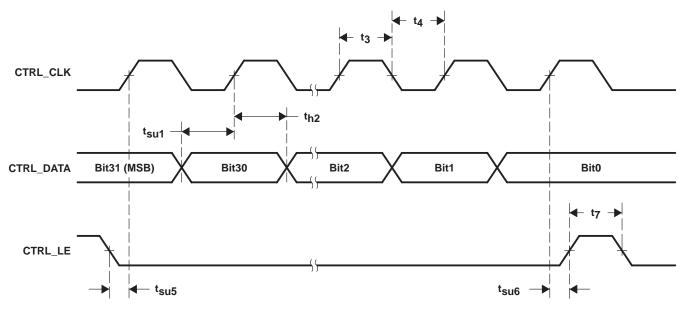

The serial interface of the CDC7005 is a simple SPI-compatible interface for writing to the registers of the device. It consists of three control lines: CTRL\_CLK, CTRL\_DATA, and CTRL\_LE. There are four 32-bit wide registers, which can be addressed by the two LSBs of a transferred word (bit 0 and bit 1). Every transmitted word must have 32 bits, starting with MSB first. Each word can be written separately. Word 0, word 1, and word 2 are user programmable; however, word 3 is reserved for factory test purposes only. There is no need to program word 3 unless it has to be filled with zeros. The transfer is initiated with the falling edge of CTRL\_LE; as long as CTRL\_LE is high, no data can be transferred. During CTRL\_LE, low data can be written. The data has to be applied at CTRL\_DATA and has to be stable before the rising edge of CTRL\_CLK. The transmission is finished by a rising edge of CTRL\_LE. With the rising edge of CTRL\_LE, the new word is asynchronously transferred to the internal register (e.g., N, M, P, ...). Each word has to be separately transmitted by this procedure.

Figure 1. Timing Diagram SPI Control Interface

# 3.3-V HIGH PERFORMANCE CLOCK SYNTHESIZER AND JITTER CLEANER SCAS685H - DECEMBER 2002 - REVISED FEBRUARY 2006

### Table 1. Word 0

| ВІТ | BIT NAME |                     | DESCRIPTION / FUNCTION                    | TYPE | POWER-UP<br>CONDITION | PIN<br>AFFECTED |

|-----|----------|---------------------|-------------------------------------------|------|-----------------------|-----------------|

| 0   | C0       |                     | Register selection                        | W    | 0                     |                 |

| 1   | C1       |                     | Register selection                        | W    | 0                     |                 |

| 2   | M0       |                     | Reference divider M bit 0                 | W    | 1                     |                 |

| 3   | M1       |                     | Reference divider M bit 1                 | W    | 1                     |                 |

| 4   | M2       |                     | Reference divider M bit 2                 | W    | 1                     |                 |

| 5   | M3       |                     | Reference divider M bit 3                 | W    | 1                     |                 |

| 6   | M4       | 5 ( 5 ) 1           | Reference divider M bit 4                 | W    | 1                     |                 |

| 7   | M5       | Reference Divider M | Reference divider M bit 5                 | W    | 1                     |                 |

| 8   | M6       |                     | Reference divider M bit 6                 | W    | 1                     |                 |

| 9   | M7       |                     | Reference divider M bit 7                 | W    | 0                     |                 |

| 10  | M8       |                     | Reference divider M bit 8                 | W    | 0                     |                 |

| 11  | M9       |                     | Reference divider M bit 9                 | W    | 0                     |                 |

| 12  | MD0      |                     | Reference delay M bit 0                   | W    | 0                     |                 |

| 13  | MD1      | Reference Delay M   | Reference delay M bit 1                   | W    | 0                     |                 |

| 14  | MD2      |                     | Reference delay M bit 2                   | W    | 0                     |                 |

| 15  | PFD0     |                     | PFD pulse width PFD bit 0                 | W    | 0                     | A4              |

| 16  | PFD1     | PFD Pulse Width     | PFD pulse width PFD bit 1                 | W    | 0                     | A4              |

| 17  | PFD2     |                     | PFD pulse width PFD bit 2                 | W    | 0                     | A4              |

| 18  | CP0      |                     | CP current setting bit 0                  | W    | 1                     | A4              |

| 19  | CP1      | CD Command          | CP current setting bit 1                  | W    | 0                     | A4              |

| 20  | CP2      | CP Current          | CP current setting bit 2                  | W    | 0                     | A4              |

| 21  | CP3      |                     | CP current setting bit 3                  | W    | 1                     | A4              |

| 22  | Y03St    |                     | Y0 3-state (1 = output enabled)           | W    | 1                     | F1, G1          |

| 23  | Y13St    |                     | Y1 3-state (1 = output enabled)           | W    | 1                     | H2, H3          |

| 24  | Y23St    |                     | Y2 3-state (1 = output enabled)           | W    | 1                     | H4, H5          |

| 25  | Y33St    | Output 3-State      | Y3 3-state (1 = output enabled)           | W    | 1                     | H6, H7          |

| 26  | Y43St    | Output 3-State      | Y4 3-state (1 = output enabled)           | W    | 1                     | G8, F8          |

| 27  | CP3St    |                     | CP 3-state (1 = output enabled)           | W    | 1                     | A4              |

| 28  | OP3St    |                     | OPA 3-state and disable (1 = OPA enabled) | W    | 0                     | A7              |

| 29  | MUXS0    |                     | MUXSEL select bit 0                       | W    | 1                     |                 |

| 30  | MUXS1    | MUXSEL              | MUXSEL select bit 1                       | W    | 1                     |                 |

| 31  | MUXS2    |                     | MUXSEL select bit 2                       | W    | 0                     |                 |

## 3.3-V HIGH PERFORMANCE CLOCK SYNTHESIZER AND JITTER CLEANER SCAS685H - DECEMBER 2002 - REVISED FEBRUARY 2006

### Table 2. Word 1

| BIT | BIT<br>NAME |           | DESCRIPTION / FUNCTION                                                                                              | TYPE | POWER-UP<br>CONDITION | PIN<br>AFFECTED |

|-----|-------------|-----------|---------------------------------------------------------------------------------------------------------------------|------|-----------------------|-----------------|

| 0   | C0          |           | Register selection                                                                                                  | W    | 1                     |                 |

| 1   | C1          |           | Register selection                                                                                                  | W    | 0                     |                 |

| 2   | N0          |           | VCXO divider N bit 0                                                                                                | W    | 1                     |                 |

| 3   | N1          |           | VCXO divider N bit 1                                                                                                | W    | 1                     |                 |

| 4   | N2          |           | VCXO divider N bit 2                                                                                                | W    | 1                     |                 |

| 5   | N3          |           | VCXO divider N bit 3                                                                                                | W    | 1                     |                 |

| 6   | N4          | VCXO      | VCXO divider N bit 4                                                                                                | W    | 1                     |                 |

| 7   | N5          | Divider N | VCXO divider N bit 5                                                                                                | W    | 1                     |                 |

| 8   | N6          |           | VCXO divider N bit 6                                                                                                | W    | 1                     |                 |

| 9   | N7          |           | VCXO divider N bit 7                                                                                                | W    | 0                     |                 |

| 10  | N8          |           | VCXO divider N bit 8                                                                                                | W    | 0                     |                 |

| 11  | N9          |           | VCXO divider N bit 9                                                                                                | W    | 0                     |                 |

| 12  | ND0         |           | VCXO delay N bit 0                                                                                                  | W    | 0                     |                 |

| 13  | ND1         | VCXO      | VCXO delay N bit 1                                                                                                  | W    | 0                     |                 |

| 14  | ND2         | Delay N   | VCXO delay N bit 2                                                                                                  | W    | 0                     |                 |

| 15  | MUX00       |           | MUX0 select bit 0                                                                                                   | W    | 0                     | F1, G1          |

| 16  | MUX01       | MUX0      | MUX0 select bit 1                                                                                                   | W    | 0                     | F1, G1          |

| 17  | MUX02       |           | MUX0 select bit 2                                                                                                   | W    | 0                     | F1, G1          |

| 18  | MUX10       |           | MUX1 select bit 0                                                                                                   | W    | 1                     | H2, H3          |

| 19  | MUX11       | MUX1      | MUX1 select bit 1                                                                                                   | W    | 0                     | H2, H3          |

| 20  | MUX12       |           | MUX1 select bit 2                                                                                                   | W    | 0                     | H2, H3          |

| 21  | MUX20       |           | MUX2 select bit 0                                                                                                   | W    | 0                     | H4, H5          |

| 22  | MUX21       | MUX2      | MUX2 select bit 1                                                                                                   | W    | 1                     | H4, H5          |

| 23  | MUX22       |           | MUX2 select bit 2                                                                                                   | W    | 0                     | H4, H5          |

| 24  | MUX30       |           | MUX3 select bit 0                                                                                                   | W    | 1                     | H6, H7          |

| 25  | MUX31       | MUX3      | MUX3 select bit 1                                                                                                   | W    | 1                     | H6, H7          |

| 26  | MUX32       |           | MUX3 select bit 2                                                                                                   | W    | 0                     | H6, H7          |

| 27  | MUX40       |           | MUX4 select bit 0                                                                                                   | W    | 1                     | G8, F8          |

| 28  | MUX41       | MUX4      | MUX4 select bit 1                                                                                                   | W    | 1                     | G8, F8          |

| 29  | MUX42       |           | MUX4 select bit 2                                                                                                   | W    | 0                     | G8, F8          |

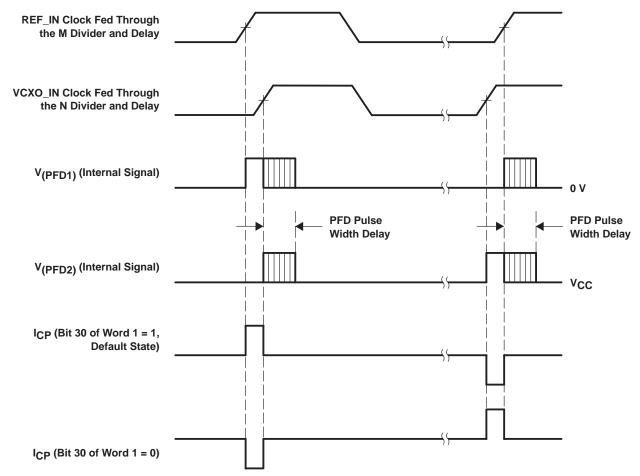

| 30  | CP_DIR      |           | Determines in which direction CP should regulate, if REF_CLK is faster than VCXO_CLK, and vice versa (see Figure 2) | W    | 1                     | A4              |

| 31  | REXT        |           | Enable external reference resistor (1 = enabled)                                                                    | W    | 0                     | C1              |

# 3.3-V HIGH PERFORMANCE CLOCK SYNTHESIZER AND JITTER CLEANER SCAS685H - DECEMBER 2002 - REVISED FEBRUARY 2006

### Table 3. Word 2

| ВІТ | BIT NAME | DESCRIPTION / FUNCTION                                                        | TYPE | POWER-UP<br>CONDITION | PIN<br>AFFECTED |

|-----|----------|-------------------------------------------------------------------------------|------|-----------------------|-----------------|

| 0   | C0       | Register selection                                                            | W    | 0                     |                 |

| 1   | C1       | Register selection                                                            |      | 1                     |                 |

| 2   | HOLD     | Enables the hold functionality (1 = enabled)                                  | W    | 0                     | A4              |

| 3   | NPD      | PD current sources, resets the dividers and 3-states all outputs (0 = active) | W    | 1                     |                 |

| 4   | NRESET   | RESET all dividers (0 = active)                                               | W    | 1                     |                 |

| 5   | ENBG     | Enable bandgap (1 = enabled), see Note 2                                      | W    | 1                     | C1              |

| 6   | LOCKW 0  | Lock detect window bit 0                                                      | W    | 0                     | A8              |

| 7   | LOCKW 1  | Lock detect window bit 1                                                      | W    | 0                     | A8              |

| 8   | RES      | Reserved                                                                      | W    | X                     |                 |

| 9   | RES      | Reserved                                                                      | W    | X                     |                 |

| 10  | RES      | Reserved                                                                      | W    | X                     |                 |

| 11  | RES      | Reserved                                                                      | W    | Х                     |                 |

| 12  | RES      | Reserved                                                                      | W    | X                     |                 |

| 13  | RES      | Reserved                                                                      | W    | X                     |                 |

| 14  | RES      | Reserved                                                                      | W    | X                     |                 |

| 15  | RES      | Reserved                                                                      | W    | Х                     |                 |

| 16  | RES      | Reserved                                                                      | W    | X                     |                 |

| 17  | RES      | Reserved                                                                      | W    | X                     |                 |

| 18  | RES      | Reserved                                                                      | W    | X                     |                 |

| 19  | RES      | Reserved                                                                      | W    | X                     |                 |

| 20  | RES      | Reserved                                                                      | W    | X                     |                 |

| 21  | RES      | Reserved                                                                      | W    | X                     |                 |

| 22  | RES      | Reserved                                                                      | W    | Х                     |                 |

| 23  | RES      | Reserved                                                                      | W    | Х                     |                 |

| 24  | RES      | Reserved                                                                      | W    | Х                     |                 |

| 25  | RES      | Reserved                                                                      | W    | Х                     |                 |

| 26  | RES      | Reserved                                                                      | W    | Х                     |                 |

| 27  | RES      | Reserved                                                                      | W    | X                     |                 |

| 28  | RES      | Reserved                                                                      | W    | Х                     |                 |

| 29  | RES      | Reserved                                                                      | W    | Х                     |                 |

| 30  | RES      | Reserved                                                                      | W    | Х                     |                 |

| 31  | RES      | Reserved                                                                      | W    | Х                     |                 |

NOTE 2: The reference voltage for the charge pump and LVPECL output circuitry can be generated in two ways. One way is to enable ENBG and the other way is to use the voltage divider circuitry (internal or external). It is recommended to enable ENBG because it gives an accurate value and it is independent on temperature variation.

# 3.3-V HIGH PERFORMANCE CLOCK SYNTHESIZER AND JITTER CLEANER SCAS685H - DECEMBER 2002 - REVISED FEBRUARY 2006

### Table 4. Word 3

| ВІТ | BIT NAME | DESCRIPTION / FUNCTION | TYPE | POWER-UP<br>CONDITION | PIN<br>AFFECTED |

|-----|----------|------------------------|------|-----------------------|-----------------|

| 0   | C0       | Register selection     | W    | 1                     |                 |

| 1   | C1       | Register selection     | W    | 1                     |                 |

| 2   | RES      | Reserved               | W    | 0                     |                 |

| 3   | RES      | Reserved               | W    | 0                     |                 |

| 4   | RES      | Reserved               | W    | 0                     |                 |

| 5   | RES      | Reserved               | W    | 0                     |                 |

| 6   | RES      | Reserved               | W    | 0                     |                 |

| 7   | RES      | Reserved               | W    | 0                     |                 |

| 8   | RES      | Reserved               | W    | 0                     |                 |

| 9   | RES      | Reserved               | W    | 0                     |                 |

| 10  | RES      | Reserved               | W    | 0                     |                 |

| 11  | RES      | Reserved               | W    | 0                     |                 |

| 12  | RES      | Reserved               | W    | 0                     |                 |

| 13  | RES      | Reserved               | W    | 0                     |                 |

| 14  | RES      | Reserved               | W    | 0                     |                 |

| 15  | RES      | Reserved               | W    | 0                     |                 |

| 16  | RES      | Reserved               | W    | 0                     |                 |

| 17  | RES      | Reserved               | W    | 0                     |                 |

| 18  | RES      | Reserved               | W    | 0                     |                 |

| 19  | RES      | Reserved               | W    | 0                     |                 |

| 20  | RES      | Reserved               | W    | 0                     |                 |

| 21  | RES      | Reserved               | W    | 0                     |                 |

| 22  | RES      | Reserved               | W    | 0                     |                 |

| 23  | RES      | Reserved               | W    | 0                     |                 |

| 24  | RES      | Reserved               | W    | 0                     |                 |

| 25  | RES      | Reserved               | W    | 0                     |                 |

| 26  | RES      | Reserved               | W    | 0                     |                 |

| 27  | RES      | Reserved               | W    | 0                     |                 |

| 28  | RES      | Reserved               | W    | 0                     |                 |

| 29  | RES      | Reserved               | W    | 0                     |                 |

| 30  | RES      | Reserved               | W    | 0                     |                 |

| 31  | RES      | Reserved               | W    | 0                     |                 |

### SCAS685H - DECEMBER 2002 - REVISED FEBRUARY 2006

### functional description of the logic

Table 5. Reference Divider M and VCXO Divider N (See Note 3)

| M9 | M8 | M7 | M6 | M5 | M4  | М3 | M2 | M1 | МО | DIV BY | DEFAULT |

|----|----|----|----|----|-----|----|----|----|----|--------|---------|

| 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  | 0  | 1      |         |

| 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  | 1  | 2      |         |

| 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 1  | 0  | 3      |         |

| 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 1  | 1  | 4      |         |

|    |    |    |    |    | • • |    |    |    |    |        |         |

| 0  | 0  | 0  | 1  | 1  | 1   | 1  | 1  | 1  | 1  | 128    | Yes     |

|    |    |    |    |    | •   |    |    |    |    |        |         |

| 1  | 1  | 1  | 1  | 1  | 1   | 1  | 1  | 0  | 1  | 1022   |         |

| 1  | 1  | 1  | 1  | 1  | 1   | 1  | 1  | 1  | 0  | 1023   |         |

| 1  | 1  | 1  | 1  | 1  | 1   | 1  | 1  | 1  | 1  | 1024   |         |

NOTE 3: If the divider value is Q, then the code will be the binary value of (Q-1).

Table 6. Reference Delay M and VCXO Delay N

| MD2/ND2 | MD1/ND1 | MD0/ND0 | DELAY <sup>†</sup> | DEFAULT |

|---------|---------|---------|--------------------|---------|

| 0       | 0       | 0       | 0 ps               | Yes     |

| 0       | 0       | 1       | 150 ps             |         |

| 0       | 1       | 0       | 300 ps             |         |

| 0       | 1       | 1       | 450 ps             |         |

| 1       | 0       | 0       | 600 ps             |         |

| 1       | 0       | 1       | 750 ps             |         |

| 1       | 1       | 0       | 1.5 ns             |         |

| 1       | 1       | 1       | 2.75 ns            |         |

<sup>†</sup> Typical values at V<sub>CC</sub> = 3.3 V, temperature = 25°C

**Table 7. PFD Pulse Width Delay**

| PFD2 | PFD1 | PFD0 | ADDITIONAL PULSE WIDTH <sup>†</sup> | DEFAULT |

|------|------|------|-------------------------------------|---------|

| 0    | 0    | 0    | 0 ps                                | Yes     |

| 0    | 0    | 1    | 300 ps                              |         |

| 0    | 1    | 0    | 600 ps                              |         |

| 0    | 1    | 1    | 900 ps                              |         |

| 1    | 0    | 0    | 1.5 ns                              |         |

| 1    | 0    | 1    | 2.1 ns                              |         |

| 1    | 1    | 0    | 2.7 ns                              |         |

| 1    | 1    | 1    | 3.7 ns                              |         |

<sup>†</sup> Typical values at V<sub>CC</sub> = 3.3 V, temperature = 25°C

## 3.3-V HIGH PERFORMANCE CLOCK SYNTHESIZER AND JITTER CLEANER SCAS685H - DECEMBER 2002 - REVISED FEBRUARY 2006

### functional description of the logic (continued)

### **Table 8. Lock Detect Window**

| LockW 1 | LockW 0 | REF_IN TO Yn TOLERABLE PHASE OFFSET (See Figure 4 and Note 1) | DEFAULT |

|---------|---------|---------------------------------------------------------------|---------|

| 0       | 0       | ±1.2 ns                                                       | Yes     |

| 0       | 1       | ±1.8 ns                                                       |         |

| 1       | 0       | ±2.4 ns                                                       |         |

| 1       | 1       | ±3 ns                                                         |         |

NOTE 1: Determined at PFD – REF\_IN and Yn feed through M/N Divider and M/N Delay.

### **Table 9. Charge Pump Current**

| CP3 | CP2 | CP1 | CP0 | NOMINAL CHARGE PUMP CURRENT | DEFAULT |

|-----|-----|-----|-----|-----------------------------|---------|

| 0   | 0   | 0   | 0   | 0.625 mA                    |         |

| 0   | 0   | 0   | 1   | 1.25 mA                     |         |

| 0   | 0   | 1   | 0   | 1.875 mA                    |         |

| 0   | 0   | 1   | 1   | 2.5 mA                      |         |

| 0   | 1   | 0   | 0   | 3.125 mA                    |         |

| 0   | 1   | 0   | 1   | 3.75 mA                     |         |

| 0   | 1   | 1   | 0   | 4.375 mA                    |         |

| 0   | 1   | 1   | 1   | 5 mA                        |         |

| 1   | 0   | 0   | 0   | 1 mA                        |         |

| 1   | 0   | 0   | 1   | 2 mA                        | Yes     |

| 1   | 0   | 1   | 0   | 3 mA                        |         |

| 1   | 0   | 1   | 1   | 4 mA                        |         |

| 1   | 1   | 0   | 0   | 5 mA                        |         |

| 1   | 1   | 0   | 1   | 6 mA                        |         |

| 1   | 1   | 1   | 0   | 7 mA                        |         |

| 1   | 1   | 1   | 1   | 8 mA                        |         |

$<sup>\</sup>uparrow$  With an internal or external reference resistor (12 k $\Omega$ ) in use.

### **Table 10. MUXSEL Selection**

| MUXS2 | MUXS1 | MUXS0 | SELECTED VCXO SIGNAL FOR THE PHASE DISCRIMINATOR | DEFAULT |

|-------|-------|-------|--------------------------------------------------|---------|

| 0     | 0     | 0     | Y0                                               |         |

| 0     | 0     | 1     | Y1                                               |         |

| 0     | 1     | 0     | Y2                                               |         |

| 0     | 1     | 1     | Y3                                               | Yes     |

| 1     | 0     | 0     | Y4                                               |         |

| 1     | 0     | 1     | Y3                                               |         |

| 1     | 1     | 0     | Y3                                               |         |

| 1     | 1     | 1     | Y3                                               |         |

### functional description of the logic (continued)

Table 11. MUX0, MUX1, MUX2, MUX3, and MUX4 Selection

| MUX2 | MUX1 | MUX0 | SELECTED DIVIDED VCXO SIGNAL | DEFAULT       |

|------|------|------|------------------------------|---------------|

| 0    | 0    | 0    | Div by 1                     | For Y0        |

| 0    | 0    | 1    | Div by 2                     | For Y1        |

| 0    | 1    | 0    | Div by 4                     | For Y2        |

| 0    | 1    | 1    | Div by 8                     | For Y3 and Y4 |

| 1    | 0    | 0    | Div by 16                    |               |

| 1    | 0    | 1    | Div by 8                     |               |

| 1    | 1    | 0    | Div by 8                     |               |

| 1    | 1    | 1    | Div by 8                     |               |

NOTE: The purpose of the PFD pulse width delay is to improve spurious suppression. (See Table 7)

**Figure 2. Charge Pump Current Direction**

### functional description of the logic (continued)

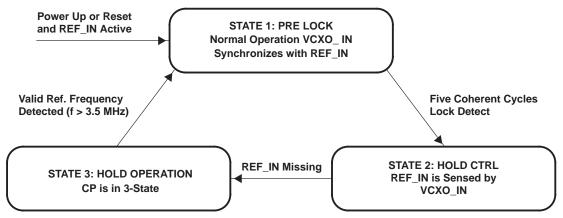

NOTES: A. For a proper hold functionality the following conditions must be maintained:

- Counter M and counter N need to have the same divider ratio

- fref\_in max = 75 MHz

- Duty cycle of 45% to 55% for 25 MHz <= fref\_in < 50 MHz

- Duty cycle of 40% to 60% for 50 MHz <= fref\_in < 75 MHz

- Duty cycle of fVCXO should be in 50% range

The hold functionality is triggered by the first missing REF\_IN cycle. It is disabled in default mode (bit 2 of word 2 = 0). While the device is in frequency hold mode, a possible leakage current caused by the external filter and VCXO may change the VCXO control voltage, and therefore changing the VCXO frequency. To keep the frequency drift as low as possible, a low leakage current filter design is recommended or the number of the disrupted / missing REF\_IN clock cycles should be kept low (< 100).

Figure 3. State Machine Operation

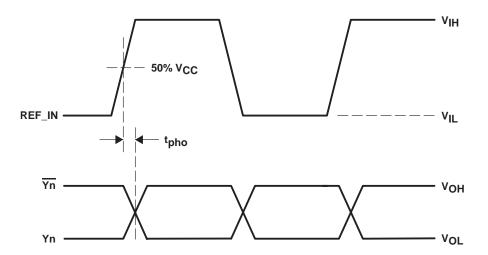

NOTE: If the rising edge of REF\_IN clock and VCXO\_IN clock for PFD are inside the lock detect window (t(lockdetect)) for at least five successive input clock periods, then the PLL is considered to be locked. In this case, the STATUS\_LOCK output is set to high level. The size of the lock detect window is programmable via the SPI control logic (bit 6 and 7 of word 2). (See Table 8)

**Figure 4. Lock Detect Window**

### absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> , AV <sub>CC</sub>                  | 0.5 V to 4.6 V                             |

|---------------------------------------------------------------------------|--------------------------------------------|

| Input voltage range, V <sub>I</sub> (see Note 2)                          | $-0.5 \text{ V to V}_{CC} + 0.5 \text{ V}$ |

| Output voltage range, V <sub>O</sub> (see Note 2)                         | $-0.5 \text{ V to V}_{CC} + 0.5 \text{ V}$ |

| Input current $(V_1 < 0, V_1 > V_{CC})$                                   | ±20 mA                                     |

| Output current for LVPECL outputs (0 < V <sub>O</sub> < V <sub>CC</sub> ) | –50 mA                                     |

| Continuous output current, I <sub>O</sub>                                 | ±50 mA                                     |

| Storage temperature range T <sub>stq</sub>                                | 65°C to 150°C                              |

| Maximum junction temperature, T <sub>J</sub>                              | 125°C                                      |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### package thermal resistance for RGZ (QFN) package (see Note 3 and Note 4)

| AIRFLOW (LFM) | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) | θ <sub>JP</sub> (°C/W) | Ψ <sub>JT</sub> (°C/W) |

|---------------|------------------------|------------------------|------------------------|------------------------|

| 0             | 29.9                   | 22.4                   | 1.5                    | 0.2                    |

| 15            | 24.7                   |                        |                        | 0.2                    |

| 250           | 23.2                   |                        |                        | 0.2                    |

| 500           | 21.5                   |                        |                        | 0.3                    |

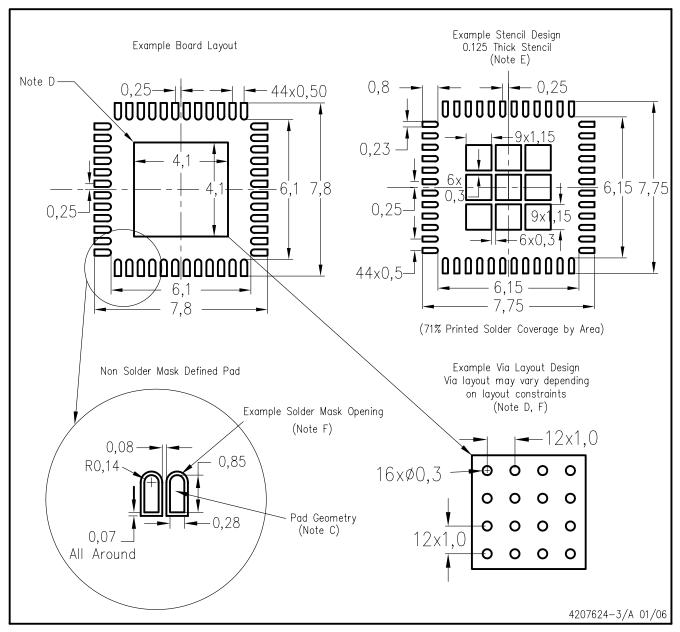

NOTE 3: The package thermal impedance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

### package thermal resistance for ZVA (BGA) package (see Note 5)

| AIRFLOW (m/s) | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) | θ <sub>JB</sub> (°C/W) | ΨJT (°C/W) |

|---------------|------------------------|------------------------|------------------------|------------|

| 0             | 54                     | 29.9                   | 44.5                   | 0.9        |

| 1             | 49                     |                        |                        | 0.9        |

| 2.5           | 47.2                   |                        |                        | 0.9        |

NOTE 5: The package thermal impedance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

### recommended operating conditions

|                                                                    | MIN                 | NOM                 | MAX                  | UNIT |

|--------------------------------------------------------------------|---------------------|---------------------|----------------------|------|

| Supply voltage, V <sub>CC</sub>                                    | 3                   | 3.3                 | 3.6                  | V    |

| Operating free-air temperature, T <sub>A</sub>                     | -40                 |                     | 85                   | °C   |

| Low-level input voltage LVCMOS, V <sub>IL</sub>                    |                     |                     | 0.3 V <sub>C</sub> C | V    |

| High-level input voltage LVCMOS, VIH                               | 0.7 V <sub>CC</sub> |                     |                      | V    |

| Input threshold voltage LVCMOS, V <sub>IT</sub>                    |                     | 0.5 V <sub>CC</sub> |                      | V    |

| High-level output current LVCMOS, IOH                              |                     |                     | -6                   | mA   |

| Low-level output current LVCMOS, IOL                               |                     |                     | 6                    | mA   |

| Input voltage range LVCMOS, VI                                     | 0                   |                     | 3.6                  | V    |

| Input amplitude LVPECL, VINPP [(VVCXO_IN - VVCXO_INB), See Note 6] | 0.5                 |                     | 1.3                  | V    |

| Common-mode input voltage LVPECL, V <sub>IC</sub>                  | V <sub>CC</sub> -2  |                     | V <sub>CC</sub> -0.4 | V    |

NOTE 6: V<sub>INPP</sub> minimum and maximum is required to maintain ac specifications; the actual device function tolerates at a minimum V<sub>INPP</sub> of 100 mV.

NOTES: 2. The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

NOTE 4: Connected to GND with nine thermal vias (0,3 mm diameter).

## 3.3-V HIGH PERFORMANCE CLOCK SYNTHESIZER AND JITTER CLEANER SCAS685H - DECEMBER 2002 - REVISED FEBRUARY 2006

### timing requirements over recommended ranges of supply voltage, load, and operating free-air temperature

|                                 | PARAMETER                                                                                           | MIN | TYP MAX | UNIT |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------|-----|---------|------|--|--|--|

| REF_IN Requ                     | irements                                                                                            |     |         |      |  |  |  |

| fREF_IN                         | LVCMOS reference clock frequency                                                                    | 3.5 | 180     | MHz  |  |  |  |

| t <sub>r</sub> / t <sub>f</sub> | Rise and fall time of REF_IN signal from 20% to 80% of V <sub>CC</sub>                              |     | 4       | ns   |  |  |  |

| dutyREF                         | Duty cycle of REF_IN at V <sub>CC</sub> / 2                                                         | 40% | 60%     |      |  |  |  |

| VCXO_IN, VC                     | XO_INB Requirements                                                                                 |     |         |      |  |  |  |

| fVCXO_IN                        | LVPECL VCXO clock frequency                                                                         | 10  | 800     | MHz  |  |  |  |

| t <sub>r</sub> / t <sub>f</sub> | Rise and fall time 20% to 80% of V <sub>INPP</sub> at 80 MHz to 800 MHz (see Note 7)                |     | 3       | ns   |  |  |  |

| duty <sub>VCXO</sub>            | Duty cycle of VCXO clock                                                                            | 40% | 60%     |      |  |  |  |

| SPI/Control R                   | Requirements (See Figure 1)                                                                         |     |         |      |  |  |  |

| fCTRL_CLK                       | CTRL_CLK frequency                                                                                  |     | 20      | MHz  |  |  |  |

| t <sub>su1</sub>                | CTRL_DATA to CTRL_CLK setup time                                                                    | 10  |         | ns   |  |  |  |

| t <sub>h2</sub>                 | CTRL_DATA to CTRL_CLK hold time                                                                     | 10  |         | ns   |  |  |  |

| t <sub>3</sub>                  | CTRL_CLK high duration                                                                              | 25  |         | ns   |  |  |  |

| t <sub>4</sub>                  | CTRL_CLK low duration                                                                               | 25  |         | ns   |  |  |  |

| t <sub>su5</sub>                | CTRL_LE to CTRL_CLK setup time                                                                      | 10  |         | ns   |  |  |  |

| t <sub>su6</sub>                | CTRL_CLK to CTRL_LE setup time                                                                      | 10  |         | ns   |  |  |  |

| t <sub>7</sub>                  | CTRL_LE pulse width                                                                                 | 20  |         | ns   |  |  |  |

| t <sub>r</sub> / t <sub>f</sub> | Rise and fall time of CTRL_DATA CTRL_CLK, CTRL_LE from 20% to 80% of V $_{\hbox{\footnotesize CC}}$ |     | 5       | ns   |  |  |  |

| NPD / NRESE                     | NPD / NRESET Requirements                                                                           |     |         |      |  |  |  |

| t <sub>r</sub> / t <sub>f</sub> | Rise and fall time of the NRESET, NPD signal from 20% to 80% of $V_{\hbox{\footnotesize{CC}}}$      |     | 4       | ns   |  |  |  |

NOTES: 7. Use a square wave for lower frequencies (< 80 MHz).

### 3.3-V HIGH PERFORMANCE CLOCK SYNTHESIZER AND JITTER CLEANER

SCAS685H - DECEMBER 2002 - REVISED FEBRUARY 2006

### device characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                                           | TEST CONDITIONS                                                                                                                                                                                      | MIN                   | TYP† | MAX                   | UNIT |

|-------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| Overall                 |                                                     |                                                                                                                                                                                                      | •                     |      |                       |      |

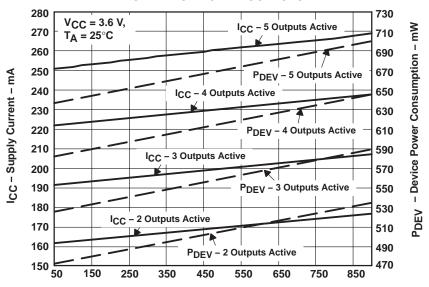

| ICC                     | Supply current (see Note 8)                         | f <sub>VCXO</sub> = 245 MHz, f <sub>REF_IN</sub> = 30 MHz,<br>V <sub>CC</sub> = 3.6 V, AV <sub>CC</sub> = 3.6 V,<br>f <sub>PFD</sub> = 240 kHz, I <sub>CP</sub> = 2 mA,<br>(see Note 10 and Note 12) |                       | 230  | 265                   | mA   |

| ICCPD                   | Power-down current                                  | f <sub>IN</sub> = 0 MHz, V <sub>CC</sub> = 3.6 V,<br>AV <sub>CC</sub> = 3.6 V, V <sub>I</sub> = 0 V or V <sub>CC</sub>                                                                               |                       | 100  | 300                   | μΑ   |

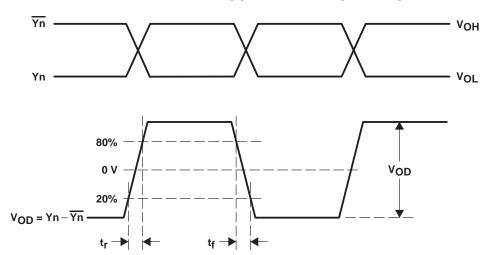

| t <sub>pho</sub>        | Phase offset (REF_IN to Y output) (see Note 9)      | VREF_IN = VCC/2,<br>Crossing point of Y, See Figure 12                                                                                                                                               | -150                  |      | 150                   | ps   |

| LVCMOS                  |                                                     |                                                                                                                                                                                                      | •                     |      |                       |      |

| VIK                     | LVCMOS input voltage                                | $V_{CC} = 3 \text{ V, I}_{I} = -18 \text{ mA}$                                                                                                                                                       |                       |      | -1.2                  | V    |

| lı                      | LVCMOS input current                                | V <sub>I</sub> = 0 V or V <sub>CC</sub> , V <sub>CC</sub> = 3.6 V                                                                                                                                    |                       |      | ±5                    | μΑ   |

| liH                     | LVCMOS input current for NPD, NRESET                | V <sub>I</sub> = V <sub>CC</sub> , V <sub>CC</sub> = 3.6 V                                                                                                                                           |                       |      | 5                     | μΑ   |

| I <sub>IL</sub>         | LVCMOS input current for NPD, NRESET                | V <sub>I</sub> = 0 V, V <sub>CC</sub> = 3.6 V                                                                                                                                                        | -15                   |      | -35                   | μΑ   |

| Vон                     | LVCMOS high-level output voltage                    | I <sub>OH</sub> = -12 mA, V <sub>CC</sub> = 3 V                                                                                                                                                      | 2.1                   |      |                       | V    |

| VOL                     | LVCMOS low-level output voltage                     | I <sub>OL</sub> = 12 mA, V <sub>CC</sub> = 3 V                                                                                                                                                       |                       |      | 0.55                  | V    |

| Cl                      | Input capacitance at REF_IN                         | VI = 0 V or VCC                                                                                                                                                                                      |                       | 2    |                       | pF   |

| Cl                      | Input capacitance at CTRL_LE, CTRL_CLOCK, CTRL_DATA | VI = 0 V or VCC                                                                                                                                                                                      |                       | 2    |                       | pF   |

| <sup>t</sup> detectREF  | Frequency detect time until STATUS_REF is valid     | fREF_IN = 3.5 MHz                                                                                                                                                                                    |                       | 5    |                       | μs   |

| <sup>t</sup> detectVCXO | Frequency detect time until STATUS_VCXO is valid    | f <sub>VCXO_IN</sub> = 10 MHz                                                                                                                                                                        |                       | 5    |                       | μs   |

| LVPECL                  |                                                     |                                                                                                                                                                                                      |                       |      |                       |      |

| lį                      | LVPECL input current                                | $V_I = 0 \text{ V or } V_{CC}$                                                                                                                                                                       |                       |      | ±100                  | μΑ   |

| loz                     | LVPECL output current 3-state                       | $V_O = 0 \text{ V or } V_{CC} - 0.8 \text{ V}$                                                                                                                                                       |                       |      | 20                    | μΑ   |

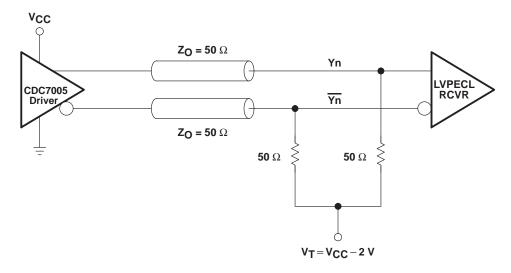

| VOH                     | LVPECL high-level output voltage                    | See Note 10                                                                                                                                                                                          | V <sub>CC</sub> -1.18 |      | V <sub>CC</sub> -0.81 | V    |

| VOL                     | LVPECL low-level output voltage                     | See Note 10                                                                                                                                                                                          | V <sub>CC</sub> -1.98 |      | V <sub>CC</sub> -1.55 | V    |

| VOD                     | Differential output voltage                         | 10 ≤ f <sub>OUT</sub> ≤ 800 MHz, See Figure 6                                                                                                                                                        | 500                   |      |                       | mV   |

$<sup>^{\</sup>dagger}$  All typical values are at VCC = 3.3 V, temperature = 25°C.

NOTES: 8. For ICC over frequency see Figure 5.

<sup>9.</sup> This is valid only for same REF\_IN clock and Y output clock frequency. It can be adjusted by the SPI controller (reference delay M and VCXO delay N).

<sup>10.</sup> Outputs are terminated through a 50- $\Omega$  resistor to V<sub>CC</sub> – 2 V.

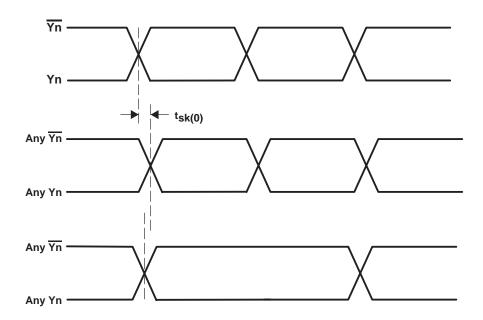

<sup>11.</sup> The  $t_{sk(0)}$  specification is only valid for equal loading of all outputs.

<sup>12.</sup> All output switching at default divider ratios.

### device characteristics over recommended operating free-air temperature range (unless otherwise noted)(continued)

|                                 | PARAMETER                             | TEST CONDITIONS                                                                | MIN    | TYP <sup>†</sup> | MAX                  | UNIT   |

|---------------------------------|---------------------------------------|--------------------------------------------------------------------------------|--------|------------------|----------------------|--------|

| tPLH/tPHL                       | Propagation delay rising/falling edge | VCXO_IN to Yn                                                                  | 500    |                  | 950                  | ps     |

| tsk(p)                          | LVPECL pulse skew                     |                                                                                |        |                  | 15                   | ps     |

| t-1./->                         | LVPECL output skew (see Note 13)      | See Figure 11, Mode 1-2-4-8-8                                                  |        |                  | 60                   | ps     |

| tsk(o)                          | EVI LOC dulput skew (see Note 13)     | See Figure 11, Mode 1-1-1-1                                                    |        |                  | 30                   | ps     |

| t <sub>r</sub> / t <sub>f</sub> | Rise and fall time                    | 20% to 80% of V <sub>OD</sub> , See Figure 10                                  | 180    |                  | 350                  | ps     |

| Cl                              | Input capacitance at VCXO_IN, VCXO_IB |                                                                                |        | 1.5              |                      | pF     |

| Phase Dete                      | ctor                                  |                                                                                |        |                  |                      |        |

| fCPmax                          | Maximum charge pump frequency         | PFD pulse width delay is 0 ps                                                  |        | 100              |                      | MHz    |

| Charge Pun                      | пр                                    |                                                                                |        |                  |                      | -      |

| ICP                             | Charge pump sink/source current range | V <sub>CP</sub> = 0.5 V <sub>CC</sub> , See Table 9                            | ±0.625 |                  | ±8                   | mA     |

| I <sub>CP3St</sub>              | Charge pump 3-state current           | 0.5 V < V <sub>CP</sub> < V <sub>CC</sub> - 0.5 V                              |        | 1                | 30                   | nA     |

| ICPA                            | I <sub>CP</sub> absolute accuracy     | V <sub>CP</sub> = 0.5 V <sub>CC</sub>                                          |        |                  | 20%                  |        |

| ICPM                            | Sink/source current matching          | V <sub>CP</sub> = 0.5 V <sub>CC</sub>                                          |        | 5%               |                      |        |

| IVCPM                           | ICP vs VCP matching                   | 0.5 V < V <sub>CP</sub> < V <sub>CC</sub> - 0.5 V                              |        | 10%              |                      |        |

| Operational                     | Amplifier                             |                                                                                |        |                  |                      |        |

| Is                              | Supply current                        | AV <sub>CC</sub> = 3.6 V                                                       |        | 2                | 5                    | mA     |

| V <sub>IO</sub>                 | Input offset voltage                  |                                                                                |        | 2                |                      | mV     |

| I <sub>IB</sub>                 | Input bias current                    | (  I <sub>OPA_IP</sub>   +   I <sub>OPA_IN</sub>  ) / 2                        |        | 1                | 30                   | nA     |

| IIO                             | Input offset current                  | IOPA_IP - IOPA_IN                                                              |        | 1                | 10                   | nA     |

| RI                              | Input resistance                      | 0.5 V <sub>CC</sub> ±500 mV                                                    | 10     |                  |                      | MΩ     |

| VICR                            | Common-mode input voltage range       |                                                                                | 0.2    |                  | V <sub>CC</sub> -0.2 | V      |

| AOL                             | Open-loop voltage gain                | See Figure 17, f = 1 kHz                                                       |        | 70               |                      | dB     |

| GBW                             | Gain bandwidth                        | See Figure 14                                                                  |        | 3                |                      | MHz    |

| SR                              | Slew rate                             | See Figure 14, 20% – 80% of VO                                                 |        | 1                |                      | V/µs   |

|                                 |                                       | R <sub>L</sub> = 10 kΩ                                                         | 0.2    |                  | V <sub>CC</sub> -0.2 |        |

| VO                              | Output voltage swing                  | $R_L = 2 k\Omega$                                                              | 0.3    |                  | V <sub>CC</sub> -0.3 | V      |

| RO                              | Output resistance                     |                                                                                |        | 60               |                      | Ω      |

|                                 |                                       | Sourcing                                                                       |        | -20              |                      |        |

| los                             | Short-circuit output current          | Sinking                                                                        |        | 50               |                      | mA     |

| CMRR                            | Common-mode rejection ratio           | V <sub>INPP</sub> = 500 mV and<br>f = 1 kHz, (see Figure 15)                   |        | 80               |                      | dB     |

| PSRR                            | Power supply rejection ratio          | AVCC modulated with sine wave from 3 V to 3.6 V and f = 100 Hz (see Figure 16) |        | 60               |                      | dB     |

| V <sub>n</sub>                  | Input noise voltage                   | f = 1 kHz, see Figure 14, V <sub>IN</sub> = 0 V                                |        | 500              |                      | nV/√Hz |

$<sup>^{\</sup>dagger}$  All typical values are at VCC = 3.3 V, temperature = 25°C.

NOTE 13: The  $t_{Sk(0)}$  specification is only valid for equal loading of all outputs.

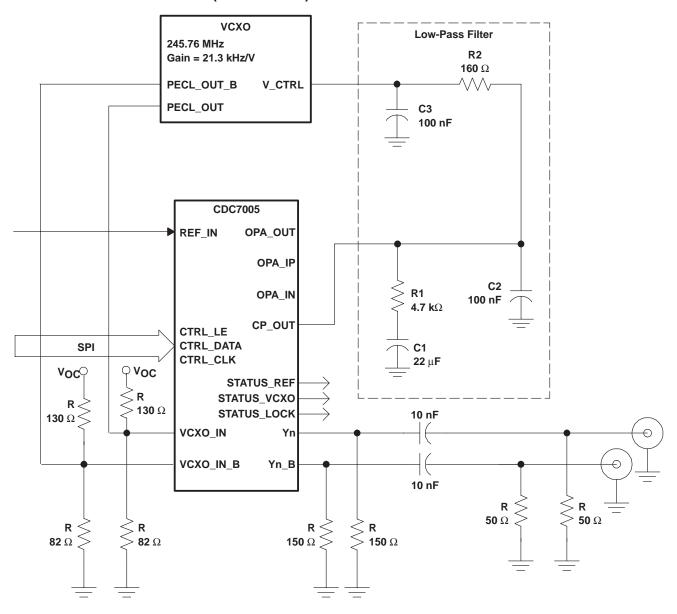

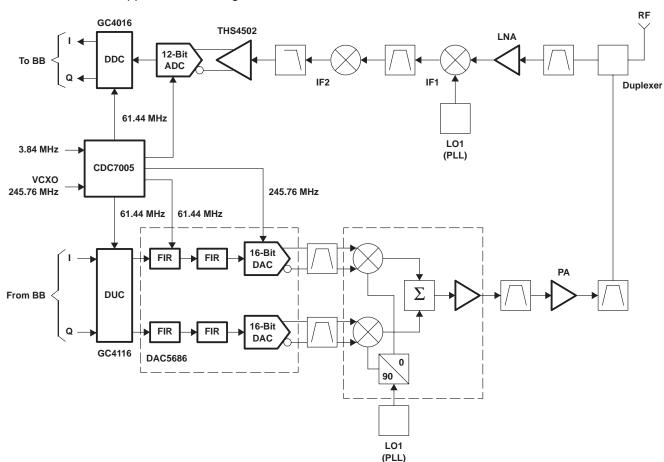

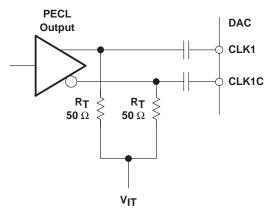

### SUPPLY CURRENT / DEVICE POWER CONSUMPTION

#### vs NUMBER OF ACTIVE OUTPUTS

NOTE A:  $P_{DEV} = P_{Tot} - P_{Term}$  $P_{DEV} = D_{evice}$  power consumption,  $P_{Tot} = T_{otal}$  power consumption,  $P_{Term} = T_{erm}$  Termination power consumption

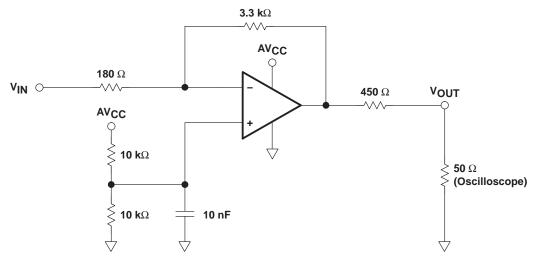

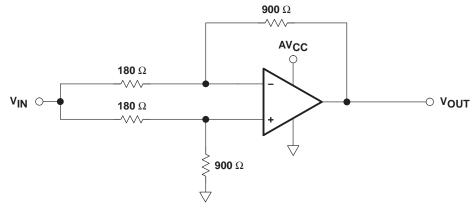

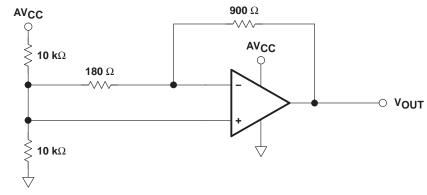

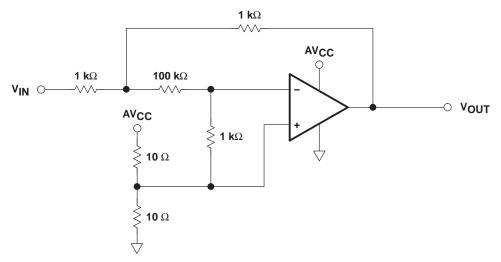

Figure 5. I<sub>CC</sub> / P<sub>DEV</sub> vs Frequency