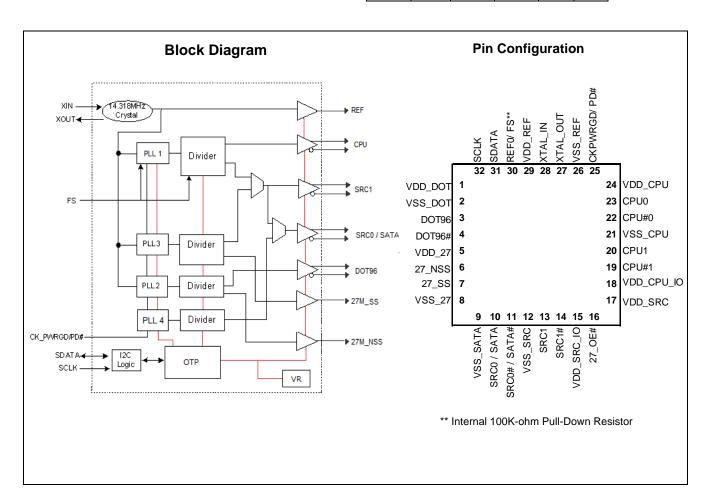

# EProClock® Generator for Intel Calpella Chipset

#### **Features**

- Intel CK505 Clock Revision 1.0 Compliant

- Hybrid Video Support Simultaneous DOT96, 27MHz\_SS and 27MHz\_NSS video clocks

- PCI-Express Gen 2 Compliant

- · Low power push-pull type differential output buffers

- · Integrated voltage regulator

- · Integrated resistors on differential clocks

- Scalable low voltage VDD\_IO (3.3V to 1.05V)

- Wireless friendly 3-bits slew rate control on single-ended clocks.

- Differential CPU clocks with selectable frequency

- 100MHz Differential SRC clocks

- 100MHz Differential SATA clocks

- 96MHz Differential DOT clock

- 27MHz Video clock

- Buffered Reference Clock 14.318MHz

- PC EProClock<sup>®</sup> Programmable Technology

- I<sup>2</sup>C support with readback capabilities

- Industrial Temperature -40°C to 85°C

- Triangular Spread Spectrum profile for maximum electromagnetic interference (EMI) reduction

- 3.3V Power supply

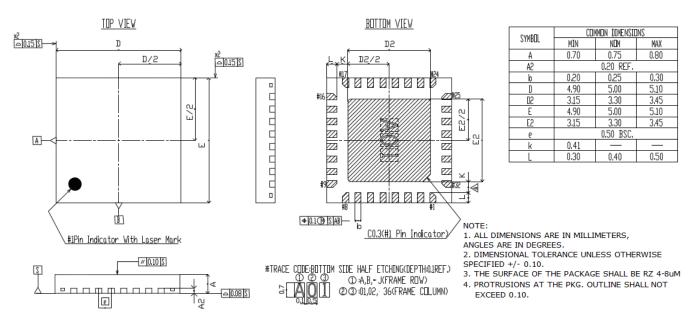

- 32-pin QFN package

| CPU | SRC | SATA | DOT96 | REF | 27M |

|-----|-----|------|-------|-----|-----|

| x2  | x1  | x 1  | x 1   | x1  | x2  |

# 32-QFN Pin Definitions

| 1  |               | Туре    | Description                                                                                                                                                                                                     |

|----|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | VDD_DOT       | PWR     | 3.3V Power supply for outputs and PLL                                                                                                                                                                           |

| 2  | VSS_DOT       | GND     | Ground for outputs                                                                                                                                                                                              |

| 3  | DOT96         | O, DIF  | Fixed true 96MHz clock output                                                                                                                                                                                   |

| 4  | DOT96#        | O, DIF  | Fixed complement 96MHz clock output                                                                                                                                                                             |

| 5  | VDD_27        | PWR     | 3.3V Power supply for 27MHz PLL                                                                                                                                                                                 |

| 6  | 27M_NSS       | O,SE    | Non-spread 27MHz video clock output                                                                                                                                                                             |

| 7  | 27M_SS        | O, SE   | Spread 27MHz video clock output                                                                                                                                                                                 |

| 8  | VSS_27        | GND     | Ground for 27MHz PLL                                                                                                                                                                                            |

| 9  | VSS_SATA      | GND     | Ground for outputs                                                                                                                                                                                              |

| 10 | SRC0 / SATA   | O, DIF  | 100MHz True differential serial reference clock                                                                                                                                                                 |

| 11 | SRC0# / SATA# | O, DIF  | 100MHz Complement differential serial reference clock                                                                                                                                                           |

| 12 | VSS_SRC       | GND     | Ground for PLL                                                                                                                                                                                                  |

| 13 | SRC1          | O, DIF  | 100MHz True differential serial reference clock                                                                                                                                                                 |

| 14 | SRC1#         | O, DIF  | 100MHz Complement differential serial reference clock                                                                                                                                                           |

| 15 | VDD_SRC_IO    | PWR     | Scalable 3.3V to 1.05V power supply for output buffer                                                                                                                                                           |

| 16 | 27_OE#        | I       | 3.3V tolerance input pin to enable and disable both 27_NSS and 27_SS                                                                                                                                            |

| 17 | VDD_SRC       | PWR     | 3.3V Power supply for PLL                                                                                                                                                                                       |

| 18 | VDD_CPU_IO    | PWR     | Scalable 3.3V to 1.05V power supply for output buffer                                                                                                                                                           |

| 19 | CPU1#         | O, DIF  | Complement differential CPU clock output                                                                                                                                                                        |

| 20 | CPU1          | O, DIF  | True differential CPU clock output                                                                                                                                                                              |

| 21 | VSS_CPU       | GND     | Ground for PLL                                                                                                                                                                                                  |

| 22 | CPU0#         | O, DIF  | Complement differential CPU clock output                                                                                                                                                                        |

| 23 | CPU0          | O, DIF  | True differential CPU clock output                                                                                                                                                                              |

| 24 | VDD_CPU       | PWR     | 3.3V Power supply for CPU PLL                                                                                                                                                                                   |

| 25 | CKPWRGD/PD#   | I       | 3.3V LVTTL input. This pin is a level sensitive strobe used to latch the FS. After CKPWRGD (active HIGH) assertion, this pin becomes a real-time input for asserting power down (active LOW)                    |

| 26 | VSS_REF       | GND     | Ground for outputs                                                                                                                                                                                              |

| 27 | XOUT          | O, SE   | 14.318MHz Crystal output                                                                                                                                                                                        |

| 28 | XIN           | I       | 14.318MHz Crystal input                                                                                                                                                                                         |

| 29 | VDD_REF       | PWR     | 3.3V Power supply for outputs and also maintains SMBUS registers during power-down                                                                                                                              |

| 30 | REF/FS**      | PD, I/O | 3.3V tolerant input for Graphic clock selection/fixed 14.318MHz clock output. (Internal 100K-ohm pull-down resistor on FS pin) Refer to DC Electrical Specifications table for Vil_FS and Vih_FS specifications |

| 31 | SDATA         | I/O     | SMBus compatible SDATA                                                                                                                                                                                          |

| 32 | SCLK          | I       | SMBus compatible SCLOCK                                                                                                                                                                                         |

# PC EProClock® Programmable Technology

PC EProClock<sup>®</sup> is the world's first non-volatile programmable PC clock. The PC EProClock<sup>®</sup> technology allows board designer to promptly achieve optimum compliance and clock signal integrity; historically, attainable typically through device and/or board redesigns.

PC EProClock<sup>®</sup> technology can be configured through SMBus or hard coded.

#### Features:

- > 4000 bits of configurations

- Can be configured through SMBus or hard coded

- Custom frequency sets

- Differential skew control on true or compliment or both

- Differential duty cycle control on true or compliment or both

- Differential amplitude control

- Differential and single-ended slew rate control

- Program Internal or External series resistor on single-ended clocks

- Program different spread profiles

- Program different spread modulation rate

- For more information: Please refer to Application Note #25

#### Frequency Select Pin (FS)

|   | FS | CPU    | Power On | SRC     | SATA    | DOT96  | 27MHz  | REF             |

|---|----|--------|----------|---------|---------|--------|--------|-----------------|

| Ī | 0  | 133MHz | Default  | 4001411 | 4001411 | 001411 | 071411 | 4.4.0.4.03.41.1 |

|   | 1  | 100MHz |          | 100MHz  | 100MHz  | 96MHz  | 27MHz  | 14.318MHz       |

#### Frequency Select Pin FS

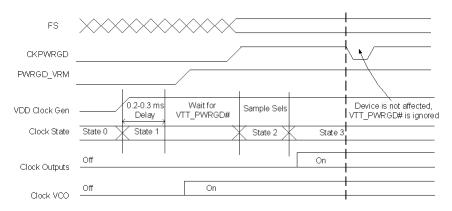

Apply the appropriate logic levels to FS inputs before CKPWRGD assertion to achieve host clock frequency selection. When the clock chip sampled HIGH on CKPWRGD and indicates that VTT voltage is stable then FS input values are sampled. This process employs a one-shot functionality and once the CKPWRGD sampled a valid HIGH, all other FS, and CKPWRGD transitions are ignored except in test mode.

#### **Serial Data Interface**

To enhance the flexibility and function of the clock synthesizer, a two-signal serial interface is provided. Through the Serial Data Interface, various device functions, such as individual clock output buffers are individually enabled or disabled. The registers associated with the Serial Data Interface initialize to their default setting at power-up. The use of this interface is optional. Clock device register changes are normally made at

system initialization, if any are required. The interface cannot be used during system operation for power management functions.

#### **Data Protocol**

The clock driver serial protocol accepts byte write, byte read, block write, and block read operations from the controller. For block write/read operation, access the bytes in sequential order from lowest to highest (most significant bit first) with the ability to stop after any complete byte is transferred. For byte write and byte read operations, the system controller can access individually indexed bytes. The offset of the indexed byte is encoded in the command code described in *Table 1*.

The block write and block read protocol is outlined in *Table 2* while *Table 3* outlines byte write and byte read protocol. The slave receiver address is 11010010 (D2h).

**Table 1. Command Code Definition**

| Bit   | Description                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 7     | 0 = Block read or block write operation, 1 = Byte read or byte write operation                                              |

| (6:0) | Byte offset for byte read or byte write operation. For block read or block write operations, these bits should be '0000000' |

Table 2. Block Read and Block Write Protocol

|       | Block Write Protocol   | Block Read Protocol |                        |

|-------|------------------------|---------------------|------------------------|

| Bit   | Description            | Bit                 | Description            |

| 1     | Start                  | 1                   | Start                  |

| 8:2   | Slave address–7 bits   | 8:2                 | Slave address–7 bits   |

| 9     | Write                  | 9                   | Write                  |

| 10    | Acknowledge from slave | 10                  | Acknowledge from slave |

| 18:11 | Command Code–8 bits    | 18:11               | Command Code–8 bits    |

| 19    | Acknowledge from slave | 19                  | Acknowledge from slave |

| 27:20 | Byte Count–8 bits      | 20                  | Repeat start           |

| 28    | Acknowledge from slave | 27:21               | Slave address–7 bits   |

# Table 2. Block Read and Block Write Protocol (continued)

|       | Block Write Protocol          |       | Block Read Protocol                 |  |  |

|-------|-------------------------------|-------|-------------------------------------|--|--|

| Bit   | Description                   | Bit   | Description                         |  |  |

| 36:29 | Data byte 1–8 bits            | 28    | Read = 1                            |  |  |

| 37    | Acknowledge from slave        | 29    | Acknowledge from slave              |  |  |

| 45:38 | Data byte 2–8 bits            | 37:30 | Byte Count from slave–8 bits        |  |  |

| 46    | Acknowledge from slave        | 38    | Acknowledge                         |  |  |

|       | Data Byte /Slave Acknowledges | 46:39 | Data byte 1 from slave–8 bits       |  |  |

|       | Data Byte N–8 bits            | 47    | Acknowledge                         |  |  |

|       | Acknowledge from slave        | 55:48 | Data byte 2 from slave–8 bits       |  |  |

|       | Stop                          | 56    | Acknowledge                         |  |  |

|       |                               |       | Data bytes from slave / Acknowledge |  |  |

|       |                               |       | Data Byte N from slave–8 bits       |  |  |

|       |                               |       | NOT Acknowledge                     |  |  |

|       |                               |       | Stop                                |  |  |

Table 3. Byte Read and Byte Write Protocol

|       | Byte Write Protocol    |       | Byte Read Protocol     |

|-------|------------------------|-------|------------------------|

| Bit   | Description            | Bit   | Description            |

| 1     | Start                  | 1     | Start                  |

| 8:2   | Slave address–7 bits   | 8:2   | Slave address–7 bits   |

| 9     | Write                  | 9     | Write                  |

| 10    | Acknowledge from slave | 10    | Acknowledge from slave |

| 18:11 | Command Code–8 bits    | 18:11 | Command Code–8 bits    |

| 19    | Acknowledge from slave | 19    | Acknowledge from slave |

| 27:20 | Data byte–8 bits       | 20    | Repeated start         |

| 28    | Acknowledge from slave | 27:21 | Slave address–7 bits   |

| 29    | Stop                   | 28    | Read                   |

|       |                        | 29    | Acknowledge from slave |

|       |                        | 37:30 | Data from slave–8 bits |

|       |                        | 38    | NOT Acknowledge        |

|       |                        | 39    | Stop                   |

......Document #: 001-08400 Rev \*\* Page 4 of 19

# **Control Registers**

# Byte 0: Control Register 0

| Bit | @Pup | Name         | Description                                                                                                                |

|-----|------|--------------|----------------------------------------------------------------------------------------------------------------------------|

| 7   | HW   | FS           | CPU Frequency Select Bit, set by HW 0 = 133MHz, 1= 100MHz                                                                  |

| 6   | 0    | RESERVED     | RESERVED                                                                                                                   |

| 5   | 1    | RESERVED     | RESERVED                                                                                                                   |

| 4   | 0    | iAMT_EN      | iAMT Enable<br>0 = Legacy Mode, 1 = iAMT Enabled                                                                           |

| 3   | 0    | RESERVED     | RESERVED                                                                                                                   |

| 2   | 0    | SRC_Main_SEL | Select source for SRC clock 0 = SRC_MAIN = PLL1, PLL3_CFG Table applies 1 = SRC_MAIN = PLL3, PLL3_CFG Table does not apply |

| 1   | 0    | SATA_SEL     | Select source of SATA clock 0 = SATA = SRC_MAIN, 1= SATA = PLL4                                                            |

| 0   | 1    | PD_Restore   | Save configuration when PD# is asserted 0 = Config. cleared, 1 = Config. saved                                             |

# Byte 1: Control Register 1

| Bit | @Pup | Name       | Description                                                         |

|-----|------|------------|---------------------------------------------------------------------|

| 7   | 1    | RESERVED   | RESERVED                                                            |

| 6   | 0    | PLL1_SS_DC | Select for down or center SS<br>0 = Down spread, 1 = Center spread  |

| 5   | 0    | PLL3_SS_DC | Select for down or center SS<br>0 = Down spread, 1 = Center spread  |

| 4   | 0    | PLL3_CFB3  | CFB Bit [4:1] only applies when SRC_Main_SEL = 0 (Byte 0, bit 2 =0) |

| 3   | 0    | PLL3_CFB2  | See Table 4 on page 9 for Configuration.                            |

| 2   | 1    | PLL3_CFB1  |                                                                     |

| 1   | 0    | PLL3_CFB0  |                                                                     |

| 0   | 1    | RESERVED   | RESERVED                                                            |

# Byte 2: Control Register 2

| Bit | @Pup | Name     | Description                                                   |

|-----|------|----------|---------------------------------------------------------------|

| 7   | 1    | REF_OE   | Output enable for REF 0 = Output Disabled, 1 = Output Enabled |

| 6   | 1    | RESERVED | RESERVED                                                      |

| 5   | 1    | RESERVED | RESERVED                                                      |

| 4   | 1    | RESERVED | RESERVED                                                      |

| 3   | 1    | RESERVED | RESERVED                                                      |

| 2   | 1    | RESERVED | RESERVED                                                      |

| 1   | 1    | RESERVED | RESERVED                                                      |

| 0   | 1    | RESERVED | RESERVED                                                      |

# Byte 3: Control Register 3

| Bit | @Pup | Name     | Description |

|-----|------|----------|-------------|

| 7   | 1    | RESERVED | RESERVED    |

| 6   | 1    | RESERVED | RESERVED    |

| 5   | 1    | RESERVED | RESERVED    |

......Document #: 001-08400 Rev \*\* Page 5 of 19

# Byte 3: Control Register 3

| 4 | 1 | RESERVED | RESERVED |

|---|---|----------|----------|

| 3 | 1 | RESERVED | RESERVED |

| 2 | 1 | RESERVED | RESERVED |

| 1 | 1 | RESERVED | RESERVED |

| 0 | 1 | RESERVED | RESERVED |

# Byte 4: Control Register 4

| Bit | @Pup | Name       | Description                                                                |  |

|-----|------|------------|----------------------------------------------------------------------------|--|

| 7   | 1    | RESERVED   | RESERVED                                                                   |  |

| 6   | 1    | SATA_OE    | Output enable for SATA 0 = Output Disabled, 1 = Output Enabled             |  |

| 5   | 1    | SRC_OE     | Output enable for SRC 0 = Output Disabled, 1 = Output Enabled              |  |

| 4   | 1    | DOT96_OE   | Output enable for DOT96 0 = Output Disabled, 1 = Output Enabled            |  |

| 3   | 1    | CPU1_OE    | Output enable for CPU1 0 = Output Disabled, 1 = Output Enabled             |  |

| 2   | 1    | CPU0_OE    | Output enable for CPU0 0 = Output Disabled, 1 = Output Enabled             |  |

| 1   | 1    | PLL1_SS_EN | Enable PLL1s spread modulation,<br>0 = Spread Disabled, 1 = Spread Enabled |  |

| 0   | 1    | PLL3_SS_EN | Enable PLL3s spread modulation 0 = Spread Disabled, 1 = Spread Enabled     |  |

# Byte 5: Control Register 5

| Bit | @Pup | Name     | Description |

|-----|------|----------|-------------|

| 7   | 0    | RESERVED | RESERVED    |

| 6   | 0    | RESERVED | RESERVED    |

| 5   | 0    | RESERVED | RESERVED    |

| 4   | 0    | RESERVED | RESERVED    |

| 3   | 0    | RESERVED | RESERVED    |

| 2   | 0    | RESERVED | RESERVED    |

| 1   | 0    | RESERVED | RESERVED    |

| 0   | 0    | RESERVED | RESERVED    |

# Byte 6: Control Register 6

| Bit | @Pup | Name        | Description                                                                              |

|-----|------|-------------|------------------------------------------------------------------------------------------|

| 7   | 0    | RESERVED    | RESERVED                                                                                 |

| 6   | 0    | RESERVED    | RESERVED                                                                                 |

| 5   | 0    | REF Bit1    | REF slew rate control (see Byte 13 for Slew Rate Bit 0 and Bit 2) 0 = High, 1 = Low      |

| 4   | 0    | RESERVED    | RESERVED                                                                                 |

| 3   | 0    | 27MHz Bit 1 | 27MHz slew rate control (see Byte 13 for Slew Rate Bit 0 and Bit 2)<br>0 = High, 1 = Low |

| 2   | 0    | RESERVED    | RESERVED                                                                                 |

| 1   | 0    | RESERVED    | RESERVED                                                                                 |

| 0   | 0    | RESERVED    | RESERVED                                                                                 |

# Byte 7: Vendor ID

| Bit | @Pup | Name            | Description         |

|-----|------|-----------------|---------------------|

| 7   | 0    | Rev Code Bit 3  | Revision Code Bit 3 |

| 6   | 1    | Rev Code Bit 2  | Revision Code Bit 2 |

| 5   | 0    | Rev Code Bit 1  | Revision Code Bit 1 |

| 4   | 0    | Rev Code Bit 0  | Revision Code Bit 0 |

| 3   | 1    | Vendor ID bit 3 | Vendor ID Bit 3     |

| 2   | 0    | Vendor ID bit 2 | Vendor ID Bit 2     |

| 1   | 0    | Vendor ID bit 1 | Vendor ID Bit 1     |

| 0   | 0    | Vendor ID bit 0 | Vendor ID Bit 0     |

# Byte 8: Control Register 8

| Bit | @Pup | Name          | Description                                                             |

|-----|------|---------------|-------------------------------------------------------------------------|

| 7   | 1    | Device_ID3    | RESERVED                                                                |

| 6   | 0    | Device_ID2    | RESERVED                                                                |

| 5   | 0    | Device_ID1    | RESERVED                                                                |

| 4   | 0    | Device_ID0    | RESERVED                                                                |

| 3   | 0    | RESERVED      | RESERVED                                                                |

| 2   | 0    | RESERVED      | RESERVED                                                                |

| 1   | 1    | 27M_non-SS_OE | Output enable for 27M_non-SS<br>0 = Output Disabled, 1 = Output Enabled |

| 0   | 1    | 27M_SS_OE     | Output enable for 27M_SS<br>0 = Output Disabled, 1 = Output Enabled     |

# Byte 9: Control Register 9

| Bit | @Pup | Name            | Description                                                                                                                    |  |

|-----|------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | 0    | RESERVED        | RESERVED                                                                                                                       |  |

| 6   | 0    | RESERVED        | RESERVED                                                                                                                       |  |

| 5   | 1    | RESERVED        | RESERVED                                                                                                                       |  |

| 4   | 0    | TEST _MODE_SEL  | Test mode select either REF/N or tri-state 0 = All outputs tri-state, 1 = All output REF/N                                     |  |

| 3   | 0    | TEST_MODE_ENTRY | Allows entry into test mode 0 = Normal Operation, 1 = Enter test mode(s)                                                       |  |

| 2   | 1    | I2C_VOUT<2>     | Amplitude configurations differential clocks                                                                                   |  |

| 1   | 0    | I2C_VOUT<1>     | I2C_VOUT[2:0]                                                                                                                  |  |

| 0   | 1    | I2C_VOUT<0>     | 000 = 0.30V<br>001 = 0.40V<br>010 = 0.50V<br>011 = 0.60V<br>100 = 0.70V<br>101 = 0.80V (default)<br>110 = 0.90V<br>111 = 1.00V |  |

# Byte 10: Control Register 10

| Bit | @Pup | Name     | Description |

|-----|------|----------|-------------|

| 7   | 0    | RESERVED | RESERVED    |

| 6   | 0    | RESERVED | RESERVED    |

| 5   | 0    | RESERVED | RESERVED    |

......Document #: 001-08400 Rev \*\* Page 7 of 19

# Byte 10: Control Register 10 (continued)

| Bit | @Pup | Name     | Description |

|-----|------|----------|-------------|

| 4   | 0    | RESERVED | RESERVED    |

| 3   | 0    | RESERVED | RESERVED    |

| 2   | 0    | RESERVED | RESERVED    |

| 1   | 1    | RESERVED | RESERVED    |

| 0   | 1    | RESERVED | RESERVED    |

# Byte 11: Control Register 11

| Bit | @Pup | Name         | Description                                             |

|-----|------|--------------|---------------------------------------------------------|

| 7   | 0    | RESERVED     | RESERVED                                                |

| 6   | 0    | RESERVED     | RESERVED                                                |

| 5   | 0    | RESERVED     | RESERVED                                                |

| 4   | 0    | RESERVED     | RESERVED                                                |

| 3   | 0    | RESERVED     | RESERVED                                                |

| 2   | 1    | CPU1_iAMT_EN | CPU1 iAMT Clock Enabled<br>0 = Disabled, 1 = Enabled    |

| 1   | 1    | PCI-e_GEN2   | PCI-e_Gen2 Compliant<br>0 = non Gen2, 1= Gen2 Compliant |

| 0   | 1    | RESERVED     | RESERVED                                                |

# Byte 12: Byte Count

| Bit | @Pup | Name | Description                                                                                                    |

|-----|------|------|----------------------------------------------------------------------------------------------------------------|

| 7   | 0    | BC7  | Byte count register for block read operation.                                                                  |

| 6   | 0    | BC6  | The default value for Byte count is 15. In order to read beyond Byte 15, the user should change the byte count |

| 5   | 0    | BC5  | limit.to or beyond the byte that is desired to be read.                                                        |

| 4   | 0    | BC4  |                                                                                                                |

| 3   | 1    | BC3  |                                                                                                                |

| 2   | 1    | BC2  |                                                                                                                |

| 1   | 1    | BC1  |                                                                                                                |

| 0   | 1    | BC0  |                                                                                                                |

# Byte 13: Control Register 13

| Bit | @Pup | Name           | Description                                                                                                                                     |   |   |   |        |  |

|-----|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|--------|--|

| 7   | 1    | REF_Bit2       | Drive Strength Control - Bit[2:0], Note: See Byte 6 Bit 5 for REF Slew Rate Bit 1 and                                                           |   |   |   |        |  |

| 6   | 1    | REF_Bit0       | Byte 6 Bit 3 for 27MHz Slew Rate Bit 1  Normal mode default '101'  Wireless Friendly Mode default to '111'  Mode Bit2 Bit1 Bit0 Buffer Strength |   |   |   |        |  |

| 5   | 1    | 27MHz_NSS_Bit2 |                                                                                                                                                 |   |   |   |        |  |

| 4   | 1    | 27MHz_NSS_Bit0 |                                                                                                                                                 |   |   |   |        |  |

| 3   | 1    | 27MHz_SS_Bit2  |                                                                                                                                                 | 0 | 0 | 0 | Strong |  |

| 2   | 1    | 27MHz_SS_Bit0  |                                                                                                                                                 | 0 | 0 | 1 | ]      |  |

|     |      |                |                                                                                                                                                 | 0 | 1 | 0 |        |  |

|     |      |                |                                                                                                                                                 | 0 | 1 | 1 | ]      |  |

|     |      |                |                                                                                                                                                 | 1 | 0 | 0 |        |  |

|     |      |                | Default                                                                                                                                         | 1 | 0 | 1 |        |  |

|     |      |                | 1 1 0                                                                                                                                           |   |   |   |        |  |

|     |      |                | Wireless Friendly                                                                                                                               | 1 | 1 | 1 | Weak   |  |

| 1   | 0    | RESERVED       | RESERVED                                                                                                                                        |   |   |   |        |  |

| 0 | 0 | Wireless Friendly mode | Wireless Friendly Mode                                                       |

|---|---|------------------------|------------------------------------------------------------------------------|

|   |   | -                      | 0 = Disabled, Default all single-ended clocks slew rate config bits to '101' |

|   |   |                        | 1 = Enabled, Default all single-ended clocks slew rate config bits to '111'  |

#### Byte 14: Control Register 14

| Bit | @Pup | Name     | Description                          |

|-----|------|----------|--------------------------------------|

| 7   | 1    | RESERVED | RESERVED                             |

| 6   | 0    | RESERVED | RESERVED                             |

| 5   | 1    | RESERVED | RESERVED                             |

| 4   | 0    | OTP_4    | OTP_ID                               |

| 3   | 0    | OTP_3    | Identification for programmed device |

| 2   | 0    | OTP_2    |                                      |

| 1   | 0    | OTP_1    |                                      |

| 0   | 0    | OTP_0    |                                      |

#### Table 4. Pin 6 and 7 Configuration Table

| B1b4 | B1b3 | B1b2 | B1b1 | Pin7    | Pin 8  | Spread<br>(%) |

|------|------|------|------|---------|--------|---------------|

| 0    | 0    | 0    | 0    | N/A     | N/A    | N/A           |

| 0    | 0    | 0    | 1    | N/A     | N/A    | N/A           |

| 0    | 0    | 1    | 0    | 27M_NSS | 27M_SS | -0.5%         |

| 0    | 0    | 1    | 1    | 27M_NSS | 27M_SS | -1%           |

| 0    | 1    | 0    | 0    | 27M_NSS | 27M_SS | -1.5%         |

| 0    | 1    | 0    | 1    | 27M_NSS | 27M_SS | -2%           |

| 0    | 1    | 1    | 0    | 27M_NSS | 27M_SS | -0.75V        |

| 0    | 1    | 1    | 1    | 27M_NSS | 27M_SS | -1.25%        |

| 1    | 0    | 0    | 0    | 27M_NSS | 27M_SS | -1.75%        |

| 1    | 0    | 0    | 1    | 27M_NSS | 27M_SS | +/-0.5%       |

| 1    | 0    | 1    | 0    | 27M_NSS | 27M_SS | +/-0.75%      |

| 1    | 0    | 1    | 1    | N/A     | N/A    | N/A           |

| 1    | 1    | 0    | 0    | N/A     | N/A    | N/A           |

| 1    | 1    | 0    | 1    | N/A     | N/A    | N/A           |

| 1    | 1    | 1    | 0    | N/A     | N/A    | N/A           |

| 1    | 1    | 1    | 1    | N/A     | N/A    | N/A           |

# Table 5. Output Driver Status during 27\_OE#

|                           | 27M_OE# Asserted | 27M_OE# Deasserted | SMBus OE Disabled |

|---------------------------|------------------|--------------------|-------------------|

| 27M_SS & 27M_NSS          | Stoppable        | Running            | Deiteration       |

| Other single-ended clocks | Running          | Running            | Driven low        |

| D:#anantial Olaska        | Running          | Running            | Drivers Issue     |

| Differential Clocks       | Running          | Running            | Driven low        |

|                           | Running          | Running            |                   |

# **Table 6. Output Driver Status**

| All Single-e | nded Clocks | All Differential Clocks |        |  |

|--------------|-------------|-------------------------|--------|--|

| w/o Strap    | w/ Strap    | Clock                   | Clock# |  |

......Document #: 001-08400 Rev \*\* Page 9 of 19

#### **Table 6. Output Driver Status**

| PD# = 0 (Power down) | Low | Hi-z | Low | Low | ì |

|----------------------|-----|------|-----|-----|---|

|----------------------|-----|------|-----|-----|---|

**Table 7. Crystal Recommendations**

| Frequency<br>(Fund) | Cut | Loading  | Load Cap | Drive<br>(max.) | Shunt Cap<br>(max.) | Motional (max.) | Tolerance<br>(max.) | Stability (max.) | Aging (max.) |

|---------------------|-----|----------|----------|-----------------|---------------------|-----------------|---------------------|------------------|--------------|

| 14.31818 MHz        | AT  | Parallel | 20 pF    | 0.1 mW          | 5 pF                | 0.016 pF        | 35 ppm              | 30 ppm           | 5 ppm        |

The SL28774 requires a Parallel Resonance Crystal. Substituting a series resonance crystal causes the SL28774 to operate at the wrong frequency and violates the ppm specification. For most applications there is a 300-ppm frequency shift between series and parallel crystals due to incorrect loading.

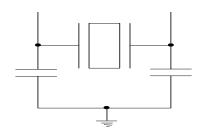

#### **Crystal Loading**

Crystal loading plays a critical role in achieving low ppm performance. To realize low ppm performance, use the total capacitance the crystal sees to calculate the appropriate capacitive loading (CL).

Figure 1 shows a typical crystal configuration using the two trim capacitors. It is important that the trim capacitors are in series with the crystal. It is not true that load capacitors are in parallel with the crystal and are approximately equal to the load capacitance of the crystal.

Figure 1. Crystal Capacitive Clarification

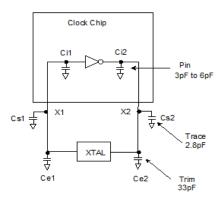

#### **Calculating Load Capacitors**

In addition to the standard external trim capacitors, consider the trace capacitance and pin capacitance to calculate the crystal loading correctly. Again, the capacitance on each side is in series with the crystal. The total capacitance on both side is twice the specified crystal load capacitance (CL). Trim capacitors are calculated to provide equal capacitive loading on both sides.

Figure 2. Crystal Loading Example

Use the following formulas to calculate the trim capacitor values for Ce1 and Ce2.

Load Capacitance (each side)

$$\mathbf{Ce} = 2 * CL - (Cs + Ci)$$

Total Capacitance (as seen by the crystal)

CLe =

$$\frac{1}{\left(\frac{1}{Ce1 + Cs1 + Ci1} + \frac{1}{Ce2 + Cs2 + Ci2}\right)}$$

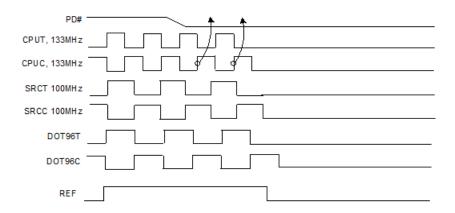

#### PD# (Power down) Clarification

The CKPWRGD/PD# pin is a dual-function pin. During initial power up, the pin functions as CKPWRGD. Once CKPWRGD has been sampled HIGH by the clock chip, the pin assumes PD# functionality. The PD# pin is an asynchronous active LOW input used to shut off all clocks cleanly before shutting off power to the device. This signal is synchronized internally to the device before powering down the clock synthesizer. PD# is also an asynchronous input for powering up the system. When PD# is asserted LOW, clocks are driven to a LOW value and held before turning off the VCOs and the crystal oscillator.

#### PD# (Power down) Assertion

When PD# is sampled LOW by two consecutive rising edges of CPU clocks, all single-ended outputs will be held LOW on their next HIGH-to-LOW transition and differential clocks must

held LOW. When PD# mode is desired as the initial power on state, PD# must be asserted LOW in less than 10  $\mu$ s after asserting CKPWRGD.

#### **PD# Deassertion**

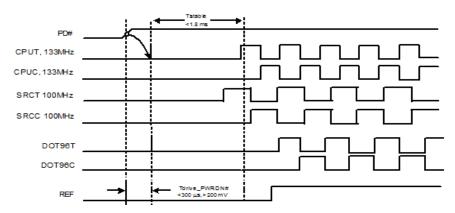

The power up latency is less than 1.8 ms. This is the time from the deassertion of the PD# pin or the ramping of the power supply until the time that stable clocks are generated from the clock chip. All differential outputs stopped in a three-state condition, resulting from are driven high in less than 300  $\mu$ s of PD# deassertion to a voltage greater than 200 mV. After the clock chip's internal PLL is powered up and locked, all outputs are enabled within a few clock cycles of each clock. *Figure 4* is an example showing the relationship of clocks coming up.

Figure 3. Power Down Assertion Timing Waveform

Figure 4. Power Down Deassertion Timing Waveform

Figure 5. CKPWRGD Timing Diagram

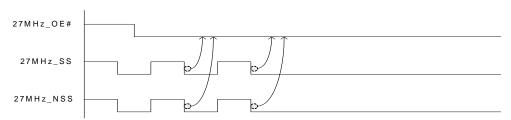

#### 27M\_OE# Assertion

The 27M\_OE# signal is an active LOW input used for stopping and starting both 27MHz spread and 27MHz non-spread output clocks while the rest of the clock generator continues to function. When the 27M\_OE# pin is asserted, both 27MHz spread and 27MHz non-spread outputs are stopped after they are sampled by two falling edges of the internal 27MHz clock. The final states of the stopped 27MHz spread and 27MHz non-spread signals are LOW.

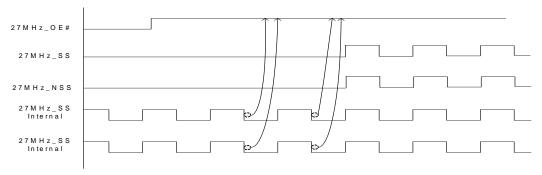

#### 27M\_OE# Deassertion

The deassertion of the 27M\_OE# signal causes both stopped 27MHz spread and 27MHz non-spread outputs to resume normal operation in a synchronous manner. No short or stretched clock pulses are produced when the clock resumes. The maximum latency from the deassertion to active outputs is no more than two 27MHz clock cycles.

Figure 6. 27M\_OE# Assertion Waveform

Figure 7. 27M\_OE# Deassertion Waveform

# **Absolute Maximum Conditions**

| Parameter          | Description                       | Condition                   | Min. | Max.  | Unit     |

|--------------------|-----------------------------------|-----------------------------|------|-------|----------|

| $V_{DD\_3.3V}$     | Main Supply Voltage               |                             | _    | 4.6   | V        |

| $V_{DD\_IO}$       | IO Supply Voltage                 |                             |      | 3.465 | V        |

| V <sub>IN</sub>    | Input Voltage                     | Relative to V <sub>SS</sub> | -0.5 | 4.6   | $V_{DC}$ |

| T <sub>S</sub>     | Temperature, Storage              | Non-functional              | -65  | 150   | °C       |

| T <sub>A</sub>     | Temperature, Operating Ambient    | Functional                  | -40  | 85    | °C       |

| T <sub>J</sub>     | Temperature, Junction             | Functional                  | _    | 150   | °C       |

| Ø <sub>JC</sub>    | Dissipation, Junction to Case     | MIL-STD-883E Method 1012.1  | -    | 20    | °C/<br>W |

| Ø <sub>JA</sub>    | Dissipation, Junction to Ambient  | JEDEC (JESD 51)             | -    | 60    | °C/<br>W |

| ESD <sub>HBM</sub> | ESD Protection (Human Body Model) | MIL-STD-883, Method 3015    | 2000 | -     | V        |

| UL-94              | Flammability Rating               | At 1/8 in.                  | V-   | -0    |          |

| MSL                | Moisture Sensitivity Level        |                             | ,    | 1     |          |

Multiple Supplies: The Voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.

# **DC Electrical Specifications**

| Parameter              | Description                      | Condition                                                                                                  | Min.               | Max.               | Unit |

|------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| VDD core               | 3.3V Operating Voltage           | 3.3 ± 5%                                                                                                   | 3.135              | 3.465              | V    |

| V <sub>IH</sub>        | 3.3V Input High Voltage (SE)     |                                                                                                            | 2.0                | $V_{DD} + 0.3$     | V    |

| V <sub>IL</sub>        | 3.3V Input Low Voltage (SE)      |                                                                                                            | $V_{SS} - 0.3$     | 0.8                | V    |

| V <sub>IHI2C</sub>     | Input High Voltage               | SDATA, SCLK                                                                                                | 2.2                | _                  | V    |

| V <sub>ILI2C</sub>     | Input Low Voltage                | SDATA, SCLK                                                                                                | _                  | 1.0                | V    |

| V <sub>IH_FS</sub>     | FS Input High Voltage            |                                                                                                            | 0.7                | VDD+0.3            | V    |

| $V_{IL_FS}$            | FS Input Low Voltage             |                                                                                                            | $V_{SS} - 0.3$     | 0.35               | V    |

| I <sub>IH</sub>        | Input High Leakage Current       | Except internal pull-down resistors, $0 < V_{IN} < V_{DD}$                                                 | _                  | 5                  | μА   |

| I <sub>IL</sub>        | Input Low Leakage Current        | Except internal pull-up resistors, 0 < V <sub>IN</sub> < V <sub>DD</sub>                                   | <b>-</b> 5         | _                  | μА   |

| V <sub>OH</sub>        | 3.3V Output High Voltage (SE)    | $I_{OH} = -1 \text{ mA}$                                                                                   | 2.4                | _                  | V    |

| V <sub>OL</sub>        | 3.3V Output Low Voltage (SE)     | I <sub>OL</sub> = 1 mA                                                                                     | _                  | 0.4                | V    |

| V <sub>DD IO</sub>     | Low Voltage IO Supply Voltage    |                                                                                                            | 1                  | 3.465              | V    |

| I <sub>OZ</sub>        | High-impedance Output<br>Current |                                                                                                            | -10                | 10                 | μА   |

| C <sub>IN</sub>        | Input Pin Capacitance            |                                                                                                            | 1.5                | 5                  | pF   |

| C <sub>OUT</sub>       | Output Pin Capacitance           |                                                                                                            |                    | 6                  | pF   |

| L <sub>IN</sub>        | Pin Inductance                   |                                                                                                            | _                  | 7                  | nΗ   |

| V <sub>XIH</sub>       | Xin High Voltage                 |                                                                                                            | 0.7V <sub>DD</sub> | $V_{DD}$           | V    |

| V <sub>XIL</sub>       | Xin Low Voltage                  |                                                                                                            | 0                  | 0.3V <sub>DD</sub> | V    |

| IDD_ <sub>PD</sub>     | Power Down Current               |                                                                                                            | _                  | 1                  | mA   |

| I <sub>DD_3.3V</sub>   | Dynamic Supply Current           | All outputs enabled. SE clocks with 8" traces. Differential clocks with 7" traces. Loading per CK505 spec. | -                  | 65                 | mA   |

| I <sub>DD_VDD_IO</sub> | Dynamic Supply Current           | All outputs enabled. SE clocks with 8" traces. Differential clocks with 7" traces. Loading per CK505 spec. | ı                  | 25                 | mA   |

......Document #: 001-08400 Rev \*\* Page 13 of 19

# **AC Electrical Specifications**

| Parameter                       | Description                                                  | Condition                                                                                                                     | Min.     | Max.     | Unit |

|---------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------|----------|------|

| Crystal                         | ,                                                            |                                                                                                                               |          | L        | _    |

| T <sub>DC</sub>                 | XIN Duty Cycle                                               | The device operates reliably with input duty cycles up to 30/70 but the REF clock duty cycle will not be within specification | 47.5     | 52.5     | %    |

| T <sub>PERIOD</sub>             | XIN Period                                                   | When XIN is driven from an external clock source                                                                              | 69.841   | 71.0     | ns   |

| $T_R/T_F$                       | XIN Rise and Fall Times                                      | Measured between 0.3V <sub>DD</sub> and 0.7V <sub>DD</sub>                                                                    | -        | 10.0     | ns   |

| T <sub>CCJ</sub>                | XIN Cycle to Cycle Jitter                                    | As an average over 1-µs duration                                                                                              | -        | 500      | ps   |

| CPU at 0.7V                     |                                                              |                                                                                                                               |          | ľ        |      |

| T <sub>DC</sub>                 | CPUT and CPUC Duty Cycle                                     | Measured at 0V differential                                                                                                   | 45       | 55       | %    |

| T <sub>PERIOD</sub>             | 100 MHz CPUT and CPUC Period                                 | Measured at 0V differential at 0.1s                                                                                           | 9.99900  | 10.00100 | ns   |

| T <sub>PERIOD</sub>             | 133 MHz CPUT and CPUC Period                                 | Measured at 0V differential at 0.1s                                                                                           | 7.49925  | 7.50075  | ns   |

| T <sub>PERIODSS</sub>           | 100 MHz CPUT and CPUC Period, SSC                            | Measured at 0V differential at 0.1s                                                                                           | 10.02406 | 10.02607 | ns   |

| T <sub>PERIODSS</sub>           | 133 MHz CPUT and CPUC Period, SSC                            | Measured at 0V differential at 0.1s                                                                                           | 7.51804  | 7.51955  | ns   |

| T <sub>PERIODAbs</sub>          | 100 MHz CPUT and CPUC Absolute period                        | Measured at 0V differential at 1 clock                                                                                        | 9.91400  | 10.0860  | ns   |

| T <sub>PERIODAbs</sub>          | 133 MHz CPUT and CPUC Absolute period                        | Measured at 0V differential at 1 clock                                                                                        | 7.41425  | 7.58575  | ns   |

| T <sub>PERIODSSAbs</sub>        | 100 MHz CPUT and CPUC Absolute period, SSC                   | Measured at 0V differential at1 clock                                                                                         | 9.914063 | 10.1362  | ns   |

| T <sub>PERIODSSAbs</sub>        | 133 MHz CPUT and CPUC Absolute period, SSC                   | Measured at 0V differential at1 clock                                                                                         | 7.41430  | 7.62340  | ns   |

| T <sub>CCJ</sub>                | CPU Cycle to Cycle Jitter                                    | Measured at 0V differential                                                                                                   | _        | 85       | ps   |

| Skew                            | CPU0 to CPU1 skew                                            | Measured at 0V differential                                                                                                   | _        | 100      | ps   |

| L <sub>ACC</sub>                | Long-term Accuracy                                           | Measured at 0V differential                                                                                                   | -        | 100      | ppm  |

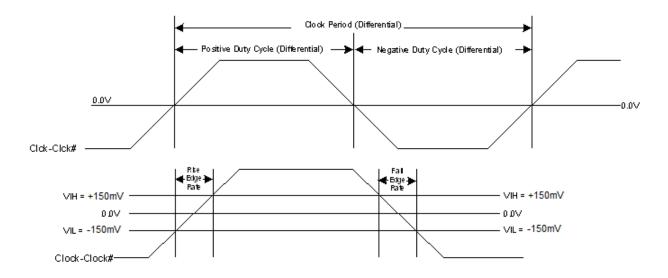

| $T_R/T_F$                       | CPU Rising/Falling Slew rate                                 | Measured differentially from ±150 mV                                                                                          | 2.5      | 8        | V/ns |

| T <sub>RFM</sub>                | Rise/Fall Matching                                           | Measured single-endedly from ±75 mV                                                                                           | -        | 20       | %    |

| $V_{HIGH}$                      | Voltage High                                                 |                                                                                                                               |          | 1.15     | V    |

| $V_{LOW}$                       | Voltage Low                                                  |                                                                                                                               | -0.3     | _        | V    |

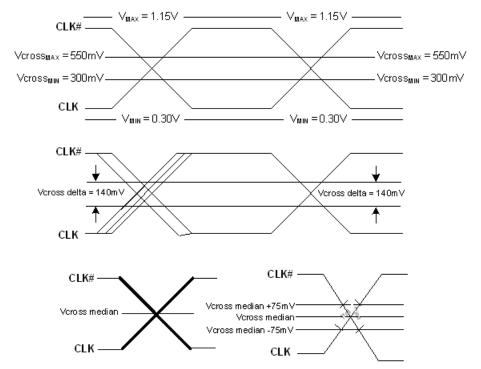

| V <sub>OX</sub>                 | Crossing Point Voltage at 0.7V Swing                         |                                                                                                                               | 300      | 550      | mV   |

| SRC at 0.7V                     |                                                              |                                                                                                                               |          |          |      |

| T <sub>DC</sub>                 | SRC Duty Cycle                                               | Measured at 0V differential                                                                                                   | 45       | 55       | %    |

| T <sub>PERIOD</sub>             | 100 MHz SRC Period                                           | Measured at 0V differential at 0.1s                                                                                           | 9.99900  | 10.0010  | ns   |

| T <sub>PERIODSS</sub>           | 100 MHz SRC Period, SSC                                      | Measured at 0V differential at 0.1s                                                                                           | 10.02406 | 10.02607 | ns   |

| T <sub>PERIODAbs</sub>          | 100 MHz SRC Absolute Period                                  | Measured at 0V differential at 1 clock                                                                                        | 9.87400  | 10.1260  | ns   |

| T <sub>PERIODSSAbs</sub>        | 100 MHz SRC Absolute Period, SSC                             | Measured at 0V differential at 1 clock                                                                                        | 9.87406  | 10.1762  | ns   |

| T <sub>SKEW(window)</sub>       | Any SRC Clock Skew from the earliest bank to the latest bank | Measured at 0V differential                                                                                                   | -        | 3.0      | ns   |

| T <sub>CCJ</sub>                | SRC Cycle to Cycle Jitter                                    | Measured at 0V differential                                                                                                   | -        | 125      | ps   |

| L <sub>ACC</sub>                | SRC Long Term Accuracy                                       | Measured at 0V differential                                                                                                   | -        | 100      | ppm  |

| T <sub>R</sub> / T <sub>F</sub> | SRC Rising/Falling Slew Rate                                 | Measured differentially from ±150 mV                                                                                          | 2.5      | 8        | V/ns |

| T <sub>RFM</sub>                | Rise/Fall Matching                                           | Measured single-endedly from ±75 mV                                                                                           | -        | 20       | %    |

| V <sub>HIGH</sub>               | Voltage High                                                 |                                                                                                                               |          | 1.15     | V    |

| $V_{LOW}$                       | Voltage Low                                                  |                                                                                                                               | -0.3     | -        | V    |

| V <sub>OX</sub>                 | Crossing Point Voltage at 0.7V Swing                         |                                                                                                                               | 300      | 550      | mV   |

| DOT96 at 0.7V                   | i                                                            |                                                                                                                               |          | •        |      |

# AC Electrical Specifications (continued)

| Parameter                       | Description                          | Condition                                  | Min.     | Max.     | Unit |

|---------------------------------|--------------------------------------|--------------------------------------------|----------|----------|------|

| T <sub>DC</sub>                 | DOT96 Duty Cycle                     | Measured at 0V differential                | 45       | 55       | %    |

| T <sub>PERIOD</sub>             | PERIOD DOT96 Period Measured at 0V   |                                            | 10.4156  | 10.4177  | ns   |

| T <sub>PERIODAbs</sub>          | DOT96 Absolute Period                | Measured at 0V differential at 0.1s        | 10.1656  | 10.6677  | ns   |

| T <sub>CCJ</sub>                | DOT96 Cycle to Cycle Jitter          | Measured at 0V differential at 1 clock     | _        | 250      | ps   |

| L <sub>ACC</sub>                | DOT96 Long Term Accuracy             | Measured at 0V differential at 1 clock     | _        | 100      | ppm  |

| T <sub>R</sub> / T <sub>F</sub> | DOT96 Rising/Falling Slew Rate       | Measured differentially from ±150 mV       | 2.5      | 8        | V/ns |

| T <sub>RFM</sub>                | Rise/Fall Matching                   | Measured single-endedly from ±75 mV        | _        | 20       | %    |

| V <sub>HIGH</sub>               | Voltage High                         |                                            |          | 1.15     | V    |

| $V_{LOW}$                       | Voltage Low                          |                                            | -0.3     | _        | V    |

| V <sub>OX</sub>                 | Crossing Point Voltage at 0.7V Swing |                                            | 300      | 550      | mV   |

| 27M_NSS/27_                     | SS at 3.3V                           |                                            |          | <u>'</u> |      |

| T <sub>DC</sub>                 | Duty Cycle                           | Measurement at 1.5V                        | 45       | 55       | %    |

| T <sub>PERIOD</sub>             | Spread 27M Period                    | Measurement at 1.5V                        | 37.03594 | 37.03813 | ns   |

|                                 | Spread Enabled 27M Period            | Measurement at 1.5V                        | 37.12986 | 37.13172 | ns   |

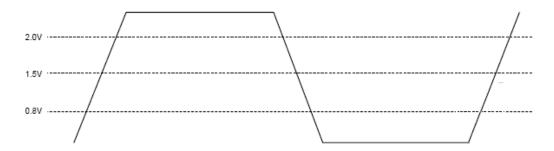

| T <sub>R</sub> / T <sub>F</sub> | Rising and Falling Edge Rate         | Measured between 0.8V and 2.0V             | 1.0      | 4.0      | V/ns |

| T <sub>CCJ</sub>                | Cycle to Cycle Jitter                | Measurement at 1.5V                        | _        | 300      | ps   |

| L <sub>ACC</sub>                | 27_M Long Term Accuracy              | Measured at crossing point V <sub>OX</sub> | -        | 50       | ppm  |

| REF                             |                                      |                                            |          |          |      |

| T <sub>DC</sub>                 | REF Duty Cycle                       | Measurement at 1.5V                        | 45       | 55       | %    |

| T <sub>PERIOD</sub>             | REF Period                           | Measurement at 1.5V                        | 69.82033 | 69.86224 | ns   |

| T <sub>PERIODAbs</sub>          | REF Absolute Period                  | Measurement at 1.5V                        | 68.83429 | 70.84826 | ns   |

| T <sub>HIGH</sub>               | REF High time                        | Measurement at 2V                          | 29.97543 | 38.46654 | ns   |

| T <sub>LOW</sub>                | REF Low time                         | Measurement at 0.8V                        | 29.57543 | 38.26654 | ns   |

| T <sub>R</sub> / T <sub>F</sub> | REF Rising and Falling Edge Rate     | Measured between 0.8V and 2.0V             | 1.0      | 4.0      | V/ns |

| T <sub>SKEW</sub>               | REF Clock to REF Clock               | Measurement at 1.5V                        | _        | 500      | ps   |

| T <sub>CCJ</sub>                | REF Cycle to Cycle Jitter            | Measurement at 1.5V                        | -        | 1000     | ps   |

| L <sub>ACC</sub>                | Long Term Accuracy                   | Measurement at 1.5V                        | -        | 100      | ppm  |

| ENABLE/DIS/                     | ABLE and SET-UP                      |                                            |          |          |      |

| T <sub>STABLE</sub>             | Clock Stabilization from Power-up    |                                            | -        | 1.8      | ms   |

| T <sub>SS</sub>                 | Stopclock Set-up Time                |                                            | 10.0     | _        | ns   |

# **Test and Measurement Set-up**

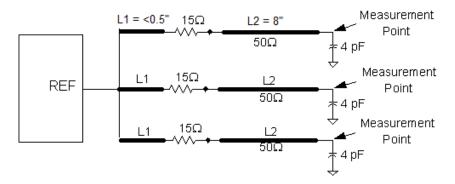

#### For Reference Clock

The following diagram shows the test load configurations for the single-ended REF output signal.

Figure 8. Single-ended REF Triple Load Configuration

Figure 9. Single-ended Output Signals (for AC Parameters Measurement)

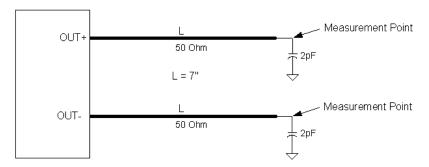

#### For Differential Clock Signals

This diagram shows the test load configuration for the differential clock signals

Figure 10. 0.7V Differential Load Configuration

Figure 11. Differential Measurement for Differential Output Signals (for AC Parameters Measurement)

Figure 12. Single-ended Measurement for Differential Output Signals (for AC Parameters Measurement)

# **Ordering Information**

| Part Number | Package Type                               | Product Flow             |

|-------------|--------------------------------------------|--------------------------|

| Lead-free   |                                            |                          |

| SL28774ELI  | 32-pin QFN                                 | Industrial, -40° to 85°C |

| SL28774ELIT | 32-pin QFN-Tape and Reel                   | Industrial, -40° to 85°C |

| SL 28 774   | ELI-T                                      |                          |

| SL 28 774   | Packaging Designate  Temperature Designate | ·                        |

| SL 28 774   | Packaging Designato                        | ·                        |

Generic Part Number

Company Initials

**Designated Family Number**

This device is Pb free and RoHS compliant.

# **Package Diagrams**

# 32-Lead QFN 5x 5mm (Saw Version)

#### **Document History Page**

| Docum | Pocument Title: SL28774 PC EProClock <sup>®</sup> Generator for Intel Calpella Chipset |                    |                                                                                                                                                                                                                     |  |  |  |

|-------|----------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| REV.  | Issue Date                                                                             | Orig. of<br>Change | Description of Change                                                                                                                                                                                               |  |  |  |

| 1.0   | 07/22/08                                                                               | JMA                | Initial Release                                                                                                                                                                                                     |  |  |  |

| 1.1   | 09/08/09                                                                               | JMA                | Removed Preliminary                                                                                                                                                                                                 |  |  |  |

| 1.2   | 10/02/09                                                                               | JMA                | Updated note in package diagram                                                                                                                                                                                     |  |  |  |

| 1.3   | 01/05/10                                                                               | JMA                | 1. Added Note in package diagram 2. Updated text content 3. Added information on trace length in Figure 8 4. Removed CPU Driven Figures 5. Updated VDD_IO spec to 3.465 maximum value 6. Edited CK_PWRGD to CKPWRGD |  |  |  |

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.