## **JN Semiconductor®**

To k are more about Old Semiconductor, please visit our website at www.onsemi.com

Please note. As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

February 2013

# FSFR-HS Series — Advanced Fairchild Power Switch (FPS™) for Half-Bridge Resonant Converters

#### **Features**

- Variable Frequency Control with 50% Duty Cycle for Half-Bridge Resonant Converter Topology

- High Efficiency through Zero Voltage Switching (ZVS)

- Built-in High-Side Gate Driver IC

- Internal UniFET™s with Fast-Recovery Type Body Diode (t<sub>rr</sub>=160 ns Typical)

- Fixed Dead Time (350 ns) Optimized for MOSFETs

- Operating Frequency Up to 600 kHz for Soft-Start

- Self Auto-Restart Operation for All Protections, Despired

External LV<sub>CC</sub> Bias

- Line UVLO with Programmable Hysteresis Level

- Simple On/Off with Line UVLO Pin

- Easy Configuration and Compati<sup>F</sup> .y w. F<sub>F</sub> 7930 or Line UVLO without External Corponents

#### Applications

- OP and CL Vs

- D ktop Cs and Servers

- Ada, Jrs

- Telecom Power Supplies

## Description

The FSFR-HS is a highly egrate power switch designed for high-efficiency half-brige resonant converters. Offering regrything there ary to build a reliable and robust remainder the FSFR-HS simplifies designs while imprising productivity and performance. The FSIR-HS simplifies designs while imprising productivity and performance. The FSIR-HS simplifies power MOSFETs, a high-size te-drive circuit an accurate current-controlled wrill a resultable protection functions.

The particular description of the provides stable operation with excellent noise immunity. Using zero-voltage-switching (ZVS) tearnique dramatically reduces the switching lesses and significantly improves efficiency. The ZVS also reduces the switching noise noticeably, even though the operating frequency increases. It allows a small Electromagnetic Interference (EMI) filter, besides the high operating frequency, to reduce the volume of the resonant tank and to increase power density.

The FSFR FS can be applied to resonant converter topologies such as series resonant, parallel resonant, and LLC resonant converters.

#### Related Resources

AN4151 — Half-Bridge LLC Resonant Converter Design Using FSFR-Series Fairchild Power Switch (FPS™)

## Ordering Information

| Part Number | Package            | Operating<br>Junction<br>Temperature | R <sub>DS(ON_MAX)</sub> | Maximum Output Power without Heatsink (V <sub>IN</sub> =350~400 V) <sup>(1,2)</sup> | Maximum Output Power with Heatsink $(V_{IN}=350\sim400 \text{ V})^{(1,2)}$ |  |

|-------------|--------------------|--------------------------------------|-------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| FSFR1800HS  | 9-SIP              |                                      |                         |                                                                                     |                                                                            |  |

| FSFR1800HSL | 9-SIP<br>L-Forming | -40 to +130°C                        | 0.95 Ω                  | 120 W                                                                               | 260 W                                                                      |  |

| FSFR1700HS  | 9-SIP              |                                      |                         |                                                                                     |                                                                            |  |

| FSFR1700HSL | 9-SIP<br>L-Forming | -40 to +130°C                        | 1.25 Ω                  | 100 W                                                                               | 200 W                                                                      |  |

#### Notes:

- 1. The junction temperature can limit the maximum output power.

- Maximum practical continuous power in an open-frame design at 50°C ambient.

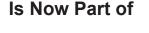

## **Application Circuit Diagram**

Figure 1. Typical Application Circuit (L C h to. 'alf-Bridge Converter)

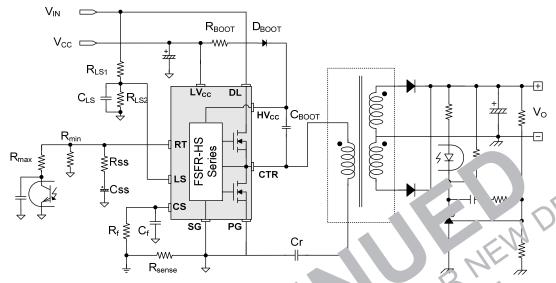

## **Block Diagram**

Figure 2. Internal Block Diagram

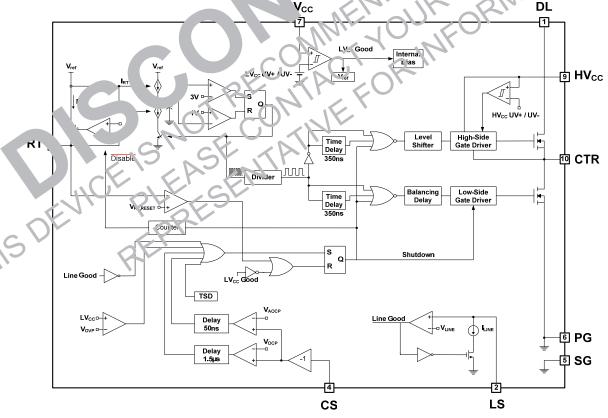

## **Pin Configuration**

Figure 3. Package Diagra

## **Pin Definitions**

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1 2 3 4 5 6 7 8 9 10 DL LS CSSG LV <sub>CC</sub> CTR RT PG HV <sub>CC</sub>                                          |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 3. Package Diagra                                                                                             |  |  |

| Pin Defi | nitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EDFORMION                                                                                                            |  |  |

| Pin #    | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Description                                                                                                          |  |  |

| 1        | DL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | This is the drain of a many the MOSi ET, typically connected to the input DC link voltage.                           |  |  |

| 2        | LS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | This is t' line-s sin nin for the เกอน voltage Under-Voltage Lockout (UVLO).                                         |  |  |

| 3        | Jin used f controlling the switching frequency in normal operation. When any protection, aggered, the internal Auto/Restant (A/R) circuit starts to sense the voltage on the pin which is discharged naturally by external resistance. The IC can be operated with R which the voltage decreases 0.1 V. Typically, an opto-coupler is connected to control the switching frequency for the output voltage regulation and resistors for setting minimum / maximum operating frequency. |                                                                                                                      |  |  |

| 4        | cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | This pin senses the current to ving through the low-side MOSFET. Typically, negative voltage is applied to this pin. |  |  |

|          | SG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | This pin is the ground of the control part.                                                                          |  |  |

| 6        | I/G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | This put is the power ground. This pin is connected to the source of the low-side MOSFET.                            |  |  |

| 7        | $LV_CC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | This pin is the supply voltage of the control IC.                                                                    |  |  |

| 8        | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No connection                                                                                                        |  |  |

| <b>9</b> | HVcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 bis is the supply voltage of the high-side gate-drive circuit.                                                     |  |  |

| 10       | CTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | This is the drain of the low-side MOSFET. Typically, a transformer is connected to this pin.                         |  |  |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                          | Pa                                                  | Min.                               | Max. | Unit            |        |  |  |

|---------------------------------|-----------------------------------------------------|------------------------------------|------|-----------------|--------|--|--|

| $V_{DS}$                        | Maximum Drain-to-Source Voltage (DL-CTR and CTR-PG) |                                    |      |                 | V      |  |  |

| LV <sub>CC</sub>                | Low-Side Supply Voltage                             | -0.3                               | 25.0 | V               |        |  |  |

| HV <sub>CC</sub> to CTR         | High-Side V <sub>CC</sub> Pin to Low-Sid            | le Drain Voltage                   | -0.3 | 25.0            | V      |  |  |

| HV <sub>CC</sub>                | High-Side Floating Supply Vo                        | ltage                              | -0.3 | 525.0           | V      |  |  |

| $V_{RT}$                        | Timing Resistor Connecting a                        | and Auto-Restart Pin Voltage       | -0.3 |                 | V      |  |  |

| $V_{LS}$                        | Line Sensing Input Voltage                          |                                    | -0.3 | LV <sub>C</sub> | У.     |  |  |

| V <sub>CS</sub>                 | Current Sense (CS) Pin Input                        | : Voltage                          | 0    | 1               | V      |  |  |

| $f_{sw}$                        | Recommended Switching Fre                           | equency                            |      | 000             | kHz    |  |  |

| dV <sub>CTR</sub> /dt           | Allowable Low-Side MOSFET                           | Drain Voltage Slew Rate            |      | 50              | V/ns   |  |  |

| Б.                              | T 1 1 D D: (4)                                      | FSFR1800HS/L                       |      | V1.7            | W      |  |  |

| $P_D$                           | Total Power Dissipation <sup>(4)</sup>              | FSFR1700HS/I                       | 00   | 11.6            |        |  |  |

| _                               | Maximum Junction Temperat                           | ure <sup>(5)</sup>                 | 50,  | +150            | 12.    |  |  |

| IJ                              | Recommended Operating Junction T                    |                                    |      | +130            | °C     |  |  |

| T <sub>STG</sub>                | Storage Temperature Range                           | 55                                 | +150 | °C              |        |  |  |

| MOSFET Sect                     | tion                                                | SUP                                | 20   | 1/1/            |        |  |  |

| $V_{DGR}$                       | Drain Gate Voltage GS=                              |                                    | 500  |                 | V      |  |  |

| $V_{GS}$                        | Gate Source (GNE /oltage                            | <u> </u>                           | ZY-  | ±30             | V      |  |  |

|                                 | Dunin Out and Bull and                              | FSFR1800HS//_                      |      | 23              | ^      |  |  |

| I <sub>DM</sub>                 | Drain Cu ent Pulsed                                 | FSFR1700HS/L                       |      | 20              | Α      |  |  |

|                                 |                                                     | T <sub>C</sub> =25°C               |      | 7.0             |        |  |  |

|                                 | Corting us Drain Current                            | F3FP: 800HS/L 7c=100°C             |      | 4.5             | ^      |  |  |

|                                 |                                                     | T <sub>C</sub> =25°C               |      | 6.0             | Α      |  |  |

|                                 | 13,15                                               | FS-R1700HS/L T <sub>C</sub> =100°C |      | 3.9             |        |  |  |

| Pack 'r ect                     | ior                                                 |                                    |      |                 |        |  |  |

| Torque Recommended Screw Torque |                                                     |                                    |      | -7              | kgf⋅cm |  |  |

#### Notes:

- 3 These parameters, although guaranteed, are tested only in EDS (wafer test) process.

- 4. Per MOSFET when to n MOSFETs are conducting.

- 5. The maximum value of the recommended operating junction temperature is limited by thermal shutdown.

- 6. Pulse width is limited by maximum junction temperature.

## Thermal Impedance

T<sub>A</sub>=25°C unless otherwise specified.

| Symbol        | Parameter                                 | Value                        | Unit |      |

|---------------|-------------------------------------------|------------------------------|------|------|

| Δ             | Junction-to-Case Center Thermal Impedance | FSFR1800HS/L                 | 10.7 | °C/W |

| $\theta_{JC}$ | (Both MOSFETs Conducting)                 | FSFR1700HS/L                 | 10.8 | G/VV |

| $\theta_{JA}$ | Junction-to-Ambient Thermal Impedance     | FSFR1800HS/L<br>FSFR1700HS/L | 80   | °C/W |

## **Electrical Characteristics**

$T_A$  =25°C, LV<sub>CC</sub>, HV<sub>CC</sub> =17 V<sub>DC</sub> and  $R_T$  =26  $k\Omega$  unless otherwise specified.

| Symbol                                                              | Paran                                                                                  | Conditions                                    | Min.                                                                                 | Тур. | Max.       | Unit    |          |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------|------|------------|---------|----------|

| MOSFET S                                                            | ection                                                                                 |                                               |                                                                                      |      |            |         |          |

| BV <sub>DSS</sub> Drain-to-Source Breakdow                          |                                                                                        |                                               | I <sub>D</sub> =200 μA, T <sub>A</sub> =25°C                                         | 500  |            |         | V        |

|                                                                     |                                                                                        | I <sub>D</sub> =200 μA, T <sub>A</sub> =125°0 |                                                                                      |      | 540        |         | V        |

| В                                                                   | On State Desistance                                                                    | FSFR1800HS/L                                  | V <sub>GS</sub> =10 V, I <sub>D</sub> =3.0 A                                         |      | 0.77       | 0.95    |          |

| R <sub>DS(ON)</sub>                                                 | On-State Resistance                                                                    | FSFR1700HS/L                                  | V <sub>GS</sub> =10 V, I <sub>D</sub> =2.0 A                                         |      | 1.00       | 1.25    | Ω        |

|                                                                     | Body Diode Reverse                                                                     | FSFR1800HS/L                                  | V <sub>GS</sub> =0 V, I <sub>DIODE</sub> =7.0 A,<br>dI <sub>DIODE</sub> /dt=100 A/μs |      | 160        |         |          |

| t <sub>rr</sub>                                                     | Recovery Time <sup>(7)</sup>                                                           | FSFR1700HS/L                                  | V <sub>GS</sub> =0 V, I <sub>DIODE</sub> =6.0 A,<br>dI <sub>DIODE</sub> /dt=100 A/μs |      | 2          |         | ns       |

|                                                                     | Input Capacitance <sup>(7)</sup>                                                       | FSFR1800HS/L                                  |                                                                                      |      | 639        |         | ρF       |

| C <sub>ISS</sub>                                                    | Input Capacitance                                                                      | FSFR1700HS/L                                  | V <sub>DS</sub> =25 V, V <sub>GS</sub> =0 V,                                         |      | 512        |         | ρF       |

|                                                                     | Output Capacitance <sup>(7)</sup>                                                      | FSFR1800HS/L                                  | f=1.0 MHz                                                                            |      | ر2.1       |         | pF       |

| Coss                                                                | Output Capacitance                                                                     | FSFR1700HS/L                                  |                                                                                      |      | 66.5       | 7       | pF       |

| Supply Sec                                                          |                                                                                        |                                               |                                                                                      |      |            |         |          |

| I <sub>LK</sub>                                                     | Offset Supply Leakage Current H\' -V <sub>CT+</sub> 500                                |                                               |                                                                                      | 2    |            | 50      | μΑ       |

| I <sub>Q</sub> HV <sub>CC</sub>                                     | Quiescent HV <sub>cc</sub> Supply Current HV <sub>c</sub> Vv 1 V                       |                                               | HVc Vv 1V                                                                            |      | <b>5</b> U | 120     | μA       |

| I <sub>Q</sub> LV <sub>CC</sub>                                     | Quiescent LV <sub>CC</sub> Supply Current (Linch +) - 0.1 V                            |                                               |                                                                                      | 100  | 200        | μΑ      |          |

| I <sub>O</sub> HV <sub>CC</sub>                                     | Operating HV Supply (                                                                  | root (PM) (aluo) fosc 70 KHz                  |                                                                                      | 250  | 6          | 9       | mA       |

| I <sub>O</sub> HV <sub>CC</sub> Operating HV <sub>CC</sub> Supply C |                                                                                        | differit (Nivic alue)                         | No Switching                                                                         |      | 100        | 200     | μΑ       |

| I <sub>o</sub> LV <sub>cc</sub>                                     | Operating LV <sub>cc</sub> Supply ( + 'S v )   f <sub>05c</sub> =£0 kHz   No Switching |                                               |                                                                                      | 1211 | 7          | 11<br>4 | mA<br>mA |

| UVLO Sect                                                           | tion                                                                                   |                                               | W. A. C. VIA                                                                         |      | ı          |         | I        |

| LV <sub>CC</sub> UV+                                                | LV <sub>CC</sub> Supply inder-Volu                                                     | a P litive Going Thres                        | shoid (LV <sub>CC,START</sub> )                                                      | 11.2 | 12.5       | 13.8    | V        |

| LV <sub>CC</sub> UV-                                                | LV <sub>CC</sub> Supply 'nder-V' ta                                                    | ge Negative Coing Thre                        | -stivid (LV <sub>CC,37 OP</sub> )                                                    | 8.9  | 10.0       | 11.1    | V        |

| LV <sub>CC</sub> UVH                                                | LV Supply L 'or' ultage Hysteresis                                                     |                                               |                                                                                      |      | 2.5        |         | V        |

| HV <sub>CC</sub> UV+                                                | HVcc Juppi Under-Voitage Positive Going Threshold (HVcc.start)                         |                                               |                                                                                      | 8.2  | 9.2        | 10.2    | V        |

| HV                                                                  | Under Voltage Negative Going Threshold (HVcc,stop)                                     |                                               |                                                                                      | 7.8  | 8.7        | 9.6     | V        |

| t cUVh                                                              | H. HV Supply Under-Voltage Flysteresis                                                 |                                               |                                                                                      |      | 0.5        |         | V        |

| Osc 'ator                                                           | Feedback Section                                                                       | NI                                            |                                                                                      | •    |            |         | •        |

| V <sub>R</sub>                                                      | Οιύρ It Voltage on RT Pin                                                              |                                               | 1.5                                                                                  | 2.0  | 2.5        | V       |          |

| fosc                                                                | Cutput Oscillation Frequency R <sub>T</sub> =26 kΩ                                     |                                               |                                                                                      | 47   | 50         | 53      | kHz      |

| D.;                                                                 | Output Duty Cycle                                                                      | -                                             |                                                                                      | 48   | 50         | 52      | %        |

|                                                                     |                                                                                        |                                               |                                                                                      |      |            |         |          |

Continued on the following page...

### **Electrical Characteristics** (Continued)

$T_A$  =25°C, LV<sub>CC</sub>, HV<sub>CC</sub> =17 V<sub>DC</sub> and  $R_T$  =26  $k\Omega$  unless otherwise specified.

| Symbol                   | Parameter Conditions                                                  |                           | Min. | Тур. | Max.  | Unit |

|--------------------------|-----------------------------------------------------------------------|---------------------------|------|------|-------|------|

| Protection               | Section                                                               |                           |      | •    | •     |      |

| V <sub>RT,RESET</sub>    | Threshold Voltage to Begin Restart                                    |                           | 0.07 | 0.12 | 0.17  | V    |

| t <sub>DELAY,RESET</sub> | Delay to Disable OSC Circuit After Protection                         | f <sub>osc</sub> =50 kHz  |      | 20   |       | ms   |

| $V_{LINE}$               | On Threshold of Input Voltage                                         |                           | 2.38 | 2.50 | 2.62  | V    |

| I <sub>LINE</sub>        | Hysteresis Current for Line UVLO                                      |                           |      | 9.5  | 11.5  | μA   |

| $V_{OVP}$                | LV <sub>CC</sub> Over-Voltage Protection                              |                           |      | 23   | 25    | V    |

| $V_{AOCP}$               | AOCP Threshold Voltage                                                |                           | -1.0 | -0.9 | -0.8  | V    |

| t <sub>BAO</sub>         | AOCP Blanking Time <sup>(7)</sup> V <sub>CS</sub> < V <sub>AOCP</sub> |                           |      | -0   |       | ns   |

| V <sub>OCP</sub>         | OCP Threshold Voltage                                                 |                           | -0.6 | -0.5 | -0.52 | V    |

| t <sub>BO</sub>          | OCP Blanking Time <sup>(7)</sup> V <sub>CS</sub> < V <sub>OCP</sub>   |                           | 1.0  | 1.5  | 2.0   | Ģε   |

| t <sub>DA</sub>          | Delay Time (Low-Side) Detecting from V <sub>AOCP</sub> to             | Switch Off <sup>(7)</sup> |      |      | 400   | ns   |

| T <sub>SD</sub>          | Thermal Shutdown Temperature <sup>(7)</sup>                           |                           |      | 135  | 150   | °C   |

| Dead-Time                | Control Section                                                       |                           |      | CV   | 4     |      |

| D <sub>T</sub>           | Dead Time <sup>(8)</sup>                                              |                           | 7    | 350  |       | ns   |

#### Notes:

- 7. This parameter, although guaranteed, is not tested in tour tion

- 8. These parameters, although guaranteed, are tested in ly in . \S \ afer test\) process

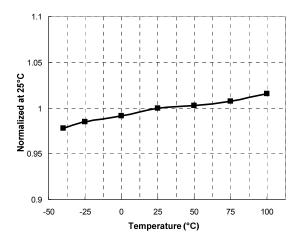

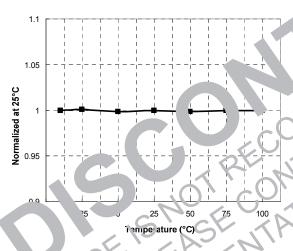

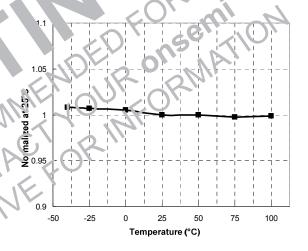

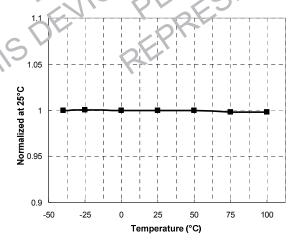

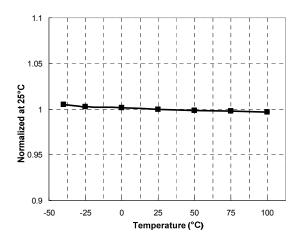

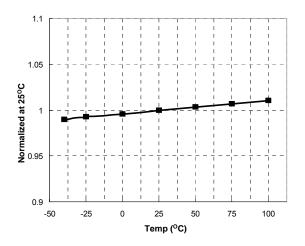

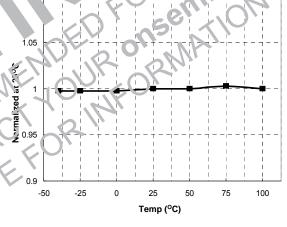

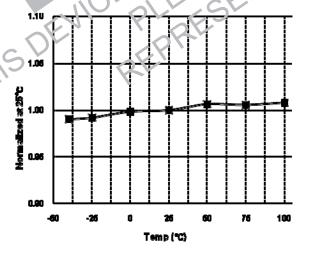

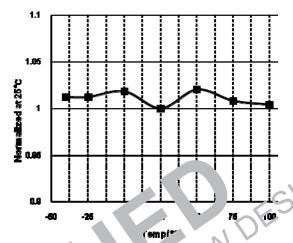

## **Typical Performance Characteristics**

These characteristic graphs are normalized at T<sub>A</sub>=25°C.

1.1 1.05 1.05 0.95 0.9 -50 -25 0 50 75 100

Figure 4. Low-Side MOSFET Duty Cycle vs. Temperature

Figure Sw hing requency's Temperature

Fig. . High Side V<sub>CC</sub> (HV<sub>C</sub>;) Start vs. 7emperature

Figure 7. High-Side  $V_{CC}$  (HV<sub>CC</sub>) Stop vs. Temperature

Figure 8. Low-Side  $V_{CC}$  (LV<sub>CC</sub>) Start vs. Temperature

Figure 9. Low-Side  $V_{\text{CC}}$  (LV<sub>CC</sub>) Stop vs. Temperature

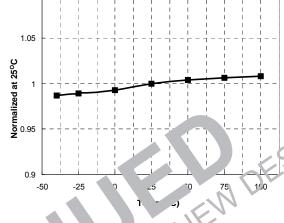

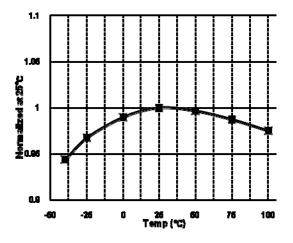

## **Typical Performance Characteristics** (Continued)

These characteristic graphs are normalized at T<sub>A</sub>=25°C.

Figure 10. LV $_{\text{CC}}$  OVP Voltage vs. Temperature

1.1

Fig re RT oltage v.s. Temperature

Jure 12. V<sub>RT,RESET</sub> Vs. Vemperature

Figure 13. OCP Voltage vs. Temperature

Figure 14. VLINE vs. Temperature

Figure 15. ILINE vs. Temperature

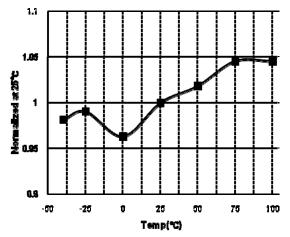

## **Typical Performance Characteristics** (Continued)

These characteristic graphs are normalized at T<sub>A</sub>=25°C.

Figure 16. t<sub>DELAY,RESET</sub> vs. Temperature

Fig 9 17. REL J. Temperature

## **Functional Description**

**1. Basic Operation:** FSFR-HS series is designed to drive high-side and low-side MOSFETs complementarily with 50% duty cycle. A fixed dead time of 350 ns is introduced between consecutive transitions, as shown in Figure 18.

Once LV<sub>CC</sub> is higher than LV<sub>CC,START</sub> = 12.5 V, the IC starts to operate, generates the low-side gate signal, and drives the low-side MOSFET. The bootstrap diode and capacitor is charged by the low-side MOSFET's operation. After the voltage on HV<sub>CC</sub> increases up to HV<sub>CC,START</sub>, typically 9.2 V, the high-side gate signal is generated for the MOSFET.

Figure 18. MOSFET Gate Drive Signals

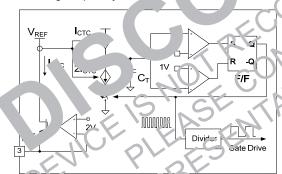

2. Internal Oscillator: FSFR-HS series employ current-controlled oscillator, as shown in Fig e 19. Internally, the voltage of the RT pin is regulated 2 V and the charging / discharging current for capacitor,  $C_T$ , is obtained by copying current for out of the RT pin ( $I_{CTC}$ ) using a current min  $T_{CTC}$  are fore, the switching frequency increases  $T_{CTC}$  in eases.

Figure 19. Current-Controlled Oscillator

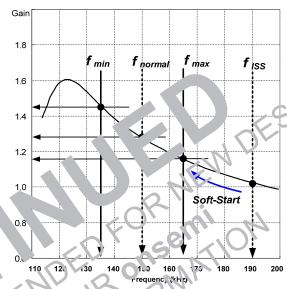

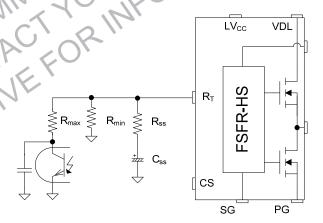

requency Setting: Figure 20 shows the typical voltage gain curve of a resonant converter, where the gain is inversely proportional to the switching frequency in the ZVS region. The output voltage can be regulated by modulating the switching frequency. Figure 21 shows the typical circuit configuration for the RT pin, where the opto-coupler transistor is connected to the RT pin to modulate the switching frequency. The switching frequency may be controlled from 20 kHz to 500 kHz.

The minimum switching frequency is determined as:

$$f_{min} = \frac{1}{792 \, p \times R_{min} + 0.54 \mu} \, [Hz] \tag{1}$$

Assuming the saturation voltage of opto-coupler transistor is 0.2 V, the maximum switching frequency is determined as:

$$f_{max} = \frac{1}{792 p \times R_{min} / |R_{max} + 0.54\mu} [Hz]$$

(2)

Figure 20. Resonant Conventor Typical Gain Curve

Figure 21. Frequency Control Circuit

To prevent excessive inrush current and overshoot of output voltage during startup, the IC needs to increase the voltage gain of the resonant converter progressively. Since the voltage gain of the resonant converter is inversely proportional to the switching frequency, softstart is implemented by sweeping down the switching frequency from an initial high frequency ( $f_{ISS}$ ) until the output voltage is established.

The soft-start circuit is constructed by connecting R-C series network to the RT pin, as shown in Figure 21. Initially, the operating frequency is set by the parallel impedance of  $R_{\rm SS}$  and  $R_{\rm min}.$

The initial maximum frequency can be set up to 600 kHz, which is given by:

$$f_{ss} = \frac{1}{792 \, p \times R_{\min} \, || \, R_{SS} + 0.54 \mu} \, [Hz] \tag{3}$$

The soft-start time,  $t_{SS}$ , can be calculated by:

$$t_{SS} = 3 \times R_{SS} \cdot C_{SS} [s]$$

(4)

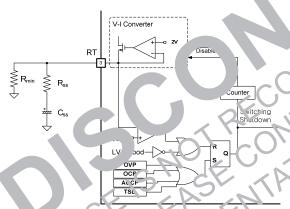

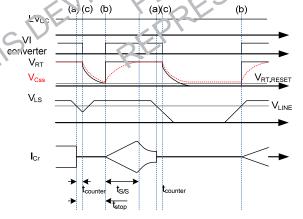

**4. Self Auto-Restart:** The FSFR-HS series can restart automatically even though any built-in protections are triggered in case external supply voltage is applied. As shown in Figure 22 and Figure 23; once a protection is triggered, the power MOSFET immediately stops. The counter starts to operate and 1008-clocks are counted, then the V-I converter is disabled.  $C_{\rm SS}$  starts to be naturally discharged with the series impedance of  $R_{\rm SS}$  and  $R_{\rm min}$  until  $V_{\rm RT}$  drops to  $V_{\rm RT,RESET}$ , typically 0.1 V. Then, all protections are reset and the V-I converter resumes. The FSFR-HS starts switching again with soft-start.

The counter operating time for 1008-clocks after protection activation is set by the current out of the RT pin until  $V_{RT}$  drops to  $V_{RT,RESET}$ . Finally, the stop time of FSFR-HS can be estimated, without considering the counter operation time, as:

$$t_{STOP} = 3C_{SS} \cdot (R_{SS} + R_{min}) [s]$$

(5)

gure 22. Internal Block for Auto-Festart

(a) Protection Trigger, (b) FSFR-HS Restart, (c) Counter Stop

Figure 23. Self Auto-Restart Operation

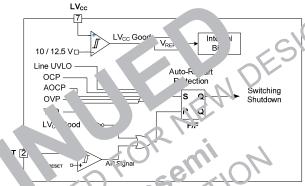

**5. Protection Circuits:** The FSFR-HS series has several self-protective functions; such as Over-Current Protection (OCP), Abnormal Over-Current Protection (AOCP), Over-Voltage Protection (OVP), Thermal Shutdown (TSD), and Line Under-Voltage Lockout (LUVLO or Brownout). These protections are Auto-Restart Mode protections, as shown in Figure 24.

Once a fault condition is detected, switching is instantly terminated and the MOSFETs remain off. When LV<sub>CC</sub> falls to the LV<sub>CC</sub> stop voltage of 10 V and V<sub>RT</sub> is lower than V<sub>RT,RESET</sub> of 0.1 V, the protection is reset. The FSFR-HS resumes normal operation when LV<sub>CC</sub> reaches the start voltage of 12.5 V.

Figure 24. Protection Blocks

- 5.1 O ter-Current Protection (OCP): When the sensing pin voltage drops below -0.58 V and its curation becomes more han OCP blanking time of 1.5 µs, OCP is trigge ed and the MOSFETs remain off.

- 5.2 Abnormal Over-Current Protection (AOCP): If the secondary rectifier diodes are shorted, large current with extremely high di/dt can flow through the MOSFET before OCP is triggered. AOCP is triggered without shutdown delay if the sensing pin voltage drops below -0.9 V.

- **5.3 Over-Voltage Protection (OVP)**: When the LV<sub>CC</sub> reaches 23 V, OVP is triggered. This protection is used when auxiliary winding of the transformer supplies  $V_{CC}$  to the FPS<sup>TM</sup>.

- **5.4 Thermal Shutdown (TSD)**: The MOSFETs and the control IC in one package make it easier for the control IC to detect the abnormal over-temperature of the MOSFETs. If the temperature exceeds approximately 130°C, thermal shutdown triggers.

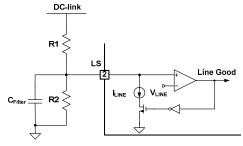

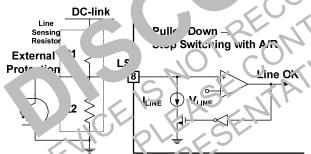

- **6. Line Under-Voltage Lockout (UVLO):** FSFR-HS includes precise line UVLO (or brownout) with programmable hysteresis voltage. This function can start or restart the IC when  $V_{LS}$  for the scale-down voltage of the DC-link by the sensing resistors, R1 and R2, is higher than  $V_{LINE}$  of 2.5 V as the DC-link voltage increases and vice versa. A hysteresis voltage between the start and stop voltage of the IC is programmable by  $I_{LINE}$ . In normal operation, the comparator's output is HIGH and  $I_{LINE}$  is deactivated so that a voltage on LS pin,  $V_{LS}$ , can be obtained as a divided voltage by R1 and R2. On the contrary,  $I_{LINE}$  is activated when the comparator's output is LOW.  $V_{LS}$  is generated by the difference between the current through R1 and  $I_{LINE}$ .

$C_{\text{Filter}}$  can be used to reduce some noise induced from transformer or switching transition. Generally, hundreds of pico-farad to tens of nano-farad is adequate, depending on the quantity of noise.

The start and stop input-voltage can be calculated as:

$$V_{dc-link,STOP} = V_{LINE} \times \frac{R1 + R2}{R2} \quad [V]$$

(6)

$$V_{dc-link,START} = V_{dc-link,STOP} + I_{LINE} \times R1 \ [V]$$

(7)

Figure 25. Half-Wave Sensing

**7. Simple Remote-On/Off:** The power stage can be shutdown with optional Auto-Restart Mode, as shown Figure 26.

To configure an external protection with Auto-, start Mode, an opto-coupler and the LS pin are the voltage on the LS pin is pulled below to be the voltage on the LS pin is pulled below to be the voltage on the LS pin is pulled below to be the voltage on the LS pin is pulled below to be the voltage on the LS pin is pulled below to be the voltage on the LS pin is pulled below to be the voltage of the voltage o

Figure 26. External Protection Circuits

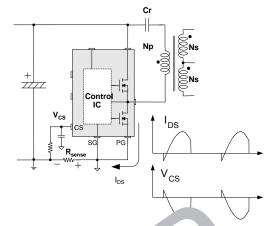

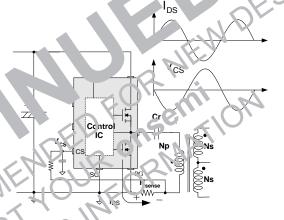

- **3. Current-Sensing Methods:** FSFR-HS series employs negative voltage sensing to detect the drain current of MOSFET, which allows a low-noise resistive sensing using a filter with low time-constant and capacitive sensing method.

- **8.1 Resistive Sensing Method:** The IC can sense drain current as a negative voltage, as shown in Figure 27 and Figure 28. Half-wave sensing allows low power dissipation in the sensing resistor; while full-wave sensing has less switching noise in the sensing signal. For a time constant range for the filter, 3/100~1/10 of the operating frequency is reasonable.

Figure 27. Half Wa Sens g

Figure 28. Full-Wave Sensing

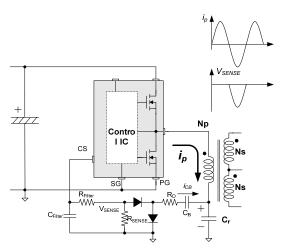

**8.2** Capacitive Sensing Method: The drain current can be sensed using an additional capacitor parallel with the resonant capacitor, as shown in Figure 29. During the low-side switch turn on, the current,  $i_{CB}$  through  $C_B$ , makes  $V_{SENSE}$  across  $R_{SENSE}$ . The  $i_{CB}$  is scale-down of  $i_p$  by the impedance ratio of  $C_r$  and  $C_B$ . Generally,  $1/100 \sim 1/1000$  is adequate for the ratio of  $C_B$  against  $C_r$ .  $R_D$  is used as a damper for reducing noise generated by switching transition. Several hundreds of ohm to a few of kilo-ohms can be normally used.

V<sub>SENSE</sub> can be estimated as;

$$V_{sense} = I_{Cr}^{pk} \frac{C_B}{Cr} \cdot R_{sense}[V]$$

(8)

Figure 29. Capacitive Sensing

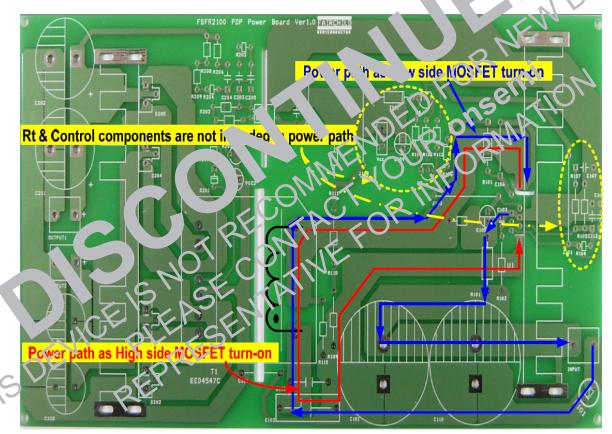

9. PCB Layout Guidelines: Duty imbalance problems may occur due to the radiated noise from the main transformer, the inequality of the secondary side leakage inductances of main transformer, and so on. This is one of the reasons that the control components in the vicinity of the RT pin are enclosed by the primary current flow pattern on PCB layout. The direction of the magnetic field on the components caused by the primary current flow is changed when the high- and low-side MOSFET turn on by turns. The magnetic fields with opposite directions induce a current through, into, or out of the RT pin, which makes the turn-on duration of each MOSFET different. It is strongly recommended to separate the control components in the vicinity of the RT pin from the primary current flow pattern in the PCB layout. Figure 30 shows an le for a dutybalanced case.

Figure 30. Example of Duty Balancing

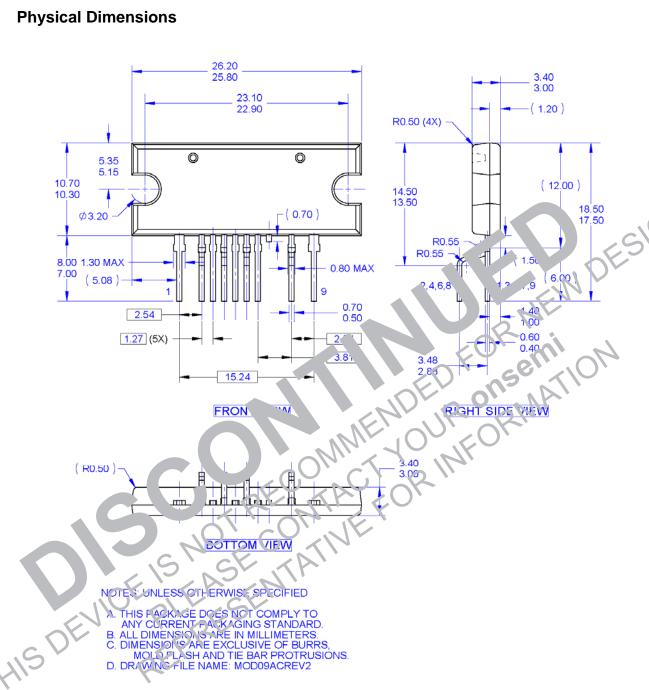

Figure 31. 9-Lead, Single Inline Package (SIP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>.

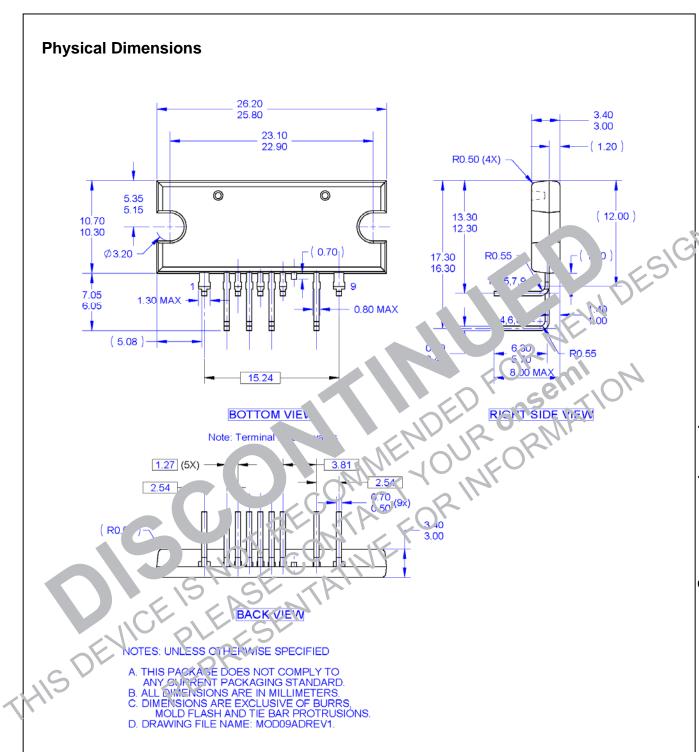

Figure 32. 9-Lead, Single Inline Package (SIP), L-Forming

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

## U

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

Sync-Lock™ 2Cool™ **FPSTM** AccuPower™ F-PFS™ SYSTEM GENERAL® AX-CAP®\* FRFET® PowerTrench® Global Power Resources BitSiC™ TinyBoost™ PowerXS™ GreenBridge™ TinyBuck™ Build it Now™ Programmable Active Droop™ CorePLUS™ Green FPS™ TinyCalc™ Green FPS™ e-Series™ Core POWER™ QSTM TinyLogic® Gmax™ CROSSVOLT" TINYOPTO\*\* Quiet Series™ CTL™ GTO™ TinyPower™ RapidConfigure™ Current Transfer Logic™ IntelliMAX™ Ti~~PV/MTM DEUXPEED<sup>®</sup> ISOPLANAR™ Saving our world, 1mW/W/kW at a time™ Making Small Speakers Sound Louder and Better™ Dual Cool™ TranS<sub>I</sub> SignalVise™ EcoSPARK® tect™ TriFault SmartMax™ MegaBuck™ EfficientMax™ PUEC' **⋌RENT** SMART START™ ESBC# MICROCOUPLER™ Solutions for Your Succers™ MicroFET™ SPM<sup>®</sup> MicroPak™ airchild<sup>®</sup> STEALTH™ MicroPak2™ Fairchild Semiconductor® SuperFET® MillerDrive™ U. "a FREET" FACT Quiet Series™ SuperSOT\* MotionMax™ THE ETTM FACT® SuperSOTMmWSaver™ FAST® VCXTM -u\_8 Sup. OptoHiT™ VisualMax™ FastvCore™ ipre. OPTOLOGIC® VricgcPlus™ ′S™ FETBench™ cFE OPTOPLANAR®

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE PIGHT 1 MAIN GES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRC SET SN. ASSUM. ANY LIABILITY ARISING CUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN, NEITHE JOES IT MAY LIABILITY ANY LICENSE SNUERITS PAIT FIRT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TIMES OF FAIRLY SWORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCT

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS AR. OT AUTI RIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTE ACROSS OF FAIR HILD SEM CONDUCTOR CORPORATION.

#### As used herein:

1. Life such that we see the same devices or systems, which, (a) are intended for surrolled in and into the body or (b) support or sustain and the final value of the perform when properly used in account of the instructions for use provided in the labeling can be reasonably expected to result in a significant rijury of the user

A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### AN CO' (ERFE!TING POLICY

Fairch Semicon of con Corporation : Anti-Counterfering Folicy: Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Stopport.

Counterfering of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Our toniers who inadvertently purch so counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of proof, do not and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the profession of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full trachability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Datasheet Identification                 | Product Status        | Definition                                                                                                                                                                                          |  |  |

|------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information                      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |

| Preliminary First Producti               |                       | Datasheet contains preliminary data, supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed Full Production |                       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |

| Obsolete                                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |  |  |

Rev. 164

<sup>\*</sup> Trademarks of System General Corporation, used under lice by Fair 1 Semic Inductor

ON Semiconductor and III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns me rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative